## Recent progress in parallel fabrication of individual single walled carbon nanotube devices using dielectrophoresis

Muhammad R. Islam<sup>1, 2</sup>, and Saiful I. Khondaker<sup>1, 2, 3\*</sup>

<sup>1</sup> Nanoscience Technology Center, <sup>2</sup> Department of Physics, <sup>3</sup>School of Electrical Engineering and Computer Science, University of Central Florida, Orlando, Florida 32826, USA.

\* To whom correspondence should be addressed. E-mail: saiful@mail.ucf.edu

## ABSTRACT

Single walled carbon nanotubes (SWNTs) have attracted immense research interest because of their remarkable physical and electronic properties. In particular, electronic devices fabricated using individual SWNT have shown outstanding device performance surpassing those of Si. However, for the widespread application of SWNTs based electronic devices, parallel fabrication techniques along with Complementary Metal Oxide (CMOS) compatibility are required. One technique that has the potential to integrate SWNTs at the selected position of the circuit in a parallel fashion is AC dielectrophoresis (DEP). In this paper, we review recent progress in the parallel fabrication of SWNT-based devices using DEP. The review begins with a theoretical background for the DEP and then discusses various parameters affecting DEP assembly of SWNTs. We also review the electronic transport properties of the DEP assembled devices and show that high performance devices can be fabricated using DEP. The technique for fabricating all semiconducting field effect transistor using DEP is also reviewed. Finally, we discuss the challenges and opportunities for the DEP assembly of SWNTs.

## Table of content:

- 1. Introduction

- 2. Theory of DEP

- 3. History of the DEP assembly of SWNT

- 4. Experimental SET up for the DEP assembly of individual SWNT

- 5. Parameters controlling the DEP assembly of individual SWNT

- 6. Electronic transport properties of DEP assembled individual SWNTs

- 6.1 Properties of individual SWNT devices assembled from mixed SWNT solution

- 6.2 Properties of individual SWNT devices assembled from semiconducting rich SWNT solution

- 6.3 Towards high yield fabrication of all SWNT FET devices via DEP

- 7. Conclusion and future outlook

Acknowledgement

References

#### **1. INTRODUCTION**

Due to their unique electrical, mechanical, and optical properties, single-walled carbon nanotubes have attracted tremendous attention as a promising building block for future nanoelectronic devices such as field effect transistors (FET), light emitting diodes, sensors, solar cell, memory devices, <sup>1-15</sup> as well as electrodes for fabricating organic devices. <sup>16-18</sup> Although several prototypes of these devices have been demonstrated with mobility of up to 79,000 cm<sup>2</sup>/Vs and transconductance of up to 6000 S/m which is significantly higher than currently prevalent silicon technology,<sup>7, 9</sup> a major bottleneck towards their commercial application is a reliable and cost effective technique for the scaled up fabrication of the SWNTs devices.<sup>1, 3, 4</sup> Scaled up fabrication of SWNT devices require assembly of SWNTs at the precise position of the circuits where the density of SWNTs can be tuned depending upon the intended application. In addition, the fabrication technique needs to be compatible with current CMOS technology which will provide added benefit of fabricating integrated circuits with SWNTs.

Scaled up integration of SWNTs were attempted via chemical vapor deposition (CVD) where nanotubes are grown directly onto the substrate using lithographically patterned catalytic island.9, 19-23 Although CVD grown SWNTs demonstrate the best device performance including novel physics,<sup>24-28</sup> the high temperature (~900°C) required for the growth of SWNTs makes it incompatible with the current CMOS technologies.<sup>29</sup> Post synthesis assembly from the SWNTs solution is an attractive alternative to the CVD technique. Easy and simple set up, low cost, and CMOS compatible room temperature operation makes the solution-processed post growth assembly advantageous over the direct growth assembly. Several solution processed techniques for the assembly of SWNTs has been demonstrated. These includes, chemical and biological patterning,<sup>30, 31</sup> bubble blown films,<sup>32</sup> Langmuir-Blodgett assembly,<sup>33</sup> flow assisted alignment,<sup>34</sup> contact printing,<sup>35</sup> evaporation driven self-assembly,<sup>36</sup> and spin coating assisted self-assembly.<sup>37</sup> However, most of these techniques lack precise control over positioning and orientation of individual SWNTs. In addition, after the assembly, post etching is required to remove the excess SWNTs from the circuit. As a result, most of these techniques may not be appropriate for scaled up fabrication of individual SWNTs devices. One technique that has been effective in assembling individual SWNTs with high yield is AC dielectrophoresis (DEP).<sup>38-40</sup> DEP has also shown to be affective in assembling 2D and 0D materials for device applications.<sup>41-45</sup> DEP can be advantageous over other solution processed techniques because it allows precise control over the assembly of individual SWNTs between prefabricated electrodes at the selected positions of the circuits and does not require post-etching or transfer printing. DEP can also control the density of the nanotubes at a given site from individual to a thin film of SWNTs for various device applications.<sup>38-40, 46-50</sup> As a result, there is a recent surge in the research interest of the DEP assembly of SWNTs.

In this paper, we review the recent progress of DEP assembly of individual SWNTs and the electronic transport properties of the DEP assembled devices. The review begins with a discussion of the theory of DEP force and DEP assembly of SWNTs. We will present a historic overview of the DEP assembly of SWNT devices. We then discuss the role of different parameters in the DEP assembly of individual SWNT with a focus on high yield integration of SWNTs devices. This will be followed by the assembly of SWNTs from a mixed solution and semiconducting rich solution. Electronic transport properties of the devices will also be discussed. We will conclude by discussing the challenges and opportunities on the DEP assembly of SWNTs. Although this review summarizes the history and techniques for the DEP assembly of SWNTs, the most recent progress in individual SWNT devices were emphasized. For readers who are interested in network type SWNT, we refer to several recent review articles.<sup>51-53</sup>

## 2. Theory of DEP

Dielectrophoresis (DEP) is the phenomena wherein a polarized particle experiences a force and gains translational motion when it is placed in a non-uniform electric field.<sup>54-56</sup> This force was first recognized and described by Pohl in 1951.<sup>57</sup> When a non-uniform electric field is applied to a suspension of polarizable particles, surface charges of different polarity are induced on either side of the particle resulting in the formation of a dipole moment and cause the particle to experience a net force. As a result, the particle undergoes a translational motion and aligns along the direction of electric field lines. When the field is uniform, no net charge is induced on the particle and it does not experience any force.

When placed in an inhomogeneous electric field, the DEP force experienced by a polarized particle is given by  $\vec{F} = (\vec{p} \cdot \vec{\nabla})\vec{E}$ , where  $\vec{p} = v\alpha\vec{E}$  is the induced dipole moment of the particle, *v* is the volume of the particle,  $\alpha$  is complex effective polarizability, and *E* is the applied electric field. For a SWNT, the

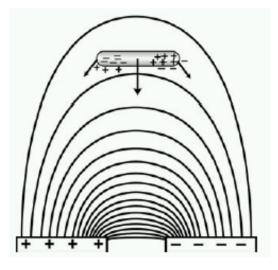

**Fig. 1.** Sketch illustrating a carbon nanotube subjected to dielectrophoresis. The nanotube immediately aligns with the field lines and experiences a net force from the ac field. This force may be directed towards the high field region (down) in the case of positive dielectrophoresis (shown), and towards the low field region (up) for negative dielectrophoresis (not shown). Reproduced with permission from [58], M. Dimaki et al., *Nanotechnology* 15, 1095 (**2004**). © 2004, IOP Publishing Ltd.

DEP force can be calculated from an effective dipole approximation by considering it as a cylinder. A simplified diagram of the DEP force on a SWNT is shown in figure 1. The DEP force acting on the tube with its major axis parallel to the applied electric field is given by<sup>58,59</sup> (new ref)  $F = \frac{\pi r^2 l}{2} \varepsilon_m^* R \varepsilon(K_A) \nabla |E|^2$  where  $\varepsilon_m$  is the real part of permittivity of the suspending medium,  $K_A$  is the Clausias-Mossotti (CM) factor which depends on both the complex dielectric constant of the medium ( $\varepsilon_m^*$ ) and the particle ( $\varepsilon_p^*$ ) and is given by  $K_A = \frac{\varepsilon_p^* - \varepsilon_m^*}{3\varepsilon_m^*}$  where  $\varepsilon^* = \varepsilon - i\frac{\sigma}{\omega}$ . Here  $\varepsilon$  is the real permittivity,  $\sigma$  is the conductivity, and  $\omega = 2\pi f$  is the frequency

of the electric field. A more detailed calculation and finite element simulation can be found in ref  $^{60}$ .

DEP force depends on the physical properties of the SWNTs as well as the properties of the medium in which the SWNTs are suspended. Depending on the permittivity of the SWNT  $(\varepsilon_p^*)$  and the suspending medium  $(\varepsilon_m^*)$ , DEP force can be either positive or negative. If  $\varepsilon_p^* > \varepsilon_m^*$  then  $K_A$  is positive, in this case the dipole moment will align along the electric field and is called positive DEP. The opposite case will occur if  $\varepsilon_p^* < \varepsilon_m^*$  in which case the particle will be directed away from the electric field and is called negative DEP. Metallic SWNT (m-SWNT) and semiconducting SWNT (s-SWNT) experiences different DEP forces due to their different dielectric constant. Typically, m-SWNTs has a dielectric constant much larger than that of the suspending medium which cause them to experience greater DEP force compared to semiconducting SWNTs<sup>58</sup>. In addition, the DEP force also depends on the size of the particle, therefore particles with larger volume experience a greater DEP force. The effect of DEP parameters on the directed assembly of SWNTs will be discussed in great details in section 5.

#### **3. HISTORY OF THE DEP ASSEMBLY OF SWNT**

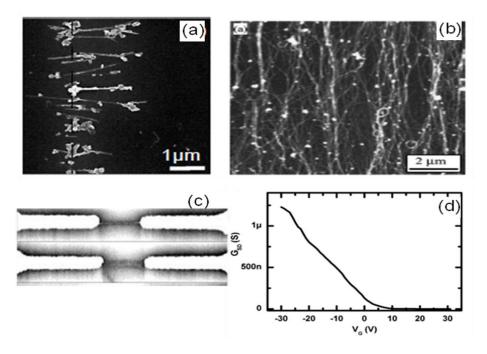

Soon after the discovery of the carbon nanotubes, DEP was used to assemble nanotubes between the prefabricated electrodes. In 1996 Yamamoto et al. demonstrated the DEP assembly of multi walled nanotubes (MWNTs).<sup>61,62</sup> Thin films of MWNTs bundles were assembled from a solution containing a mixture of MWNTs and carbon particles (Fig. 4(a)). DEP assisted alignment of SWNTs was first reported by Chen et al. in 2001.<sup>63</sup> A thin film of SWNTs bundles (Fig. 4(b)) were assembled by immersing a substrate containing source and drain electrodes in SWNTs solution and then applying AC electric field between the electrodes. It was shown that the density and alignment of SWNTs bundles depends on the frequency and magnitude of applied AC voltage. Since the SWNTs have strong van der walls interaction, they prefer to remain in bundle.<sup>64</sup> If a solution contains a lot of bundles, the DEP will assemble the bundles because of their high dielectric constant together with larger volume. Besides, the uniform electric field produced between the planer electrodes used in this study resulted in the assembly of thin films.

Assembly of single SWNT bundles was first demonstrated in 2003 by Krupke et. al <sup>65, 66</sup> (Fig. 4(c)). In addition, taper shaped electrode was used which helps assembly of single bundles as the field was strongest at the edge of the tip. Unlike previous studies, they used purified SWNTs suspended in *N*, *N*-dimethylformamide (DMF) solvent. However, the absence of any stabilizer re-aggregates the SWNTs into bundle resulting in the assembly of individual bundles due to their high dielectric constant and larger volume. Since the bundles contain metallic SWNTs, the assembled devices show metallic behavior. However, these authors demonstrated that FET characteristics can be achieved from such a device after selectively breaking the metallic SWNTs in the bundle shown in Fig. 4(d). Controlled assembly of bundle of SWNTs by varying different DEP parameters was also demonstrated by several research groups.<sup>67-69</sup>

**Fig. 4.** (a) SEM images of a thin film of bundle of MWNT aligned by the application of electric field. Reproduced with permission from [62], K. Yamamoto et al., *J. Phys. D-Appl. Phys.* 31, L34, (**1998**). © 1998, IOP Publishing Ltd. (b) Tapping-mode AFM images of a thin film of bundle of SWNT aligned by applying DEP. Reproduced with permission from [63], X. Q. Chen et al., *Appl. Phys. Lett.* 78, 3714 (**2001**). © 2001, American Institute of Physics. (c) SEM image of single bundle of SWNT trapped by DEP, Separation between the electrodes are 400 nm. (d) Source-drain conductance  $G_{SD}$  vs gate voltage  $V_G$  for a single bundle of SWNT formed by ac-dielectrophoresis giving p-type FET behavior after selective burning of metallic SWNT by high voltage pulse. Reproduced with permission from [65], R. Krupke et al., *Nano Lett.* 3, 1019 (**2003**). © 2003, American Chemical Society.

For the assembly of individual SWNTs, a bundle free, individually dispersed SWNTs solution is needed. Usually this can be achieved either by noncovalent adsorption or covalent functionalization of SWNTs. In noncovalent adsorption, SWNTs are encapsulated with surfactants by long and aggressive sonication times. While in covalent functionalization, carboxylic groups are introduced to the SWNTs sidewall through acid treatments which separate the bundles and stabilize the suspension.

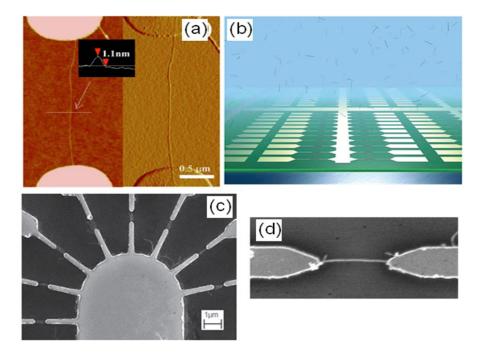

It was shown by O'Connell et al. that individually dispersed SWNTs solution can be obtained by immersing the as grown SWNTs in a aqueous solution containing Sodium dodecyl sulfate (SDS).<sup>70</sup> Advent of highly effective surfactant for individually dispersed SWNTs <sup>70-75</sup> facilitates the DEP assembly of individual SWNTs. Site selective DEP assembly of individual metallic and semiconducting SWNTs was demonstrated by Zhang et al. in 2005<sup>76,77</sup> using a surfactant stabilized SWNTs solution (Fig. 5(a)). Around the same time, controlled and reproducible alignment of individual SWNTs was demonstrated using floating-potential DEP method.<sup>64</sup> Individual SWNTs assembled by these techniques contain both metallic and semiconducting SWNTs.

**Fig. 5.** (a) AFM images images of of an individual semiconducting SWNT with diameter 1.1 nm deposited by DEP. Reproduced with permission from [77], Z. B. Zhang et al., *J. Appl. Phys.* 98, 056103 (**2005**). © 2005, American Institute of Physics. (b) Schematic of the high-density array of single-tube devices, comprising interconnected biased electrodes and counter electrodes capacitively coupled to the p-type silicon substrate SiO<sub>2</sub>. Reproduced with permission from [38], A. Vijayaraghavan et al., *Nano Lett.* 7, 1556 (**2007**). © 2007, American Chemical Society. (c) SEM image of high-density device array fabricate using semiconducting rich (99%) SWNT solution. Reproduced with permission from [91], M. Ganzhorn et al., *Adv. Mater.* 23, 1374 (**2011**). © 2011, John Wiley & Sons, Inc. (d) SEM image of individual SWNT assembled between source-drain contact with a separation of 1µm via DEP using all s-SWNT solution. Reproduced with permission from [92], M. R. Islam et al., *Nanotechnology* 23, 125201 (**2012**). © 2012, IOP Publishing Ltd.

Ultra-large-scale assembly of individual SWNT was demonstrated by Vijayaraghavan et al. in 2007 shown in Fig. 5(b).<sup>38</sup> The simultaneous deposition technique with capacitively coupled counter electrodes was used to assemble a high density of individually contacted SWNTs within a short period of time. By using a thick oxide layer of 800 nm, the authors obtained a 90% assembly yield for individual SWNTs. However, the thick gate oxide resulted in higher subthreshold swing together with large hysteresis.

Over the last few years, there has been tremendous research effort and continuous progress in producing high quality, individually dispersed, and stable SWNTs solutions.<sup>81,82</sup> This has led to the commercialization of not only high quality mixed SWNTs solution but also chirally sorted metallic and semiconducting SWNT solutions.<sup>83,84</sup> Controlled assembly of individual and array of SWNT devices using high quality SWNTs solution was demonstrated by Khondaker group.<sup>40, 46, 47, 85, 86</sup> The effect of various DEP parameters on the integration of SWNTs and performance of the assembled devices were reported in their works. They showed that individual SWNTs devices made from commercially obtained mixed SWNTs solution presents improved device performances and can be comparable to those of CVD grown SWNTs

<sup>40, 60</sup>. It was also demonstrated that the SWNTs contains much less defects or no defect which gives rise to high quality device performance.<sup>87</sup>

One of the major bottleneck in DEP assembly is that when a mixed solution of SWNTs is used, a semiconducting device yield of 50% or lower<sup>39, 40, 77, 78</sup> is obtained as metallic SWNTs feel greater force over semiconducting during the DEP assembly. Since only s-SWNTs can be used for FET application, using a mixed solution leaves a large percentage of devices non-functioning. Recently, solution based SWNTs sorting techniques have been used to separate nanotubes by chirality.<sup>37, 88-90</sup> Chirally shorted all semiconducting SWNTs (s-SWNTs) solution had been used to assemble s-SWNTs by Ganzhorn et al.<sup>91</sup>, and Islam et al.<sup>92</sup> (shown in Fig. 5(c),and 5(d) respectively). A significant improvement in the FET yield (up to 99%) had been demonstrated using a semiconducting-enriched, high quality s-SWNTs aqueous solution.<sup>91-94</sup>

#### 4. Experimental SET up for the DEP assembly of individual SWNT

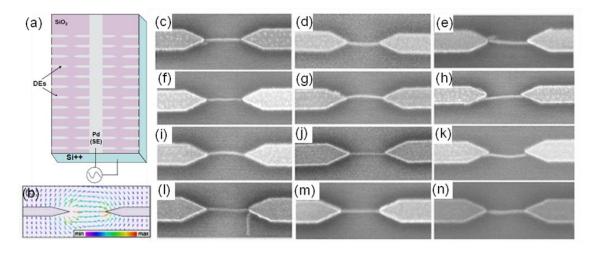

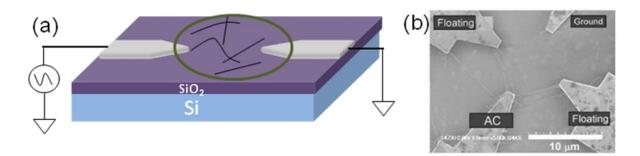

For the assembly of individual SWNTs via DEP, pre-fabricated metal electrode patterns on a suitable substrate is required. Since the assembly is done in an ambient environment and the SWNTs are solution processed, the DEP assembly technique is compatible with any substrate including plastic. Figure 2 (a) shows a cartoon of a typical DEP assembly set up. Here, the metal (Pd) electrode patterns are fabricated on a Si/SiO<sub>2</sub> substrate. The highly doped Si can be used as a global back gate while the thermally grown oxide works as a gate insulator. The metal electrode pattern has a common source for simultaneous deposition of many SWNTs between the common source and individually accessible drain electrodes. The electrode patterns can be defined by electron beam lithography (EBL) or optical lithography depending on the gap size between the electrodes. If the gap size is larger than 1 µm, optical lithography can be used while if the gap size is 1 µm or less, typically EBL is used to define the pattern. The design of the electrode gap depends on the length of the SWNTs in the solution. Although as grown SWNTs can be tens of microns long, however, solution processing of the SWNTs breaks them to a few micron length. Since, the aim is to connect individual SWNTs between the source and drain electrode patterns, the typical electrode gaps are 1-2  $\mu$ m to match the median length of SWNTs in the solution. After defining the pattern through lithography, a thin film of metals is deposited by thermal or electron beam evaporation followed by lift off. Pd or Au is widely used for the fabrication of SWNTs based field effect transistors as these materials give best contact with SWNTs.<sup>95-97</sup>

The next step in the DEP assembly involves casting of a small drop of SWNT solution of optimized concentration onto the chip containing the electrodes. An AC voltage of desired frequency is then applied between the common source electrode (SE) and gate electrode (GE) while floating the drain electrodes (DE). The AC voltage is applied for a short period of time (~1 to 3 min) depending on the solution concentration. Since the DEs are capacitively connected to the GE, they experience a similar potential as that of GE. As a result, a potential difference exists between each SE and DE which allows parallel integration of a large number SWNTs between the electrode gaps within a short time. This is called simultaneous deposition technique as it allows the deposition of a large number of SWNTs simultaneously by applying the AC voltage only once. It is expected that, as soon as one SWNTs bridges a SE - DE electrode pair, the

**Fig. 2.** (a) Schematic of the electrode array and DEP assembly setup for simultaneous deposition. Reproduced with permission from [40], P. Stokes et al., *Appl. Phys. Lett.* 96, 083110 (**2010**). © 2010, American Institute of Physics. (b) 2D simulated electric field around the electrode gap for the taper shaped electrodes and (c)-(n) SEM images of several individual SWNT assembled via DEP from commercial solution at a concentration of ~10 ng/ml. Gap between the electrodes is 1  $\mu$ m. Reproduced with permission from [85], P. Stokes et al., *J. Vac. Sci. Technol. B* 28, C6B7 (**2010**). © 2010, American Institute of Physics.

potential difference between the electrodes are significantly reduced which would prevent further deposition of SWNTs in the channel. Figure 2(a) show a schematic of a Pd electrode pattern fabricated on Si/SiO<sub>2</sub> substrate<sup>40</sup>. One important thing to notice is that the electrodes are taper shaped. Simulated image of the electric field created by the taper shaped electrodes due to AC voltage are shown in Fig. 2 (b).<sup>85</sup> It can be seen that for a taper shaped electrode the electric field is strongest at the tips, which in turn increase the probability of the alignment of individual SWNTs between the tips. If the electrodes are not taper shaped and have considerable width, it can be challenging to optimize the assembly of individual SWNTs as those electrode patterns can attract many SWNTs simultaneously. Even though the use of common back gate increases the DEP assembly yield, however using back gate for transistor operation can lead to a lower switching speed which can be circumvented using local gates discussed in section 6.

DEP assembly of individual SWNTs can also be achieved by using individual source and drain electrode (without a common source). In this case, a series of parallel SE and DE's are fabricated and an ac voltage is applied between each pair of SE and DE and then moved to the next pair. The schematic of this assembly is shown in Fig. 3 (a). Here, the time taken to assemble individual SWNTs between each pair can only be a few seconds.

Sometimes an external resistor (~  $G\Omega$ ), called a self-limiting resistor is used in series with the DEP set up.<sup>98, 99</sup> This is to ensure only an individual SWNTs is assembled between the electrodes. When an individual SWNTs is connected between the electrodes, the resistance between the electrode gap becomes much smaller (~M $\Omega$ ) than the limiting resistor and the entire applied voltage drops across the limiting resistor. In other words electric field between the electrodes.

**Fig. 3.** (a) DEP assembly setup for the assembly of SWNT using individual source and drain (b) SEM image shows a single nanotube guided along the edge of 1 $\mu$ m-wide strips using floating potential technique. Reproduced with permission from [79], Benerjee et al., *J. Vac. Sci. Technol. B* 24, 3173 (**2006**). © 2006, American Institute of Physics.

Another technique that has been used for DEP assembly of SWNT is called floating potential technique.<sup>78, 79</sup> This is shown in Fig 3 (b). In floating potential method, there is a SE where the electric field is applied (often called control electrode) while several additional metal posts are placed nearby. This technique is similar to simultaneous deposition technique where the floating posts get the potential due to capacitive coupling with the source. However, in this technique the assembled SWNTs need to be connected to drain electrode with additional lithography step.<sup>78, 80</sup>

Following the DEP assembly, the deposition yield is typically checked via Scanning electron microscopy (SEM) or atomic force microscopy (AFM). The quality of the assembly depends on the quality of the solution. If there are catalytic particles in the solution, the particles will also be assembled along with the SWNTs. In addition, if there are bundles of SWNTs, they will be preferentially assembled as the DEP force is greater for the bundle.<sup>65, 85</sup> Figure 2(c)-(n) show SEM images of a number of individual SWNTs assembled by DEP from a catalytic particle free, high quality SWNT solution.<sup>85</sup> It can be seen here that the devices are free from bundles or any additional short SWNTs in the channel. Typical assembly yield for individual SWNT varies between 20% - 30%.<sup>38-40, 78</sup> In one report, an assembly yield of up to 90% was reported.<sup>38</sup> The assembly of individual SWNT and its yield depends on the nature and quality of the solution, solution concentration, applied frequency, voltage applied, DEP time, shape of electrodes, and substrate oxide thickness.<sup>56, 59, 60, 92, 100-109</sup> The effects of those parameters on the assembly of SWNTs will be discussed in the section 5.

#### 5. PARAMETERS CONTROLLING THE DEP ASSEMBLY OF INDIVIDUAL SWNT

Assembly of SWNTs via DEP depends on several parameters such as the quality of the SWNTs solution, the magnitude of the applied AC voltage, frequency of the AC signal, size and shape of the electrodes, deposition time and substrate oxide thickness. Since DEP is a solution processed assembly technique, the assembly of individual SWNT and their yield are greatly influenced by the quality and stability of the SWNT solution. For high yield assembly of SWNTs, the solution needs to be catalytic particles free, stable, and the nanotubes need to be uniformly dispersed. Being catalytic particle free is important, as catalytic particles in the solution tend to make their way into the electrode gap along with the SWNTs during the

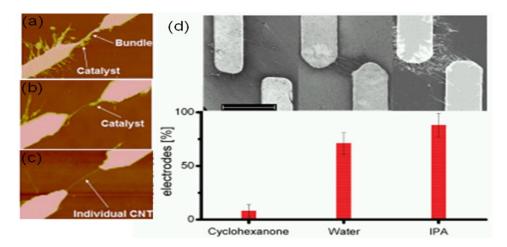

**Fig. 6.** Effect of the presence of catalyst particle on DEP assembly of individual SWNT (a) from DMF solution, (b) from DCE solution, and (c) from Brewer Science solution. Separation between the source and drain electrode is 1 $\mu$ m. Reproduced with permission from [85], P. Stokes et al., *J. Vac. Sci. Technol. B* 28, C6B7 (**2010**). © 2010, American Institute of Physics. (d) Statistics of electrode connection yield after dielectrophoresis.of CNTs dispersed in cyclohexanone, water, and IPA Representative SEM micrographs are presented for each solvent with a scale bar of 5  $\mu$ m. Reproduced with permission from [100], M. Duchmap et al., *ACS Nano* 4, 279 (**2010**). © 2010, American Chemical Society.

assembly process. The catalytic particles are highly conductive and their presence in the device can disrupt the device performance. The effect of catalytic particle on the DEP assembly of individual SWNT is shown in Fig. 6 (a)- (c)<sup>88</sup>, where (i) a homemade dimethylformide (DMF) solution, (ii) a homemade dichloroethane (DCE) solution, and (iii) a commercial catalytic particle-free aqueous SWNT solution (from Brewer Science Inc<sup>83</sup>) were used. It was found that bundles of SWNT were assembled for both the DMF and DCE solution and catalytic particle were attached to the SWNTs whereas the commercial surfactant free solution gives individual SWNT free from any catalytic particle. Along with being catalytic particle free, the SWNTs solution also needs to be highly stable over longer period of time which allows reproducible assembly.

Properties of the solvent in which SWNTs are immersed also play an important role in the DEP assembly. Since the conductivity, permittivity, and dielectric constant of SWNTs and various solvents are different,<sup>56, 59, 100, 110-114</sup> the DEP force is therefore unique for each solvent used, resulting in differences in the assembly yield. SWNTs immersed in a solvent with a low conductivity experience a higher DEP force compared to a solvent with high conductivity.<sup>56</sup> Besides, solvent with a low dielectric permittivity does not contribute to the DEP force resulting in low DEP yield.<sup>56, 100</sup> For example, the dielectric permittivity of both DI water and IPA is higher compared to that of cyclohexanone, which results in a higher assembly yield as shown in Fig. 6 (d).<sup>100</sup> In addition, volatile solvents represent additional challenges as the solvent can be evaporated before the assembly can be completed.

The DEP force, and hence the assembly can be manipulated significantly by varying the magnitude and frequency of the applied AC voltage. At low voltage the assembly yield is low as

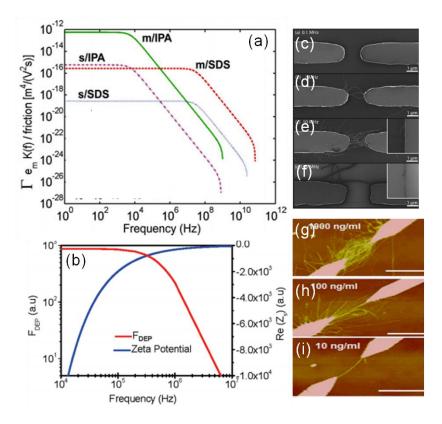

**Fig. 7.** (a) A plot of real part of Clausius-Mossotti (CM) factor as a function of frequency. Reproduced with permission from [56], M. Dimaki et al., *Nanotechnology* 15, 1095 (**2004**). © 2004, IOP Publishing Ltd. (b) Plot of DEP force (left axis) and zeta- potential (right axis) as a function of frequency. Reproduced with permission from [47], B. K. Sarker et al., *ACS Nano* 5, 6297 (**2011**) © 2011, American chemical Society. Frequency dependent DEP deposition yield studies at constant potentials. (c) 100 kHz (d) 1 MHz. (e) 10 MHz, and (f) 100 MHz. Scale bar: 1µm. Reproduced with permission from [103], B. R. Brug et al., *J. Appl. Phys.* 107, 124308 (**2010**). © 2010, American Institute of Physics. Dependence of solution concentration on the assembly of SWNT (g) 1000 ng/ml (h) 100 ng/ml, and (i)10 ng/ml in the solution. Scale bar: 1µm . Reproduced with permission from [85], P. Stokes et al., *J. Vac. Sci. Technol. B* 28, C6B7 (**2010**). © 2010, American Institute of Physics.

the DEP force is not strong enough for the SWNTs to align and assemble. The yield increases with the increase of applied voltage<sup>98, 115</sup>. However, application of a very high voltage can break the assembled SWNTs and therefore reduces the assembly yield. Typically a peak to peak voltage ( $V_{pp}$ ) between 2V/µm to 5V/µm has been used for optimal yield.

Frequency of the applied AC voltage plays a crucial role during DEP assembly of SWNTs.<sup>59, 101, 103, 108</sup> From DEP equation it is seen that the DEP force depends on the Clausius-Mossotti (CM) factor, which depends on the frequency. Dependence of real part of CM factor as a function of frequency for both metallic and semiconducting SWNTs is shown in Fig. 7 (a).<sup>56</sup> It can be seen here that for a particular solvent at a particular frequency the CM factor is higher for m-SWNTs than s-SWNTs and therefore the m-SWNTs experience greater DEP force. It can also be seen that the DEP force is higher at low frequency and is smaller at very high frequency. However, at low frequency the DEP assembly is strongly opposed by the surface charge induced zeta-potential (Fig. 7(b)) giving low assembly yield.<sup>47, 116, 117</sup> At high frequency the zeta-potential

diminishes and a higher DEP assembly yield is obtained. Highest assembly yield for individual SWNTs are typically observed at frequency between 1-10 MHz.<sup>38-40</sup> The effect of frequency on the DEP deposition yield is shown in Fig. 7 (c) – (f).<sup>103</sup>

DEP assembly of the SWNTs greatly depends on the concentration of SWNTs in the solution. By varying the concentration of SWNTs in the suspending medium, it is possible to vary the number of SWNTs in the channel. Figure 7(g)-(h) presents the effect of solution concentration on the DEP assembly of SWNT.<sup>85</sup> In this case, the applied voltage, the frequency and the assembly time was kept fixed. A lot of SWNT assembled in the channel when a high solution concentration is used. By systematically reducing the solution concentration, individual SWNTs can be assembled in the channel.<sup>85, 109</sup> It is important to note that the solution concentration and DEP time are interrelated.<sup>118</sup> The density of SWNTs in the channel can also be varied to some extend by varying the DEP time while keeping the solution concentration fixed. For a particular solution concentration the SWNT density increases with the increase of DEP time. By keeping one of them fixed and varying the other parameter it is possible to control the number of SWNTs in the channel.<sup>92, 119</sup>

The dielectric oxide thickness and substrate conductivity also play an important role for the DEP assembly of SWNT.<sup>100, 102</sup> In particular, during simultaneous deposition method, the SWNT assembly yield is greatly influenced by the SiO<sub>2</sub> thickness.<sup>102</sup> For a particular areal size of the electrodes, the capacitance between the drain electrode and gate electrode is inversely proportional to the thickness of SiO<sub>2</sub>. By optimizing the gate oxide thickness it is possible to obtain an optimum capacitive coupling which can provide a high deposition yield. For example, using a 800nm SiO<sub>2</sub> layer, it was shown by Vijayaraghavan et al. that an assembly yield of up to 90% <sup>38</sup> is possible whereas 250 nm SiO<sub>2</sub> gives only ~ 25%.<sup>40, 92, 94</sup>

For a particular type of SWNTs solution and electrode pattern the DEP parameters can be optimized for high yield assembly of individual SWNTs. Changing the SWNTs solution or electrode geometry requires re-optimization of DEP parameters for the new design. Since different groups use different kinds of SWNT solutions, surfactants, substrates and electrode patterns, the optimized parameters are not universal and are different for each group. However, once the parameters are optimized for a particular design, it will consistently give a similar device yield.

# 6. ELECTRONIC TRANSPORT PROPERTIES OF DEP ASSSEMBLED INDIVIDUAL SWNTS

We have already discussed that DEP offers a promising technique for the scalable and parallel fabrication of individual SWNT for device application. However, a common question is that whether solution processing techniques introduces defects in the SWNTs and degrades the intrinsic electrical properties of SWNTs which can limit their application in nanoelectronic devices? The properties of the DEP assembled devices can be evaluated from the electron transport measurements and several research groups have directed their research efforts towards that.<sup>38-40, 85, 91-94, 120</sup> In this section, we will present an overview of the electrical transport properties of the DEP assembled individual SWNT devices.

#### 6.1 Properties of individual SWNT devices assembled from mixed SWNT solution

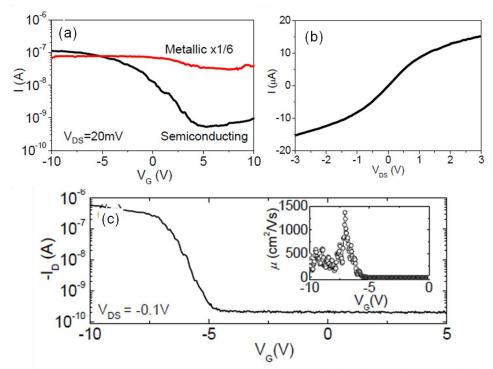

When as synthesized SWNTs are used for making stable solution, it contains both metallic and semiconducting SWNTs (mixed SWNTs solution). As a result, the DEP assembled individual SWNTs devices also contain either metallic or semiconducting SWNT in the channel. Typically, the mixed solution has about 2/3 s-SWNTs and 1/3 m-SWNTs.<sup>121, 122</sup> However, after the DEP assembly it was found that more than 50% of the devices are metallic while the rest are semiconducting.<sup>38-40, 78, 79</sup> The higher yields for metallic devices are attributed to larger DEP force experienced by m-SWNTs. The device properties are typically measured in a three terminal geometry with highly doped Si/SiO<sub>2</sub> substrate working as a gate. Figure 8 (a) shows the drain current (*I*) plotted as a function of back gate voltage ( $V_{BG}$ ) of a representative metallic and semiconducting device for a fixed source drain voltage ( $V_{DS}$ ).<sup>60</sup> As expected, the metallic nanotubes (m-SWNTs) show a weak modulation or no modulation in *I* as a function of  $V_{BG}$ , whereas semiconducting nanotubes (s-SWNTs) show several orders of magnitude change in *I* as a function of  $V_{BG}$ .

High quality contact is one of the major requirements for nanoscale device fabrication. It was found that the two-terminal contact resistances of as assembled SWNTs devices shows a wide ranges variation from a few K $\Omega$  to a few hundred M $\Omega$ . The high contact resistance has

**Fig. 8** (a) Drain current (*I*) versus gate voltage ( $V_G$ ) characteristics for semiconducting and metallic devices. (b) High bias *I*- $V_{DS}$  characteristic for a low contact resistance device showing saturation current of ~15 µA. Reproduced with permission from [85], P. Stokes et al., *J. Vac. Sci. Technol. B* 28, C6B7 (**2010**). © 2010, American Institute of Physics. (c) Drain current ( $I_D$ ) vs. gate voltage ( $V_G$ ) at  $V_{DS} = -0.1V$  for s-SWNT FET device (with *d*~1.3 nm). Inset: Mobility versus gate voltage showing a peak mobility value of ~1380 cm<sup>2</sup>/Vs. Reproduced with permission from [40], P. Stokes et al., *Appl. Phys. Lett.* 96, 083110 (**2010**). © 2010, American Institute of Physics.

been attributed to the presence of residual surfactant on the SWNT surface which causes poor contact at metal-SWNTs interface.<sup>85, 91, 123</sup> Annealing the SWNTs devices at high temperature (200-250°C) for 1 to 2 hour reduces the contact resistance by 1-2 orders of magnitude by removing the surfactants from the surface of the SWNTs<sup>38-40</sup>. Figure 8(b) shows a plot of *I* versus  $V_{DS}$  up to 3 V for a high quality m-SWNT device giving a saturation current of ~15  $\mu A^{85}$ . This is similar to a CVD grown m-SWNT with Ohmic contact, demonstrating that a high quality contact can be achieved from DEP assembled metallic devices.<sup>124</sup>

s-SWNTs devices also show large variation in device performance such as current on-off ratio and mobility. However, high mobility DEP assembled devices has also been demonstrated whose performance is similar to high quality CVD grown s-SWNTs device. Figure 8(c) shows transfer characteristics (drain current,  $I_D$  plotted as a function of  $V_{BG}$ ) of a high quality DEP assembled individual s-SWNTs device at  $V_{DS} = -0.1 \text{ V}^{.40}$  The device shows p-type FET behavior with a high current on/off ratio (~  $3 \times 10^4$ ), a high on state conductance ( $G_{on}=I_{on}/V_{DS}$ ) ~ 6  $\mu$ S together with a transconductance of 1.15  $\mu$ S which are close to the performance achieved by high quality back gated CVD grown SWNT devices.<sup>125</sup> Mobility, of the device was calculated from the transfer characteristics curve using the relation  $\mu = (L^2/C_G \times V_{DS}) (dI_{DS}/dV_G)$ , where L is the channel length and  $C_G = (2\pi\epsilon L)/ln(1+2t_{ox}/r)$  is the gate capacitance, where  $\varepsilon \sim 3.9\varepsilon_0$  is the effective dielectric constant of SiO<sub>2</sub>, h is the thickness of the oxide, and r is the radius of the s-SWNTs.<sup>124</sup> The device (with r = 0.65 nm) gives a peak mobility of  $\mu \sim 1380$  cm<sup>2</sup>/Vs (inset of Fig. 8(c)), which is close to the value obtained from theoretical approximation<sup>125, 126</sup> suggesting that high quality, defect free SWNTs devices can be fabricated using DEP.

The use of mixed solution for assembly possesses a severe limitation in transistor yield. Since m-SWNTs feels a greater DEP force then s-SWNTs, more than half of the assembled SWNTs are metallic when mixed SWNT solution is used for the DEP assembly. This reduces the overall FET yield, as only s-SWNTs can function as FET. This problem can be solved by using all s-SWNT solution during DEP assembly. In the next subsection we will discuss the electron transport properties of DEP assembled devices from semiconducting rich SWNTs solution.

# 6.2 Properties of individual SWNT devices assembled from semiconducting rich SWNT solution

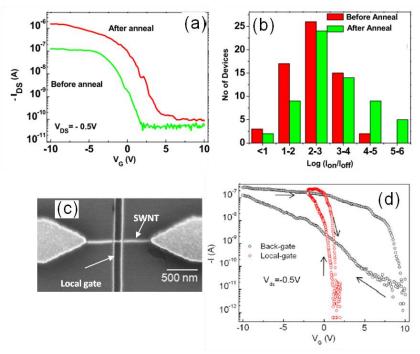

Recently, solution based sorting techniques have been developed to separate SWNTs by their electronic type (chirality) <sup>37, 88-90</sup> which opens up an opportunity for the DEP assembly of semiconducting rich SWNT in order to obtain higher FET yield. Krupke group and Khondaker group independently studied the DEP assembly of s-SWNTs using s-SWNTs aqueous solution of 99% purity obtained by the density gradient ultracentrifugation technique.<sup>91, 92, 94</sup> It was found that the assembly yield for individual s-SWNTs is 20-30%. Figure 9(a) show transfer characteristics of such an individual s-SWNTs device.<sup>92</sup> The device shows p-type FET behavior with a high current on/off ratio ( $I_{on}/I_{off}$ ) ~ 10<sup>5</sup>. The current on/off ratio ( $I_{on}/I_{off}$ ) histogram of 63 such individual s-SWNT devices are shown in Fig. 9(b).<sup>92</sup> The most important point of this figure is that about 97% of the devices show  $I_{on}/I_{off} > 10^{-39, 94}$  implying a 97% FET yield. However, a device-to-device variation in the FET performance is also observed for those devices. Such variations may be explained by the differences of chirality and diameter from tube

**Fig. 9** (a) Transfer characteristics of a representative individual SWNT FET device before and after annealing. (b) Histogram of  $I_{on}/I_{off}$  for individual s-SWNT devices using all semiconducting SWNT solution before and after annealing. Reproduced with permission from [92], M. Islam et al., *Nanotechnology* 23, 125201 (**2012**). © 2012, IOP Publishing Ltd. (c) SEM image of a local gated device based on an individual s-SWNT.(d) Comparison of back-gated and local-gated transfer characteristics. The local gate shows much faster switching behavior and reduced hysteresis compared to the back gate. Reproduced with permission from [94], K. J. Kormondy et al., *Nanotechnology* 22, 415201 (**2011**). © 2011, IOP Publishing Ltd.

to tube which affect the band-gap and contact resistance of the s-SWNT, and in turn the mobility and on/off current ratio of the devices.<sup>95, 125, 127, 128</sup>

Figure 9(a) also show that it takes about 5 V to switch from on state to off state giving a subthreshold swing (S) of 1200 mV/dec. The high subthreshold swing is attributed to the thick SiO<sub>2</sub> gate oxide (250 nm). However, small S (~60mV/dec) are preferred in FETs for low power consumption and high speed operation<sup>7</sup>. Most of the DEP assembled back gated devices have S ~1000-2000 mV/dec,<sup>91.94</sup> which are too large for logic operation and far from their maximum capability. For SWNT FET the subthreshold swing is given by, S=(2.303KT/q)(1+C<sub>IT</sub>/C<sub>G</sub>).<sup>129, 130</sup> Where, C<sub>G</sub> is the gate oxide capacitance and C<sub>IT</sub> is the capacitance due to interface trap charges. The subthreshold swing along with the hysteresis can be improved by employing local gated device geometry with a thin gate oxide. Khondaker group demonstrated a local gated at the middle of the channel between the source and drain electrodes, shown in Fig. 9(c).<sup>107</sup> Figure 9(d) presents a comparison of transfer characteristics between the local-gate and back-gate for a s-SWNTs device.<sup>94</sup>. The back-gated device shows a significantly reduced S ~

200 mV/dec and hysteresis of ~ 1 V. S values as low as 140 mV/dec had been reported, which is comparable to those for the CVD-grown  $Al_2O_3$  gated devices.<sup>131, 132</sup> The faster switching behavior with the local gated device can be mainly attributed to the much thinner  $Al_2O_3$  layer (~2–3 nm) compared to the thick layer of SiO<sub>2</sub> (250 nm). Besides, the reduced hysteresis observed in local gated device is a consequence of less interface traps at the SWNT/local gate oxide interface<sup>133-135</sup> which also helps reducing S.

#### 6.3 Towards high yield fabrication of all SWNT FET devices via DEP

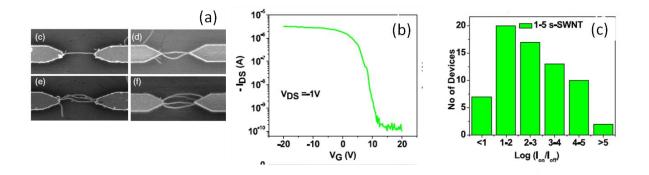

Even though 97% of the devices show FET when high purity s-SWNTs solution was used, the low assembly yield for individual s-SWNTs (~20-30%) reduces the overall device fabrication yield. The DEP assembly yield can be increased to 90% if the assembly condition is optimized such that in addition to individual SWNT, 2-5 SWNTs are allowed to connect per electrode pair (Fig 10 (a)). Electron transport study shows that the devices having 2-5 s-SWNTs also shows good FET behavior. For example, Figure 10(b) shows the transport characteristics of a device with 2-SWNTs in the channel.<sup>92</sup> It gives p-type FET behavior with a current on-off ratio ~  $2 \times 10^4$  and an on-conductance of 3.4 µS with a mobility of 126 cm<sup>2</sup>/Vs. The mobility was  $(L/WC_iV_{DS})(dI_{DS}/dV_G),$ calculated using the formula  $\mu =$  $C_i = D/[C_0]$ with  $^{1}+(1/2\pi\epsilon)\ln[\sinh(2\pi t_{ox}D)/\pi Dr]]$ , where D is the linear density of the SWNT, W is the channel width, and C<sub>i</sub> is the specific capacitance per unit area of aligned array with  $C_0 (=4 \times 10^{-10} \text{ Fm}^{-1})^{45}$ . For this calculation L=1  $\mu$ m was used while an upper limit of W=0.25  $\mu$ m for 2 SWNT was determined from SEM image giving D=8.<sup>80</sup> Statistics for the  $I_{on}/I_{off}$  of the devices made from 1-5 SWNTs are shown in Fig. 10(c).<sup>92</sup> It shows that 90% of such devices show FET behavior. Using such a scheme, an assembly yield of  $90\%^{80, 86}$  with an overall FET yield of 90% had been demonstrated.<sup>92</sup> This is in contrast to the mixed s-SWNT solution where the assembly of more than one SWNT per site significantly increases the chance of getting at least one m-SWNTs per site resulting in metallic behavior of the device. A FET yield of 90% with an assembly yield of

**Fig. 10:** Local view of the SEM images of the devices containing (a) one, two, three, and four s-SWNTs between the electrodes. Separation between the source and drain electrode is 1 $\mu$ m. (b) Transfer characteristics of a FET device with two s-SWNTs. (c) Histogram of the I<sub>on</sub>/I<sub>off</sub> for all devices with one to five s-SWNTs. Reproduced with permission from [92], M. Islam et al., *Nanotechnology* 23, 125201 (**2012**). © 2012, IOP Publishing Ltd.

90% obtained by DEP is by far the best for any type of device assembly technique<sup>92</sup>.

# 7. CONCLUSION AND FUTURE OUTLOOK

In conclusion, we presented an overview on the DEP assembly of individual SWNTs towards the realization of scaled up fabrication of SWNTs devices for practical applications. We have discussed the theory of DEP, presented a historic overview with an emphasis on the recent progress on the DEP assembly of individual SWNTs devices, and discussed the electronic transport properties of the fabricated devices. From these discussions, it is clear that the DEP assembly of SWNTs has made tremendous progress during the last two decades. With continuous progress in solution processing, it is now possible to obtain high quality and catalytic particle free stable SWNTs solution that are chirally sorted. High performance DEP assembled SWNT devices has also been demonstrated. With semiconducting rich SWNTs, a 90% transistor yield with 90% assembly yield has become a reality.

While significant progress has been made, there still exists a number of scientific and technical challenges that need to be addressed for wide scale application of the SWNT based devices. One of them is a large device-to-device performance variation (contact resistance, mobility, on-off ratio) in the DEP assembled SWNT devices. Even though the technique has been developed to separate metallic and semiconducting SWNTs, the wide range of variation in the diameter of SWNT, causes individual SWNTs based devices to show variation in their performance such as mobility and current on-off ratio. Very recently, effective technique had been developed demonstrating narrow distribution of diameters and chirality of SWNTs<sup>136, 137</sup> which could facilitate more homogeneous device performance and the future effort should be directed in the DEP assembly of uniformly mono-dispersed SWNTs for device application. In addition, techniques need to be developed to improve the contact resistance of the DEP assembled SWNTs. Contact resistance also depends on the diameter of the nanotube as well as the surfactant used for the processing. Improving the diameter distribution will also help reduce the contact resistance inhomogeneity. Large-scale assembly of ultra short (sub-100 nm) SWNTs has not been demonstrated yet, which is necessary for device scaling. Besides, complex device structures such as inverter or logic circuits also need to be demonstrated using DEP. Addressing these challenges along with the progress already made will allow parallel fabrication of CMOS compatible individual SWNT devices for future nanoelectronic application.

Acknowledgement: The authors acknowledge financial support from U.S. National Science Foundation under Grant No. ECCS-0748091 (CAREER)

# References

1. P. L. McEuen; Nanotechnology - Carbon-based electronics; *Nature* 393, 15 (**1998**).

2. P. Avouris, Z. Chen, and V. Perebeinos; Carbon-based electronics; *Nature Nanotechnol.* 2, 605 (**2007**).

3. H. Dai; Carbon nanotubes: Synthesis, integration, and properties; *Acc.Chem. Res.* 35, 1035 (2002).

4. R. H. Baughman, A. A. Zakhidov, and W. A. de Heer; Carbon nanotubes - the route toward applications; *Science* 297, 787 (**2002**).

5. S. J. Tans, A. R. M. Verschueren, and C. Dekker; Room-temperature transistor based on a single carbon nanotube; *Nature* 393, 49 (**1998**).

6. R. Martel, T. Schmidt, H. R. Shea, T. Hertel, and P. Avouris; Single- and multi-wall carbon nanotube field-effect transistors; *Appl.Phys.Lett.* 73, 2447 (**1998**).

7. A. Javey, H. Kim, M. Brink, Q. Wang, A. Ural, J. Guo, P. McIntyre, P. McEuen, M. Lundstrom, H. Dai; High-kappa dielectrics for advanced carbon-nanotube transistors and logic gates; *Nature Materials* 1, 241, (**2002**).

8. A. Javey, J. Guo, Q. Wang, M. Lundstrom, and H. Dai; Ballistic carbon nanotube field-effect transistors; *Nature* 424, 654 (**2003**).

9. T. Durkop, S. A. Getty, E. Cobas, and M. S. Fuhrer; Extraordinary mobility in semiconducting carbon nanotubes; *Nano Lett.* 4, 35 (**2004**).

10. S. Frank, P. Poncharal, Z. L. Wang, and W. A.de Heer; Carbon nanotube quantum resistors; *Science* 280, 1744 (**1998**).

11. J. Kong, N. R. Franklin, C. W. Zhou, M. G. Chapline, S. Peng, K. J. Cho, H. Dai; Nanotube molecular wires as chemical sensors; *Science* 287, 622 (**2000**).

12. A. Modi, N. Koratkar, E. Lass, B. Q. Wei, and P. M. Ajayan; Miniaturized gas ionization sensors using carbon nanotubes; *Nature* 424, 171 (**2003**).

13. T. Rueckes, K. Kim, E. Joselevich, G. Y. Tseng, C. L. Cheung, and C. M. Lieber; Carbon nanotube-based nonvolatile random access memory for molecular computing; *Science* 289, 94 (**2000**).

14. A. Kongkanand, R. M. Dominguez, and P. V. Kamat; Single wall carbon nanotube scaffolds for photoelectrochemical solar cells capture and transport of photogenerated electrons; *Nano Lett.* 7, 676 (**2007**).

15. M. W. Rowell, M. A. Topinka, M. D. McGehee, H. J. Prall, G. Dennler, N.S. Sariciftci, L. Hu, and G.Gruner; Organic solar cells with carbon nanotube network electrodes; *Appl. Phys. Lett.* 88, 233506 (**2006**).

16. B. K. Sarker, J. Liu, L. Zhai, and S. I. Khondaker; Fabrication of organic field effect transistor by directly grown poly(3 hexylthiophene) crystalline nanowires on carbon nanotube aligned array electrode; *ACS Appl. Mater.Interfaces* 3, 1180 (**2011**).

17. B. K. Sarker, and S. I. Khondaker; High-performance short channel organic transistors using densely aligned carbon nanotube array electrodes; *Appl. Phys. Lett.* 100, 023301 (**2012**).

18. C. M. Aguirre, C. Ternon, M. Paillet, P. Desjardins, and R. Martel; Carbon nanotubes as injection electrodes for organic thin film transistors; *Nano Lett.* 9, 1457 (**2009**).

19. J. Kong, H. T. Soh, A. M. Cassell, C. F. Quate, and H. Dai; Synthesis of individual single-walled carbon nanotubes on patterned silicon wafers; *Nature* 395, 878 (**1998**).

20. Y. C. Tseng, P. Q. Xuan, A. Javey, R. Malloy, Q. Wang, J. Bokor, and H.Dai; Monolithic integration of carbon nanotube devices with silicon MOS technology; *Nano Lett.* 4, 123 (**2004**).

21. A. Javey, Q. Wang, A. Ural, Y. M. Li, and H. Dai; Carbon nanotube transistor arrays for multistage complementary logic and ring oscillators; *Nano Lett.* 2, 929 (**2002**).

22. B. Zheng, C. G. Lu, G. Gu, A. Makarovski, G. Finkelstein, and J. Liu; Efficient CVD growth of single-walled carbon nanotubes on surfaces using carbon monoxide precursor; *Nano Lett.* 2, 895 (2002).

23. S. J. Kang, C.; Kocabas, T. Ozel, M. Shim, N. Pimparkar, M. A. Alam, S.V. Rotkin, and J. A. Rogers; High-performance electronics using dense, perfectly aligned arrays of single-walled carbon nanotubes; *Nature Nanotechnol.* 2, 230 (**2007**).

24. S. J.Tans, M. H. Devoret, H. Dai, A. Thess, R. E.Smalley, L. J. Geerligs, and C.Dekker; Individual single-wall carbon nanotubes as quantum wires; *Nature* 386, 474 (**1997**).

25. M. Bockrath, D. H.Cobden, J. Lu, A. G. Rinzler, R. E. Smalley, L. Balents, and P. L. McEuen; Luttinger-liquid behaviour in carbon nanotubes; *Nature* 397, 598 (**1999**).

26. J. Nygard, D. H. Cobden, and P. E. Lindelof; Kondo physics in carbon nanotubes; *Nature* 408, 342 (**2000**).

27. W. J. Liang, M. Bockrath, D. Bozovic, J. H. Hafner, M. Tinkham, and H. Park; Fabry-Perot interference in a nanotube electron waveguide; *Nature* 411, 665 (**2001**).

28. M. Kociak, A. Y. Kasumov, S. Gueron, B. Reulet, II. Khodos, Y. B. Gorbatov, V. T. Volkov, L. Vaccarini, and H. Bouchiat; Superconductivity in ropes of single-walled carbon nanotubes; *Phys. Rev. Lett.* 86, 2416 (**2001**).

29. A. M. Cassell, J. A. Raymakers, J. Kong, and H. Dai; Large scale CVD synthesis of single-walled carbon nanotubes; *J. Phys. Chem. B* 103, 6484 (**1999**).

30. S. Auvray, V. Derycke, M. Goffman, A. Filoramo, O.Jost, and J. P. Bourgoin; Chemical optimization of self-assembled carbon nanotube transistors; *Nano Lett.* 5, 451 (**2005**).

31. K. Keren, R. S. Berman, E. Buchstab, U. Sivan, and E. Braun; DNA-templated carbon nanotube field-effect transistor; *Science*, 302, 1380 (**2003**).

32. G. Yu, A. Cao, and C. M. Lieber; Large-area blown bubble films of aligned nanowires and carbon nanotubes; *Nature Nanotechnol.* 2, 372 (**2007**).

33. X. Li, L. Zhang, X. Wang, I. Shimoyama, X. Sun, W. S. Seo, and H. Dai; Langmuir-Blodgett assembly of densely aligned single-walled carbon nanotubes from bulk materials; *J. Am. Chem. Soc.* 129, 4890 (**2008**).

34. S. Jin, D. M. Whang, M.C. McAlpine, R. S. Friedman, Y. Wu, and C. M. Lieber; Scalable interconnection and integration of nanowire devices without registration; *Nano Lett.*, 4, 915 (**2004**).

35. K. Kordas, T. Mustonen, G. Toth, H. Jantunen, M. Lajunen, C. Soldano, S. Talapatra, S. Kar, R. Vajtai, and P. M. Ajayan, Inkjet printing of electrically conductive patterns of carbon nanotubes; *Small* 2, 1021 (**2006**).

36. M. Engel, J. P. Small, M. Steiner, M. Freitag, A. A. Green, and M. C. Hersam, and P. Avouris; Thin Film Nanotube Transistors Based on Self-Assembled, Aligned, Semiconducting Carbon Nanotube Arrays; *ACS Nano* 2, 2445 (**2008**).

37. M. C. LeMieux, M. Roberts, S. Barman, Y. W. Jin, J. M. Kim, and Z. Bao; Self-sorted, aligned nanotube networks for thin-film transistors; *Science* 321, 101 (**2008**).

38. A. Vijayaraghavan, S. Blatt, D. Weissenberger, M. Oron-Carl, F.Hennrich, D. Gerthsen, H. Hahn, and R. Krupke; Ultra-large-scale directed assembly of single-walled carbon nanotube devices; *Nano Lett.* 7, 1556 (**2007**).

39. B. R. Burg, J. Schneider, M. Muoth, L. Durrer, T. Helbling, N. C.Schirmer, T. Schwamb, C. Hierold, and D. Poulikakos; Aqueous Dispersion and Dielectrophoretic Assembly of Individual Surface-Synthesized Single-Walled Carbon Nanotubes; *Langmuir* 25, 7778 (**2009**).

40. P. Stokes, and S. I. Khondaker, High quality solution processed carbon nanotube transistors assembled by dielectrophoresis; *Appl. Phys. Lett.* 96, 083110 (**2010**).

41. S. I. Khondaker, K. Luo, and Z. Yao; The fabrication of single-electron transistors using dielectrophoretic trapping of individual gold nanoparticles; *Nanotechnology* 21, 095204 (**2010**).

42. M. R. Islam, D. Joung, and S. I. Khondaker; Schottky diode via dielectrophoretic assembly of reduced graphene oxide sheets between dissimilar metal contacts; *New J. Phys.* 13, 035021 (**2011**).

43. D. Joung, A. Chunder, L. Zhai, and S. I. Khondaker; High yield fabrication of chemically reduced graphene oxide field effect transistors by dielectrophoresis; *Nanotechnology* 21, 165202 (**2010**).

44. D. Joung, and S. I. Khondaker; Efros-Shklovskii variable range hopping in reduced graphene oxide sheets of varying carbon sp2 fraction; Phys. *Rev. B* 86, 235423 (**2012**).

45. S. I. Khondaker; Fabrication of nanoscale device using individual colloidal gold nanoparticle; *IEE proceedings: circuits, devices and systems* 151, 457 (**2004**).

46. S. Shekhar, P. Stokes, and S. I. Khondaker; Ultrahigh Density Alignment of Carbon Nanotube Arrays by Dielectrophoresis; *ACS Nano* 5, 1739 (**2011**).

47. B. K. Sarker, S. Shekhar, and S. I. Khondaker; Semiconducting enriched carbon nanotube aligned arrays of tunable density and their electrical transport properties; *ACS Nano* 5, 6297 (2011).

48. R. Krupke, S. Linden, M. Rapp, and F.Hennrich; Thin films of metallic carbon nanotubes prepared by dielectrophoresis; *Adv.Mater.* 18, 1468 (**2006**).

49. L. Nougaret, H. Happy, G. Dambrine, V. Derycke, J. -P. Bourgoin, A. A. Green and M. C. Hersam; *Appl. Phys. Lett.* 94, 243505 (**2009**).

50. M. Steiner, M. Engel, Y. Lin, Y. Wu, K. Jenkins, D. B. Farmer, J. J. Humes, N. L. Yoder, J.T. Seo, A. A. Green, M. C. Hersam, R. Krupke and P. Avouris; *Appl. Phys. Lett.* 101, 053123 (**2012**).

51. L. Hu, D. S. Hecht, and G. Gruener; Carbon Nanotube Thin Films: Fabrication, Properties, and Applications; *Chemical Reviews* 110, 5790 (**2010**).

52. Q. Cao, and J. A. Rogers; Random Networks and Aligned Arrays of Single-Walled Carbon Nanotubes for Electronic Device Applications; *Nano Res.* 1, 259 (**2008**).

53. N. Rouhi, D. Jain, P. J. Burke; High-Performance Semiconducting Nanotube Inks: Progress and Prospects; *Acs Nano* 5, 8471 (**2011**).

54. H. A. Pohl; Dielectrophoresis; Cambridge University Press, New York, (1978).

55. T. B. Jones; Electromechanics of Particles; Cambridge University Press, New York, (1995).

56. H. Morgan, N. G. Green; AC Electrokinetics: colloids and nanoparticles; Research Studies Press Ltd, Hertfordshire (**2003**).

57. H. A. Pohl; The motion and precipitation of suspensoids in divergent electric fields, *J. Appl.Phys.* 22, 869 (**1951**).

58. M. Dimaki, and P. Boggild; Dielectrophoresis of carbon nanotubes using microelectrodes: a numerical study; *Nanotechnology* 15, 1095 (**2004**).

59. R. Krupke, F. Hennrich, M. M. Kappes, and H. V. Lohneysen; Surface conductance induced dielectrophoresis of semiconducting single-walled carbon nanotubes; *Nano Lett.* 4, 1395 (2004).

60. S. Blatt, F. Hennrich, H. von Lohneysen, M. M. Kappes, A. Vijayaraghavan, and R. Krupke; Influence of structural and dielectric anisotropy on the dielectrophoresis of single-walled carbon nanotubes; *Nano Lett.* 7, 1960 (**2007**).

61. K. Yamamoto, S. Akita, and Y. Nakayama; Orientation of carbon nanotubes using electrophoresis; *Japanese J. Appl. Phys.* 35, L917 (**1996**).

62. K. Yamamoto, S. Akita, and Y. Nakayama; Orientation and purification of carbon nanotubes using ac electrophoresis; *J. Phys. D-Appl. Phys.* 31, L34 (**1998**).

63. X. Q. Chen, T. Saito, H. Yamada, K. Matsushige; Aligning single-wall carbon nanotubes with an alternating-current electric field; *Appl.Phys. Lett.* 78, 3714 (**2001**).

64. B. Vigolo, A. Penicaud, C. Coulon, C. Sauder, R. Pailler, C. Journet, P. Bernier, and P. Poulin; Macroscopic fibers and ribbons of oriented carbon nanotubes; *Science* 290, 1331(**2000**).

65. R. Krupke, F. Hennrich, H. B. Weber, M. M. Kappes, and H. von Lohneysen; Simultaneous deposition of metallic bundles of single-walled carbon nanotubes using acdielectrophoresis; *Nano Lett.* 3, 1019 (**2003**).

66. R. Krupke, F. Hennrich, H. B. Weber, D. Beckmann, O. Hampe, S.Malik, M. M. Kappes, and H. V. Lohneysen; Contacting single bundles of carbon nanotubes with alternating electric fields; *Appl. Phys. A-Mater. Sci. Proces.* 76, 397 (**2003**).

67. J. Q. Li, Q. Zhang, D. J. Yang, and J. Z. Tian; Fabrication of carbon nanotube field effect transistors by AC dielectrophoresis method; *Carbon* 42, 2263 (**2004**).

68. Z. Chen, Y. L. Yang, F. Chen, Q. Qing, Z. Y. Wu, and Z. F. Liu; Controllable interconnection of single-walled carbon nanotubes under AC electric field; *J. Phys. Chem. B* 109, 11420 (**2005**).

69. H. W. Seo, C. S.Han, D. G.Choi, K. S. Kim, and Y. H. Lee; Controlled assembly of single SWNTs bundle using dielectrophoresis; *Mic. Engr.* 81, 83 (**2005**).

70. M. J. O'Connell, P. Boul, L. M. Ericson, C. Huffman, Y. H. Wang, E. Haroz, C. Kuper, J. Tour, K. D. Ausman, and R. E.Smalley; Reversible water-solubilization of single-walled carbon nanotubes by polymer wrapping; *Chem. Phys. Lett.* 342, 265 (**2001**).

71. M. J. O'Connell, S. M. Bachilo, C. B. Huffman, V. C. Moore, M. S. Strano, E. H. Haroz, K. L. Rialon, P. J. Boul, W. H. Noon, C. Kittrell, J. P. Ma, R. H. Hauge, R. B. Weisman, and R. E. Smalley; Band gap fluorescence from individual single-walled carbon nanotubes; *Science* 297, 593 (**2002**).

72. S. M. Bachilo, M. S. Strano, C. Kittrell, R. H. Hauge, R. E. Smalley, and R. B. Weisman; Structure-assigned optical spectra of single-walled carbon nanotubes, *Science* 298, 2361 (**2002**).

73. V. C. Moore, M. S. Strano, E. H. Haroz, R. H.; Hauge, R. E. Smalley, J. Schmidt, and Y. Talmon; Individually suspended single-walled carbon nanotubes in various surfactants; *Nano Lett.* 3, 1379 (**2003**).

74. O. Matarredona, H.Rhoads, Z. R. Li, J. H. Harwell, L. Balzano, and D. E. Resasco; Dispersion of single-walled carbon nanotubes in aqueous solutions of the anionic surfactant NaDDBS; *J. Phys. Chem. B* 107, 13357 (**2003**).

75. M. F. Islam, E. Rojas, D. M. Bergey, A. T Johnson, and A. G.Yodh; High weight fraction surfactant solubilization of single-wall carbon nanotubes in water; *Nano Lett.* 3, 269 (**2003**).

76. Z. B. Zhang, J. Cardenas, E. E. B. Campbell, and S. L. Zhang; Reversible surface functionalization of carbon nanotubes for fabrication of field-effect transistors; *Appl. Phys. Lett.* 87, 043110 (**2005**).

77. Z. B. Zhang, X. J Liu, E. E. B. Campbell, and S. L. Zhang; Alternating current dielectrophoresis of carbon nanotubes; *J. Appl. Phys.* 98, 056103 (**2005**).

78. L. F. Dong, V. Chirayos, J.Bush, J. Jiao, V. M. Dubin, R. V. Chebian, Y. Ono, J. F. Conley, and B. D. Ulrich; Floating-potential dielectrophoresis-controlled fabrication of single-carbon-nanotube transistors and their electrical properties; *J. Phys. Chem. B* 109, 13148 (**2005**).

79. S. Banerjee, B. E. White, L. M. Huang, B. J. Rego, S. O'Brien, and I. P. Herman; Precise positioning of single-walled carbon nanotubes by ac dielectrophoresis; *J.Vac. Sci. Technol. B* 24, 3173 (**2006**,).

80. S. Banerjee, B.White, L. Huang, B. J. Rego, S. O'Brien, and I. P.Herman; Precise positioning of carbon nanotubes by ac dielectrophoresis using floating posts; *Appl. Phys.A-Mater. Sci. Processing* 86, 415 (**2007**).

81. M. C. Hersam; Progress towards monodisperse single-walled carbon nanotubes; *Nature Nanotechnol.* 3, 387 (**2008**).

82. A. Nish, J. Y. Hwang, J. Doig, and R. J. Nicholas; Highly selective dispersion of single walled carbon nanotubes using aromatic polymers; *Nature Nanotechnol.* 2, 640 (**2007**).

83. https://www.berewerscience.com.

84. https://www.nanointegris.com.

60. P. Stokes, and S. I. Khondaker; Directed assembly of solution processed single-walled carbon nanotubes via dielectrophoresis: From aligned array to individual nanotube devices; *J. Vac.Sci. Technol. B* 28, C6B7 (**2010**).

86. P. Stokes, E. Silbar, Y. M. Zayas, S. I. Khondaker; Solution processed large area field effect transistors from dielectrophoreticly aligned arrays of carbon nanotubes; *Appl. Phys. Lett.* 94, 113104 (**2009**).

87. P. Stokes, and S. I. Khondaker; Evaluating defects in solution-processed carbon nanotube devices via low-temperature transport spectroscopy; *ACS Nano* 4, 2659 (**2010**).

88. M. S. Arnold, A. A. Green, J. F. Hulvat, S. I. Stupp, and M. C. Hersam; Sorting carbon nanotubes by electronic structure using density differentiation; *Nature Nanotechnol.* 1, 60 (2006).

89. M. S. Arnold, S. I. Stupp, and M. C. Hersam; Enrichment of single-walled carbon nanotubes by diameter in density gradients; *Nano Lett.* 5, 713 (**2005**).

90. S. Campidelli, M. Meneghetti, and M. Prato; Separation of metallic and semiconducting single-walled carbon nanotubes via covalent functionatization; *Small* 3, 1672 (**2007**).

91. M. Ganzhorn, A. Vijayaraghavan, A. A. Green, S. Dehm, A.Voigt, M. Rapp, M. C. Hersam, and R. Krupke; A scalable, CMOS-compatible assembly of ambipolar semiconducting single-walled carbon nanotube devices; *Adv. Mater.* 23, 1734 (**2011**).

92. M. R. Islam, K. J. Kormondy, E. Silbar, S. I. Khondaker; A general approach for high yield fabrication of CMOS-compatible all-semiconducting carbon nanotube field effect transistors; *Nanotechnology* 23, 125201 (**2012**).

93. A. Vijayaraghavan, F. Hennrich, N. Sturzl, M. Engel, M. Ganzhorn, M. Oron-Carl, C. W. Marquardt, S. Dehm, S. Lebedkin, M. M. Kappes, and R. Krupke; Toward single-chirality carbon nanotube device arrays; *ACS Nano* 4, 2748 (2010).

94. K. J. Kormondy, P. Stokes, and S. I. Khondaker; High yield assembly and electron transport investigation of semiconducting-rich local-gated single-walled carbon nanotube field effect transistors; *Nanotechnology* 22, 415201 (**2011**).

95. Z. H. Chen, J. Appenzeller, J. Knoch, Y. M. Lin, and P. Avouris; The role of metalnanotube contact in the performance of carbon nanotube field-effect transistors; *Nano Lett.*5, 1497 (**2005**).

96. D. Mann, A. Javey, J. Kong, Q. Wang, H. Dai; Ballistic transport in metallic nanotubes with reliable Pd ohmic contacts; *Nano Lett.* 3, 1541 (**2003**).

97. A. Javey, J. Guo, M. Paulsson, Q. Wang, D. Mann, M. Lundstrom, and H. Dai; High-field quasiballistic transport in short carbon nanotubes; *Phys. Rev. Lett.* 92, 106804 (**2004**).

98. J. Y. Chung, K. H. Lee, J. H.; Lee, and R. S. Ruoff; Toward large-scale integration of carbon nanotubes; *Langmuir* 20, 3011 (**2004**.

99. A. Arun, P. Salet, and A. M. Ionescu; A Study of Deterministic Positioning of Carbon Nanotubes by Dielectrophoresis; *J. Elec.Mater.* 38, 742 (**2009**).

100. M. Duchamp, K. Lee, B. Dwir, J. W. Seo, E. Kapon, L. Forro, and A. Magrez; Controlled Positioning of Carbon Nanotubes by Dielectrophoresis: Insights into the Solvent and Substrate Role; *ACS Nano* 4, 279 (**2010**).

101. M. Dimaki, and P. Boggild; Frequency dependence of the structure and electrical behaviour of carbon nanotube networks assembled by dielectrophoresis; *Nanotechnology* 16, 759 (**2005**).

102. C. W. Marquardt, S. Blatt, F. Hennrich, H. V. Lohneysen and R. Krupke; Probing dielectrophoretic force fields with metallic carbon nanotubes; *Appl. Phys. Lett.* 89, 183117 (2006).

103. B. R. Burg, V. Bianco, J. Schneider, D. Poulikakos; Electrokinetic framework of dielectrophoretic deposition devices; *J. Appl. Phys.* 107, 124308 (*2010*).

104. A. W. Maijenburg, M. G. Maas, E. J. B. Rodijk, W. Ahmed, E. S. Kooij, E. T. Carlen, D. H. A. Blank, J. E.ten Elshof; Dielectrophoretic alignment of metal and metal oxide nanowires and nanotubes: A universal set of parameters for bridging prepatterned microelectrodes; *J.Colloid and Interface Science* 355, 486 (**2011**).

105. D. D. Xu, A. Subramanian, L. Dong, and B. J. Nelson; Shaping nanoelectrodes for highprecision dielectrophoretic assembly of carbon nanotubes; IEEE *Tran. Nanotechnol.* 8, 449 (**2009**).

106. L. An, C. R. Friedrich, Process parameters and their relations for the dielectrophoretic assembly of carbon nanotubes; *J. Appl. Phys.* 105, 014314 (**2009**).

107. A. K. Naieni, and A. Nojeh; Effect of solution conductivity and electrode shape on the deposition of carbon nanotubes from solution using dielectrophoresis; *Nanotechnology* 23, 495606 (**2012**).

108. N. Peng, Q. Zhang, J. Q. Li, and N. Y. Liu; Influences of ac electric field on the spatial distribution of carbon nanotubes formed between electrodes; *J. Appl. Phys.* 100, 024309 (**2006**).

109. P. F. Li, and W. Xue; Selective deposition and alignment of single-walled carbon nanotubes assisted by dielectrophoresis: from thin films to individual nanotubes; *Nanoscale Res. Lett.* 5, 1072 (**2010**).

110. C. W.Zhou, J. Kong, and H. Dai; Intrinsic electrical properties of individual single-walled carbon nanotubes with small band gaps; *Phys. Rev. Lett.* 84, 5604 (**2000**).

111. A. Javey, M. Shim, and H. Dai; Electrical properties and devices of large-diameter single-walled carbon nanotubes; *Appl. Phys. Lett.* 80, 1064 (**2002**).

112. C. W. Zhou, J. Kong, and H. Dai; Electrical measurements of individual semiconducting single-walled carbon nanotubes of various diameters; *Appl. Phys. Lett* 76, 1597 (**2000**).

113. L. X. Benedict, S. G. Louie, and M. L. Cohen; Statistical Polarizibilities of single wall carbon nanotubes; *Phys. Rev. B* 52, 8541 (**1995**).

114. R. Krupke, F. Hennrich, H. von Lohneysen, and M. M. Kappes; Separation of metallic from semiconducting single-walled carbon nanotubes; *Science* 301, 344 (**2003**).

115. M. S. Kumar, T. H. Kim, S. H. Lee, S. M. Song, J. W. Yang, K. S. Nahm, and E. K. Suh; Influence of electric field type on the assembly of single walled carbon nanotubes; *Chem. Phys. Lett.* 383, 235 (**2004**).

116. A. Castellanos A. Ramos, A. Gonzalez, N. G. Green, H. Morgan; Electrohydrodynamics and dielectrophoresis in microsystems: scaling laws; *J. Phys. D-Appl. Phys.* 36, 2584 (**2003**).

117. M. Uppalapati, Y. M. Huang, T. N. Jackson, and W. O. Hancock; Microtubule alignment and manipulation using AC electrokinetics; *Small* 4, 1371 (**2008**).

118. L. B. An, and C. R. Friedrich; Process parameters and their relations for the dielectrophoretic assembly of carbon nanotubes; *J. Appl. Phys.* 105, 074314 (**2009**).

119. A. H. Monica, S. J. Papadakis, R. Osiander, and M. Paranjape; Wafer-level assembly of carbon nanotube networks using dielectrophoresis; *Nanotechnology* 19, 085303 (**2008**).

120. P. Stokes, and S. I. Khondaker; Local-gated single-walled carbon nanotube field effect transistors assembled by AC dielectrophoresis; *Nanotechnology* 19, 175202 (**2008**).

121. M. S. Dresselhaus, G. Dresselhaus, P. Avouris; Carbon Nanotubes: Synthesis, Structure, Properties, and Applications; Springer, New York, (**2001**).

122. M. J. O'Connell; Carbon Nanotubes Properties and Applications; Taylor & Francis, Florida (2006).

123. C. N. R. Rao, A. Govindaraj, F. L. Deepak, N. A. Gunari, and M. Nath; Surfactant-assisted synthesis of semiconductor nanotubes and nanowires; *Appl. Phys. Lett.* 78, 1853 (2001).

124. J. Y. Park, S. Rosenblatt, Y. Yaish, V.; Sazonova, H.; Ustunel, S. Braig, T. A. Arias, P. W. Brouwer, and P. L.; McEuen; Electron-phonon scattering in metallic single-walled carbon nanotubes; *Nano Lett.* 4, 517 (**2004**).

125. X. J. Zhou, J. Y. Park, S. M. Huang, J. Liu, and P. L. McEuen; Band structure, phonon scattering, and the performance limit of single-walled carbon nanotube transistors; *Phys.Rev. Lett.* 95, 146805 (**2005**).

126. M. J. Biercuk, S. Ilani, C. M. Marcus, and P. L. McEuen; Electrical transport in singlewall carbon nanotubes; *Topics Appl. Physics* 111, 455 (**2008**).

127. J. W. G. Wildoer, L. C. Venema, A. G. Rinzler, R. E. Smalley, and C. Dekker; Electronic structure of atomically resolved carbon nanotubes; *Nature* 391, 59 (**1998**).

128. Y. C. Tseng, K. Phoa, D. Carlton, and J. Bokor; Effect of diameter variation in a large set of carbon nanotube transistors; *Nano Lett.* 6, 1364 (**2006**).

129. S. M. SZE; Physics of Semiconductor devices; Wiley, New York (1981).

130. S. Kumar, N. Pimparkar, J. Y. Murthy, and M. A. Alam; Theory of transfer characteristics of nanotube network transistors; *Appl. Phys. Lett.* 88, 123505, (**2006**).

131. Y. M. Lin, J. Appenzeller, J. Knoch, and P.Avouris; High-performance carbon nanotube field-effect transistor with tunable Polarities; *IEEE Tran. Nanotechnol.* 4, 481 (**2005**).

132. S. K. Kim, Y.; Xuan, P. D.; Ye, S. Mohammadi, J. H. Back, and M. Shim; Atomic layer deposited Al<sub>2</sub>O<sub>3</sub> for gate dielectric and passivation layer of single-walled carbon nanotube transistors; *Appl. Phys. Lett.* 90, 163108 (**2007**).

133. R. T. Weitz, U. Zschieschang, F. Effenberger, H. Klauk, M. Burghard, and K. Kern; High-performance carbon nanotube field effect transistors with a thin gate dielectric based on a self-assembled monolayer; *Nano Lett.* 7, 22 (**2007**).

134. W. Kim, A. Javey, O. Vermesh, O. Wang, Y. M. Li, and H. J. Dai; Hysteresis caused by water molecules in carbon nanotube field-effect transistors; *Nano Lett.* 3, 193 (**2003**).

135. S. A. McGill; S. G. Rao, P. Manandhar, P. Xiong, and S. Hong; High-performance, hysteresis-free carbon nanotube field-effect transistors via directed assembly; *Appl. Phys. Lett.* 89, 163123, (**2006**).

136. T. P.Tyler, T. A. Shastry, B. J. Leever, and M. C. Hersam; Narrow diameter Distributions of metallic arc discharge single-walled carbon nanotubes via dual-iteration density gradient ultracentrifugation; *Adv. Mater.* 24, 4765 (**2012**).

137. J. T. Seo, N. L. Yoder, T. A. Shastry, J. J. Humes, J. E. Johns, A. A. Green, and M. C. Hersam; Diameter refinement of semiconducting arc discharge single-walled carbon nanotubes via density gradient ultracentrifugation; *J. Phys. Chem. Lett* 4, 2805 (**2013**).