# High-Performance Complementary III-V Tunnel FETs with Strain Engineering

Jun Z. Huang, Yu Wang, Pengyu Long, Yaohua Tan, Michael Povolotskyi, and Gerhard Klimeck

Abstract-Strain engineering has recently been explored to improve tunnel field-effect transistors (TFETs). Here, we report design and performance of strained ultra-thin-body (UTB) III-V TFETs by quantum transport simulations. It is found that for an InAs UTB confined in [001] orientation, uniaxial compressive strain in [100] or [110] orientation shrinks the band gap meanwhile reduces (increases) transport (transverse) effective masses. Thus it improves the ON state current of both n-type and p-type UTB InAs TFETs without lowering the source density of states. Applying the strain locally in the source region makes further improvements by suppressing the OFF state leakage. For p-type TFETs, the locally strained area can be extended into the channel to form a quantum well, giving rise to even larger ON state current that is comparable to the n-type ones. Therefore strain engineering is a promising option for improving complementary circuits based on UTB III-V TFETs.

Index Terms—Tunnel FETs (TFETs), strained TFETs, p-type TFETs, ultra-thin-body (UTB) TFETs, complementary TFETs.

## I. INTRODUCTION

TUNNEL field-effect transistor (TFET) is a steep subthreshold swing (SS) device that is promising in building future low-power integrated circuits. But its drive current  $(I_{ON})$  is usually limited by the small tunnel probability [1] leading to pronounced switching delay (CV/I). Various methods have been proposed to improve  $I_{ON}$ , such as the doping engineering [2], [3], different channel materials (including low band gap III-V materials and two-dimensional materials) [4], broken/staggered gap heterojunction [4], [5], grading of the source [6], resonant enhancement [7]–[9], and channel/source heterojunctions [10], [11].

As a widely used technique to engineer electronic devices, strain has also been employed to improve the performance of silicon/germanium TFETs [12]–[14] and III-V materials (InAs and InAs/GaSb) based nanowire TFETs [15]–[18]. These studies show that strain can reduce the band gap and/or effective masses leading to improved tunnel probability. At the same time, however, there are two side effects. One is that the

Manuscript received xxx xx, 2016; revised xxxx xx, 2016. This work uses nanoHUB.org computational resources operated by the Network for Computational Nanotechnology funded by the U.S. National Science Foundation under Grant EEC-0228390, Grant EEC-1227110, Grant EEC-0634750, Grant OCI-0438246, Grant OCI-0832623, and Grant OCI-0721680. This material is based upon work supported by the National Science Foundation under Grant 1125017. NEMO5 developments were critically supported by an NSF Peta-Apps award OCI-0749140 and by Intel Corp.

direct source-to-drain tunneling and ambipolar leakage are also increased. The other is that the valence band density of states (DOS) is reduced, creating large source Fermi degeneracy (the distance between Fermi level and valence band edge) that degrades the SS toward thermal limit (60mV/dec). The first one can be mitigated by using local strain, i.e., by applying strain around the source only so that the band gap and effective masses in the channel remains unchanged [14], [19]. The second one has recently been addressed by lowering the doping concentration in the source but maintaining a high doping region next to the tunnel junction to shorten the tunnel distance [20].

However, for experimentally more favorable ultra-thin-body (UTB) III-V TFETs, strain engineering has not been studied yet. UTB structures offer more design freedoms. For example, by selecting  $(\bar{1}10)/[110]$  instead of (001)/[100] as the confinement/transport orientation, the tunnel probability of GaSb/InAs heterojunction is increased due to the smaller band gap and transport effective masses [10]. Besides, the effect of strain is different if strain is applied in different directions [21].

Moreover, the efforts mentioned above mainly focus on strained n-type TFETs (nTFETs). Strain effects on p-type TFETs (pTFETs) still need to be explored as strain influences conduction and valence bands differently. In fact, due to the asymmetric conduction and valence band structures of III-V materials, pTFETs behave differently from nTFETs. For pTFETs, since the conduction band DOS is lower than valence band DOS, the allowed source doping density in pTFETs is lower than that of nTFETs. This leads to longer source depletion region and consequently smaller  $I_{\rm ON}$  [22], [23]. The study in [24] shows that doping or heterojunction design in the source can help to solve this problem.

In this paper, we systematically study globally and locally strained InAs UTB nTFETs and pTFETs using accurate quantum transport simulations. Different types of strain and crystal orientations are investigated. It is found that, by selecting [001]/[100] orientation as the confinement/transport direction and applying uniaxial compressive strain along the transport direction,  $I_{\rm ON}$  of both nTFETs and pTFETs can be significantly improved. Furthermore, the improvement is more pronounced for pTFETs, narrowing the performance gap between nTFETs and pTFETs. These make strain engineering a promising technique for enabling low-power high-performance complementary circuits based on III-V UTB TFETs.

## II. SIMULATION METHOD

The devices are simulated using NEMO5 tool [25] with Poisson equation and quantum ballistic transport equations

J. Z. Huang, Y. Wang, P. Long, M. Povolotskyi, and G. Klimeck are with the Network for Computational Nanotechnology and Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907 USA (e-mail: junhuang1021@gmail.com).

Y. Tan is with Department of Electrical and Computer Engineering, University of Virginia, Charlottesville, VA 22904-4743 USA

| $E_g$ (eV) | $\Delta$ (eV) | $E_p$ (eV) | $m_e^*/m_0$ | $\gamma_1$            | $\gamma_2$               | $\gamma_3$               |

|------------|---------------|------------|-------------|-----------------------|--------------------------|--------------------------|

| 0.347      | 0.397         | 19.20      | 0.022       | 20.63                 | 8.917                    | 9.724                    |

| $a_v$ (eV) | $a_c$ (eV)    | b (eV)     | d (eV)      | C <sub>11</sub> (GPa) | C <sub>12</sub><br>(GPa) | C <sub>44</sub><br>(GPa) |

| -1.00      | -5.08         | -1.8       | -3.6        | 832.9                 | 452.6                    | 395.9                    |

(quantum transmitting boundary method [26]) solved self-consistently. Phonon scattering is excluded in this work since it does not significantly impact the I-V characteristics of III-V homojunction TFETs [15], [27]. As a widely used method to study strained III-V materials, the eight-band  $\mathbf{k} \cdot \mathbf{p}$  method [28] is employed to obtain the device Hamiltonian. It is also computationally more efficient than atomistic full-band tight binding (TB) method especially when strain is included.

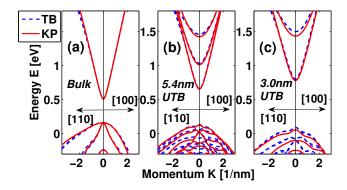

Fig. 1. TB and KP calculations of E-k diagram for (a) bulk InAs, (b) a 5.4nm thick UTB InAs, and (c) a 3.0nm thick UTB InAs. Both UTBs are confined in the [001] direction.

Since tunneling current is very sensitive to band structures, the accuracy of  $\mathbf{k} \cdot \mathbf{p}$  method needs to be validated. We first extract the  $\mathbf{k} \cdot \mathbf{p}$  band parameters from corresponding TB (sp<sup>3</sup>d<sup>5</sup>s\* basis with spin-orbit coupling) calculation of bulk material. The TB parameters taken from [29] are fit to first-principles density functional theory (DFT) band structures as well as wave functions, and have been shown to be transferrable to UTB structures [30]. The extraction procedure can be found in [17]. The extracted  $\mathbf{k} \cdot \mathbf{p}$  parameters for InAs used in this study are list in Table I. Note that the values of deformation potentials and elastic constants (for calculating Poisson ratio and converting stress to strain) are suggested in [31]. As shown in Fig. 1 (a), for bulk InAs, the two calculations match well around k = 0 as expected.

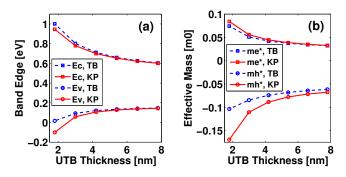

We then compare the confined band structures of InAs UTBs calculated from both methods, as shown in Fig. 1 (b) and (c). It is observed that the shapes of the band structures are quite similar to each other around the band gap, for both UTB thicknesses. The band edges and effective masses (which are of great interest for TFETs) for different UTB thicknesses are further calculated and plotted in Fig. 2. It is seen that the  $\mathbf{k} \cdot \mathbf{p}$  calculations match TB calculations quite well when the UTB is thick. When the UTB becomes thinner, the results start to diverge, especially for the hole effective mass. The general

Fig. 2. TB and KP calculations of (a) conduction band edge (Ec) and valence band edge (Ev), (b) electron effective mass (me\*) and hole effective mass (mh\*) in the [100] direction, for different InAs UTB thicknesses. The UTBs are confined in the [001] direction.

trend, i.e., the band gap and effective masses increase as UTB thickness decreases, is captured by both methods.

# III. STRAINED INAS UTBS

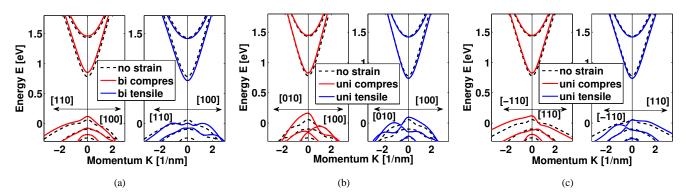

The benchmarked  $\mathbf{k} \cdot \mathbf{p}$  method is then used to study the properties of a 3.0nm thick InAs UTB under various strain conditions. We consider the most common (001) oriented wafer with a channel direction along [100] and [110]. Note that the direction of the applied uniaxial strain is always aligned with channel (transport) direction. The band structures are plotted in Fig. 3, with their band gaps and effective masses at the band edges summarized in Table II. Comparing biaxial and uniaxial strain, we find that biaxial strain only slightly changes the band gap or effective masses. The uniaxial strain, instead, significantly modulates the band gap and effective masses. The uniaxial tensile (compressive) strain increases (decreases) transport masses meanwhile decreases (increases) the transverse masses. Since tunneling probability is an exponential function of the band gap and transport masses [32], uniaxial compressive strain is expected to improve TFET  $I_{ON}$ significantly. In addition, there is a large amount of valence band edge shift under uniaxial compressive strain. Comparing uniaxial compressive strain in the [100] and [110] orientations, we find that [100] strain leads to larger reduction of band gap and transport effective masses and thus is expected to be the most effective in improving  $I_{ON}$  of TFETs. Thus [100] uniaxial compressive strain is the focus of the remaining study.

## IV. GLOBALLY STRAINED INAS UTB TFETS

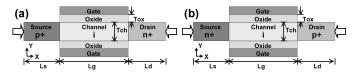

At first, we study InAs UTB TFETs under global (or uniform) strain. The device structures and parameters are illustrated in Fig. 4. We consider 0.3V power supply, i.e.,  $V_{\rm DD}=0.3V$ . A lightly doped drain is employed for nTFETs to suppress ambipolar leakage, while a moderately doped source of pTFET is a trade off of Fermi degeneracy and depletion length. Source and drain lengths are different since lower doping density requires a longer depletion region to reach charge neutrality. The confinement and transport orientations are [001] and [100], respectively, with the uniaxial compressive stress applied along [100] as explained above. For high-performance (HP), low operating power (LOP), and

Fig. 3. KP calculations of *E-k* diagram for a 3.0nm InAs UTB with 2% biaxial strain in the (001) plane (a), 2GPa uniaxial stress along [100] direction (b), 2GPa uniaxial stress along [110] direction (c). The confinement direction is along [001] for all cases. The unstrained cases are also shown for comparison.

TABLE II BAND GAPS (EG) AND EFFECTIVE MASSES ( $m_e^*$  FOR ELECTRON AND  $m_h^*$  FOR HOLE) EXTRACTED FROM FIG. 3. THE PERCENTAGES IN THE PARENTHESES ARE THE CHANGES RELATIVE TO THE UNSTRAINED CASES.

| 2% Biaxial                          | Eg (eV)                                           | $m_e^*$ [100]                                      | $m_e^*$ [110]                                      | $m_h^*$ [100]                                          | $m_h^*$ [110]                                          |

|-------------------------------------|---------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| No strain<br>Tensile<br>Compressive | 0.7206<br>0.7111<br>(-1.3%)<br>0.7339<br>(+1.9%)  | 0.0558<br>0.0577<br>(+3.4%)<br>0.0546<br>(-2.2%)   | 0.0562<br>0.0581<br>(+3.4%)<br>0.0550<br>(-2.1%)   | -0.1106<br>-0.1272<br>(+15.0%)<br>-0.1015<br>(-8.2%)   | -0.1133<br>-0.1313<br>(+15.9%)<br>-0.1038<br>(-8.4%)   |

| 2GPa Uni-<br>axial [100]            | Eg (eV)                                           | $m_e^*$ [100]                                      | $m_e^*$ [010]                                      | $m_h^*$ [100]                                          | $m_h^*$ [010]                                          |

| No strain<br>Tensile<br>Compressive | 0.7206<br>0.6398<br>(-11.2%)<br>0.6595<br>(-8.5%) | 0.0558<br>0.0660<br>(+18.3%)<br>0.0463<br>(-17.0%) | 0.0558<br>0.0477<br>(-14.5%)<br>0.0636<br>(+14.0%) | -0.1106<br>-0.2917<br>(+163.7%)<br>-0.0587<br>(-46.9%) | -0.1106<br>-0.0663<br>(-40.1%)<br>-0.2386<br>(+115.7%) |

| 2GPa Uni-<br>axial [110]            | Eg (eV)                                           | $m_e^*$ [110]                                      | $m_e^*$ [ $\bar{1}10$ ]                            | $m_h^*$ [110]                                          | $m_h^* = [\bar{1}10]$                                  |

| No strain<br>Tensile                | 0.7206<br>0.6852<br>(-4.9%)                       | 0.0562<br>0.0620<br>(+10.3%)                       | 0.0562<br>0.0518<br>(-7.8%)                        | -0.1133<br>-0.3549<br>(+213.2%)                        | -0.1133<br>-0.0704<br>(-37.9%)                         |

| Compressive                         | 0.7034<br>(-2.4%)                                 | 0.0502<br>(-10.7%)                                 | 0.0598<br>(+6.4%)                                  | -0.0637<br>(-43.8%)                                    | -0.2445<br>(+115.8%)                                   |

low standby power (LSTP) applications,  $I_{\rm OFF}$  is fixed to  $1\times 10^{-1}{\rm A/m},\, 1\times 10^{-3}{\rm A/m},\, {\rm and}\, 1\times 10^{-5}{\rm A/m},\, {\rm respectively}.$

Fig. 4. Device structures of UTB nTFET (a) and pTFET (b) under global uniaxial compressive strain. For nTFET, doping density of the source (drain) is  $-5\times10^{19} {\rm cm}^{-3}~(+5\times10^{18} {\rm cm}^{-3}),$  Ls=10nm, Lg=20nm, and Ld=20nm. For pTFET, doping density of the source (drain) is  $+1.5\times10^{19} {\rm cm}^{-3}~(-2\times10^{19} {\rm cm}^{-3}),$  Ls=20nm, Lg=20nm, and Ld=10nm. Channel (InAs UTB) thickness is 3.0nm and equivalent oxide thickness (EOT) is 0.7nm, for both devices. The Z direction is periodic.

# A. N-Type TFETs

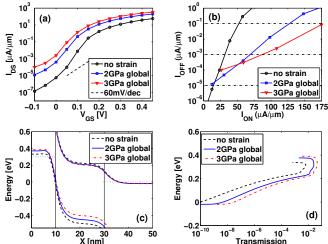

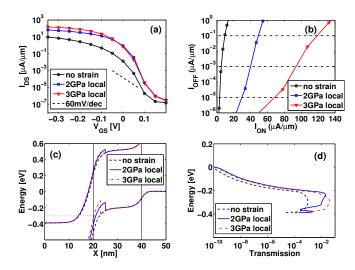

Fig. 5 compares the nTFETs without strain and with 2GPa/3GPa global uniaxial compressive stress. From (a), it is

found that the strain improves the turn-on characteristics, but degrades the SS. As a result, as shown in (b), with fixed  $I_{\rm OFF}$ ,  $I_{\rm ON}$  is improved for HP and LOP applications, but degraded for LSTP application. For LOP application,  $I_{\rm ON}$  is improved from 32A/m to 69A/m (2GPa) and 87A/m (3GPa). As shown in (c) and (d), the smaller band gap and transport effective masses enabled by the uniaxial compressive strain enhance the transmission, both above and below the channel conduction band edge, leading to not only larger source-to-channel tunnel current but also larger source-to-drain tunnel leakage.

Fig. 5. (a)  $I_{\rm DS}\text{-}V_{\rm GS}$  curve ( $V_{\rm DS}=0.3V$ ), (b) $I_{\rm ON}\text{-}I_{\rm OFF}$  plot, (c) band diagrams at  $V_{\rm GS}=0.2V$ , and (d) transmissions at  $V_{\rm GS}=0.2V$  and transverse  $k_z=0$ , of 2GPa and 3GPa globally strained nTFETs, in comparison with the unstrained case. In (b), HP, LOP, and LSTP applications are marked with dashed lines. In (c), the source and drain Fermi levels are marked with dotted lines.

It should be noted that, different from the nanowire case [15] where large source Fermi degeneracy is created by strain, the source Fermi degeneracy for the strained cases here is only about 0.05eV higher than the unstrained case so it does not appreciably degrade the SS. This is because although the hole transport effective mass is reduced by strain the hole transverse effective mass is increased, as shown in Table II, and therefore the source DOS is only slightly reduced.

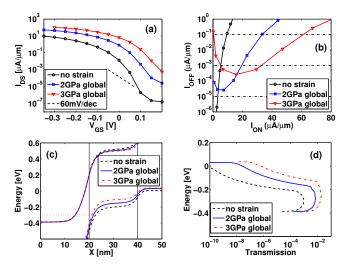

# B. P-Type TFETs

Fig. 6 compares the pTFETs without strain and with 2GPa/3GPa global uniaxial compressive stress. Similar to the n-type cases, the strain improves  $I_{\rm ON}$  of pTFETs for both HP and LOP applications, but degrades  $I_{\rm ON}$  for LSTP application. For LOP application,  $I_{\rm ON}$  is improved from 5A/m to 19A/m (2GPa) and 33A/m (3GPa). It is seen that the source Fermi degeneracy does not change with the strain, as the density of states (DOS) of the conduction band does not change much with the strain (the electron transport mass decreases but the electron transverse mass increases, as shown in Table II).

Fig. 6. (a)  $I_{\rm DS}\text{-}V_{\rm GS}$  curve ( $V_{\rm DS}=-0.3V$ ), (b) $I_{\rm ON}\text{-}I_{\rm OFF}$  plot, (c) band diagrams at  $V_{\rm GS}=-0.1V$ , and (d) transmissions at  $V_{\rm GS}=-0.1V$  and transverse  $k_z=0$ , of 2GPa and 3GPa globally strained pTFETs, in comparison with the unstrained case. In (b), HP, LOP, and LSTP applications are marked with dashed lines. In (c), the source and drain Fermi levels are marked with dotted lines.

## V. LOCALLY STRAINED INAS UTB TFETS

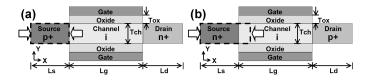

Local (or non-uniform) strain can be used to overcome the drawbacks of globally strained TFETs, i.e., large source-to-drain and ambipolar leakage, and at the same time to retain the advantages, i.e., large source-to-channel transmission. As illustrated in Fig. 7, the local uniaxial compressive strain is applied only to the source portion of nTFET and pTFET. For pTFET, the locally strained region is slightly extended into the channel to induce further improvement, as will be explained in the following. The feasibility of fabricating such locally strained TFETs has been discussed in [14].

Fig. 7. Device structures of UTB nTFET (a) and pTFET (b) under local uniaxial compressive strain. The device parameters are the same as those in Fig. 4. Note the difference of the strained areas.

## A. N-Type TFETs

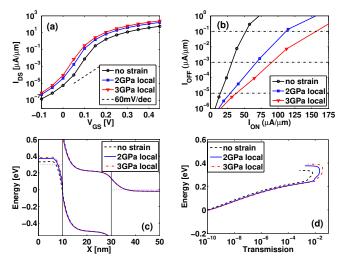

Fig. 8 compares nTFETs without strain and with 2GPa/3GPa local uniaxial compressive strain in the source. It is found that the strain improves  $I_{\rm ON}$  for all HP, LOP, and LSTP applications. For LOP application,  $I_{\rm ON}$  is improved from 32A/m to 68A/m (2GPa) and 91A/m (3GPa), which is similar to the global strain case. For LSTP application,  $I_{\rm ON}$  is improved from 15A/m to 29A/m (2GPa) and 38A/m (3GPa). As shown in (c), the band gap and transport effective mass decrease in the source, but remain unchanged in the channel. As seen in (d), the source-to-channel tunnel probability still increases, as in the global strain case; but the source-to-drain leakage and ambipolar leakage are not affected, in contrast to the global strain case.

Fig. 8. The same plots as Fig. 5 but for locally strained nTFETs.

# B. P-Type TFETs

Fig. 9 compares the pTFETs without strain and with 2GPa/3GPa local uniaxial compressive strain in the source and in the 5nm/3nm extension region. It is found that the strain improves  $I_{\rm ON}$  for all HP, LOP, and LSTP applications. For LOP application,  $I_{\rm ON}$  is improved from 5A/m to 40A/m (2GPa) and 94A/m (3GPa), larger than the improvement enabled by global strain. For LSTP application,  $I_{ON}$  is improved from 3A/m to 30A/m (2GPa) and 68A/m (3GPa). Similar to the locally strained nTFET cases, the source-to-channel tunnel probability increases while the source-to-drain leakage and ambipolar leakage are not infuenced. In addition, the sourceto-channel tunnel barrier thickness is further reduced by the valence band discontinuity (between strained and unstrained parts), similar to the channel heterojunction design [10]. For nTFETs, unfortunately, we could not employ the same design, i.e., extending the locally strained area into the channel and make use of the conduction band discontinuity. This is because the conduction band edge moves upward instead of downward under uniaxial compressive strain. Thus, the improvement of p-type cases is more significant than the n-type cases.

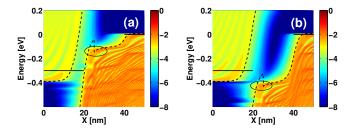

Fig. 10 (a) and (b) depict the local density of states (LDOS) of the locally strained pTFET with 2GPa stress, around ON

Fig. 9. The same plots as Fig. 6 but for locally strained pTFETs.

and OFF state, respectively. At ON state, the band discontinuity forms a triangular quantum well, creating a resonant notch state aligned with the channel valence band edge, enhancing the transmission. At OFF state, the notch state lies outside the quantum well, reducing the thermal emission induced leakage. When the stress is increased from 2GPa to 3GPa, the band discontinuity increases, and the extension region needs to be reduced from 5nm to 3nm so as to avoid forming the notch state inside the quantum well. The phenomenon has also been observed in channel heterojunction TFETs [10].

Fig. 10. LDOS (in logarithmic scale) of the locally strained pTFET with 2GPa stress, around ON state with  $V_{\rm GS}=-0.2V$  (a) and around OFF state with  $V_{\rm GS}=0.1V$  (b). Band diagrams (dashed lines) and contact Fermi levels (solid lines) are superimposed. The notch states are highlighted with circles.

It should be mentioned that the local strain is assumed to be abrupt in this study. In practice, there should be a transition region between the strained and the relaxed portions, which will smooth out the abrupt band profile and may change the simulation results quantitatively. We have not performed such kind of simulation since the actual strain profile depends on specific strain implementation. Note that studies in [14], [19] assume Gaussian strain profiles.

# VI. CONCLUSION

Quantum ballistic transport simulations employing eightband  $\mathbf{k} \cdot \mathbf{p}$  Hamiltonian are carried out to study strain effects on UTB III-V TFETs. It is found, that for an InAs UTB confined in the [001] orientation, uniaxial compressive stress in the [100] orientation significantly reduces the band gap and

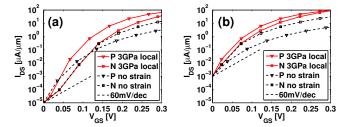

Fig. 11.  $I_{\rm DS}$ - $V_{\rm GS}$  characteristics ( $V_{\rm DD}=0.3V$ ) of P and N type InAs UTB TFETs before and after 3GPa local uniaxial compressive stress, at two  $I_{\rm OFF}$  targets. (a)  $I_{\rm OFF}=1\times10^{-5}{\rm A/m}$ , and (b)  $I_{\rm OFF}=1\times10^{-3}{\rm A/m}$ .

transport masses, meanwhile increases the transverse masses, and thus can be employed to improve InAs UTB TFETs. Larger improvements can be obtained by applying the strain locally in the source. As compared in Fig. 11, for an n-type (p-type) InAs UTB TFET with 20nm channel length and 3nm body thickness, at  $V_{\rm DD} = 0.3V$  and  $I_{\rm OFF} = 1 \times 10^{-5} {\rm A/m}$ , the strain improves  $I_{ON}$  from 15A/m (3A/m) to 38A/m (68A/m). While at  $V_{\rm DD} = 0.3V$  and  $I_{\rm OFF} = 1 \times 10^{-3} {\rm A/m}$ , it improves  $I_{\rm ON}$  from 32A/m (5A/m) to 91A/m (94A/m). The strain not only improves  $I_{ON}$  of both n-type and p-type devices but also narrows the performance gap between them. Therefore we think strain engineering is a promising performance booster for complementary circuits based on UTB III-V TFETs. This study focuses on strain engineering of homojunction TFETs, but it can be combined with heterojunction engineering and/or doping engineering to further boost the performances.

#### REFERENCES

- A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energyefficient electronic switches," *Nature*, vol. 479, pp. 329–337, Nov. 2011.

- [2] R. Jhaveri, V. Nagavarapu, and J. C. Woo, "Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor," *IEEE Trans. Electron Devices*, vol. 58, no. 1, pp. 80–86, 2011.

- [3] J. Z. Huang, P. Long, M. Povolotskyi, M. J.W. Rodwell, and G. Klimeck, "Exploring channel doping designs for high-performance tunneling FETs," in *Proc. 74th Annu. Device Res. Conf. (DRC)*, Jun. 2016.

- [4] M. Luisier and G. Klimeck, "Performance comparisons of tunneling field-effect transistors made of InSb, Carbon, and GaSb-InAs broken gap heterostructures," in *IEEE IEDM Tech. Dig.*, Dec. 2009, pp. 37.6.1–37.6.4.

- [5] D. K. Mohata *et al.*, "Demonstration of MOSFET-like on-current performance in arsenide/antimonide tunnel FETs with staggered heterojunctions for 300 mV logic applications," in *IEEE IEDM Tech. Dig.*, Dec. 2011, pp. 33.5.1–33.5.4.

- [6] S. Brocard, M. G. Pala, and D. Esseni, "Large on-current enhancement in hetero-junction tunnel-FETs via molar fraction grading," *IEEE Electron Devices Lett.*, vol. 35, no. 2, pp. 184–186, Feb. 2014.

[7] U. E. Avci and I. A. Young, "Heterojunction TFET scaling and resonant-

- [7] U. E. Avci and I. A. Young, "Heterojunction TFET scaling and resonant-TFET for steep subthreshold slope at sub-9nm gate-length," *IEEE IEDM Tech. Dig.*, Dec. 2013, pp. 4.3.1–4.3.4.

- [8] M. G. Pala, and S. Brocard, "Exploiting hetero-junctions to improve the performance of III-V nanowire tunnel-FETs," *IEEE J. Electron Devices* Soc., vol. 3, no. 3, pp. 115–121, 2015.

- [9] P. Long, E. Wilson, J. Z. Huang, G. Klimeck, M. J.W. Rodwell, and M. Povolotskyi, "Design and simulation of GaSb/InAs 2D transmissionenhanced tunneling FETs," *IEEE Electron Device Lett.*, vol. 37, no. 1, pp. 107–110, Jan. 2016.

- [10] P. Long, J. Z. Huang, M. Povolotskyi, G. Klimeck, and M. J.W. Rodwell, "High-current tunneling FETs with (110) orientation and a channel heterojunction," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 345–348, Mar. 2016.

- [11] P. Long, M. Povolotskyi, J. Z. Huang, H. Ilatikhameneh, T. Ameen, R. Rahman, T. Kubis, G. Klimeck, and M. J.W. Rodwell, "Extremely high simulated ballistic currents in triple-heterojunction tunnel transistors," in *Proc. 74th Annu. Device Res. Conf. (DRC)*, Jun. 2016.

- [12] O. M. Nayfeh et al., "Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions," IEEE Electron Device Lett., vol. 29, no. 9, pp. 1074–1077, Sep. 2008.

- [13] T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat, "Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60 mV/dec subthreshold slope," in *IEEE IEDM Tech. Dig.*, Dec. 2008, pp. 947–949.

- [14] K. Boucart, W. Riess, and A. M. Ionescu, "Lateral strain profile as key technology booster for all-silicon tunnel FETs," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 656–658, Jun. 2009.

- [15] F. Conzatti, M. G. Pala, D. Esseni, E. Bano, and L. Selmi, "Strain-induced performance improvements in InAs nanowire tunnel FETs," *IEEE Trans. Electron Devices*, vol. 59, no. 8, pp. 2085–2092, 2012.

[16] S. Brocard, M. G. Pala, and D. Esseni, "Design options for hetero-

- [16] S. Brocard, M. G. Pala, and D. Esseni, "Design options for heterojunction tunnel FETs with high on current and steep sub-threshold voltage slope," *IEEE IEDM Tech. Dig.*, Dec. 2013, pp. 5.4.1–5.4.4.

- [17] J. Z. Huang, L. Zhang, P. Long, M. Povolotskyi, and G. Klimeck, "Quantum transport simulation of III-V TFETs with reduced-order k · p method," in *Tunneling Field Effect Transistor Technology*, L. Zhang and M. Chan, Eds. Switzerland: Springer, 2016, pp. 151–180.

- [18] M. Visciarelli, E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, "Impact of strain on tunneling current and threshold voltage in III-V nanowire TFETs," *IEEE Electron Devices Lett.*, vol. 37, no. 5, pp. 560– 563, 2016.

- [19] F. Conzatti, M. G. Pala, D. Esseni, and E. Bano, "Investigation of localized versus uniform strain as a performance booster in InAs Tunnel-FETs," *Solid-State Electron.*, vol. 88, pp. 49–53, Oct. 2013.

- [20] D. Verreck, A. S. Verhulst, M. L. Van de Put, B. Sorée, N. Collaert, A. Mocuta, A. Thean, and G. Groeseneken, "Uniform strain in heterostructure tunnel field-effect transistors," *IEEE Electron Device Lett.*, vol. 37, no. 3, pp. 337–340, Mar. 2016.

- [21] M. Moussavou, N. Cavassilas, E. Dib, and M. Bescond, "Influence of uniaxial strain in Si and Ge p-type double-gate metal-oxide-semiconductor field effect transistors," *J. Appl. Phys.* vol. 118, no. 11, pp. 114503-1–114503-5, 2015.

- [22] U. E. Avci, R. Rios, K. J. Kuhn, and I. A. Young, "Comparison of power and performance for the TFET and MOSFET and considerations for P-TFET," in *Proc. 11th IEEE Int. Conf. Nanotechnol.*, Aug. 2011, pp. 869–872.

- [23] U. E. Avci, D. H. Morris, and I. A. Young, "Tunnel field-effect transistors: prospects and challenges," *IEEE J. Electron Devices Soc.*, vol. 3, no. 3, pp. 88–95, May 2015.

- [24] D. Verreck, A. S. Verhulst, B. Sorée, N. Collaert, A. Mocuta, A. Thean, and G. Groeseneken, "Improved source design for p-type tunnel field-effect transistors: Towards truly complementary logic," *Appl. Phys. Lett.*, vol. 105, no. 5, pp. 243506-1–243506-4, Dec. 2014.

- [25] S. Steiger, M. Povolotskyi, H.-H. Park, T. Kubis, and G. Klimeck, "NEMO5: A parallel multiscale nanoelectronics modeling tool," *IEEE Trans. Nanotechnol.*, vol. 10, no. 6, pp. 1464–1474, Nov. 2011.

- [26] C. S. Lent and D. J. Kirkner, "The quantum transmitting boundary method," J. Appl. Phys., vol. 67, no. 10, pp. 6353–6359, 1990.

- [27] M. Luisier and G. Klimeck, "Simulation of nanowire tunneling transistors: From the Wentzel-Kramers-Brillouin approximation to full-band phonon-assisted tunneling," *J. Appl. Phys*, vol. 107, no. 8, pp. 084507-1–084507-6, 2010.

- [28] T. B. Bahder, "Eight-band k · p model of strained zinc-blende crystals," Phys. Rev. B, vol. 41, no. 17, p. 11992, 1990.

- [29] Y. Tan et al., Tight Binding Parameters by DFT Mapping. https://nanohub.org/resources/15173, accessed Apr. 26, 2016.

- [30] Y. P. Tan, M. Povolotskyi, T. Kubis, T. B. Boykin, and G. Klimeck, "Tight-binding analysis of Si and GaAs ultrathin bodies with subatomic wave-function resolution," *Phys. Rev. B*, vol. 92, no. 8, p. 085301, 2015.

- [31] I. Vurgaftman, J. R. Meyer, and L. R. Ram-Mohan, "Band parameters for III-V compound semiconductors and their alloys," *J. Appl. Phys.* vol. 89, no. 11, pp. 5815–5875, 2001.

- [32] A. C. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proc. IEEE*, vol. 98, no. 12, pp. 2095–2110, Dec. 2010