# Structural Synthesis for GXW Specifications

Chih-Hong Cheng, Yassine Hamza, and Harald Ruess

fortiss - An-Institut Technische Universität München Guerickestr. 25, 80805 Munich, Germany {cheng,ruess}@fortiss.org, yassine.hamza@in.tum.de

Abstract. We define the GXW fragment of linear temporal logic (LTL) as the basis for synthesizing embedded control software for safety-critical applications. Since GXW includes the use of a weak-until operator we are able to specify a number of diverse programmable logic control (PLC) problems, which we have compiled from industrial training sets. For GXW controller specifications, we develop a novel approach for synthesizing a set of synchronously communicating actor-based controllers. This synthesis algorithm proceeds by means of recursing over the structure of GXW specifications, and generates a set of dedicated and synchronously communicating sub-controllers according to the formula structure. In a subsequent step, 2QBF constraint solving identifies and tries to resolve potential conflicts between individual GXW specifications. This structural approach to GXW synthesis supports traceability between requirements and the generated control code as mandated by certification regimes for safety-critical software. Synthesis for GXW specifications is in PSPACE compared to 2EXPTIME-completeness of full-fledged LTL synthesis. Indeed our experimental results suggest that GXW synthesis scales well to industrial-sized control synthesis problems with 20 input and output ports and beyond.

## 1 Introduction

Embedded control software in the manufacturing and processing industries is usually developed using specialized programming languages such as ladder diagrams or other IEC 61131-3 defined languages. Programming in these rather low-level languages is not only error-prone but also time-and resource-intensive. Therefore we are addressing the problem of correct-by-construction and automated generation of embedded control software from high-level requirements, which are expressed in a suitable fragment of linear temporal logic.

Moreover, an explicit correspondence between the high-level requirements and the generated control code is essential, since embedded control software is usually an integral part of safety-critical systems such as supervisory control and data acquisition (SCADA) systems for controlling critical machinery or infrastructure. In particular current industrial standards for safety-related development such as IEC 61508, DO 178C for avionics, and ISO 26262 for automotive applications mandate traceability between the control code and it requirements. Controllers generated by state-of-the-art LTL synthesis algorithms and tools such as generalized reactivity(1) (GR(1)) [15,25] or bounded LTL synthesis [8,11,28], however, usually do not explicitly support such traceability requirements. For example, the GR(1) synthesis tool Anzu generates circuit descriptions in Verilog from BDDs [15].

We are therefore proposing a novel approach for synthesizing structured control software. In essence, the control code is generated by means of structural recursion on the given LTL formulas. Therefore, the structure of the control code corresponds closely to the syntactic structure of the given requirements, and there is a direct correspondence between controller components and sub-formulas of the specification.

In a first step towards this goal, we identify a fragment of LTL for specifying the input-output behavior of typical embedded control components. Besides the specification of input assumptions, invariance conditions on outputs, and transition-like reactions of the form  $\mathbf{G}(\mathsf{input} \to \mathbf{X}^i \mathsf{output})$ , this fragment also contains specifications of reactions of the form  $\mathbf{G}(\mathsf{input} \to \mathbf{X}^i \mathsf{(output} \, \mathbf{W} \, \mathsf{release}))$ , where input is an LTL formula containing at most i consecutive  $\mathbf{X}$  operators (i.e., an LTL formula whose validity is determined by the next i input valuations). The latter reaction formula states that if there is a temporal input event satisfying the constraint input, then the output constraint should hold on output events until there is a release event (or output always holds). The operator

${f G}$  is the universal path quantifier,  ${f X}^i$  abbreviates i consecutive next-steps,  ${f W}$  denotes the weak until temporal operator, the constraint output contains no temporal operator, and the subformula release may contain certain numbers of consecutive next-steps but no other temporal operators. The resulting fragment of LTL is called  ${\sf GXW}$ .

So far we have successfully modelled more than 70 different embedded control scenarios in GXW. The main source for this set of benchmarking problems are publicly available collections of industrial training materials for PLCs (including CODESYS 3.0 and AC500) [2,16,24]. The proposed GXW fragment of LTL is also similar to established requirements templates for specifying embedded control software in the aerospace domain, such as EARS [23].

Previous work on LTL synthesis (e.g., [8,11,28,14,10,15,25,5,31,7]) usually generates gate-level descriptions for the synthesized control strategies. In contrast, we generate control software in an actor language with high-level behavioral constructs and synchronous dataflow communication between connected actors. This choice of generating *structured controllers* is motivated by current practice of programming controllers using, say, Matlab Simulink [4], continuous function charts (IEC 61131-3), and Ptolemy II [12], which also supports synchronous dataflow (SDF) models [19]. Notice, however, that the usual notions of LTL synthesis also apply to synthesis for SDF, since the composition of actors in SDF may also be viewed as Mealy machines with synchronous cycles [30].

Synthesis of structured controllers from GXW specifications proceeds in two subsequent phases. In the first phase, the procedure recurses on the structure of the given GXW formulas for generating dedicated actors for monitoring inputs events, for generating corresponding control events, and for wiring these actors according to the structure of the given GXW formulas. In the second phase, appropriate values for unknown parameters are synthesized in order to realize the conjunction of all given GXW specifications. Here we use satisfiability checking for quantified Boolean formula (2QBF) for examining if there exists such conflicts between multiple GXW specifications. More precisely, existential variables of generated 2QBF problems capture the remaining design freedom when an output variable is not constrained by any trigger of low-level events.

We demonstrate that controller synthesis for the GXW fragment is in PSPACE as compared to the 2EXPTIME-completeness result of full-fledged LTL [27]. Under some further reasonable syntactic restrictions on the GXW fragment we show that synthesis is in coNP.

An implementation of our GXW structural synthesis algorithm and application to our benchmark studies demonstrates a substantial speed-up compared to existing LTL synthesis tools. Moreover, the structure of the generated control code in SDF follows the structure of the given GXW specifications, and is more compact and, arguably, also more readable and understandable than commonly used gate-level representations for synthesized control strategies.

The paper is structured as follows. We introduce in Section 2 some basic notation for LTL synthesis, a definition of the GXW fragment of LTL and SDF actor systems together with the problem of actor-based LTL synthesis under GXW fragment. Section 3 illustrates GXW and actor-based control for such specifications by means of an example. Section 4 includes the main technical contributions and describes algorithmic workflow for generating structured controllers from GXW, together with soundness and complexity results for GXW synthesis. A summary of our experimental results is provided in Section 5, and a comparison of GXW synthesis with closely related work on LTL synthesis is included in Section 6. The paper closes with concluding remarks in Section 7.

## 2 Problem Formulation

We present basic concepts and notations of LTL synthesis, and we define the GXW fragment of LTL together with the problem of synthesizing actor-based synchronous dataflow controllers for GXW.

#### 2.1 LTL Synthesis

Given two disjoint sets of Boolean variables  $V_{in}$  and  $V_{out}$ , the linear temporal logic (LTL) formulae over  $\mathbf{2}^{V_{in} \cup V_{out}}$  is the smallest set such that (1)  $v \in \mathbf{2}^{V_{in} \cup V_{out}}$  is an LTL formula, (2) if  $\phi_1, \phi_2$  are LTL-formulae, then so are  $\neg \phi_1, \neg \phi_2, \phi_1 \lor \phi_2, \phi_1 \land \phi_2, \phi_1 \to \phi_2$ , and (3) if  $\phi_1, \phi_2$  are LTL-formulae,

| ID | Meaning       | Pattern                                                                                                                                |

|----|---------------|----------------------------------------------------------------------------------------------------------------------------------------|

|    | Initial-Until |                                                                                                                                        |

| P2 | Trigger-Until | $\mathbf{G}(\phi_{in}^i \to \mathbf{X}^i(\varrho_{out} \mathbf{W}(\varphi_{in}^j \vee \rho_{out}^0)))$                                 |

| Р3 | If-Then       | $\mathbf{G}(\phi_{in}^{i} \to \mathbf{X}^{i} \varrho_{out}) \\ \mathbf{G}(\phi_{in}^{i} \leftrightarrow \mathbf{X}^{i} \varrho_{out})$ |

| P4 | Iff           | $\mathbf{G}(\phi_{in}^i \leftrightarrow \mathbf{X}^i \varrho_{out})$                                                                   |

|    |               | $\mathbf{G}(\phi_{out}^0)$                                                                                                             |

| P6 | Assumption    | $\mathbf{G}(\phi_{in}^0)$                                                                                                              |

| Table 1  | Patterns | defined | in | CXW/          | specifications |

|----------|----------|---------|----|---------------|----------------|

| Table 1. | ratterns | denned  | ш  | $G \wedge VV$ | Specifications |

|    | High-level Control Specification                                                                                                                                                                                        |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1 | output ${f W}$ input                                                                                                                                                                                                    |

| P2 | $\mathbf{G}(input 	o (output\mathbf{W}release))$                                                                                                                                                                        |

| P3 | $\begin{aligned} & \text{output } \mathbf{W} \text{ input} \\ & \mathbf{G}(\text{input} \rightarrow (\text{output } \mathbf{W} \text{ release})) \\ & \mathbf{G}(\text{input} \rightarrow \text{output}) \end{aligned}$ |

**Table 2.** Specification patterns and corresponding skeleton specification.

then so are  $\mathbf{G}\phi_1$ ,  $\mathbf{X}\phi_1$ ,  $\phi_1\mathbf{U}\phi_2$ . Given an  $\omega$ -word  $\sigma$ , define  $\sigma(i)$  to be the *i*-th element in  $\sigma$ , and define  $\sigma^i$  to be the suffix  $\omega$ -word of  $\sigma$  obtained by truncating  $\sigma(0) \dots \sigma(i-1)$ . The satisfaction relation  $\sigma \vDash \phi$  between an  $\omega$ -word  $\sigma$  and an LTL formula  $\phi$  is defined in the usual way. The weak until operator, denoted  $\mathbf{W}$ , is similar to the until operator but the stop condition is not required to occur; therefore  $\phi_1\mathbf{W}\phi_2$  is simply defined as  $(\phi_1\mathbf{U}\phi_2) \vee \mathbf{G}\phi_1$ . Also, we use the abbreviation  $\mathbf{X}^i\phi$  to abbreviate i consecutive  $\mathbf{X}$  operators before  $\phi$ .

A deterministic *Mealy machine* is a finite automaton  $\mathcal{C} = (Q, q_0, \mathbf{2}^{V_{in}}, \mathbf{2}^{V_{out}}, \delta)$ , where Q is set of (Boolean) state variables (thus  $\mathbf{2}^Q$  is the set of states),  $q_0 \in \mathbf{2}^Q$  is the initial state,  $\mathbf{2}^{V_{in}}$  and  $\mathbf{2}^{V_{out}}$  are sets of all input and output assignments defined by two disjoint sets of variables  $V_{in}$  and  $V_{out}$ .  $\delta := \mathbf{2}^Q \times \mathbf{2}^{V_{in}} \to \mathbf{2}^{V_{out}} \times \mathbf{2}^Q$  is the transition function that takes (1) a state  $q \in \mathbf{2}^Q$  and (2) input assignment  $v_{in} \in \mathbf{2}^{V_{in}}$ , and returns (1) an output assignment  $v_{out} \in \mathbf{2}^{V_{out}}$  and (2) the successor state  $q' \in \mathbf{2}^Q$ . Let  $\delta_{out}$  and  $\delta_s$  be the projection of  $\delta$  which considers only output assignments and only successor states. Given a sequence  $a_0 \dots a_k$  where  $\forall i = 0 \dots k, \ a_i \in \mathbf{2}^{V_{in}}$ , let  $\delta_s^k(q_0, a_0 \dots a_k)$  abbreviate the output state derived by executing  $a_0 \dots a_k$  as an input sequence on the Mealy machine.

Given a set of input and output Boolean variables  $V_{in}$  and  $V_{out}$ , together with an LTL formula  $\phi$  on  $V_{in}$  and  $V_{out}$  the LTL synthesis problem asks the existence of a controller as a deterministic Mealy machine  $\mathcal{C}_{\phi}$  such that, for every input sequence  $a=a_0a_1a_2\ldots$ , where  $a_i\in\mathbf{2}^{V_{in}}$ : (1) given the prefix  $a_0$  produce  $b_0=\delta_{out}(q_0,a_0)$ , (2) given the prefix  $a_0a_1$  produce  $b_1=\delta_{out}(\delta_s(q_0,a_0),a_1)$ , (3) given the prefix  $a_0\ldots a_ka_{k+1}$ , produce  $b_{k+1}=\delta_{out}(\delta_s^k(q_0,a_0\ldots a_k),a_{k+1})$ , and (4) the produced output sequence  $b=b_0b_1\ldots$  ensures that the word  $\sigma=\sigma_1\sigma_2\ldots$ , where  $\sigma_i=a_ib_i\in\mathbf{2}^{V_{in}\cup V_{out}}$ ,  $\sigma\models\phi$ .

#### 2.2 GXW Synthesis

We formally define the GXW fragment of LTL. Let  $\phi^i$ ,  $\varphi^i$ ,  $\psi^i$  be LTL formulae over input variables  $V_{in}$  and output variables  $V_{out}$ , where all formulas are (without loss of generality) assumed to be in disjunctive normal form (DNF), and each literal is of form  $\mathbf{X}^j v$  or  $\neg \mathbf{X}^j v$  with  $0 \le j \le i$  and  $v \in V_{in} \cup V_{out}$ . Clauses in DNF are also called *clause formulae*. Moreover, a formula  $\phi^i_{in}$  is restricted to contain only input variables in  $V_{in}$ , and similarly,  $\phi^i_{out}$  contains only output variables in  $V_{out}$ . Finally,  $\varrho_{out}$  denotes either  $v_{out}$  or  $\neg v_{out}$ , where  $v_{out}$  is an output variable.

For given input variables  $V_{in}$  and output variables  $V_{out}$ , a GXW formula is an LTL formula of one of the forms (P1)-(P6) as specified in Table 1. For example, GXW formulas of the form (P2) stop locking  $\varrho_{out}$  as soon as  $(\varphi_{in}^j \vee \rho_{out}^0)$  holds. GXW specifications are of the form

$$\varrho \to \bigwedge_{m=1...k} \eta_m , \qquad (1)$$

where  $\varrho$  matches the GXW pattern (P6), and  $\eta_m$  matches one of the patterns (P1) through (P5) in Table 1. Furthermore, the notation "." is used for projecting subformulas from  $\eta_m$ , when it satisfies a given type. For example, assuming that sub-specification  $\eta_m$  is of pattern P3, i.e., it matches  $\mathbf{G}(\phi_{in}^i \to \mathbf{X}^i \varrho_{out})$ ,  $\eta_m.\varrho_{out}$  specifies the matching subformula for  $\varrho_{out}$ . Notice also that GXW specifications, despite including the  $\mathbf{W}$  operator, have the *finite model property*, since the smallest number of unrolling steps for disproving the existence of an implementation is linear with respect to the structure of the given formula (cmp. Section 4.4).

Instead of directly synthesizing a Mealy machine as in standard LTL synthesis, we are considering here the generation of actor-based controllers using the computational model of synchronous dataflow

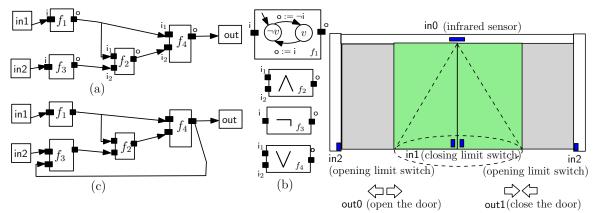

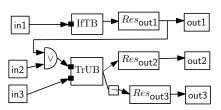

**Fig. 1.** An actor system allowing functional composition and corresponding actors  $f_1$  (a)(b), feedback loops such as (c) are not considered here.

Fig. 2. Control of automatic door switch.

(SDF) without feedback loops. An actor-based controller is a tuple  $S = (V_{in}, V_{out}, Act, \tau)$ , where  $V_{in}$  and  $V_{out}$  are disjoint sets of external input and output ports. Each port is a variable which may be assigned a Boolean value or undefined if no such value is available at the port. In addition, actors  $A \in Act$  may be associated with internal input ports  $U_{in}$  and output ports  $U_{out}$  (all named apart), which are also three-valued. The projection  $A.\mathfrak{u}$  denotes the port  $\mathfrak{u}$  of A. An actor  $A \in Act$  defines Mealy machine C whose input and output assignments are based on  $\mathbf{2}^{U_{in}}$  and  $\mathbf{2}^{U_{out}}$ , i.e., the output update function of C sets each output port to true or false, when each input port has value in  $\{\text{true}, \text{false}\}$ . Lastly,  $A^{(i)}$  denotes a copy of A which is indexed by i.

Let  $Act.U_{in}$  and  $Act.U_{out}$  be the set of all internal input and output ports for Act. The wiring  $\tau \subseteq (\mathcal{V}_{in} \cup Act.U_{in}) \times (\mathcal{V}_{out} \cup Act.U_{out})$  connects one (external, internal) input port to one or more (external, internal) output ports. For convenience, denote the wiring from port out of  $\mathcal{A}_1$  to port in of  $\mathcal{A}_2$  as  $(\mathcal{A}_1.\text{out} \longrightarrow \mathcal{A}_2.\text{in})$ . All ports are supposed to be connected, and every internal input port and every external output port is only connected to one wire (thus a port does not receive data from two different sources). Also, we do not consider actor systems with feedback loops here (therefore no cycles such as the one in Figure 1(c)), since systems without feedback loops can be statically scheduled [18].

Evaluation cycles are triggered externally under the semantics of synchronous dataflow. In each such cycle, the data received at the external input ports is processed and corresponding values are transferred to external output ports. Notice also that the composition of actors under SDF acts cycle-wise as a Mealy machine [30]. We illustrate the operational semantics of actor-based systems under SDF by means of the example in Figure 1(a), with input ports in1, in2, output port out, and actors  $f_1$ ,  $f_2$ ,  $f_3$ ,  $f_4$  (see also Figure 1(b))<sup>1</sup>. Now, assume that in the first cycle, the input ports in1 and in2 receive the value (false, true) and in the second cycle the value (false, true). The false value in in1 is copied to  $f_1$ .i. As  $f_1$  is initially at state where v = false, it creates the output value true (places it to  $f_1$ .o) and changes its internal state to v = true. The value true from  $f_1$ .o is then transferred to  $f_4$ .i and  $f_2$ .i. However, at this stage one cannot evaluate  $f_2$  or  $f_4$ , as the i<sub>2</sub> port is not yet filled with a value.  $f_3$  receives the value from in2 and produces  $f_3$ .o to false. Continuing this process, at the end of first cycle out is set to true, while in the second cycle, out is set to false.

As we do not consider feedback loops between actors in Act, from input read to output write, one can, using the enumeration method as exemplified above, create a static linear list  $\Xi$  of size  $|Act| + |\tau|$ , where each element  $\xi_{ind} \in \Xi$  is either in Act or in  $\tau$ , for specifying the linear order (from the partial order) how data is transferred between wires and actors. Such a total order  $\Xi$  is also called an *evaluation ordering* of the actor system S.

One may wrap any Mealy machine  $\mathcal{C}$  as an actor  $\mathcal{A}(\mathcal{C})$  by simply creating corresponding ports in  $\mathcal{A}(\mathcal{C})$  and by setting the underlying Mealy machine of  $\mathcal{A}(\mathcal{C})$  to  $\mathcal{C}$ . Therefore, actor-based controllers

<sup>&</sup>lt;sup>1</sup> The formal operational semantics, as it is standardized notation from SDF, is relegated to the appendix.

may be synthesized for a given LTL specification  $\phi$  by first synthesizing a Mealy machine  $\mathcal{C}$  realizing  $\phi$ , followed by the wrapping  $\mathcal{C}$  as  $\mathcal{A}(\mathcal{C})$ , creating external I/O ports, and connecting external I/O ports with  $\mathcal{A}(\mathcal{C})$ .

Given a GXW specification  $\phi$  over the input variables  $V_{in}$  and output variables  $V_{out}$ , the problem of GXW synthesis is to generate an actor-based SDF controller  $\mathcal{S}$  realizing  $\phi$ . As one can always synthesize a Mealy machine followed by wrapping it to an actor-based controller, GXW synthesis has the same complexity for Mealy machine and for actor-based controllers.

## 3 Example

We exemplify the use of GXW specifications and actor-based synthesis for these kinds of specification by means of an automatic sliding door [1], which is visualized in Figure 2. Inputs and outputs are as follows: in0 is true when someone enters the sensing field; in1 denotes a closing limit switch - it is true when two doors touch each other; in2 denotes an opening limit switch - it is true when the door reaches the end; out0 denotes the opening motor - when it is set to true the motor rotates clockwise, thereby triggering the door opening action; and out1 denotes closing motor - when it is set to true the motor rotates counter-clockwise, thereby triggering the door closing action. Finally, the triggering of a timer t0 is modeled by means a (controllable) output variable t0start and the expiration of a timer is modeled using an (uncontrollable) input variable t0expire.

Before stating the formal GXW specification for the example we introduce some mnemonics.

```

\begin{array}{lll} - \; \mathsf{entering}^1 := \neg \mathsf{in} 0 \wedge \mathbf{X} \, \mathsf{in} 0 & - \; \mathsf{lim\_reached}^1 := \neg \mathsf{in} 2 \wedge \mathbf{X} \mathsf{in} 2 \\ - \; \mathsf{expired}^1 := \neg \mathsf{t0expire} \wedge (\mathbf{X} \mathsf{t0expire}) & - \; \mathsf{closing\_stopped} := \mathsf{in} 1 \vee \mathsf{in} 0 \vee \mathsf{out} 0 \end{array}

```

The superscripts denote the maximum number of consecutive next-steps. Now the automatic sliding door controller is formalized in GXW as follows.

```

\begin{array}{lll} S1: & \mathbf{G}(\mathsf{entering}^1 \to \mathbf{X}(\mathsf{out0}\,\mathbf{W}\,\mathsf{in2})) & S5: & \mathbf{G}(\mathsf{lim\_reached}^1 \leftrightarrow \mathbf{X}(\mathsf{t0start})) \\ S2: & \mathbf{G}(\mathsf{expired}^1 \to \mathbf{X}(\mathsf{out1}\,\mathbf{W}\,\mathsf{closing\_stopped})) & S6: & \mathbf{G}(\mathsf{in0} \to \neg\mathsf{out1}) \\ S3: & \neg\mathsf{out0}\,\mathbf{W}\,\mathsf{entering}^1 & S7: & \mathbf{G}(\neg(\mathsf{out0} \land \mathsf{out1})) \\ S4: & \mathbf{G}(\mathsf{in2} \to \neg\mathsf{out0}) & \\ \end{array}

```

In particular, formula (S1) expresses the requirement that the opening of the door should continue (out0 = true) until the limit is reached (in2), and formulas (S3) and (S7) specify the expected initial behavior of the automatic sliding door. The GXW specifications for the sliding door example are classified as follows: formulas (S1), (S2) are of type (P2), (S3) is of type (P1), (S4), (S6) is of type (P3), (S5) is of type (P4), and (S7) of type (P5) according to Table 1.

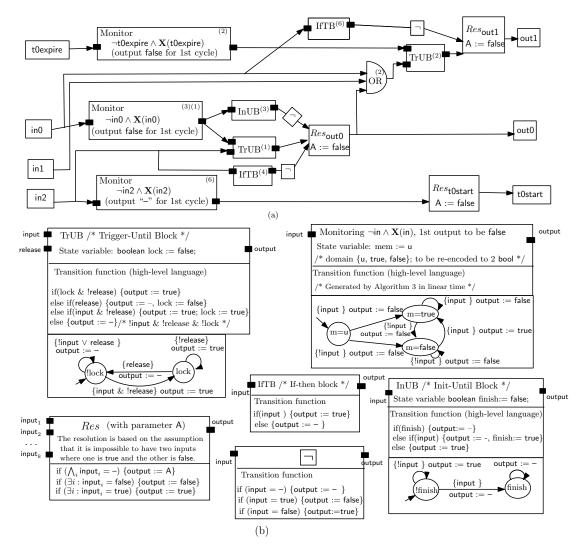

Figure 3 visualizes an actor-based automatic sliding door controller which realizes the GXW specification (S1)-(S7). It is constructed from a small number of building blocks, which are also described in Figure 3. Monitor actors, for example, are used for monitoring when the entering, expired, and lim\_reached constraints are fulfilled, the OR actor is introduced because of the closing\_stopped release condition in specification (S1), and the two copies of the trigger-until actors are introduced because of the (P2) shape of the specifications (S1) and (S2). The input and output ports of the trigger-until actor are in accordance with the namings for (P2) in Table 2. Resolution actors are used for resolving potential conflicts between individual GXW formulas in a specification. These actors are parameterized with respect to a Boolean A, which is the output of the resolution actor in case all inputs of this actor may be in {true, false} (this set is denoted by the shorthand "-" in Figure 3). The presented algorithm sets up a 2QBF problem for synthesizing possible values for these parameters. Because of the constraint (S7) on possible outputs out0 and out1, the parameter A for the resolution actor for output out0, for example, needs to be set to A:=false. Figure 3 also includes the operational behavior of selected actors in terms of high-level transitions and/or Mealy machines. The internal state and behavior for monitor actors, however, is synthesized, in linear time, from a given GXW constraint on inputs (see Section 4).

Finally, the structural correspondence of the actor-based controller in Figure 3 with the given  $\mathsf{GXW}$  specification of the sliding door example is being made explicit by superscripting actors with index (i) whenever the actor has been introduced due to the i-th specification.

Fig. 3. Actor-based controller realizing automatic sliding door.

## 4 Structural Synthesis

We now describe the algorithmic details for generating structured controllers from the GXW specifications of the form  $\varrho \to \bigwedge_{m=1...k} \eta_m$ . The automated sliding door is used as running example for illustrating the result of each step.

First, our algorithm prepares I/O ports, iterates through every formula  $\eta_m$  for creating high-level controllers (Step 1) based on the appropriate GXW pattern. For specifications of types P1 to P3, Table 2 lists the corresponding LTL specification (as high-level control objective), where input and release are input Boolean variables, output is an output Boolean variable.

Then, for each GXW formula, the algorithm constructs actors and wirings for monitoring low-level events by mimicking the DNF formula structure (Steps 2 and 3). On the structural level of clause formulas in DNF, the algorithm constructs corresponding controllers in linear time (Algorithm 1). Finally, the algorithm applies 2QBF satisfiability checking (and synthesis of parameters for resolution actors) for guaranteeing nonexistence of potential conflicts between different formulas in the GXW specifications (Step 4).

### 4.1 High-level Control Specifications and Resolution Actors

The initial structural recursion over GXW formulas is described in Step 1.

Step 1: Prepare external I/O ports, initiate high-level controller and resolution controllers

```

Input: LTL specification \phi = \varrho \to \bigwedge_{m=1...k} \eta_m, input variables V_{in}, output variables V_{out}

Output: Actor-based (partial) controller implementation S = (V_{in}, V_{out}, Act, \tau), map<sub>out</sub>

1 let map_{pattern} := \{P1 \mapsto InUB, P2 \mapsto TrUB, P3 \mapsto IfTB\}

\mathbf{2} \ \mathcal{V}_{in} := \{ \boxed{v_{in}} \mid v_{in} \in V_{in} \}

3 \mathcal{V}_{out} := \{ \lceil v_{out} \rceil \mid v_{out} \in V_{out} \}

4 foreach \eta_m, m = 1 \dots k do

if (p := \mathsf{DetectPattern}(\eta_m)) \in \{P1, P2, P3\} then

Create actor \mathcal{A}^{(m)} from \mathcal{A} := \mathsf{map}_{nattern}.\mathsf{get}(p), and add to \mathcal{S};

6

else if (p := \mathsf{DetectPattern}(\eta_m)) \not\in \{P4, P5, P6\} then return error

\mathbf{8} \ \mathbf{let} \ \mathsf{map}_{out} := \mathsf{NewEmptyMap}();

9 foreach v_{out} \in V_{out} do map_{out}.put(v_{out}, NewEmptyList());

10 foreach \eta_m, m = 1 \dots k do

\mathsf{map}_{out}.\mathsf{get}(v_{out}).\mathsf{add}(m), where v_{out} is the output variable used in \tau_m.\varrho_{out};

11

12 for each v_{out} \in V_{out} do Add actor Res_{v_{out}} := \mathsf{CreateResActor}(\mathsf{map}_{out}.\mathsf{get}(v_{out}).\mathsf{size}()) to Act

13 foreach \eta_m, m = 1 \dots k do

let v_{out} be the variable used in \tau_m.\varrho_{out}, ind := map<sub>out</sub>.get(v_{out}).indexOf(m);

14

if \neg v_{out} equals \tau_m.\varrho_{out} then // negation is used in literal

15

Create a negation actor \boxed{\neg}^{(m)} and add it to Act; \tau := \tau \cup \{(\mathcal{A}^{(m)}.\mathsf{output} \dashrightarrow \boxed{\neg}^{(m)}.\mathsf{input}), (\boxed{\neg}^{(m)}.\mathsf{output} \dashrightarrow Res_{v_{out}}.\mathsf{input}_{\mathsf{ind}})\};

16

17

else \tau := \tau \cup \{(\mathcal{A}^{(m)}.\mathsf{output} \dashrightarrow Res_{v_{out}}.\mathsf{input}_{\mathsf{ind}})\}

18

19 foreach v_{out} \in V_{out} do \tau := \tau \cup \{(Res_{v_{out}}.output \dashrightarrow v_{out})\}

```

Step 1.1 - Controller for high-level control objectives. Line 1 associates the three high-level controller actors InUB, TrUB, IfTB with their corresponding pattern identifier. Implementations for the actors InUB, TrUB, IfTB are listed in Figure 3(b). For example, the actor IfTB is used for realizing  $\mathbf{G}(\mathsf{input} \to \mathsf{output})$  in Table 2. When input equals false, the output produced by this actor equals "–". This symbol is used as syntactic sugar for the set  $\{\mathsf{true}, \mathsf{false}\}$ . Therefore the output is unconstrained, that is, it is feasible for output to be either true or false. The value "–" is transferred in the dataflow, thereby allowing the delay of decisions when considering multiple specifications influencing the same output variable.

Step 1.2 - External I/O ports. Line 2 and 3 are producing external input and output port for each input variable  $v_{in} \in V_{in}$  and output variable  $v_{out} \in V_{out}$ .

Step 1.3 - High-level control controller instantiation. Lines 4 and 5 iterate through each specification  $\eta_m$  for finding the corresponding pattern (using DetectPattern). Based on the corresponding type, line 6 creates a high-level controller by copying the content stored in the map. If there exists a specification which does not match one of the patterns, immediately reject (line 7). Notice that pattern P4 is handled separately in Step 3. For the door example, the controller in Figure 3(a) contains the two copies  $TrUB^{(1)}$  and  $TrUB^{(2)}$  of the trigger-until actor TrUB; the subscripts of these copies are tracing the indices of the originating formulas (S1) and (S2).

Step 1.4 - Resolution Actors. This step is to consider all sub-specifications that influence the same output variable  $v_{out}$ . Line 9 to 11 adds, for each specification  $\eta_m$  using  $v_{out}$ , its index m maintained by  $\mathsf{map}_{out}.\mathsf{get}(v_{out})$ . E.g., for the door example, specifications S1, S3 and S4 all output out0. Therefore after executing line 10 and 11, we have  $\mathsf{map}_{out}.\mathsf{get}(\mathsf{out0}) = \{1, 3, 4\}$ , meaning that for variable out0, the value is influenced by S1, S3 and S4.

For each output variable  $v_{out}$ , line 12 creates one Resolution Actor  $Res_{v_{out}}$  which contains one parameter equaling the number of specifications using  $v_{out}$  in  $\varrho_{out}$ . Here we make it a simple memoryless controller as shown in Figure 3(b) -  $Res_{v_{out}}$  outputs true when one of its inputs is true, outputs false when one of its inputs is false, and outputs A (which is currently an unknown value to be synthesized later) when all inputs are "-". The number of input pins is decided by calling the map. E.g., for  $Res_{out0}$  in Figure 3(a), three inputs are needed because  $map_{out}$ ·get(out0).size()=3. The output of

Step 2: Synthesize monitoring controllers (for pattern P1, P2, P3)

```

Input : \phi = \varrho \to \bigwedge_{m=1...k} \eta_m, V_{in}, V_{out}, \mathcal{S} = (\mathcal{V}_{in}, \mathcal{V}_{out}, \overline{Act}, \tau) from Step 1.

Output: Actor-based (partial) controller S = (V_{in}, V_{out}, Act, \tau) by adding more elements

1 foreach \eta_m, m = 1 \dots k do

p := \mathsf{DetectPattern}(\eta_m);

\mathbf{2}

if p \in \{P1, P2, P3\} then

3

Add an OR-gate actor \mathsf{OR}_{\phi^i_{in}} with \mathsf{size}(\eta_m.\phi^i_{in}) inputs to Act;

4

foreach clause formula \chi_{in}^i from DNF of \eta_m.\phi_{in}^i do

5

Add \mathcal{A}(\mathcal{C}) to Act, where \mathcal{C} := \mathsf{Syn}(\mathbf{G}(\chi_{in}^i \leftrightarrow \mathbf{X}^i \mathsf{out}) \wedge \bigwedge_{z=0}^{i-1} \mathbf{X}^z \neg \mathsf{out}, \mathsf{In}(\chi_{in}^i), \{\mathsf{out}\});

6

foreach v_{in} \in In(\chi_{in}^i) do \tau := \tau \cup \{(v_{in} \to A(\mathcal{C}).v_{in})\}

7

\tau := \tau \cup \{(\mathcal{A}(\mathcal{C}).\mathsf{out} \dashrightarrow \mathsf{OR}_{\phi^i_{in}}.\mathsf{in}_{\mathsf{Index}(\chi^i_{in},\phi^i_{in})})\};

8

\tau := \tau \cup \{(\mathsf{OR}_{\phi^i_{i_n}}.\mathsf{out} \dashrightarrow \mathcal{A}^{(m)}.\mathsf{input})\};

9

if p \in \{P2\} then

10

Add an OR-gate actor \mathsf{OR}_{\varphi_{in}^j \vee \rho_{out}^0} with \mathsf{size}(\eta_m.(\varphi_{in}^j \vee \rho_{out}^0)) inputs to Act;

11

foreach clause formula \chi_{in}^h from DNF \eta_m.\varphi_{in}^j do

12

Add \mathcal{A}(\mathcal{C}) to Act, where \mathcal{C} := \mathsf{Syn}(\mathbf{G}(\chi_{in}^h \leftrightarrow \mathbf{X}^h \mathsf{out}) \wedge \bigwedge_{z=0}^{h-1} \mathbf{X}^z \neg \mathsf{out}, \, \mathsf{In}(\chi_{in}^h), \, \{\mathsf{out}\});

13

foreach v_{in} \in In(\chi_{in}^i) do \tau := \tau \cup \{(v_{in}) \to A(\mathcal{C}).v_{in})\} if h = 0 then Add

14

\begin{array}{l} (\mathcal{A}(\mathcal{C}).\mathsf{out} \dashrightarrow \mathsf{OR}_{\varphi_{in}^j \vee \rho_{out}^0}.\mathsf{in}_{\mathsf{Index}(\chi_{in}^z, \varphi_{out}^j)}) \ \mathsf{to} \ \tau \ \ \mathsf{else} \\ & \ \mathsf{Add} \ \mathcal{A}(\mathcal{C}_{\Theta_h}) \ \mathsf{to} \ \mathit{Act}, \ \mathsf{where} \ \mathcal{C}_{\Theta_h} := \mathsf{CreateThetaCtrl}(\mathsf{h}); \\ & \tau := \tau \cup \{(\mathsf{OR}_{\phi_{in}^j}.\mathsf{out} \dashrightarrow \mathcal{A}(\mathcal{C}_{\Theta_h}).\mathsf{set}), (\mathcal{A}(\mathcal{C}).\mathsf{out} \dashrightarrow \mathcal{A}(\mathcal{C}_{\Theta_h}).\mathsf{in}), (\mathcal{A}(\mathcal{C}_{\Theta_h}).\mathsf{out} \dashrightarrow \mathcal{A}(\mathcal{C}_{\Theta_h}).\mathsf{out} \\ \end{array}

15

16

\mathrm{OR}_{\varphi_{in}^{j}\vee\rho_{out}^{0}}.\mathrm{in}_{\mathrm{Index}(\chi_{in}^{z},\varphi_{in}^{j}\vee\rho_{out}^{0})})\};

foreach clause formula \chi_{out}^0 from DNF of \eta_m.\rho_{out}^0 do

17

Add an AND-gate actor \mathsf{AND}_{\eta_m \cdot \chi^0_{out}} with \mathsf{size}(\chi^0_{out}) inputs to Act;

18

for

each literal \omega_{out} of \chi^0_{out} do

19

let v_{out} be the variable used in \omega_{out};

20

if \omega_{out} equals \neg v_{out} (i.e., negation is used in literal) then

21

Create \neg_{Res_{v_{out}}} and add it to Act (if not exists in Act);

Add (Res_{v_{out}}.output \dashrightarrow \neg_{Res_{v_{out}}}.input) to \tau (if not exists in \tau);

Add (\neg_{Res_{v_{out}}}.output \dashrightarrow AND_{\chi_{out}^0}.in_{Index(\omega_{out},\chi_{out}^0)}) to \tau;

else \tau := \tau \cup \{Res_{v_{out}}.output \dashrightarrow AND_{\chi_{out}^0}.in_{Index(\omega_{out},\chi_{out}^0)}\}

22

23

24

25

\tau := \tau \cup \{\mathsf{AND}_{\chi_{out}^0}.\mathsf{out} \dashrightarrow \mathsf{OR}_{\varphi_{in}^j \vee \rho_{out}^0}.\mathsf{in}_{\mathsf{Index}(\chi_{out}^0, \varphi_{in}^j \vee \rho_{out}^0)}\}

26

\tau := \tau \cup \{\mathsf{OR}_{\phi_{in}^j \vee \rho_{out}^0}.\mathsf{out} \dashrightarrow \mathcal{A}^{(m)}.\mathsf{release}\};

27

```

the high-level controller  $A^{(m)}$  is connected to the input of  $Res_{v_{out}}$ . When negation is needed due to the negation symbol in  $\varrho_{out}$  (line 15), one introduces a negation actor  $\neg$  which negates  $A^{(m)}$  output when  $A^{(m)}$  input is true or false (line 16,17). To ensure that connections are wired appropriately, map<sub>out</sub> is used such that the number "ind" records the precise input port of the  $Res_{out}$  (line 14). Consider again the door example. Due to the maintained list  $\{1,3,4\}$ ,  $TrUB^{(1)}$  output is connected to  $Res_{v_{out}}$  input<sub>1</sub>, i.e., the first input pin of  $Res_{v_{out}}$ . Also, as  $\neg$ out0 is used in S3 and S4, the wiring from  $InUB^{(3)}$  and  $IfTB^{(4)}$  to  $Res_{out0}$  in Figure 3(a) has a negation actor in between.

Lastly, line 19 connects the output port of a resolution actor to the corresponding external output port. If  $Res_{v_{out}}$  receives simultaneously true and false from two of its input ports, then  $Res_{v_{out}}$  output needs to be simultaneously true and false. These kinds of situations are causing unrealizability of GXW specification, and Step 4 is used for detecting these kinds of inconsistencies.

#### 4.2 Monitors and and Phase Adjustment Actors

The second step of the algorithm synthesizes controllers for monitoring the appearance of an event matching the subformula, and connects these controllers to previously created actors for realizing high-level control objectives. For a formula  $\phi$  in DNF form, let  $size(\phi)$  return the number of clauses in

$\phi$ . For clause formula  $\chi_{in}^i$  in  $\phi$ , let  $\ln(\chi_{in}^i)$  return the set of all input variables and  $\alpha = \operatorname{Index}(\chi_{in}^i, \phi_{in}^i)$  specify that  $\chi_{in}^i$  is the  $\alpha$ -th clause in  $\phi_{in}^i$ .

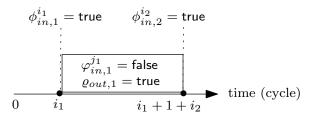

Step 2.1 - Realizing "input" part for pattern P1, P2, P3. In Step 2, from line 3 to 9, the algorithm synthesizes controller realizing the portion input listed in Table 2, or equivalently, the  $\phi^i_{in}$  part listed in Table 1. Line 4 first creates an OR gate, as the formula is represented in DNF. Then synthesize a controller for monitoring each clause formula (line 5, 6) using function Syn, with input variables defined in  $\ln(\chi^i_{in})$  and a newly introduced output variable  $\{\text{out}\}^2$ . The first attempt is to synthesize  $\mathbf{G}(\chi^i_{in} \leftrightarrow \mathbf{X}^i \text{out})$ . By doing so, the value of  $\chi^i_{in}$  is reflected in out. However, as the output of the synthesized controller is connected to the input of an OR-gate (line 8) and subsequently, passed through the port "input" of the high-level controller (line 9), one needs to also ensure that from time 0 to i-1, out remains false, such that the high-level controller  $\mathcal{A}_m$  for specification  $\eta_m$  will not be "unintentionally" triggered and subsequently restrict the output. To this end, the specification to be synthesized is  $\mathbf{G}(\chi^i_{in} \leftrightarrow \mathbf{X}^i \text{out}) \wedge \bigwedge_{z=0...i-1} \mathbf{X}^z \neg \text{out}$ , being stated in line 6.

For above mentioned property that needs to be synthesized in line 6, one does not need to use full LTL synthesis algorithms. Instead, we present a simpler algorithm (Algorithm 1) which creates a controller in time linear to the number of variables times the maximum number of  $\mathbf{X}$  operators in the formula. Here again for simplicity, each state variable is three-valued (true, false, u); in implementation every 3-valued state variable is translated into 2 Boolean variables. In the algorithm, state variable  $v_{in}[i]$  is used to store the i-step history of for  $v_{in}$ , and  $v_{in}[i] = \mathbf{u}$  means that the history is not yet recorded. Therefore, for the initial state, all variables are set to  $\mathbf{u}$  (line 4). The update of state variable  $v_{in}[i+1]$  is based on the current state of  $v_{in}[i]$ , but for state variable  $v_{in}[1]$ , it is updated based on current input  $v_{in}$  (line 17). With state variable recording previously seen values, monitoring the event is possible, where the value of out is based on the condition stated from line 6 to 16.

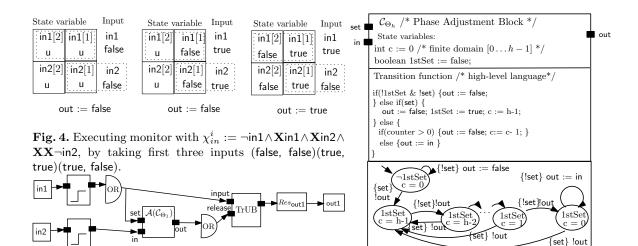

Consider a controller realizing  $\chi_{in}^i := \neg \text{in} 1 \land \text{Xin} 2 \land \text{XX} \neg \text{in} 2$ , being executed under a run prefix (false, false)(true, true)(true, false). As shown in Figure 4, the update of state variables is demonstrated by a left shift. The first and the second output are false. After receiving the third input, the controller is able to detect a rising edge of in1 (via in1[2]=false and in1[1]=true) is immediately followed by a falling edge of in2 (via in2[1]=true and in2=false).

Step 2.2 - Realizing "release" part for pattern P2. Back to Step 2, the algorithm from line 10 to 29 synthesizes a controller realizing the portion release listed in Table 2, or equivalently, the  $\varphi_{in}^j \vee \rho_{out}^0$  part listed in Table 1. The DNF structure is represented as an OR-actor (line 11), taking input from  $\varphi_{in}^j$  (line 12-18) and  $\rho_{out}^0$  (line 19-28).

For  $\rho_{out}^0$  (line 19-28), first create an AND-gate for each clause in DNF. Whenever output variable  $v_{out}$  is used, the wiring is established by a connection to the output port of  $Res_{v_{out}}$  (line 27). Negation in the literal is done by adding a wire to connect  $Res_{v_{out}}$  to a dedicated negation actor  $\Box_{Res_{v_{out}}}$  to negate the output (line 23 to 26). Consider, for example, specification S2 of the automatic door running example, where the "release" part (in1  $\lor$  in0  $\lor$  out0) is a disjunction of literals using output variable out0. As a consequence, one creates an AND-gate (line 20) which takes one input  $Res_{out0}$ .output (line 27), and connects this AND-gate to the OR-gate (line 28). Figure 3(a) displays an optimized version of this construction, since the single-input AND-gate may be removed and  $Res_{out0}$ .output is directly wired with the OR-gate.

For  $\varphi^j_{in}$  (line 12 to 23), similar to Step 2.1, one needs to synthesize a controller which tracks the appearance of  $\chi^h_{in}$  (line 13). However, the start of tracking is triggered by  $\phi^i_{in}$  (the input subformula). That is, whenever  $\phi^i_{in}$  is true, start monitoring if  $\varphi^j_{in}$  has appeared true. This is problematic when  $\chi^h_{in}$  contains  $\mathbf{X}$  operators (i.e., h > 0). To realize this mechanism, at line 19, the function CreateThetaCtrl additionally initiates a controller which guarantees the following: Whenever input variable set turns

For pattern type P2 or P3, one needs to have each clause formula of  $\phi_{in}^i$  be of form  $\chi_{in}^i$ , i.e., the highest number of consecutive **X** should equal i. The purpose is to align  $\chi_{in}^i$  with the preceding  $\mathbf{X}^i$  in  $\mathbf{G}(\phi_{in}^i \to \mathbf{X}^i(\varrho_{out}\mathbf{W}(\varphi_{in}^j \vee \rho_{out}^0))))$  or  $\mathbf{G}(\phi_{in}^i \to \mathbf{X}^i\varrho_{out})$ . If a clause formula in DNF contains no literal starting with  $\mathbf{X}^i$ , one can always pad a conjunction  $\mathbf{X}^i$  true to the clause formula. The padding is not needed for P1.

## Algorithm 1: Realizing Syn without full LTL synthesis

```

Input: LTL specification \mathbf{G}(\chi_{in}^i \leftrightarrow \mathbf{X}^i \text{out}) \wedge \bigwedge_{z=0}^{i-1} \mathbf{X}^z \neg \text{out}), input variables \ln(\chi_{in}^i), output

variables {out}

Output: Mealy machine C = (Q, q_0, \mathbf{2}^{V_{in}}, \mathbf{2}^{V_{out}}, \Delta) for realizing the specification

1 V_{out} := \{ \text{out} \}, V_{in} := \ln(\chi_{in}^i);

2 foreach Variable\ v_{in}\in \mathit{In}(\chi_{in}^i)\ \mathbf{do}\ //\ \mathsf{Create}\ \mathsf{all}\ \mathsf{state}\ \mathsf{variables}\ \mathsf{in}\ \mathsf{the}\ \mathsf{Mealy}\ \mathsf{machine}

for j = 1 \dots i do Q := Q \cup \{v_{in}[j]\}, where v_{in}[j] is three-valued (true, false, u)

4 q_0 := \bigwedge_{v_{in} \in \text{In}(\chi^i_{in}), j \in \{1, ...i\}} v_{in}[j] := \mathbf{u}

// Initial state;

5 let Cond := true;

6 foreach literal X^k v_{in} in \chi^i_{in} do

if k = i then

\mathsf{Cond} := \mathsf{Cond} \wedge (v_{in} = \mathsf{true})

9

else

\mathsf{Cond} := \mathsf{Cond} \wedge (v_{in}[i-k] = \mathsf{true})

10

11 foreach literal X^k \neg v_{in} in \chi_{in}^i do

12

if k = i then

Cond := Cond \land (v_{in} = false)

13

else

14

Cond := Cond \land (v_{in}[i-k] = \mathsf{false})

15

16 \delta_{out} := (\mathsf{out} := \mathsf{Cond})

// Output assignment should follow the value of Cond;

17 \delta_s := (\bigwedge_{v_{in} \in \ln(\chi_{in}^i), j=1...i-1} v_{in}[j+1] := v_{in}[j]) \wedge (\bigwedge_{v_{in} \in \ln(\chi_{in}^i)} v_{in}[1] := v_{in});

```

true, the following h output value of out is set to false. After that, the value of output variable out is the same as the input variable in. This property can be formulated as  $\Theta_h$  (to trigger consecutive h false value over out after seeing set = true) listed in Equation 2, with implementation shown in Figure 6. By observing the Mealy machine and the high-level transition function, one infers that the time for constructing such a controller in symbolic form is again linear to h.

$$\Theta_h := (\neg \mathsf{out} \, \mathbf{W} \, \mathsf{set}) \wedge \mathbf{G}(\mathsf{set} \to (\bigwedge_{z=0}^{h-1} \neg \mathbf{X}^z \mathsf{out} \wedge \mathbf{X}^h ((\mathsf{in} \leftrightarrow \mathsf{out}) \, \mathbf{W} \, \mathsf{set}))) \tag{2}$$

The overall construction in Step 2 is illustrated using the example in Figure 5, which realizes the formula

$$\mathbf{G}((\neg \mathsf{in1} \land \mathbf{X} \mathsf{in1}) \to \mathbf{X}(\mathsf{out1} \ \mathbf{W}(\neg \mathsf{in2} \land \mathbf{X} \mathsf{in2}))) \tag{3}$$

with  $V_{in} = \{\text{in1,in2}\}$  and  $V_{out} = \{\text{out1}\}$ . This specification requires to set output out1 to true when a rising edge of in1 appears, and after that, out0 should remain true until detecting a raising edge of in2. Using the algorithm listed in Step 2, line 6 synthesizes the monitor for the input part (i.e., detecting rising edge of in1), line 13 synthesizes the monitor for the release part (i.e., detecting rising edge of in2), line 14 creates the wiring from input port to the monitor. As h = 1 (line 16), line 17 creates  $\mathcal{A}(\mathcal{C}_{\Theta_1})$ , and line 18 establishes the wiring to and from  $\mathcal{A}(\mathcal{C}_{\Theta_1})$ .

The reader may notice that it is incorrect to simply connect the monitor controller for  $\neg in2 \land Xin2$  directly to TrUB.release, as, when both  $\neg in1 \land Xin1$  and  $\neg in2 \land Xin2$  are true at the same time, TrUB.output is unconstrained. On the contrary, in Figure 5, when  $\neg in1 \land Xin1$  is true and the value is passed through TrUB.input,  $\mathcal{A}(\mathcal{C}_{\Theta_1})$  enforces to invalidate the incoming value of TrUB.release for 1 cycle by setting it to false.

Step 3 - Realizing "input" for pattern P4. For pattern P4, in contrast to pattern P1, P2, and P3, the synthesized controller (following Step 3) is directly connected to a Resolution Actor. To maintain maximum freedom over output variable, one synthesizes the event monitor from the specification allowing the first i output to be -, via  $\bigwedge_{z=0}^{i-1} \mathbf{X}^z dc \wedge \mathbf{X}^i \mathbf{G} \neg dc$ . The construction is analogous to Algorithm 1.

Optimizations. Runtimes for Steps 2 and 3 may be optimized by using simple pattern matching and hashing of previously synthesized controllers. We are listing three different opportunities for

Fig. 5. Correct controller construction for specification sat- Fig. 6. Implementing  $\Theta_h$  (state variables not isfying pattern P2.

mentioned in update remain the same value).

optimized generation of monitors. First, the controller in Figure 3(a) for monitoring  $\neg in0 \land X in0$ is connected to two high-level controllers. The second case can be observed in Figure 5, where by rewriting in 1 and in 2 to in, the controller being synthesized is actually the same. Therefore, one can also record the pattern for individual monitor and perform synthesis once per pattern. A third opportunity for optimization occurs when Algorithm 1 takes i=0 (i.e., no **X** operator is used). In these case there is no need to create a controller at all and one may proceed by directly building a combinatorial circuit, similar to the constructions of line 19 to 28 in Step 2. For example, for specification S2 of the automatic door, the release part is in1 \(\sin \text{in0} \times \text{out0};\) since no X operator occurs, a combinatorial circuit is created by wiring directly | in1 | and | in0 | to the OR-gate.

#### Parameter Synthesis for 2QBF without Unroll

Step 3 as described above constructs actors as building blocks and wires the actors according to the structure of the given GXW specification. The resulting (partial) controller, however, does not yet realize this specification as it may still contain unknowns in the resolution actors. Further checks are necessary, and a controller is rejected if one of the following conditions holds.

(Condition 1) The wiring forms a directed loop in the constructed actor-based controller.

(Condition 2) It is possible for a resolution actor  $Res_{v_{out}}$  to receive true and false simultaneously. (Condition 3) Outputs violate invariance conditions of pattern P5.

Condition 1 is checked by means of a simple graph analysis: (1) let all ports be nodes and wirings be edges; (2) for each actor, create directed edges from each of its input port to each of its output port; (3) check if there exists a strongly connected component in the resulting graph using, for example, Tarjan's algorithm [29].

Conditions 2 and 3 are checked by means of creating corresponding 2QBF satisfiability problems. Recall that each resolution actor  $Res_{v_{out}}$  is parameterized with respect to the output A when all incoming inputs for  $Res_{v_{out}}$  are "—". The corresponding parameter assignment problem is encoded as a 2QBF<sup>3</sup> formula, where existential variables are the parameters to be synthesized, universal variables are input variables, and the quantifier-free body is a logical implication specifying that the encoding of the system guarantees condition 2 and 3.

Step 4 shows a simplified algorithm for generating 2QBF constraints which does not perform unrolling. Stated in line 15, the quantifier free formula is of form  $\Upsilon_a \to \Upsilon_g$ , where  $\Upsilon_a$  are input assumptions and system dynamics, and  $\Upsilon_q$  are properties to be guaranteed.

<sup>&</sup>lt;sup>3</sup> Quantified Boolean Formula with one top-level quantifier alternation.

**Step 3:** Synthesize monitoring controllers (for pattern P4)

```

Input: LTL specification \phi = \varrho \to \bigwedge_{m=1...k} \eta_m, V_{in}, V_{out}, actor-based (partial) controller

S = (V_{in}, V_{out}, Act, \tau) and \mathsf{map}_{out} from Step 2.

Output: Actor-based (partial) controller S = (V_{in}, V_{out}, Act, \tau) by adding more elements

1 foreach \eta_m, m = 1 \dots k do

if DetectPattern(\eta_m) \in \{P4\} then

Add a size(\eta_m.\phi_{in}^i)-input OR-gate actor \mathsf{OR}(\phi_{in}^i) to Act;

3

foreach clause formula \chi_{in}^i from DNF of \eta_m.\phi_{in}^i do

4

\mathcal{C}_{\chi} := \mathsf{Syn}((\mathbf{G}(\chi_{in}^i) \leftrightarrow \mathbf{X}^i \mathsf{out})) \wedge \bigwedge_{z=0}^{i-1} \mathbf{X}^z \mathsf{dc} \wedge \mathbf{X}^i \mathbf{G} \neg \mathsf{dc}, \, \mathsf{In}(\chi_{in}^i), \, \{\mathsf{out}, \, \mathsf{dc}\});

5

Add \mathcal{A}(\mathcal{C}_{\chi_{in}^i}) to Act;

6

for each v_{in} \in \mathit{In}(\chi_{in}^i) do \tau := \tau \cup \{(v_{in} \rightarrow \mathcal{A}(\mathcal{C}_{\chi_{in}^i}.v_{in}))\}

7

\tau := \tau \cup \{(\mathsf{OR}_{\phi^i_{in}}.\mathsf{out} \dashrightarrow Res_{v_{out}}.\mathsf{input}_i)\};

8

let v_{out} be the variable used in \tau_m.\varrho_{out}, ind := map<sub>out</sub>.get(v_{out}).indexOf(m);

9

if \varrho_{out} equals \neg v_{out} then // negation is used in literal Create a negation actor \boxed{}^{(m)} and add it to Act; Add (\mathsf{OR}_{\phi^i_{in}}.\mathsf{out} \dashrightarrow \boxed{}^{(m)}.\mathsf{in}), (\boxed{}^{(m)}.\mathsf{output} \dashrightarrow Res_{v_{out}}.\mathsf{input}_{\mathsf{ind}}) to \tau; else Add (\mathsf{OR}_{\phi^i_{in}}.\mathsf{out} \dashrightarrow Res_{v_{out}}.\mathsf{input}_{\mathsf{ind}}) to \tau

10

11

12

13

```

First, unknown parameters are added to the set of existential variables  $V_{\exists}$  (line 2). All other variables are universal variables. Then based on the evaluation ordering of S, perform one of the following tasks:

- When an element  $\xi$  in the execution ordering  $\Xi$  is a wire (line 5), we add source and dest as universal variables (as  $V_{\forall}$  is a set, repeated variables will be neglected), and establish the logical constraint (source  $\leftrightarrow$  dest) (lines 6 to 8).

- When an element  $\xi$  in the execution ordering  $\Xi$  is an actor, we use function EncodeTransition to encode the transition (pre-post) relation as constraints (line 11), and add all state variables (for pre and post) in the actor (recall our definition of Mealy machine is based on state variables) to  $V_{\forall}$  using function GetStateVariable (line 10).

$\Upsilon_a$  is initially set to  $\varrho$  (line 1) to reflect the allowed input patterns regulated by the specification (specification type P6). Line 12 creates the constraint stating that no two inputs of a resolution actor should create contradicting conditions. As the number of input ports for any resolution actor is finite, the existential quantifier is only an abbreviation which is actually rewritten to a quantifier-free formula describing relations between input ports of a resolution actor.

The encoding presented in Step 4 does not involve unroll (it encodes the transition relation, but not the initial condition). Therefore, by setting all variables to be universally quantified, one approximates the behavior of the system dynamics without considering the relation between two successor states. Therefore, using Step 4 only guarantees *soundness*: If the formula is satisfiable, then the specification is realizable (line 15, 16). Otherwise, unknown is returned (line 17).<sup>4</sup>

As each individual specification of one of the types  $\{P1, P2, P3, P4\}$  is trivially realizable, the reason for rejecting a specification is (1) simultaneous true and false demanded by different subspecifications, (2) violation of properties over output variables (type P5), and (3) feedback loop within S. Therefore, as Steps 1-4 guarantees non-existence of above three situations, the presented method is *sound*.

**Theorem 1.** (Soundness) Let  $\phi$  be a GXW specification, and S be an actor-based controller as generated by Steps 1-4 from  $\phi$ ; then S realizes  $\phi$ .

<sup>&</sup>lt;sup>4</sup> Even without unroll, one can infer relations over universal variables via statically analyzing the specification. As an example, consider two sub-specifications  $S1: \mathbf{G}(\mathsf{in1} \to (\mathsf{out}\,\mathbf{W}\,\mathsf{in2}))$  and  $S2: \mathbf{G}(\mathsf{in2} \to (\neg\mathsf{out}\,\mathbf{W}\,\mathsf{in1}))$ . One can infer that it is impossible for  $TrUB^{(1)}$  and  $TrUB^{(2)}$  to be simultaneously have state variable  $lock = \mathsf{true}$ , as both starts with  $lock = \mathsf{false}$ , and if S1 first enters lock ( $lock = \mathsf{true}$ ) due to in1, the S2 cannot enter, as release part of S2 is also in1. Similar argument follows vice versa.

Step 4: Parameter synthesis by generating 2QBF constraints

```

Input: LTL specification \phi = \varrho \to \bigwedge_{m=1...k} \eta_m, input variables V_{in}, output variables V_{out}, partial

controller implementation S = (V_{in}, V_{out}, Act, \tau) with unknown parameters

Output: Controller implementation S or "unknown"

1 let \Upsilon_a := \varrho, \Upsilon_q := \mathsf{true}, V_\exists, V_\forall := \mathsf{NewEmptySet}();

2 foreach v_{out} \in V_{out} do V_{\exists} := V_{\exists} \cup \{Res_{v_{out}}.A\}

3 let \Xi be the evaluation ordering of S;

foreach \xi \in \Xi do

if \xi \in \tau then // \xi is w wire; encode biimplication among two ports

5

Let \xi be (source ---> dest);

6

V_{\forall}.add(source), V_{\forall}.add(dest);

7

\Upsilon_a := \Upsilon_a \wedge (\mathsf{source} \leftrightarrow \mathsf{dest});

8

9

else

V_{\forall}.add(\mathsf{GetStateVariable}(\xi));

10

\Upsilon_a := \Upsilon_a \wedge (\mathsf{EncodeTransition}(\xi)) / \xi \in Act * / ;

11

\textbf{12 for } v_{out} \in V_{out} \ \textbf{do} \ \ \varUpsilon_g := \varUpsilon_g \land (\not \exists i,j: (Res_{v_{out}}.\mathsf{input}_i = \mathsf{true}) \land (Res_{v_{out}}.\mathsf{input}_j = \mathsf{false}))

13 foreach \eta_m, m = 1 \dots k do

\textbf{if DetectPattern}(\eta_m) \in \{P5\} \ \textbf{then} \ \ \varUpsilon_g := \varUpsilon_g \wedge \eta_m

15 if Solve2QBF(V_\exists,V_\forall,\varUpsilon_a	o\varUpsilon_g).isSatisable then

return S by replacing each Res_{out}. A by the value of witness in 2QBF;

17 else return unknown

```

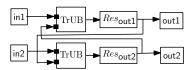

The GXW synthesis algorithm as described above, however is *incomplete*, as controllers with feedback loops are rejected; that is, whenever output variables listed in the release part of P2 necessitate simultaneous reasoning over two or more output variables. Figure 7 display an controller (with feedback loop) for realizing the specification  $\mathbf{G}(\mathsf{in1} \to (\mathsf{out1Wout2})) \land \mathbf{G}(\mathsf{in2} \to (\mathsf{out2Wout1}))$ . However, our workflow rejects such a controller even though the given specifi-

Fig. 7. Incompleteness example.

cation is realizable. With further structural restriction over GXW (which guarantees no feedback loop in during construction) and by using unrolling of the generated actor-based controllers, the workflow as presented here can be made to be *completeness*, as demonstrated in Section 4.4.

(Remarks) Notice that in the presented algorithm, the synthesized controller does not contain a detector for checking if environment assumption (type P6) is violated. Practically, input assignments violating P6 should never appear. If such a violation is possible, then immediately after the assumption violation and from that time onwards, the controller is allowed to produce arbitrary output assignment<sup>5</sup>. Here we omit details, but would like to stress that one can easily mediate such scenarios by several ways. E.g., one can append a detection actor (by building a combinational circuit out of the specification type P6) to detect the event whether the environment assumption is violated. At the same time, provide an additional input port on every resolution actor to override the output (i.e., a resolution actor should consider first if environment assumption is violated: if so, then continuously output false), and link the detection actor with the newly created port.

Also, there are unlikely scenarios such as declaring output variables without having them used in any specification. One can mediate it by always connecting a wire from one input port to the output port of a unused output variable, without building a resolution actor. The presented algorithm here also omits details of such corner cases.

#### 4.4 General Properties for GXW Synthesis

Since unrealizability of a GXW specification is due to the conditions (1) simultaneous true and false demanded by different sub-specifications, and (2) violation of properties over output variables (type

<sup>&</sup>lt;sup>5</sup> In practice, if a violation is possible, it should be captured and handled properly; it is never the case that output variables are allowed to be assigned with arbitrary value.

P5)<sup>6</sup>, one can build a counter-strategy<sup>7</sup> by first building a tree that provides input assignments to lead all runs to undesired states violating (1) or (2), then all leafs of the tree violating (1) or (2) are connected to a self-looped final state, in order to accept  $\omega$ -words. As the input part listed in Table 2 does not involve any output variable, a counter-strategy, if exists, can lead to violation of (1) or (2) within  $\Omega$  cycles, where  $\Omega$  is a number sufficient to let each input part of the sub-specification be true in a run.

**Lemma 1.** For GXW specification  $\varrho \to \bigwedge_{m=1...k} \eta_m$ , if (a)  $\rho_{out}^0$  is false for all  $\eta_m$  of type P2 and (b) no specification of type P5 exists, then if the specification is not realizable, then there exists a counter-strategy which leads to violation of (1) or (2) in  $\Omega$  steps, where  $\Omega$  is bounded by the sum of (i) the number of specifications k, and (ii) the sum of all i value defined within each  $\phi_{in}^i$  of  $\eta_m$ .

When  $\rho_{out}^0$  is false for all  $\eta_m$  of type P2, our presented construction guarantees no feedback loop. As no specification of type P5 exists, the selection of A never influences whether the specification is realizable. Therefore, quantifier alternation is removed. To this end, checking unrealizability is equivalent to nondeterministically guessing  $\Omega$  input assignments and subsequently, checking if a violation of (1) or (2) appears by executing S. This also means that under the restriction from Lemma 1, a slight modification of Step 4 to perform unrolling the computation  $\Omega$ -times makes our synthesis algorithm complete.

Fig. 8. Control implementation.

**Lemma 2.** Deciding whether a given GXW specification, which also obeys the additional restrictions as stated in Lemma 1, is realizable or not is in co-NP.

For the general case, the bound in Lemma 1 remains valid (as input part is not decided by the output variable). Complexity result is achieved by, without using our construction, directly using finite memory to store and examine all possible control strategies in  $\Omega$  steps.

**Lemma 3.** For GXW specification  $\varrho \to \bigwedge_{m=1...k} \eta_m$ , if the specification is not realizable, then there exists a counter-strategy which leads to violation of (1) or (2) in  $\Omega$  steps, where  $\Omega$  is bounded by condition similar to Lemma 1.

Lemma 4. Deciding whether a given GXW specification is realizable or not is in PSPACE.

The above mentioned bounds are only conditions to detect realizability of a GXW specification, while our presented workflow in Section 4 targets generating structured implementations. Still, by unrolling the computation  $\Omega$ -times, one can detect if a controller, following our regulated structure, exists.

#### 4.5 Extensions

One can extend the presented workflow to allow richer specification than previously presented GXW fragment. Here we outline how these extensions are realized by considering the following sample specification:  $\mathbf{G}(\mathsf{in1} \to \mathsf{out1}) \land \mathbf{G}((\mathsf{in2} \lor \mathsf{out1}) \to ((\mathsf{out2} \land \neg \mathsf{out3})\mathbf{W} \mathsf{in3}))$ . The SDF controller implementation is shown in Figure 8. First, conjunctions in  $\varrho_{out}$  can be handled by considering each output variable separately. E.g., for  $\varrho_{out} \equiv \mathsf{out2} \land \neg \mathsf{out3}$ , in Figure 8 both are connected to the same TrUB. Second, the use of output variables in "input" part for pattern P1, P2, P3 is also supported, provided that in effect a combinatorial circuit is created (i.e., output variables should always proceed with  $\mathbf{X}^i$ ), and the generated system does not create a feedback loop. E.g., for the antecedent (in2  $\lor$  out1), it is created by wiring the  $Res_{out1}$  out to an OR-gate.

<sup>6</sup> Rejecting feedback loops on the controller structure is only a restriction of our presented method and is not the reason for unrealizability; similar to Figure 7, feedback loop can possibly be resolved by merging all actors involving feedback to a single actor.

<sup>7</sup> A counter-strategy in LTL synthesis a state machine where the environment can enforce to violate the given property, regardless of all possible moves by the controller [27].

## 5 Experimental Evaluation

We implemented a tool for GXW synthesis in Java, which invokes DepQBF [21] (Version 5.0) for QBF solving. Table 3 includes experimental results for a representative subset of our PLC benchmark examples. Execution times is recorded using Ubuntu VM (Virtual Box with 3GB RAM) running on an Intel i7-3520M 2.9 Ghz CPU and 8GB RAM). Most control problems are solved in less than a second<sup>8</sup>. GXW synthesis always generated a controller without feedback loops for all examples.

Table 3 lists a comparison of execution times of GXW synthesis and the bounded LTL synthesis tool Acacia+ [8] (latest version 2.3). We used the option <code>--player 1</code> of Acacia+ for forcing the environment to take a first move, but we did not do manual annotation in order to support compositional synthesis in Acacia+, as it is not needed by our tool. For many of the simpler case studies, the reported runtimes of Acacia+ are similar to GXW synthesis. However, GXW seems to scale much better to more complex case studies with a larger number of input and output variables such as examples 5, 9, 11, 12, 13, 15, 16, 17, 18, 19 in Table 3. The representation of the generated controller in terms of a system of interacting actors in GXW synthesis, however, allows the engineering to trace each sub-specification with corresponding partial implementation. In fact the structure of the controllers generated by GXW is usually similar to reference implementations by the case study providers. In contrast, a controller expressed in terms of single Mealy machine is rather difficult to grasp and to maintain for problems such as example 18 with 13 input and 13 output variables.

## 6 Related Work

Apart from the description in Section 1, here we compare GXW synthesis with related GR(1) synthesis (e.g., [15,25,31,5]) and bounded LTL synthesis (e.g., [8,11,28]) techniques.

Synthesis for the GR(1) fragment of LTL is in time polynomial to the number of nodes of a generated game, which is EXPTIME when considering exponential blow-up caused by input and output variables. GXW is in PSPACE, where GXW allows W and GR(1) allows F. Even though it has been demonstrated that the expressiveness of GR(1) is enough to cover many practical examples, the use of an until logical operator, which is not included in GR(1), proved to be essential for encoding a majority of our PLC case studies. Also, implementations of GR(1) synthesis such as Anzu [15] do not generate structured controllers. Since GR(1) synthesis, however, includes a round-robin arbiter for circulating among sub-specifications, the systematic structuring of controllers underlying GXW synthesis may be applicable for synthesizing structured GR(1) controllers.

Bounded synthesis supports full LTL and is based on a translation of the LTL synthesis problem to safety games. By doing so, one solves the safety game and finds smaller controllers (as demonstrated in synthesis competitions via tools like Simple BDD solver [13], AbsSynthe [9], Demiurge [17]). The result of solving safety games in bounded LTL synthesis usually is a monolithic Mealy (or Moore) machine, whereas our GXW synthesis method of creating SDF actors may be understood as a way of avoiding the expensive construction of the product of machines. Instead, we are generating controllers by means of wiring smaller sub-controllers for specific monitoring and event triggering tasks. The structure of the resulting controllers seem to be very close to what is happening in practice, as a number of our industrial benchmark examples are shipped with reference implementation which are usually structured in a similar way. The size of the representations of generated controllers is particularly important when considering resource-bounded embedded computing device such as a PLCs. LTL component synthesis, however, has the same worst-case complexity as full LTL synthesis [22].

#### 7 Conclusion

We have identified a useful subclass GXW of LTL for specifying a large class of embedded control problems, and we developed a novel synthesis algorithm (in PSPACE) for automatically generating structured controllers in a high-level programming language with synchronous dataflow without

<sup>&</sup>lt;sup>8</sup> Approximately 0.25 seconds is used for initializing JVM in every run.

| ID | Description                                        | Source          | I/O vars | GXW Time (s) | Acacia+ Time (s) |

|----|----------------------------------------------------|-----------------|----------|--------------|------------------|

| 1  | Automatic Door                                     | Ex15 [2]        | (4,3)    | 0.389        | 0.180            |

| 2  | Simple Conveyor Belt                               | Ex7.1.19 [24]   | (3,3)    | 0.556        | 0.637            |

| 3  | Hydraulic Ramp                                     | Ex7.1.3[24]     | (5,2)    | 0.642        | 0.451            |

| 4  | Waste Water Treatment V1                           | Ex7.1.8 [24]    | (6,3)    | 0.471        | 0.323            |

| 5  | Waste Water Treatment V2                           | Ex7.1.9 [24]    | (8,9)    | 0.516        | 5.621            |

| 6  | Container Fusing                                   | Ex10 [2]        | (7,6)    | 0.444        | 0.425            |

| 7  | Elevator Control Mixing Plant                      | Ex7.1.4 [24]    | (10,5)   | 0.484        | 2.902            |

| 8  | Lifting Platform                                   | Ex21 [16]       | (6,3)    | 0.350        | 0.645            |

| 9  | Control of Reversal                                | Ex36 [16]       | (7,7)    | 0.395        | 2.901            |

| 10 | Gear Wheel                                         | Ex19 [16]       | (4,6)    | 0.447        | 0.302            |

| 11 | Two Directional Conveyor (simplified)              | Ex7.1.31.1 [24] | (9,5)    | 0.789        | 6.552            |

| 12 | Garage Door Control                                | Ex7.1.25 [24]   | (13,5)   | 0.574        | 7.002            |

| 13 | Contrast Agent Injection                           | Ex7.1.18 [24]   | (6,8)    | 0.458        | 3.209            |

| 14 | Identification                                     | Ex39 [16]       | (5,5)    | 0.430        | 0.392            |

| 15 | Monitoring Chain Elevator                          | Ex7.1.15[24]    | (10,9)   | 0.429        | 9.647            |

| 16 | Two Directional Conveyor                           | Ex7.1.31.1 [24] | (12,5)   | 0.890        | 51.553           |

| 17 | Control of single torque drive (simplified)        | Ex7.1.26 [24]   | (12,8)   | 0.538        | 38.010           |

| 18 | Gravel transportation via 3 conveyors (simplified) | Ex7.1.31.4 [24] | (13,13)  | 1.227        | > 600 (t.o.)     |

| 19 | Control of two torque drives (simplified)          | Ex7.1.26 [24]   | (22,16)  | 0.790        | > 600 (t.o.)     |

Table 3. Experimental Result

cycles. Our experimental results suggest that GXW synthesis scales well to industrial-sized control problems with around 20 input and output ports and beyond.

In this way, GXW synthesis can readily be integrated with industrial design frameworks such as CODESYS [3], Matlab Simulink, and Ptolemy II, and the generated SDF controllers (without cycles) can be statically scheduled and implemented on single and multiple processors [18]. It would also be interesting to use our synthesis algorithms to automatically generate control code from established requirement frameworks for embedded control software such as EARS[23]. Moreover, our presented method supports traceability between specifications and the generated controller code as required by safety-critical applications. Traceability is also the basis for an incremental development methodology.

One of the main impediments of using synthesis in engineering practice, however, is the lack of useful and automated feedback in case of unrealizable specifications [6,10,20] or realizable specifications with unintended realizations. The use of a stylized specification languages such as GXW seems to be a good starting point for supporting design engineers in identifying and analyzing unrealizable specifications, since there are only a relatively small number of potential sources of unrealizability in GXW specifications<sup>9</sup>. Finally, hierarchical SDF may also be useful for modular synthesis [30].

## Acknowledgement

We thank Lăcrămioara Aştefănoaei for her feedback during the development of the paper.

### References

- 1. The automatic door example is adapted from http://plc-scada-dcs.blogspot.com/2014/08/basic-plc-ladder-programming-training\_20.html.

- 2. Online training material for PLC programming. http://plc-scada-dcs.blogspot.com/.

- 3. CODESYS industrial IEC 61131-3 PLC programming framework http://www.codesys.com/.

- 4. Simulink Simulation and Model-Based Design http://www.mathworks.com/products/simulink/.

- R. Bloem, A. Cimatti, K. Greimel, G. Hofferek, R. Knighofer, M. Roveri, and R. Seeber. RATSY a new requirements analysis tool with synthesis. In: CAV, volume 6174 of LNCS, pages 425–429. Springer, 2010.

- R. Bloem, R. Ehlers, S. Jacobs, R. Knighofer: How to Handle Assumptions in Synthesis. In: SYNT, pages 34–50, EPTCS 157, 2014.

Observe the example in the paper, closing\_stopped contains out0. This is the only part that is not mentioned in the textural specification, but it is required to make the specification realizable. Introducing out0 needs creativity, and it is the part where one needs an engineer in the loop. Not mentioned in this paper, we are also developing concepts in order to automatically add such a disjunction, similar to discovery of environment assumptions as investigated by us and also by others (e.g., [20]).

- 7. R. Bloem, B. Knighofer, R. Knighofer, C. Wang. Shield Synthesis: Runtime Enforcement for Reactive Systems. In: *TACAS*, volume 9035 of *LNCS*, pages 533–548. Springer, 2015.

- 8. A. Bohy, V. Bruyère, E. Filiot, N. Jin, and J. Raskin. Acacia+, a tool for LTL synthesis. In: *CAV*, volume 7358 of *LNCS*, pages 652–657. Springer, 2012.

- 9. R. Brenguier, G. A. Prez, J.-F. Raskin, O. Sankur AbsSynthe: abstract synthesis from succinct safety specifications In SYNT, EPTCS 157, pages 100-116, 2014.

- C.-H. Cheng, C.-H. Huang, H. Ruess, and S. Stattelmann. G4LTL-ST: automatic generation of PLC programs. In: CAV, volume 8559 of LNCS, pages 541–549. Springer, 2014.

- 11. R. Ehlers. Unbeast: Symbolic bounded synthesis. In: *TACAS*, volume 6605 of *LNCS*, pages 272–275. Springer, 2011.

- 12. J. Eker, J. Janneck, E. A. Lee, J. Liu, X. Liu, J. Ludvig, S. Sachs, Y. Xiong. Taming heterogeneity the Ptolemy approach Proceedings of the IEEE, 91(1):127-144 (2003).

- S. Jacobs, R. Bloem, R. Brenguier, R. Ehlers, T. Hell, R. Knighofer, G. A. Prez, J.-F. Raskin, L. Ryzhyk,

O. Sankur, M. Seidl, L. Tentrup, A. Walker. The First Reactive Synthesis Competition. (SYNTCOMP 2014). http://arxiv.org/abs/1506.08726

- 14. B. Jobstmann and R. Bloem. Optimizations for LTL synthesis. In: FMCAD, pages 117-124. IEEE, 2006.

- 15. B. Jobstmann, . Galler, M. Weiglhofer, and R. Bloem. Anzu: A tool for property synthesis. In: *CAV*, volume 4590 of *LNCS*, pages 258–262. Springer, 2007.

- 16. J. Kaftan. Praktische Beispiele mit AC500 von ABB: 45 Aufgaben und Lsungen mit CoDeSys. http://pwww.kaftan-media.com/ISBN 978-3-943211-05-4, 2014.

- 17. R. Knighofer, M. Seidl. Demiurge 1.2: A SAT-Based Synthesis Tool. Tool description for the Synt-Comp'15 competition.

- 18. E. A. Lee, D. G. Messerschmitt: Static Scheduling of Synchronous Data Flow Programs for Digital Signal Processing. IEEE Trans. Computers 36(1): 24-35 (1987).

- 19. E. A. Lee and D. G. Messerschmitt: Synchronous Data Flow. Proceedings of the IEEE, 75(9):1235-1245 (1987).

- 20. W.-C. Li. Specification Mining: New Formalisms, Algorithms and Applications. Ph.D. Thesis. UC Berkeley, 2015.

- 21. F. Lonsing, A. Biere. DepQBF: A dependency-aware QBF solver. Journal on Satisfiability, Boolean Modeling and Computation, 7, 71–76. (2010).

- 22. Y. Lustig, M. Y. Vardi: Synthesis from component libraries. STTT 15(5-6):603-618 (2013).

- A. Mavin, P. Wilkinson, A. Harwood, M. Novak: Easy Approach to Requirements Syntax (EARS). In: RE, pages 317–322. IEEE, 2009

- 24. J. Petry. IEC 61131-3 mit CoDeSys V3: Ein Praxisbuch fuer SPS-Programmierer. Eigenverlag 3S-Smart Software Solutions, ISBN 978-3-000465-08-6, 2011.

- 25. N. Piterman, A. Pnueli, Y. Sa'ar. Synthesis of Reactive(1) Designs. In: *VMCAI*, volume 3855 of *LNCS*, pages 364–380. Springer, 2006.

- 26. A. Pnueli. The temporal logic of programs. In: FOCS, pages 46–57. IEEE, 1977.

- 27. A. Pnueli, R. Rosner, On the Synthesis of a Reactive Module. In: POPL, pages 179–190. IEEE, 1989.

- S. Schewe and B. Finkbeiner. Bounded synthesis. In: ATVA, volume 4762 of LNCS, pages 474–488.

Springer, 2007.

- 29. R. E. Tarjan. Depth-first search and linear graph algorithms. SIAM Journal on Computing 1(2):146-160 (1972).

- 30. S. Tripakis, D. N. Bui, M. Geilen, B. Rodiers, E. A. Lee. Compositionality in synchronous data flow: Modular code generation from hierarchical SDF graphs. ACM Trans. on Embedded Computing Systtems 12(3): 83 (2013).

- 31. K.-W. Wong, R. Ehlers, and H. Kress-Gazit. Correct High-level Robot Behavior in Environments with Unexpected Events Robotics: Science and Systems X (RSS X), 2014.

# Appendix

## A Operational Semantics of SDF