# Well-Posed Models of Memristive Devices

Tianshi Wang and Jaijeet Roychowdhury

Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, CA, USA email: {tianshi, jr}@berkeley.edu

#### Abstract

Existing compact models for memristive devices (including RRAM and CBRAM) all suffer from issues related to mathematical ill-posedness and/or improper implementation. This limits their value for simulation and design and in some cases, results in qualitatively unphysical predictions. We identify the causes of ill-posedness in these models. We then show how memristive devices in general can be modelled using only continuous/smooth primitives in such a way that they always respect physical bounds for filament length and also feature well-defined and correct DC behaviour. We show how to express these models properly in languages like Verilog-A and ModSpec (MATLAB<sup>®</sup>). We apply these methods to correct previously published RRAM and memristor models and make them well posed. The result is a collection of memristor models that may be dubbed "simulation-ready", *i.e.*, that feature the right physical characteristics and are suitable for robust and consistent simulation in DC, AC, transient, *etc.*, analyses. We provide implementations of these models in both ModSpec/MATLAB<sup>®</sup> and Verilog-A.

## I. Introduction

In 1971, Leon Chua noted [1] that while two-terminal circuit elements relating voltage and current (*i.e.*, resistors), voltage and charge (capacitors) and current and flux (inductors) were well known, no element that directly relates charge and flux seemed to exist. He explored the properties of this hypothetical element and found that its voltage-current characteristics would be those of a resistor, but that if the element were nonlinear, its resistance would change with time and be determined by the history of biasses applied to the device. In other words, the instantaneous resistance of the element would retain some memory of past inputs. Chua dubbed this missing element a "memristor", and showed that a telltale characteristic was that its *i*-*v* curves would always pass through (0,0), regardless of how it was biassed as a function of time.<sup>1</sup> Long after Chua's landmark observation, devices with memristive behaviour were found in nature, *e.g.*, in the well-publicized nano-crossbar device of Stan Williams and colleagues [2, 3], and others as well [4, 5]. It was also realized that many physically observed devices prior to [2, 3] were in fact memristors [6–8].

Physically, present-day memristive nano-devices typically operate by forming and destroying conducting filaments through an insulating material sandwiched between two contacts separated by a small distance l. The conducting filaments can be of different types. For example, they can consist of oxide vacancies, by filling which electrons can flow, as in RRAM (Resistive Random Access Memory [9]). In CBRAM (Conductive Bridging RAM [10]), metal ions<sup>2</sup> that infiltrate the insulator form the conducting filament. In memristors made of Si-impregnated silica [11], conduction occurs via tunnelling between traps. Depending on the magnitude and polarity of the voltage applied, the conducting filaments can lengthen or shorten; it is their length that determines the resistance of the device. Basic geometry indicates that the length of the filament(s) must always be between zero (*i.e.*, there is no filament) and the distance between the contacts (*i.e.*, the filament connects the two contacts) — in other words, the length of the filament(s) must never be outside the range [0, l]. Another basic property is that when the voltage across the device has one polarity (say positive), the filament grows until it reaches its maximum length l, at which it settles; whereas for the opposite polarity (say negative), the filament shrinks until it reaches its minimum length 0. Therefore, if a positive DC voltage is applied, the DC (*i.e.*, long term) response of the memristor's filament length must be l; whereas if a negative DC voltage is applied, its DC response must be 0.

<sup>&</sup>lt;sup>1</sup>*i.e.*, a memristor's i-v characteristics are "pinched" at the origin.

<sup>&</sup>lt;sup>2</sup>various metals, including Cu, Ag, W, Sn and Cr, have been used.

A number of novel circuits based on memristors have been proposed [12, 13], most of which use crossbar architectures for non-volatile memory [14, 15] and neuromorphic computing [16–18] applications. To support their design, various compact models of memristors, purportedly suitable for simulation in SPICE-like simulators, have been published. However, our attempts to use these models have revealed shortcomings serious enough to preclude their general use for simulation or design. Broadly speaking, these existing models suffer from *ill-posedness* issues; *e.g.*, they are not properly defined at all biasses, or their outputs are not unique, or they suffer from continuity/smoothness problems. Well-posedness [19, 20]<sup>3</sup> is a fundamental requirement for models meant to represent physical reality and is also crucial for numerical algorithms using the models to work properly.

The well-posedness requirement applies not only to memristive devices, but to any model meant for simulation. To appreciate why, it is important to realize that a model represents a *mathematical abstraction* of a physical device. While this abstraction must represent reality well enough to be useful for prediction, it must also be suitable for use with numerical simulation algorithms. To be so, it needs to satisfy certain important mathematical properties, the most basic and universal of which is well posedness.

To illustrate how a well-posed mathematical model must often be "more than" the physical device it represents, consider the question: is it necessary to model a device outside regions that are physically reasonable in proper operation?<sup>4</sup> For example, should a compact model of a memristor (or a diode, or resistor, or IC MOSFET), be "valid" at a bias of a million volts (at which, in reality, most physical devices would simply burn up)? The answer to this question is yes – indeed, it has been a standard requirement for device models (including resistors, capacitors, diodes, BJT and MOS devices, *etc.*) in SPICE-like simulators to evaluate successfully and provide unique, smoothly varying outputs at all biasses, including large, physically unrealistic, biasses. These requirements stem not only from the numerical algorithms used by simulators (in particular, the Newton-Raphson (NR) algorithm for solving nonlinear equations [21]), but also from the iterative methodology using which circuits are typically designed:

- 1) In the process of converging to a valid solution of the circuit, NR typically applies a sequence of biasses to devices; many of these biasses can be large or physically unreasonable. Compact models must be designed to evaluate successfully and be smooth at *every* bias applied, whether it is physically reasonable or not, in order for NR to go about trying to find a solution [22, 23]. If devices are modelled well and the circuit has been designed properly, then, *at the solution found by NR*, biasses to devices can be expected to be physically reasonable.

- 2) Even if NR converges to a solution that is physically unreasonable, the "bad" solution has value in circuit design, for it typically provides quantitative insight into what is wrong with the design. A compact model that refuses to evaluate or generates a floating-point error prevents such solutions, and the insights they provide, from being found.

Common ill-posedness mechanisms in models include division-by-zero errors, often due to expressions like  $\frac{1}{x-a}$ , which become unbounded (and feature a "doubly infinite" jump) at x=a; the use of log() or  $\sqrt{()}$  without ensuring that their arguments are always positive, regardless of bias; the fundamental misconception that non-real (*i.e.*, complex) numbers or infinity are legal values for device models (they are not!); and "sharp"/"pointy" functions like |x|, whose derivatives are not continuous.

Another key aspect of well-posedness is that the model's equations must produce mathematically valid outputs for any mathematically valid input to the device. Possibly the most basic kind of input is one that is constant ("DC") for all time. DC solutions ("operating points") are fundamental in circuit design; they are typically the kind of solution a designer seeks first of all, and are used as starting points for other analyses like transient, small signal AC, *etc*. If a model's equations do not produce valid DC outputs given DC inputs, it fails a very fundamental well-posedness requirement. For example, the equation  $\frac{d}{dt}o(t) = i(t)$  is ill posed, since no DC (constant) solution for the output o(t) is possible if the input i(t) is any non-zero

$<sup>^{3}</sup>$ A well-posed mathematical model of a physical device should have the properties that a unique solution or output should exist for any given input, and that outputs should vary smoothly with respect to inputs and parameters.

<sup>&</sup>lt;sup>4</sup>This is a frequent point of confusion amongst compact model developers.

constant. Such ill posedness is typically indicative of some fundamental physical principle being violated; for example, in the case of  $\frac{d}{dt}o(t) = i(t)$ , the system is not strictly stable [24]. Indeed, a well-posed model that is properly written and implemented should work consistently in every analysis (including DC, transient, AC, *etc.*).<sup>5</sup>

In spite of seemingly significant efforts to devise memristor models, *every* model we are aware of<sup>6</sup> in the literature [25–30] suffers from one or more of the above-mentioned types of ill-posedness. The University of Michigan model [25], many aspects of which have been adopted by later models, suffers from division-by-zero errors and DC response problems. An RRAM model from Stanford/ASU with several variants [26–29, 31–34] that has received considerable publicity suffers from egregious DC response problems.<sup>7</sup> The UESTC memristor models [30], though they avoid many issues common to other models, still suffer from subtle (but serious) DC response problems. The TEAM models for general memristors [31–34] also suffer from DC, uniqueness and continuity/smoothness issues. Over and above well-posedness issues, released versions of existing memristor compact models frequently suffer from deficiencies in the way their equations are expressed in modelling languages like Verilog-A. Examples of deficiencies we have encountered include attempts to perform time-integration of differential equations within the model definition, inserting time-varying noise terms as an integral part of the model, using integral formulations instead of differential ones, *etc.* As explained in [23], such practices compromise accuracy, limit the model's ability to support all analyses, reduce portability across simulators, and so on. Further details about the shortcomings we have observed in these models are provided later in this paper.

In this paper, we explain the correct generic way to model memristive devices in a well-posed manner. Our modelling technique sets up the dynamics of the filament length using a differential equation, and the current-voltage relationship of the memristor using an algebraic equation involving the filament length. Employing only continuous/smooth mathematical constructs, we show how filament dynamics can be modelled such that physical bounds are always respected and correct DC behaviour for positive and negative biasses always results. In the process of developing our modelling technique, we pinpoint several common mechanisms underlying ill-posedness in prior models. Since filament dynamics in memristive devices have features closely related to hysteresis,<sup>8</sup> we explain how to model hysteresis correctly in general, then apply this to memristive devices. We use our techniques to correct several previous models, making them well posed and suitable for any analysis (including DC, transient, AC, periodic steady state, *etc.*). The process of restoring well-posedness to memristor models also provides insights into possible physical mechanisms in memristors that seem not to have been looked into yet.

The remainder of the paper is organized as follows. In Sec. II, we explain how hysteresis should be modelled in general, *i.e.*, using internal unknown variables and implicit equations. We illustrate how a model with internal unknowns and implicit equations can be written properly in both Verilog-A [23, 35–37] and ModSpec [38, 39]. In Sec. IV, we specialize our general model template for hysteresis to RRAM devices, showing how to design the continuous/smooth equations involved so that filament length boundaries are always respected and the correct DC behaviour results. We write well-posed RRAM models in both Verilog-A and ModSpec and test them in simulation, using DC, transient and homotopy [40] analyses.<sup>9</sup> Then, in Sec. V, we develop techniques for aiding numerical convergence in the RRAM model. In particular, we design a SPICE-compatible limiting function for the rapidly-growing hyperbolic sine function used in the RRAM model, inspired by the limiting function designed to aid convergence after PNJLIM and FETLIM, which were developed as part of the original Berkeley SPICE [41]. Next,

<sup>&</sup>lt;sup>5</sup>Different analyses correspond to different ways of exciting the device, or to finding specific kinds of outputs. For example, periodic steady state analyses excite the device with time-periodic inputs, and seek similarly time-periodic outputs.

<sup>&</sup>lt;sup>6</sup>We request the reader to contact us if he/she is aware of published, openly available and reproducible memristor models prior to this work (other than the ones noted here), especially if they do not suffer from ill-posedness issues.

<sup>&</sup>lt;sup>7</sup>To their credit, the authors of [27] explicitly note this deficiency in their model's documentation.

<sup>&</sup>lt;sup>8</sup>Memristive devices may be said to be at the "cusp of hysteresis".

<sup>&</sup>lt;sup>9</sup>Homotopy analysis provides considerable insight into RRAM behaviour.

in Sec. VI, we study all the published compact models for memristors we are aware of that come with concrete equations or code. We identify issues of ill-posedness and poor implementation that affect their applicability in simulation. We then use our modelling techniques to correct their problems and turn them into well-posed models, providing proper implementations in ModSpec and Verilog-A.

The result of our study is a collection of well-posed, properly implemented, compact models for memristive devices. Specifically, we devise 5 different algebraic current-voltage and 6 different differential equation dynamical models for filament length, *i.e.*, 30 different models for memristors and/or RRAM devices, all well posed.

Although we use underlying equations published by others, we modify them to remove ill-posedness issues, and also provide proper implementations. Understanding the process by which we do this can be valuable for the development of future models, not only of memristors, but of other hysteretic devices as well.

## II. How to Model Hysteresis Properly

To develop our memristor models, we first study how to model i-v hysteresis in two-terminal devices properly. We show that the i-v hysteresis can be modelled with the help of an internal state variable and an implicit differential equation. Then with the help of an example, we illustrate how a model with internal unknowns and implicit equations can be properly written in both Verilog-A and the ModSpec format.

### A. Model Template for Devices with *i*-v Hysteresis

The equation of a general two-terminal resistive device can be written as

$$i(t) = f(v(t)), \tag{1}$$

where v(t) is the voltage across the device, i(t) the current through it. For example, the function f(.) for a simple linear resistor can be written as

$$f(v(t)) = \frac{v(t)}{R}.$$

(2)

For devices with i-v hysteresis, i(t) and v(t) cannot have a simple algebraic mapping like (1). Instead, we introduce a state variable s(t) into (1) and rewrite the i-v relationship as

$$i(t) = f_1(v(t), s(t)).$$

(3)

The dynamics of the internal state variable s(t) is governed by a differential equation:

$$\frac{d}{dt}s(t) = f_2(v(t), \ s(t)). \tag{4}$$

The internal state variable s(t) can have several physical meanings. If we consider the original memristor model proposed by Chua in the 1970s [1, 42], s(t) can be thought of as the flux or charge stored in the device. In the context of metal-insulator-metal-(MIM)-structured RAM devices, *e.g.*, RRAMs and CBRAMs, s(t) can represent either the length of the conductive filament/bridge, or the gap between the tip of the filament/bridge to the opposing electrode.<sup>10</sup>

In all these scenarios, s(t) has some influence on i(t). So we cannot directly calculate the current based on the voltage applied to the device at a single time t; i(t) also depends on the value of s(t). On the other hand, at time t, the value of s(t) is determined by the history of v(t) according to (4). Therefore, we can think of the device as having internal "memory" of the history of its input voltage. If we choose the formula for  $f_1$  and  $f_2$  in (3) and (4) properly, as we sweep the voltage, hysteresis in the current becomes possible.

In the rest of this paper, (3) and (4) serve as a model template for two-terminal devices with i-v hysteresis. To illustrate its use, we design a device example, namely "hys\_example", with functions  $f_1$  and  $f_2$  defined as follows.

<sup>10</sup>For CBRAM devices, the tunnelling gap can also form in the middle of the conductive bridge instead of on one of its ends [43].

$$f_1(v(t), s(t)) = \frac{v(t)}{R} \cdot (\tanh(s(t)) + 1).$$

(5)

$$f_2(v(t), s(t)) = \frac{1}{\tau} \left( v(t) - s^3(t) + s(t) \right).$$

(6)

The choice of  $f_1$  is easy to understand. tanh() is a monotonically increasing function with range (-1,1). We add 1 to it to make its range positive. We then incorporate it into  $f_1$  as a factor such that s(t) can modulate the conductance of the device between 0 and 2/R.

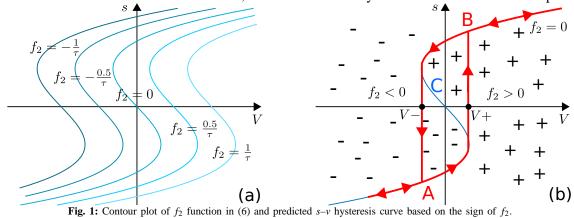

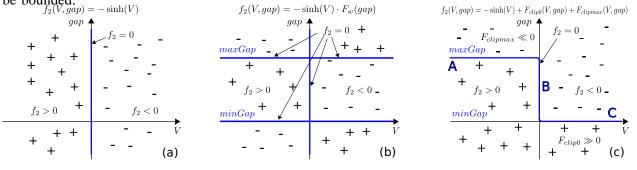

The choice of  $f_2$  determines the dynamics of s(t). And when  $f_2 = 0$ , the corresponding (v, s) pairs will show up as part of the DC solutions of circuits containing this device. Therefore, if we plot the values of  $f_2$  in a contour plot, such as in Fig. 1 (a), the curve representing  $f_2 = 0$  is especially important. Through the use of a simple cubic polynomial of s(t) in (6), we design the  $f_2 = 0$  curve to fold back in the middle, crossing the v = 0 axis three times. In this way, when v is around 0, there are three possible values s can settle on, all satisfying  $\frac{d}{dt}s(t) = f_2 = 0$ . This multiple stability in state variable s is the foundation of hysteresis found in the DC sweep on the device.

Fig. 1 (b) illustrates how hysteresis takes place in DC sweeps. In Fig. 1 (b), we divide the  $f_2 = 0$  curve into three parts: curve A and B have positive slopes while C has a negative one. When we sweep v towards the right at a very slow speed to approximate DC conditions, starting from a negative value left of  $V_{-}$ , at the beginning, there is only one possible DC solution of s. As we increase v, the (v, s) pair will move along curve A, until A ends when v reaches  $V_{+}$ . If v increases slightly beyond  $V_{+}$ , multiple stability in s disappears. (v, s) reaches the  $f_2 > 0$  region and s will grow until it reaches the B part of the  $f_2 = 0$  curve. This shows up in the DC solutions as a sudden jump of s towards curve B. Similarly, when we sweep v in the other direction starting from the right of  $V_{+}$ , the (v, s) pair will follow curve B, then have a sudden shift to A at  $V_{-}$ . Because  $V_{+} > V_{-}$ , hysteresis occurs in s when sweeping v, as illustrated in Fig. 1 (b). Since s modulates the device's conductance, there will also be hysteresis in the  $i_{-}v$  relationship.

Note that we are analyzing and predicting hysteresis based on the DC solution curve defined by  $f_2(v, s) = 0$ . This clarifies a common confusion people have. As hysteresis is normally defined as a type of timedependence between output and input, people often believe that it has nothing to do with the circuit's or device's DC properties. It is true that hysteresis is normally observed in transient analysis. But from the above discussions, we can see that it is indeed generated by the multiple stability and the abrupt change in DC solutions. As mentioned earlier, at a certain time t, s(t) can be thought of as encoding the memory of v(t) from the past. Its multiple stability reflects the different possible sets of history of v(t). And the separation between V+ and V- in the DC curves ensures that no matter at what speed we sweep v, there will always be hysteresis in the s-v relationship.

When we sweep v back and forth, curve C, the one with a negative slope in Fig. 1 (b) never shows up in solutions. The reason is that, although it also consists of solutions of  $f_2 = 0$ , these solutions are not

stable. If a (v, s) point on curve C is perturbed to move above C, whether because of physical noise or numerical error, it falls in the  $f_2 > 0$  region and will continue to grow until it reaches B. Similarly, if it moves below C, it will decrease to curve A. Therefore, it won't be observed during voltage sweep, leaving only A and B to form the s-v hysteresis curves.

# **B.** Compact Model in MAPP

With the model equations for hys\_example defined in (5) and (6), how do we put them into a compact model so that we can simulate it in circuits? To answer this question, in this section, we first discuss our formulation of the general form of device compact models, namely the ModSpec format [38, 39]. Then we develop the ModSpec model for hys\_example and implement it in MAPP [44].

ModSpec is MAPP's way of specifying device models. A device model describes the relationship between variables using equations. Among the variables of interest, some are the device's inputs/outputs; they are related to the circuit connectivity. We call them the device's I/Os. In the context of electrical devices, they are branch voltages and currents. Among all the I/Os, some may be expressed explicitly using the other variables; they are the outputs of the model's explicit equations. Furthermore, a device model can also have non-I/O internal unknowns and implicit equations. Taking all these possibilities into consideration, we specify model equations in the following ModSpec format.

$$\vec{z} = \frac{d}{dt}\vec{q}_e(\vec{x},\vec{y}) + \vec{f}_e(\vec{x},\vec{y},\vec{u}), \tag{7}$$

$$0 = \frac{d}{dt}\vec{q}_{i}(\vec{x},\vec{y}) + \vec{f}_{i}(\vec{x},\vec{y},\vec{u}).$$

(8)

Vectors  $\vec{x}$  and  $\vec{z}$  contain the device's I/Os:  $\vec{z}$  comprises those I/Os that can be expressed explicitly (for hys\_example, it contains only *i*), while  $\vec{x}$  comprises those that cannot (for hys\_example, it is *v*).  $\vec{y}$  contains the model's internal unknowns (for hys\_example, it is *s*), while  $\vec{u}$  provides a mechanism for specifying time-varying inputs within the device (*e.g.*, as in independent voltage or current sources). The functions  $\vec{q}_e$ ,  $\vec{f}_e$ ,  $\vec{q}_i$  and  $\vec{f}_i$  define the differential and algebraic parts of the model's explicit and implicit equations.

For hys\_example, we can write its model equations in the ModSpec format as follows.

$$\vec{f}_{e}(\vec{x}, \vec{y}, \vec{u}) = \frac{x}{R} \cdot (\tanh(\vec{y}) + 1), \quad \vec{q}_{e}(\vec{x}, \vec{y}) = 0,$$

$$\vec{f}_{i}(\vec{x}, \vec{y}, \vec{u}) = \vec{x} - \vec{y}^{3} + \vec{y}, \quad \vec{q}_{i}(\vec{x}, \vec{y}) = -\tau \cdot \vec{y},$$

(9)

with  $\vec{x} = [v], \ \vec{y} = [s], \ \vec{z} = [i], \ \vec{u} = [].$

We can enter the model information in (9) into MAPP by constructing a ModSpec object MOD. The code in Appendix A-A shows how to create this device model for hys\_example entirely in the MATLAB<sup>®</sup> language. For more detailed description of the ModSpec format, users can issue the command "help ModSpec\_concepts" in MAPP.

## C. Simulation Results

In this section, we verify our analysis and prediction of i-v hysteresis in Sec. II-A by testing the compact models presented in Sec. II-B and in a circuit shown in Fig. 2.

Fig. 2: Schematic of the test bench circuit for hys\_example. The three circuit unknowns are node voltage  $e_1$ , current  $i_1$  and internal state variable s.

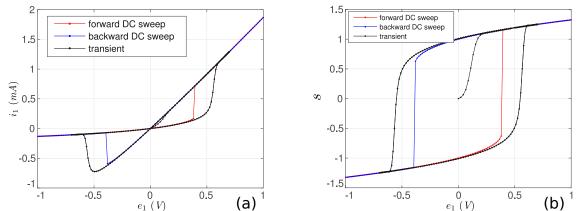

Fig. 3 shows the results from DC sweep and transient simulation with input voltage sweeping up and down on the circuit in Fig. 2. It confirms that hysteresis takes place in both i-v and s-v relationships of the device.

Fig. 3: Results from DC sweep and transient simulation in MAPP on the circuit in Fig. 2, showing hysteresis in both s and  $i_1$  when sweeping the input voltage, in either type of the analyses.

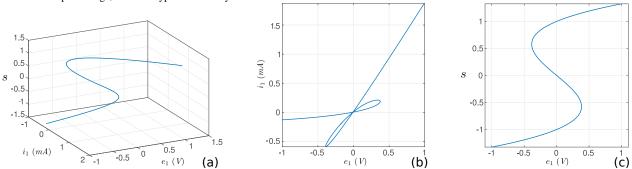

Fig. 4: Results from homotopy analysis in MAPP. (a) 3-D view of all the DC solutions of the circuit in Fig. 2 with voltage input between -1V and 1V. (b) top view of all the DC solutions shows the folding in the *i*-v characteristic curve, explaining the *i*-v hysteresis in Fig. 3. (c) side view of the DC solutions.

In Fig. 3 (b), curve C (defined in Fig. 1 (b)) with a negative slope never shows up in either forward or backward voltage DC sweep. This matches our discussion in Sec. II-A. In order to plot this curve and complete the DC solutions, also to get rid of the abrupt change of solutions in DC sweeps, we can use the homotopy analysis [40]. Homotopy analysis can track the DC solution curve in the state space.

Results from homotopy analysis on the circuit in Fig. 2 are shown in Fig. 4. We note that all the circuit's DC solutions indeed form a smooth curve in the state space. The side view of the 3-D plot displays curve C we have designed in our model equation (6). The corresponding curve in the top view connects the two discontinuous DC sweep curves in Fig. 3; it consists of all the unstable solutions in the i-v relationship. This curve was previously missing in DC and transient sweep results, and now displayed by the homotopy analysis. These results from homotopy analysis provide us with important insights into the model. They reveal that there is a single smooth and continuous DC solution curve in the state space, which is an indicator of the well-posedness of the model. They also illustrate that it is the folding in the smooth DC solution curve that has created the discontinuities in DC sweep results. These insights are important for the proper modelling of hysteresis.

Moreover, the top view explains the use of internal state *s* for modelling hysteresis from another angle. Without the internal state, it would be difficult if not impossible to write a single equation describing the i-v relationship shown in Fig. 4 (b). With the help of *s*, we can easily choose two simple model equations as (5) and (6), and the complex i-v relationship forms naturally.

III. How to Model Internal Unknowns Properly in Verilog-A

In this section, we write the hys\_example model in the Verilog-A language.

Apart from the differences in syntax, Verilog-A differs from ModSpec in one key aspect — the way of handling internal unknowns and implicit equations. Verilog-A models a device with an internal circuit

topology, *i.e.*, with internal nodes and branches defined just like in a subcircuit. The variables in a Verilog-A model, the "sources" and "probes", are potentials and flows specified based on this topology. Coming from this subcircuit perspective, the language doesn't provide a straightforward way of dealing with general internal unknowns and implicit equations inside the model, *e.g.*, the state variable *s* and the equation (4) in hys\_example.

This limitation gives rise to so much confusion about the modelling of devices with hysteresis, that we would like to examine the common modelling mistakes and pitfalls before describing our approach. Here is the list of how not to model internal unknowns and implicit equations in Verilog-A.

• Declare the internal unknown as a general variable, *e.g.*, using "real", then use "idt()" function to describe the differential equation the variable should satisfy. This approach is not recommended because of several reasons.

First, Verilog-A provides most consistent definitions and support for potentials and flows as circuit unknowns; it is unclear how "real" variables inside differential equations are handled by each Verilog-A compiler. Some simulators will return inconsistent or incorrect results. Moreover, another potential hazard from this practice is that the simulator may create a memory state for the variable [23], limiting its use in some simulation algorithms, *e.g.*, those for periodic steady state (PSS) analysis.

Also, people often attempt to use "idt()" in this scenario, apparently because Verilog-A doesn't allow using "ddt()" to contribute to a none-potential/flow quantity as "source", for good reasons. But this "workaround" with the use of "idt()" is not recommended [23, 36], as different simulators have inconsistent support for "idt()".

- Another pitfall is to use implicit contributions. While an implicit contribution in Verilog-A seems to simplify the code, and forces users to model the internal unknown as a potential or flow, which is in line with what we propose, it is not recommended [23, 37]. In fact, it is not supported properly even by some well-known commercial simulators.

- Model the differential relationship by coding time integration inside. In this approach, the model has access to the absolute time and calculates the time step inside, then approximates the differential equation (4) by integrating  $f_2$  at each time step. The approach may seem straightforward, but it has so many problems that I have to create another list for them:

- The method inevitably uses "abstime" function in the model. To set the starting point of the integration, it also has to use the "initial\_step" event. These are both bad practices in analog modelling [23, 36].

- The method can only use Forward Euler (FE) [22] internally for integration, potentially causing convergence issues for stiff systems.

- In this method, the internal unknown is intentionally defined as a memory state, again creating difficulties for PSS simulation.

- The model won't perform correctly in analyses that do not involve time integration, like DC, small signal AC analysis and Harmonic Balance.

- Even for transient simulation, it defeats the purpose of using the simulator, as it bypasses the simulator's many built-in facilities, *e.g.*, convergence aiding techniques, truncation error estimation, time step control, *etc*.

- There are many more issues with this approach. For example, circuit designers cannot set transient analysis initial conditions for the internal unknown the normal way they do for capacitor voltages and inductor currents. Also, to "ensure" the accuracy of internal time integration, "bound\_step" is often used. And the bounded step specified either makes simulation inaccurate or unnecessarily slow.

We note that these problems and pitfalls arise partly from the limitation of the Verilog-A language in intuitively handling general internal unknowns and implicit equations, mostly from bad modelling practices. To circumvent these issues and write a robust Verilog-A model for hys\_example that should work consistently in all simulators and all simulation algorithms, we model state variable *s* as a voltage. We declare an internal branch, whose voltage represents *s*. One end of the branch is an internal node that doesn't connect to any other branches. In this way, by contributing  $V - s^3 + s$  and ddt (-tau \* s) both to this same branch, the KCL at the internal node will enforce the implicit differential equation in (6).

Declaring s as a voltage is not the only way to model hys\_example in Verilog-A. Depending on the physical nature of s, one can also use Verilog-A's multiphysics support and model it as a mechanical property, such as a position from the kinematic discipline. This may be closer to the actual meaning of s for MIM-structured RAM devices. Alternatively, we can also use the property for potential from the thermal or magnetic discipline. One can also switch potential and flow by defining s as a flow instead. These alternatives may make the model look more physical, but they do not make a difference mathematically, except from the scale of tolerances in each discipline, which we will discuss in more detail in Sec. IV-C. The essence of our approach is to recognize that state variable s is a circuit unknown, and thus should be modelled as a potential or flow in Verilog-A, for the consistent support from different simulators in various circuit analyses.

The Verilog-A code for hys\_example is provided in Appendix A-B. It generates consistent results in many simulation platforms, including Spectre<sup>®</sup>,<sup>11</sup> HSPICE,<sup>12</sup> and the open-source simulator Xyce.<sup>13</sup> The test benches with all these simulators can be found in Appendix A.

# IV. RRAM Model

The model hys\_example developed in Sec. II is a model template for devices with hysteresis, such as RRAM devices. By changing its  $f_1$  (5) and  $f_2$  (6) functions in model equations, as well as the corresponding function implementations in MAPP and Verilog-A code, we can then have compact models capturing the physics of RRAM devices.

# A. Model Equations

An RRAM device consists of two metal electrodes, namely t (top) and b (bottom), and a thin oxide film separating them. A conductive filament can form in the film. When it grows to connect the two electrodes, the device is in low resistance state (LRS); when part of it dissolves, the device enters high resistance state (HRS). As a RAM, its "memory" is stored in the status of its internal conductive filament and the corresponding resistance state.

From the above discussion, the internal state variable for RRAM models can be either the length of the filament [25], or the gap between the tip of the filament and the opposing electrode [26, 27]. We choose to use the gap in this section, as it is what really determines the tunnelling current. Then the variables in the RRAM model are: the voltage vtb across the device, the current *itb* through it and the internal unknown *gap*. We can then rewrite the equations (3) and (4) from the model template in Sec. II-A as

$$itb(t) = f_1(vtb(t), gap(t)), \tag{10}$$

$$\frac{d}{dt}gap(t) = f_2(vtb(t), gap(t)).$$

(11)

The physical contexts of these RRAM model equations are straightforward to understand. Equation (10) determines how the current is modulated by both the voltage and gap; equation (11) describes the growth rate of gap at a given voltage with some existing gap size. Our goal of RRAM modelling is to find suitable  $f_1$  and  $f_2$  functions to capture these physical properties.

The formula for  $f_1$  are mostly consistent across several existing RRAM models developed in different groups [25, 27, 29, 32]. Among them, [27, 29] use the same equation, which is only different from that used in [32] in the choice of internal unknown.<sup>14</sup> Therefore, in this section, we choose to use the  $f_1$

<sup>&</sup>lt;sup>11</sup>Spectre<sup>®</sup> version: 7.2.0 64bit.

<sup>&</sup>lt;sup>12</sup>HSPICE version: J-2014.09 64bit.

<sup>&</sup>lt;sup>13</sup>Xyce version: 6.4.

<sup>&</sup>lt;sup>14</sup>In the I-V relationship equation in [32], we can redefine the internal unknown and make a one-to-one mapping between  $s^n$  and  $\exp(-gap/g_0)$ , to make the equation equivalent to the one in [27, 29].

function in [27, 29]:

$$f_1(vtb, gap) = I_0 \cdot \exp(-\frac{gap}{g_0}) \cdot \sinh(\frac{vtb}{V_0}), \tag{12}$$

where  $I_0$ ,  $g_0$ ,  $V_0$  are fitting parameters.

For  $f_2$ , we can adapt the gap growth formulation in [27, 29] and write it as

$$f_2(vtb, gap) = -v_0 \cdot \exp(-\frac{E_a}{V_T}) \cdot \sinh(\frac{vtb \cdot \gamma \cdot a_0}{t_{ox} \cdot V_T}), \tag{13}$$

where  $v_0$ ,  $E_a$ ,  $a_0$  are fitting parameters,  $t_{ox}$  is the thickness of the oxide film,  $V_T = k \cdot T/q$  is the thermal voltage, and

$$\gamma = \gamma_0 - \beta \cdot gap^3. \tag{14}$$

$\gamma$  in (14) is known as the local field enhancement factor [45]. It accounts for the abrupt SET (filament grows enough to connect electrodes) and gradual RESET (filament dissolves) behaviors in bipolar RRAM devices [46]. Parameters are normally chosen to ensure that this  $\gamma$  factor is always positive. So the sign and zero-crossings of  $f_2$  in (13) are determined only by *vtb*.

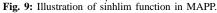

While there are small differences among the  $f_2$  functions in models developed by various groups [25, 27, 29, 32], they differ mainly in the definitions of fitting parameters. A property they all share is that the sign of  $f_2$  is the same as that of  $-\sinh(vtb)$ . Put in other words, *gap* begins to decrease whenever *vtb* is positive, and vice versa, as illustrated in Fig. 5 (a). While there is some physical truth to this statement, considering that an RRAM device will eventually be destroyed<sup>15</sup> if applied a constant voltage for an indefinite amount of time, for the model to work in numerical simulation, the state variable *gap* has to be bounded.

Fig. 5: Illustration of several choices of  $f_2$  in RRAM model.

Ensuring that the upper and lower bounds for *gap* are always respected in simulation is one major challenge for the compact modelling of RRAM devices. To address this challenge, several techniques have been attempted in the existing RRAM compact models:

• Directly use if-then-else statements on gap [27, 29]. This type of model is normally written in Verilog-A. They declare gap as a real variable, then directly enforce "if (gap < 0) gap = 0;". We have discussed in great detail in Sec. III about the problems of modelling internal unknowns as general Verilog-A variables. On top of these problems, no matter whether the Verilog-A compiler treats gap as a circuit unknown or a memory state, the use of if-then-else statements for bounding the variable excludes the model from the differential equation framework. Thus they are not suitable for simulation analyses.

Moreover, the use of if-then-else also introduces hard discontinuities in the model, causing convergence problems [22]. Also, forcefully setting variable gap to certain values can result in singular circuit Jacobian matrices, creating difficulties for most simulation algorithms.

• Use window functions [25, 32].

<sup>15</sup>Under constant negative voltages, the filament will dissolve to the extent that SET cannot restore it. The device will need to go through the forming process again. Under constant positive voltages, the filament will grow too thick to RESET, and the device becomes shorted.

The goal is to set  $\frac{d}{dt}gap = f_2 = 0$  when gap = maxGap and gap = minGap. The method used in these models is to multiply the  $f_2$  in (13) with a window function that is close to 1 when minGap < gap < maxGap, equal to 0 when gap is at minGap or maxGap, and has negative values elsewhere. Directly constructing such windows functions with step() functions [25] is not recommended as it introduces discontinuities into the model. One better example of such window functions for [0,1] window size is known as the Joglekar window [33]:

$$F_w(x) = 1 - (2 \cdot x - 1)^{2 \cdot p}, \tag{15}$$

where p is a positive integer used to adjust the sharpness of the window.

After multiplying window functions, the  $f_2$  function used in these models is still smooth and continuous, and the models still in the differential equation format, complying with the model template we have discussed in Sec. II. As a result, the models are often reported to run reasonably well in transient simulations [31, 33, 34].

However, there are subtle and deeper problems with this approach. The problems can also be illustrated by analyzing the sign and zero-crossings of function  $f_2$ . After multiplying  $f_2$  by window functions, the zero-crossings of  $f_2$  are shown in Fig. 5 (b). The  $f_2 = 0$  curves consist of three lines: the *maxGap* and *minGap* lines, and the V = 0 line. Based on the sign of  $f_2$ , the left half of the *minGap* line and the right half of the *maxGap* line consist of unstable DC solutions; they are unlikely to show up in transient simulations. Therefore, when sweeping the voltage between negative and positive values, *gap* will move between *maxGap* and *minGap*. This is the foundation for the model to work in transient simulations. However, based on Fig. 5 (b), the model has several problems in other types of analyses.

- In DC operating point analysis or DC sweeps, all lines consisting the  $f_2 = 0$  curves can show up, including those containing unphysical results. For example, when the voltage is zero, any gap size is a solution; gap is not bounded anymore.

- In homotopy analysis, the intersection of solution lines introduced by the window functions makes the solution curve difficult to track. In particular, it will attempt to track the V = 0 line where gap grows without bound. The fact that there is no single continuous solution curve in the state space indicates poor numerical properties of the model in other types of simulation algorithms as well.

- Even in transient analysis, the model won't run properly unless we carefully set an initial condition for *gap*. If the initial value of *gap* is beyond (*minGap*, *maxGap*), or if it falls outside this range due to any numerical error, it can start to grow without bound.

Other window functions are also tried for this approach, *e.g.*, Biolek and Prodromakis windows [31, 33]. But as long as the window function is multiplied to  $f_2$ , the picture of DC solutions in Fig. 5 (b) stays the same. And it is this introduction of unnecessary DC solutions the modelling artifact that limits the RRAM model's use in simulation analyses.

In our approach, we try to bound variable gap while keeping the DC solutions in a single continuous curve, illustrated as the  $f_2 = 0$  curve in Fig. 5 (c). This is inspired by studying the model template hys\_example in Sec. II. The sign and zero-crossing of  $f_2$  for our RRAM model are closely related to those of the  $f_2$  function (6) for hys\_example (shown in Fig. 1).

The desired  $f_2 = 0$  solution curve consists of three parts: curve A and C contain the stable solutions; curve B contains those that are unstable (or marginally stable). In this way, when sweeping the voltage past zero, variable *gap* will start to switch between *maxGap* and *minGap*. If the sweeping is fast enough, I-V hysteresis will show up.

To construct the desired  $f_2 = 0$  solution curve, we modify the original  $f_2$  in (13) by adding clipping terms to it. Our new  $f_2^*$  can be written as

$$f_2^*(vtb, gap) = f_2(vtb, gap) + F_{clipmin}(vtb, gap) + F_{clipmax}(vtb, gap),$$

(16)

where  $f_2$  is the original function in (13),  $F_{clipmin}$  and  $F_{clipmax}$  are clipping functions:  $F_{clipmin}(vtb, gap) = (safeexp(K_{clip} \cdot (minGap - gap), maxslope) - f_2(vtb, gap)) \cdot F_{w1}(gap), (17)$

$F_{clipmax}(vtb, gap) = (-\operatorname{safeexp}(K_{clip} \cdot (gap - maxGap), maxslope) - f_2(vtb, gap) \cdot F_{w2}(gap).$ (18)

Functions  $F_{w1}$  and  $F_{w2}$  in (17) and (18) are smooth versions of step functions:  $F_{w1}(gap) = \text{smoothstep}(minGap - gap, smoothing}),$

(19)

$$F_{w2}(gap) = \text{smoothstep}(gap - maxGap, smoothing).$$

(20)

The intuition behind  $F_{w1}$  and  $F_{w2}$  is to make  $F_{w1} \approx 0$  and  $F_{w2} \approx 0$  when gap is within [minGap, maxGap]; then  $F_{w1} \approx 1$  when gap < minGap,  $F_{w2} \approx 1$  when gap > maxGap.

When  $F_{w1} \approx 1$  or  $F_{w2} \approx 1$ , the added clipping term in (17) or (18) is "in effect". Either term will first use  $-f_2(vtb, gap)$  to cancel out the effect of  $f_2$ , then add a fast growing component modelled using exponential functions to ensure that  $f_2^*$  has the desired sign as in Fig. 5 (c). Parameter  $K_{clip}$  is used to adjust the speed in which these exponential components grow.

Note that in equations (17), (18) and (19), (20), instead of using normal exponential and step functions, we use safeexp() and smoothstep(). These are smooth functions we have developed with better numerical properties than the original ones. safeexp() linearises the exponential function from the point its derivative reaches parameter *masslope*. smoothstep() is implemented whether as a parameterised tanh, or as

smoothstep

$$(x) = 0.5 \cdot \left(\frac{x}{\sqrt{x^2 + smoothing}} + 1\right).$$

(21)

Issuing commands "help safeexp;" and "help smoothstep;" in MAPP will display more usage and implementation details of these functions.

The  $f_2^*$  we have proposed for RRAM model is smooth and continuous in both *vtb* and *gap*. Its sign and zero-crossings are designed to mimic those shown in Fig. 5 (c). By adjusting the parameters  $K_{clip}$  and smoothing, users can tune the sharpness of the DC solution curve in Fig. 5 (c). The clipping terms can also leave the values from the original  $f_2$  function in (13) almost intact when minGap < gap < maxGap. While the intention of adding the clipping terms in (16) is to set up bounds for variable gap and to construct DC solution curve in Fig. 5 (c), there is also some physical justification to our approach. As a physical quantity, gap is indeed bounded by definition. Therefore,  $\frac{d}{dt}gap = f_2$  cannot look like Fig. 5 (a) in reality. The  $f_2 = 0$  curves must have the A and B parts in Fig. 5 (c). One can think of the clipping terms as infinite amount of resisting "force" to keep gap from decreasing below minGap, or increasing beyond maxGap. The analogy is the modelling of MEMS switches, where the switching beam's position is often used as an internal state variable. This variable reaches its bound when the switching beam hits the opposing electrode (often the substrate). The position does not move further. The beam cannot move into the electrode/substrate because of the huge force resisting it from causing any shape change in the structures. Similarly, in RRAM modelling, if the variable *gap* represents it physical meaning accurately, one can expect such "forces" to exist to make it a bounded quantity. This physics intuition matches well with our proposed numerical technique of using fast growing exponential components to enforce the bounds.

The compact model we propose for RRAM devices, with equations (12) and (16), complies with the differential equation format. It uses the correct model template for hysteretic devices proven to work. The study of the model template and the use of it for RRAM help us avoid many of the modelling pitfalls at this equation formulation stage. Compared with existing models, our model does not have to use "idt()" [27, 28], or events and functions like "initial\_step", "bound\_step" and "abstime" [27, 29]. It is not limited to using SPICE subcircuits written in simulator-dependent syntax [25, 32]. With our model formulation, for the first time, it is possible to write robust compact models for RRAM devices in both ModSpec and Verilog-A, that should run consistently on various simulation platforms in different analyses.

Apart from the use in modelling and simulation, our analysis of the RRAM equations provides important insights into the physical nature of these devices. Comparing Fig. 1 (b) and Fig. 5 (c), we note that the  $f_2$  function for RRAM, unlike that of the model template hys example, does not have DC solutions folding back with a negative slope. We can say that there is no "DC hysteresis" for these devices. Put in other words, if voltage is swept slowly enough, there will be no I-V hysteresis; there will only be an abrupt change in gap at zero voltage. We would like to clarify that this does not constitute a problem for

using RRAMs as memory devices. Because the growth rate of filament is exponential in the input voltage; only when the voltage is substantially large will the growth be significant. When the applied voltage is small, it may take years or decades for SET and RESET to happen. Therefore, the device can still keep its "memory" securely. From our analysis, it is this exponential relationship that accounts for the switching voltages measured in RRAM devices. But the lack of "DC hysteresis" distinguishes RRAM from the general hysteresis devices like hys\_example. This provides new perspective to the debate over whether RRAMs are memristors or not [47–49]. The lack of "DC hysteresis" in RRAM devices explains why they cannot cope with inevitable thermal fluctuations and will erratically change state over time in the presence of noise [49]. Although showing I-V hysteresis curves like a genuine memristor during voltage sweeps, RRAMs are more like "chemical capacitors" as they violate some essential requirements on a genuine memristor [48]. It is arguable whether these criticisms are valid. Nevertheless, our analysis in this section explains the difference between hys\_example, a device with true "DC hysteresis" and the RRAM device model vigorously, while being easy to appreciate graphically.

## **B.** Compact Model in MAPP

Similar to the hys model in Sec. II, we can put the RRAM equations  $f_1$  (12) and  $f_2^*$  (16) into a compact model by writing them in the ModSpec format:

$$\vec{f}_{e}(\vec{x}, \vec{y}, \vec{u}) = f_{1}(\vec{x}, \vec{y}), \quad \vec{q}_{e}(\vec{x}, \vec{y}) = 0,$$

$$\vec{f}_{i}(\vec{x}, \vec{y}, \vec{u}) = f_{2}^{*}(\vec{x}, \vec{y}), \quad \vec{q}_{i}(\vec{x}, \vec{y}) = -10^{-9} \cdot \vec{y},$$

$$[itb] \vec{u} = 0$$

(22)

with  $\vec{x} = [vtb], \ \vec{y} = [gap], \ \vec{z} = [\vec{u}tb], \ \vec{u} = [].$

Note that there is  $10^{-9}$  in the  $\vec{q}_i$  function. This is to scale the equation for better convergence. We explain this technique in more detail in Sec. IV-C.

The code in Appendix B-A shows how to enter this RRAM model into MAPP.

# C. Compact Model in Verilog-A

Having followed the model template discussed in Sec. II and formulated the RRAM model in the differential equation format in Sec. IV-A, in this section, we discuss the Verilog-A model for RRAM. The Verilog-A model is show in Appendix B-B.

Same as in the Verilog-A model for hys\_example (Sec. III), we also model the internal state variable *gap* in RRAM as a voltage. We have discussed why this approach results in more robust Verilog-A models compared with many alternatives, *e.g.*, using "idt()" [27, 28], implementing time integration inside models [29], *etc.* In this section, we would like to highlight from the provided Verilog-A code a few more details in our modelling practices.

• <u>Scaling of unknowns and equations.</u> In the Verilog-A code, we can see that gap is modelled in nanometers, as opposed to meters. This is not an arbitrary choice; the intention is to bring the value of this variable to around 1, at the same scale as other voltages in the circuit. When the simulator solves for an unknown, only a certain accuracy can be achieved, controlled by absolute and relative tolerances. The abstol in most simulator for voltages is set to be  $10^{-6}$ V. If gap is modelled in meters with nominal values around  $10^{-9}$ , it won't be solved accurately. Apart from the scaling of unknowns, we can also see from the Verilog-A code another  $10^{-9}$  factor in the implicit equation, scaling down its value. In this RRAM model, the implicit equation is represented as the KCL at the internal node. The equality in KCL is calculated to a certain accuracy as well — often  $10^{-12}$ A. However, without scaling down, the equation is expressed in nano-meter per second. For RRAM models, this is a value around  $10^{6}$ . The simulator has to ensure an accuracy of at least 18 digits such that the KCL is satisfied, which is not necessary and often not achievable with double precision. So we scale it by  $10^{-9}$  to bring its nominal value to around  $10^{-3}$ , just like a regular current in a circuit.

Note that when explaining the scaling of unknowns and equations, we are using the units nm or nm/s, mainly for readers to grasp the idea more easily. It doesn't indicate that certain units are more suitable for modelling than others. The essence of scaling is to make the model work better with simulation tolerances set for unknowns and equations.

- <u>Numerical accuracy</u>. Note that in the Verilog-A code, we include the standard constants.vams file and use physical constants from it. This practice ensures that we are using these constants with their best accuracy; their values will also be consistent with other models also including constants.vams. Although this is straightforward to understand, it is often neglected in existing models. For example, in the model released in [25], many constants are used with only two digits of accuracy. A variable named alpha, which can be calculated with 16 digits, is hard-coded to  $1.4 \times 10^{19}$ . Since numerical errors propagate through computations, the best accuracy the model can possibly achieve is limited to two digits, and worse if the inaccurate variables are used in non-linear functions.

- <u>Smooth and safe functions</u>. In the Verilog-A code, we have used limexp, smoothstep. As discussed earlier, these functions help with convergence greatly and are highly recommended for use in compact models.

#### **D.** Simulation Results

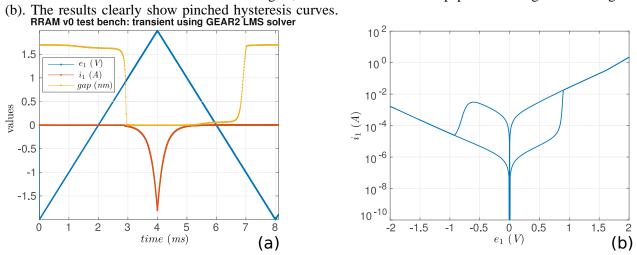

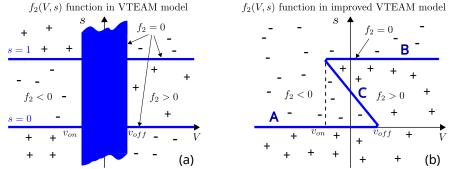

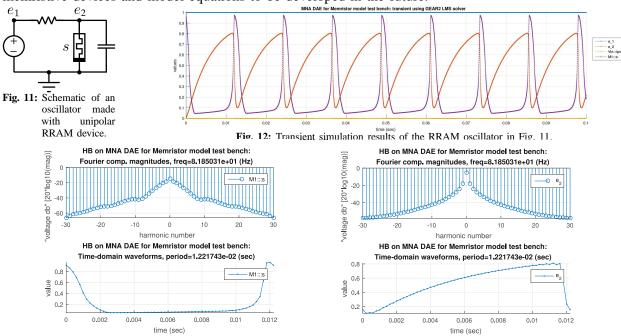

In this section, we simulate the RRAM model in a test circuit with the same schematic as in Fig. 2. The transient simulation results are shown in Fig. 6, with the I-V relationship plotted in log scale in Fig. 6 (b). The results clearly show pinched hysteresis curves

Fig. 6: Transient results on the circuit with a voltage source connected to an RRAM device.

Fig. 7: Homotopy analysis results on the circuit with a voltage source connected to an RRAM device.

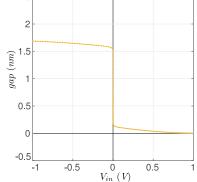

The model we develop also work in DC and homotopy analyses. gap-V relationship under DC conditions acquired from homotopy analysis are shown in Fig. 7. DC sweeps from both directions in this case give the same results since the model doesn't have DC hysteresis. The gap-V curve in Fig. 7 matches our discussion on the  $f_2 = 0$  solutions in Sec. IV-A.

Note that in the transient results, gap is not perfectly flat at *minGap* or *maxGap*; same phenomenon can also be observed in the DC solutions obtained using homotopy. This is because that the clipping functions

we use, although fast growing, cannot set exact hard limits on the internal unknown. In other words, even when gap is close to *minGap* or *maxGap*, changing the voltage can still affect gap slightly. This is not a modelling artifact. In fact, this makes the model numerically robust, and at the same time more physical. It maintains the smoothness of equations and reduces the chance for Jacobian matrix to become singular in simulation. Physically, even when *gap* is close to the boundary, changing voltage still causes the device's state to change. The small changes in *gap* in this scenario can be interpreted as reflecting the change in device's state, *e.g.*, the width of the filament. We conclude that, by making the model equations smooth, we are actually making the model more physical.

## V. Convergence Aids

A common issue with newly-developed compact models of non-linear devices is that they often do not converge in simulation. In this section, we discuss several techniques in compact modelling that can often improve the convergence of simulation. Among these techniques, we focus on the use of SPICE-compatible limiting functions. We explain the intuition behind this technique and use this intuition to design a limiting function specific to the RRAM model.

In the previous sections, we have already discussed several convergence aiding techniques used in our RRAM model. One of them is the proper scaling of both unknowns and equations. This improves both the accuracy of solutions and the convergence of simulation. The use of GMIN makes sure that the two terminals are always connected with a finite resistance, reducing the chance for the circuit Jacobian matrix to become singular during simulation. We have also discussed the use of smooth and safe functions (smoothstep(), safeexp()). We highly recommend that compact model developers consider these techniques when they encounter convergence issues with their models.

However, the above techniques do not solve all the convergence problems with the RRAM model. In particular, we have observed that the values and derivatives of  $f_1$  (12) and  $f_2$  (13) often become very large while the Newton Raphson (NR) iterations [22] are trying different guesses during DC operating point analysis. This is because of the fast-growing sinh functions in the equations. One solution is to use safesinh instead of sinh. The safesinh function uses safeexp/limexp inside to eliminate the fast-growing part with its linearized version, keeping the function values from exploding numerically. Although it has some physical justifications, it also has the potential problems of inaccuracy, especially since the exponential relationship is the key to the switching behaviour of RRAM devices (Sec. IV-A). Therefore, in this section, we focus on another technique that can keep the fast-growing exp or sinh function intact, but prevent NR from evaluating these functions with large input values. The techniques are known as initialization and limiting; they were implemented in Berkeley SPICE, for nonlinear devices such as diodes, BJTs and MOSFETs. Initialization evaluates these fast-growing nonlinear equations of semiconductor devices with "good" voltage values at the first NR iteration; limiting changes the NR guesses for these voltages in the subsequent iterations, based on both the current guess at each iteration and the value used in the last evaluation.

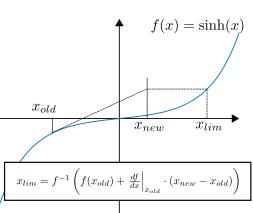

The limiting functions in SPICE include pnjlim, fetlim and limvds. Among them, pnjlim calculates new p-n junction voltage based on the current NR guess and the last junction voltage being used, in an attempt to avoid evaluating the exp function in the diode equation with large values. This mechanism is applicable to sinh as well. Inspired by pnjlim, we design a sinhlim that can reduce the chance of numerical exposion for the RRAM model.

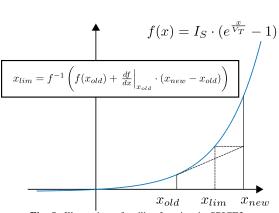

pnjlim calculates the new junction voltage using the mechanism illustrated in Fig. 8. The current NR guess is  $x_{new}$ , which is too large a value for evaluating an exponential function. So pnjlim calculates the limited version,  $x_{lim}$ , in between  $x_{new}$  and  $x_{old}$ . Since NR linearized the system equation at  $x_{old}$  in the last NR iteration, and the linearization indicates that the new guess is  $x_{new}$ , what NR actually wants is for the p-n junction to generate the current predicted for  $x_{new}$ . Because this prediction is based on the linearization at  $x_{old}$ , the actual current at  $x_{new}$  is apparently far larger than it. Therefore, a more sensible choice for the junction voltage should be one that gives out the predicted current. From the above discussion, we

Fig. 8: Illustration of pnjlim function in SPICE3.

can write an equation for the desired  $x_{lim}$ :

$$I_{S} \cdot (e^{\frac{x_{lim}}{V_{T}}} - 1) = y_{lim} = I_{S} \cdot (e^{\frac{x_{old}}{V_{T}}} - 1) + I_{S} \cdot \frac{1}{V_{T}} \cdot e^{\frac{x_{old}}{V_{T}}} \cdot (x_{new} - x_{old}).$$

(23)

Solving  $x_{lim}$  from the above equation, we get the core of pnjlim.

$$x_{lim} = \text{pnjlim\_core}(x_{new}, x_{old}, V_T) = x_{old} + V_T \cdot \ln\left(1 + \frac{x_{new} - x_{old}}{V_T}\right).$$

(24)

From the above formula, the operation of pnjlim is essentially inverting the diode I-V equation to calculate the desired voltage from the predicted current at  $x_{old}$ . Based on the same idea, we can write the limiting function for sinh. As illustrated in Fig. 9, given  $x_{old}$  and the current guess  $x_{new}$ , we can calculate the desired "current" (function value), then invert sinh to get the corresponding  $x_{lim}$  for function evaluation. Such an  $x_{lim}$  satisfies

$$\sinh(x_{lim}) = y_{lim} = \sinh(k \cdot x_{old}) + k \cdot \cosh(k \cdot x_{old}) \cdot (x_{new} - x_{old}),$$

(25) which gives out the formulation of sinhlim:

$$x_{lim} = \sinh\lim(x_{new}, x_{old}, k) = \frac{1}{k} \cdot \ln\left(y_{lim} + \sqrt{1 + y_{lim}^2}\right).$$

(26)

This new limiting function sinhlim can be easily implemented in any SPICE-compatible circuit simulator. To demonstrate its effectiveness, we implement a simple two-terminal device with its I-V relationship governed by a sinh function, *i.e.*, the device equation is  $I = \sinh(V)$ . As sinh is a rapidly-growing function, even a simple circuit with a series connection of a voltage source, a resistor of 1 $\Omega$  and this device may not converge if the supply voltage is large. This is because when searching for the solution, plain NR algorithm may try large voltage values as inputs to the model's sinh function, resulting difficulties or failure in convergence. In contrast, SPICE-compatible NR can use sinhlim to calculate  $x_{lim}$  for use in iterations, preventing using large  $x_{new}$  directly. We run DC operating point analyses on this simple circuit, with NR starting from all-zeros as initial guesses. As shown in Table I, with the same convergence criteria,<sup>16</sup> the use of sinhlim improves convergence greatly.

| Supply Voltage (V) | with sinlim (niters) | without limiting (niters)        |

|--------------------|----------------------|----------------------------------|

| 1                  | 4                    | 4                                |

| 10                 | 4                    | 9                                |

| 100                | 4                    | 50                               |

| 1000               | 4                    | non-convergence within 100 iters |

**TABLE I:** Number of NR iterations required for DC operating point analyses on a circuit with a series connection of a voltage source, a resistor and a device with sinh I-V relationship.

We implement parameterized versions of the sinhlim function in our RRAM model to aid convergence; the code is included in Appendix B-A. Since there are two sinh function used in the RRAM model,

<sup>&</sup>lt;sup>16</sup>In the simulation experiments, reltol is 1e-6, abstol is 1e-12, residualtol is 1e-12.

in both  $f_1$  and  $f_2$ , two limited variables are declared in the model, with two sinhlim with different parameters used in a vectorized limiting function.

Many simulators available today are SPICE-compatible, in the sense that they implement the equivalent limiting technique as in SPICE.<sup>17</sup> However, we would like to note that the limiting functions available in literature today, 40 years after the introduction of SPICE, are still limited to only the original pnjlim, fetlim and limvds. The sinhlim we have developed for RRAM models, is a new one. Moreover, among all these limiting functions, sinhlim is the only one that is smooth and continuous, making it more robust to use in simulation.

## **VI.** Models for General Memristive Devices

In this section, we apply the modelling techniques and methodology we have developed in previous sections to the modelling of general memristive devices. We use the same model template we have demonstrated in Sec. II, where  $f_1$  specifies the device's I-V relationship,  $f_2$  describes the dynamics of the internal unknown. For general memristive devices, there are several equations available for  $f_1$  and  $f_2$ , from existing models such as the linear and non-linear ion drift models [31], Simmons tunnelling barrier model [50], TEAM/VTEAM model [34, 51], Yakopcic's model [32, 33], *etc.* In this section, we examine the reason why they do not work well in simulation, especially in DC analysis. We first summarize the common issues with the  $f_1$  and  $f_2$  functions used in them, then examine the individual problems of each  $f_1/f_2$  function, and list our improvements in Table II and Table III.

As discussed earlier, both  $f_1$ , the I-V relationship, and  $f_2$ , the internal unknown dynamics, are often highly non-linear and asymmetric *wrt* positive and negative voltages; available  $f_1$  and  $f_2$  functions often use discontinuous and fast-growing components in them, *e.g.*, exponential, sinh functions, power functions with a large exponent, *etc.* These components result in difficulty of convergence in simulation. To overcome these difficulties, similar to what we did in Sec. IV for the RRAM model, we can use smooth and safe functions.

The key idea of the design of smooth functions is to combine common elementary functions to approximate the original non-smooth ones. A parameter common to all these functions, *aka*. smoothing factor, is used to control the trade-off between better approximation and more smoothness, which is often synonymous to better convergence. Similar ideas apply to safe functions. For the fast-growing functions, their "safe" versions limit the maximum slope the functions can reach, then linearize the functions to keep the slopes constant beyond those points. For functions that are not defined for all real inputs, *e.g.*, sqrt, log, *etc.*, their "safe" versions clip the inputs using smoothclip such that these functions will never get invalid inputs.

Specifically, for the available  $f_1$  and  $f_2$  functions, the if-then-else statements can be replaced with smoothswitch. The exp and sinh functions can be replaced with safeexp and safesinh. The power functions, *e.g.*, pow(a, b), can also be replaced with safeexp(b\*safelog(a)).

We have implemented common smooth and safe functions in MAPP. For example, issuing "help smoothclip" within MAPP will display more information on the usage of smoothclip. For Verilog-A, we have implemented these smooth and safe functions as "analog functions", listed them in a separate file in Appendix C-C for model developers to use conveniently.

The use of smooth and safe functions are more than numerical tricks, and they do not necessarily make models less physical. On the contrary, physical systems are usually smooth. For example, when switching the voltage of a two-terminal device across zero, the current should change continuously and smoothly. Therefore, compared with the original if-then-else statements, the smoothswitch version is likely to be closer to physical reality. The same applies to the safe functions we use in our models. For example, there are no perfect exponential relationships in physical reality. Even the growth rate of bacteria, which is often characterized as exponential in time, will saturate eventually. Another quantity often modelled using exponential functions is the current through a p-n junction. When the voltage indeed becomes large,

<sup>&</sup>lt;sup>17</sup>Some simulators implement a technique known as "limiting correction", which is compatible with SPICE's limiting formulation. Our sinhlim can also be incorporated there.

the junction doesn't really give out next to infinite current. Instead, other factors come into play — the temperature will become too high that the structure will melt. This is not considered when writing the exponential I-V relationship; the use of exponential function is not to capture the physics exactly, but more an approximation and simplification of physical reality. So the use of safeexp and safesinh is more than just a means to prevent numerical explosion, but also a fix to the original over-simplified models.

| No. | Original f <sub>1</sub>                                                                                                                                    | Comments and improved $f_1$                                                                                                                                                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $f_1 = (R_{on} \cdot s + R_{off} \cdot (1-s))^{-1} \cdot vpn.$                                                                                             | Can have division-by-zero when $s = R_{off}/(R_{on} - R_{off})$ .<br>We use<br>$y = \text{smoothclip}(s - R_{off}/(R_{on} - R_{off}), \text{ smoothing}) + R_{off}/(R_{on} - R_{off})$ ,<br>then<br>$f_1 = (R_{on} \cdot y + R_{off} \cdot (1 - y))^{-1} \cdot vpn$ .                                      |

| 2   | $f_1 = \frac{1}{R_{on}} \cdot e^{-\lambda \cdot (1-s)} \cdot vpn.$                                                                                         | We change exponential function to safeexp().                                                                                                                                                                                                                                                               |

| 3   | $f_1 = s^n \cdot \beta \cdot \sinh(\alpha \cdot vpn) + \chi \cdot (\exp(\gamma \cdot vpn) - 1).$                                                           | We change sinh to safesinh(), exponential function to safe exp().                                                                                                                                                                                                                                          |

| 4   | $f_1 = \begin{cases} A_1 \cdot s \cdot \sinh(B \cdot vpn), & \text{if } vpn \ge 0\\ A_2 \cdot s \cdot \sinh(B \cdot vpn), & \text{otherwise.} \end{cases}$ | We change sinh to safesinh(), then smooth the function.<br>$\begin{aligned} f_{1p} &= A_1 \cdot s \cdot \text{safesinh}(B \cdot vpn, \ maxslope), \\ f_{1n} &= A_2 \cdot s \cdot \text{safesinh}(B \cdot vpn, \ maxslope), \\ f_1 &= \text{smoothswitch}(f_{1n}, f_{1p}, vpn, \ smoothing). \end{aligned}$ |

| 5   | $f_1 = I_0 \cdot \exp\left(-\frac{Gap}{g_0}\right) \cdot \sinh(\frac{vpn}{V_0}).$                                                                          | We express $Gap$ using s:<br>$Gap = s \cdot minGap + (1 - s) \cdot maxGap$ .<br>Then we change sinh to safesinh(), exponential function to<br>safeexp().                                                                                                                                                   |

**TABLE II:** The available I-V relationships  $(f_1(vpn, s)$  functions) for general memristive devices, their problems and our improvements. One common problem with existing  $f_2$  functions is the range of the internal unknown. We have discussed this problem in Sec. IV in the context of RRAM device models. The  $f_2$  functions available either neglect this issue or use window functions to set the bounds for the internal unknown. From the discussion in Sec. IV, using window functions introduces modelling artifacts that limit the usage of the model to only transient simulation. To fix this problem, we apply the same modelling technique using clipping functions in our memristor models.

Another problem with the available  $f_2$  functions is the way they handle DC hysteresis. As discussed earlier, DC hysteresis is observed in forward and backward DC sweeps; it accounts for the pinched I-V curves when voltage is moving infinitely slow. From the model example hys\_example in Sec. II, we can conclude that DC hysteresis results from the model's DC solution curve folding backward in voltage, which creates multiple stable solutions of internal state variable at certain voltages. In fact, from the equations of TEAM/VTEAM model and Yakopcic's model, we can see an attempt to model DC hysteresis. However, the way it is done in both these models is to set  $f_2 = 0$  within a certain voltage range, e.g., when voltage is close to 0. In this way, as long as the voltage is within this range, there are infinitely many solutions for the model, regardless of values of s. During transient simulation, s will just keep its old value from the previous time point. In DC analysis, if s also keeps its old value from the last sweeping point, there can be DC hysteresis. However, since s actually has infinitely many solutions within this voltage range, the equation system becomes ill-conditioned. The circuit Jacobian matrix can also become singular, since s has no control over the value of  $f_2$ . Homotopy analysis won't work with these device models since there is no solution curve to track. Even in DC operating point (OP) analysis, the OP can have a random s as part of the solution, depending on the initial condition, and if it is not provided, on how the OP analysis is implemented. DC sweep results also depend on how DC sweep is written, particularly on the way the old values are used as initial guesses for current steps.<sup>18</sup> In other words, because of the model is ill-conditioned, the behaviour of the model is specific to the implementation

<sup>&</sup>lt;sup>18</sup>For example, if the DC sweep implements predictor, when sweeping across the hysteresis range of voltage, s may not stay flat.

| No. | <b>Original</b> <i>f</i> <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                        | Comments and improved f <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | Linear ion drift model:                                                                                                                                                                                                                                                                                                                                                                                                                      | No DC hysteresis. Doesn't ensure $0 \le s \ge 1$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |