# Automated Tiling of Unstructured Mesh Computations with Application to Seismological Modelling

FABIO LUPORINI, Imperial College London

MICHAEL LANGE, Imperial College London

CHRISTIAN T. JACOBS, University of Southampton

GERARD J. GORMAN, Imperial College London

J. RAMANUJAM, Louisiana State University

PAUL H. J. KELLY, Imperial College London

Sparse tiling is a technique to fuse loops that access common data, thus increasing data locality. Unlike traditional loop fusion or blocking, the loops may have different iteration spaces and access shared datasets through indirect memory accesses, such as A[map[i]] – hence the name "sparse". One notable example of such loops arises in discontinuous-Galerkin finite element methods, because of the computation of numerical integrals over different domains (e.g., cells, facets). The major challenge with sparse tiling is implementation – not only is it cumbersome to understand and synthesize, but it is also onerous to maintain and generalize, as it requires a complete rewrite of the bulk of the numerical computation. In this article, we propose an approach to extend the applicability of sparse tiling based on raising the level of abstraction. Through a sequence of compiler passes, the mathematical specification of a problem is progressively lowered, and eventually sparse-tiled C for-loops are generated. Besides automation, we advance the state-of-the-art by introducing: a revisited, more efficient sparse tiling algorithm; support for distributed-memory parallelism; a range of fine-grained optimizations for increased run-time performance; implementation in a publicly-available library, SLOPE; and an in-depth study of the performance impact in Seigen, a real-world elastic wave equation solver for seismological problems, which shows speed-ups up to 1.28× on a platform consisting of 896 Intel Broadwell cores.

CCS Concepts: • Computing methodologies  $\rightarrow$  Parallel algorithms; • Mathematics of computing  $\rightarrow$  Mathematical software performance; • Software and its engineering  $\rightarrow$  Compilers; Domain specific languages;

Additional Key Words and Phrases: Finite element method, unstructured mesh, compiler, performance optimization, loop fusion, loop tiling, sparse tiling

#### **ACM Reference format:**

Fabio Luporini, Michael Lange, Christian T. Jacobs, Gerard J. Gorman, J. Ramanujam, and Paul H. J. Kelly. 2022. Automated Tiling of Unstructured Mesh Computations with Application to Seismological Modelling. 1, 1, Article 1 (February 2022), 30 pages.

This work was supported by the Engineering and Physical Sciences Research Council through grants EP/I00677X/1, EP/L000407/1, EP/I012036/1], by the Imperial College London Department of Computing, and by the Imperial College London Intel Parallel Computing Centre (IPCC). The work of J. Ramanujam is supported by the US National Science Foundation award CCF-1619303, the Louisiana Board of Regents contract LEQSF(2016-19)-RD-B-03 and by Louisiana State University. The authors would like to thank the HPC Service Support team at Imperial College London for their help with the Helen cluster. The authors would also like to thank Gheorghe-Teodor Bercea, Lawrence Mitchell, and David Ham for their suggestions during the development of this project..

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

1:2 F. Luporini et al.

DOI: 10.1145/nnnnnnn.nnnnnnn

## 1 INTRODUCTION

In many unstructured mesh applications, for example those approximating the solution of partial differential equations (PDEs) using the finite volume or the finite element method, sequences of numerical operators accessing common fields need to be evaluated. Usually, these operators are implemented by iterating over sets of mesh elements and computing a kernel in each element. In languages such as C or Fortran, the resulting sequence of loops is typically characterized by heterogeneous iteration spaces and accesses to shared datasets (reads, writes, increments) through indirect pointers, like A[map[i]]. One notable example of such operators/loops arises in discontinuous-Galerkin finite element methods, in which numerical integrals over different domains (e.g., cells, facets) are evaluated; here, A could represent a discrete function, whereas map could store connectivity information (e.g., from mesh elements to degrees of freedom). In this article, we devise compiler theory and technology to automate a sophisticated version of *sparse tiling*, a technique to maximize data locality when accessing shared fields (like the A and map arrays in the earlier example), which consists of fusing a sequence of loops by grouping iterations such that all data dependencies are honored. The goal is to improve the overall application performance with minimal disruption (none, if possible) to the source code.

Three motivating real-world applications for this work are Hydra, Volna and Seigen. Hydra [30] is a finite-volume computational fluid dynamics application used at Rolls Royce for the simulation of next-generation components of jet engines. Volna [11] is a finite-volume computational fluid dynamics application for the modelling of tsunami waves. Seigen [17] aims to solve the elastic wave equation using the discontinuous Galerkin finite element method for seismic exploration purposes. All these applications are characterized by the presence of a time-stepping loop, in which several loops over the mesh (thirty-three in Hydra, ten in Volna, twenty-five in Seigen) are repeatedly executed. These loops are characterized by the irregular dependence structure mentioned earlier, with for example indirect increments in one loop (e.g., A[m[i]] += f(...)) followed by indirect reads in one of the subsequent loops (e.g., b = g(A[n[j]])). The performance achievable by Seigen through sparse tiling will extensively be studied in Section 7.

Although our work is general in nature, we are particularly interested in supporting increasingly sophisticated seismological problems that will be developed on top of Seigen. This has led to the following strategic decisions:

Automation, but no interest in legacy codes Sparse tiling is an "extreme optimization". An implementation in a low level language requires a great deal of effort, as a thoughtful restructuring of the application is necessary. In common with many other low level transformations, it also makes the source code impenetrable, affecting maintenance and extensibility. We therefore aim for a fully automated system based on domain-specific languages (DSLs), which abstracts sparse tiling through a simple interface (i.e., a single construct to define a scope of fusible loops) and a tiny set of parameters for performance tuning (e.g., the tile size). We are not interested in automating sparse tiling in legacy codes, in which the key computational aspects (e.g., mesh iteration, distributed-memory parallelism) are usually hidden for software modularity, thus making such a transformation almost impossible.

**Unstructured meshes require mixed static/dynamic analysis** Unstructured meshes are often used to discretize the computational domain, since they allow for an accurate representation of complex geometries. Their connectivity is stored by means of adjacency lists

(or equivalent data structure), which leads to indirect memory accesses within the loop nests. Indirections break static analysis, thus making purely compiler-based approaches insufficient. Runtime data dependence analysis is essential for sparse tiling, so integration of compiler and run-time tracking algorithms becomes necessary.

**Realistic datasets not fitting in a single node** Real-world simulations often operate on terabytes of data, hence execution on multi-node systems is often required. We have extended the original sparse tiling algorithm to enable distributed-memory parallelism.

Sparse tiling does *not* change the semantics of a numerical method – only the order in which some iterations are executed. Therefore, if most sections of a PDE solver suffer from computational boundedness and standard optimizations such as vectorization have already been applied, then sparse tiling, which targets memory-boundedness, will only provide marginal benefits (if any). Likewise, if a global reduction is present in between two loops, then there is no way for sparse tiling to be applied, unless the numerical method itself is rethought. This is regardless of whether the reduction is explicit (e.g., the first loop updates a global variable that is read by the second loop) or implicit (i.e., within an external function, as occurs for example in most implicit finite element solvers). These are probably the two greatest limitations of the technique; otherwise, sparse tiling may provide substantial performance benefits.

The rest of the article is structured as follows: in Section 2 we present the abstraction on which sparse tiling relies. We then show, in Section 3, examples of how the algorithm works on shared- and distributed-memory systems. This is followed by the formalization of the algorithms (Sections 4, 5) and the implementation of the compiler that automates sparse tiling (Section 6). The experimentation is described in Section 7. A discussion on the limitations of the algorithms and the future work that we expect to carry out in the years to come conclude the article.

## 2 THE LOOP CHAIN ABSTRACTION FOR UNSTRUCTURED MESH APPLICATIONS

The *loop chain* is an abstraction introduced in [21]. Informally, a loop chain is a sequence of loops with no global synchronization points, enriched with information to enable run-time data dependence analysis – necessary since indirect memory accesses inhibit common static approaches to loop optimization. The idea is to replace static with dynamic analysis, exploiting the information carried by a loop chain. Loop chains must somehow be added to or automatically derived (e.g., exploiting a DSL) from the input code. A loop chain will then be used by an *inspector/executor* scheme [32]. The *inspector* is an algorithm performing data dependence analysis using the information carried by the loop chain, which eventually produces a *sparse tiling schedule*. This schedule is used by the *executor*, a piece of code semantically equivalent to the original sequence of loops (i.e., computing the same result) executing the various loop iterations in a different order.

Before diving into the description of the loop chain abstraction, it is worth observing two aspects.

- The inspection phase introduces an overhead. In many scientific computations, the data dependence pattern is static or, more informally, "the topology does not change over time". This means that the inspection cost may be amortized over multiple iterations of the executor. If instead the mesh changes over time (e.g., in case of adaptive mesh refinement), a new inspection must be performed.

- To adopt sparse tiling in a code there are two options. One possibility is to provide a library

and leave the application specialists with the burden of carrying out the implementation

(re-implementation in case of legacy code). A more promising alternative consists of raising

the level of abstraction: programs can be written using a DSL; loop chain, inspector, and

executor can then be automatically derived at the level of the intermediate representation.

1:4 F. Luporini et al.

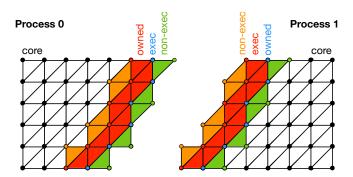

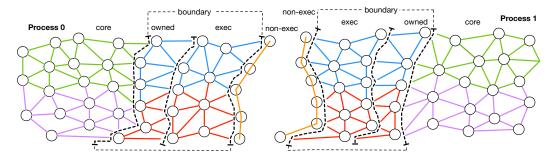

Fig. 1. Two partitions of a mesh distributed to two neighboring processes,  $P_0$  and  $P_1$ . The *core* region includes all iterations that can be processed without reading halo data. The *owned* iterations can be processed only by reading halo data. *Exec* is the set of iterations that must be executed because they indirectly write (increment) the owned iterations. The union of the *owned* and *exec* regions is referred to as the *boundary*. The *non-exec* region includes halo data which is indirectly read during the *exec* computation. The iterations in  $P_0$ 's ( $P_1$ 's) *exec* region are, logically, the same iterations in  $P_1$ 's ( $P_0$ 's) *owned* region; thus, we say that these iterations are "redundantly executed". Matching colors across the two processes represent identical subsets of iterations in the non-partitioned mesh. The image was inspired by an example in [27].

As we shall see in Section 6, the tools developed in this article enable both approaches, though our primary interest is in the automated approach (i.e., via DSLs).

These points will be further elaborated in later sections.

The loop chain abstraction was originally defined as follows:

- A loop chain  $\mathbb{L} = [L_0, L_1, ..., L_{n-1}]$  is an ordered sequence of n loops. There are no global synchronization points in between the loops. Although there may be dependencies between successive loops in the chain, the execution order of a loop's iterations does not influence the result.

- $\mathbb{D} = \{D_0, D_1, ..., D_{m-1}\}$  is a collection of m disjoint data spaces. Each loop accesses (reads from, writes to) a subset of these data spaces. An access can be either direct (e.g., A[i]) or indirect (e.g., A[map(i)]).

- $R_{L_l \to D_d}(i)$  and  $W_{L_l \to D_d}(i)$  are access relations for a loop  $L_l$  over a data space  $D_d \in \mathbb{D}$ . They indicate which locations in the data space  $D_d$  an iteration  $i \in L_l$  reads from and writes to, respectively. A loop chain must provide all access relations for all loops.

We here refine this definition, and specialize it for unstructured mesh applications. This allows the introduction of new concepts, necessary to extend the sparse tiling algorithm presented in [34]. Some terminology and ideas are inspired by the programming model of OP2, a library for unstructured mesh applications [14] used to implement the already mentioned Hydra code.

- A loop chain  $\mathbb{L} = [L_0, L_1, ..., L_{n-1}]$  is an ordered sequence of n loops. There are no global synchronization points in between the loops. Although there may be dependencies between successive loops in the chain, the execution order of a loop's iterations does not influence the result.

- $\mathbb{S} = \{S_0, S_1, ..., S_{m-1}\}$  is a collection of m disjoint iteration spaces. Possible iteration spaces are the topological entities of the mesh (e.g., cells, vertices) or the degrees of freedom associated with a function.

When using distributed-memory parallelism, an iteration space *S* is logically split into three contiguous regions: *core*, *boundary*, and *non-exec* (see also Figure 1). Given a generic process *P* executing a loop over *S*, these regions represent:

**core** the subset of iterations computed by *P* that does not depend on halo exchanges. In other words, these are *P*'s local iterations.

**boundary** the union of two sub-regions, *owned* and *exec*, which are defined next. The *boundary* region requires up-to-date halo data. Like *core*, *owned* contains iterations owned by *P*; the data produced by *owned* are sent out through a halo exchange. The *exec* iterations, instead, are executed because they indirectly write (increment) data in *P*'s *owned* sub-region.

**non-exec** the subset of iterations not computed by *P* mapping read-only data sent over to *P* during a halo exchange.

An iteration space is uniquely identified by a name and the sizes of its three regions.

- The *depth* is an integer indicating the extent of the boundary region. This is constant across all iteration spaces in  $\mathbb{S}$ .

- $\mathbb{M} = \{M_0, M_1, ..., M_{o-1}\}$  is a set of o maps. A map of arity a is a vector-valued function  $M: S_i \to S_j^a$  connecting elements in different iteration spaces. For example, we can express the mapping of a triangular cell c to three vertices  $v_0, v_1, v_2$  as  $M(c) = [v_0, v_1, v_2]$ ; here cells and vertices are iteration spaces, while  $c, v_0, v_1, v_2$  are iteration identifiers (i.e., natural numbers).

- A loop L<sub>i</sub> over the iteration space S is associated with one or more descriptors. A descriptor is

a 2-tuple <M, mode>. M is either a map from S to some other iteration spaces or the special

placeholder ⊥. In the former case, L<sub>i</sub> is accessing data associated with M(S) indirectly; in

the latter case, the data accesses are direct. mode is one of [r, w, i], indicating whether a

memory access is a read, write or increment.

There are a few crucial differences in this refined definition for the unstructured mesh case. One of them is the presence of iteration spaces in place of data spaces. In unstructured mesh applications, loops tend to access multiple data spaces associated with the same iteration space. A key observation is that if a loop is writing to some data spaces, then it is extremely likely that at least a subset of them will be accessed by the subsequent loop in the chain. The idea, therefore, is to rely on iteration spaces, rather than data spaces, to perform dependence analysis. This can substantially reduce the inspection cost, since typically  $|\mathbb{S}| << |\mathbb{D}|$ . Obviously, this relaxation might also create "false dependences", thus potentially affecting data communication. This would be the case if, for example, two consecutive, independent loops accessed different data fields associated with the same iteration space (e.g., *pressure* and *velocity* defined over the same set of degrees of freedom). In our experience, however, this rarely happens in practice (never in the case of the already mentioned Volna, Hydra and Seigen).

Another fundamental addition is the characterization of iteration spaces into the three regions core, boundary and non-exec. As we shall see, this separation is essential to enable distributed-memory parallelism. The extent of the boundary regions is captured by the *depth* of the loop chain. Informally, the *depth* tells how many extra "strips" of elements are provided by the neighboring processes. This allows some redundant computation along the partition boundary and also limits the depth of the loop chain (i.e., how many loops can be fused). The role of the parameter *depth* will be clear by the end of Section 5.

1:6 F. Luporini et al.

```

for t = 0 to T {

inspector = init inspector(...):

// L_0: loop over edges, increment vertices

for e = 0 to E {

// Three sets, edges, cells, and vertices

x = X + e;

E = set(inspector, "edges", core_edges,

tmp_0 = edges2vertices[e + 0];

boundary_edges, nonexec_edges, ...);

tmp_1 = edges2vertices[e + 1];

C = set(inspector, "cells", core_cells,

kernel1(x, tmp_0, tmp_1);

boundary_cells, nonexec_cells, ...);

V = set(inspector, "verts", core_verts,

boundary_verts, nonexec_verts, ...);

// L_1: loop over cells, increment vertices

for c = 0 to C {

// Two maps, from edges to vertices and from cells

res = R + c:

to vertices

tmp_0 = cells2vertices[c + 0];

e2vMap = map(inspector, E, V, edges2verts, ...);

tmp_1 = cells2vertices[c + 1];

c2vMap = map(inspector, C, V, cells2verts, ...);

tmp_2 = cells2vertices[c + 2];

kernel2(res, tmp_0, tmp_1, tmp_2);

// The loop chain comprises three loops

// Each loop has some descriptors

loop(inspector, E, { \bot, "r"}, {e2vMap, "i"});

// L_2: loop over edges, read vertices

loop(inspector, C, { \(\perp}\), \(\text{c2vMap}\), \(\text{i"}\));

for e = 0 to E {

loop(inspector, E, { \perp, "w"}, {e2vMap, "r"});

tmp_0 = edges2vertices[e + 0];

tmp_1 = edges2vertices[e + 1];

// Now can run the inspector

kernel3(tmp_0, tmp_1);

return inspection(mode, inspector, tile_size, ...);

```

(a) Example sequence of sparse-tilable loops.

Fig. 2. On the left, a "toy" program used as running example in Section 3 to illustrate the loop chain abstraction and show how the sparse tiling algorithms (inspection, execution) work. Note that all parameters passed to the kernels are pointers. On the right, a code snippet showing the loop chain corresponding to the program on the left. The syntax is very close to the actual API of SLOPE, the sparse tiling library that we have implemented, described in Section 6.

(b) Loop chain for the example program.

# 3 LOOP CHAIN, INSPECTION AND EXECUTION EXAMPLES

Using the example in Figure 2a, we describe the actions performed by our sparse tiling inspector. The inspector takes as input the loop chain illustrated in Figure 2b. We show two variants, for shared-memory and distributed-memory parallelism. The value of the variable mode in Figure 2b determines the variant to be executed.

# 3.1 Overview

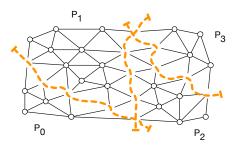

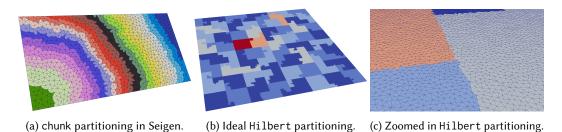

The inspector starts with partitioning the iteration space of a *seed loop*, for example  $L_0$ . Partitions are used to initialize tiles: the iterations of  $L_0$  falling in  $P_i$  – or, in other words, the edges in partition  $P_i$  – are assigned to the tile  $T_i$ . Figure 3 displays the situation after the initial partitioning of  $L_0$  for a given input mesh. There are four partitions, two of which ( $P_0$  and  $P_3$ ) are not connected through any edge or cell. These four partitions correspond to four tiles, [ $T_0$ ,  $T_1$ ,  $T_2$ ,  $T_3$ ], with  $P_i = T_i$ .

As detailed in the next two sections, the inspection proceeds by populating  $T_i$  with iterations from  $L_1$  and  $L_2$ . The challenge of this task is guaranteeing that all data dependencies – read after write, write after read, write after write – are honored. The output of the inspector is eventually passed to the executor. The inspection carries sufficient information for computing sets of tiles in parallel.  $T_i$  is always executed by a single thread/process and the execution is atomic; that is, it does not require communication with other threads/processes. When executing  $T_i$ , first all iterations from  $L_0$  are executed, then all iterations from  $L_1$  and finally those from  $L_2$ .

Fig. 3. Partitioning of the seed loop over edges. The vertices are illustrated to make the connectivity of the mesh clear, although they do not belong to any partition yet.

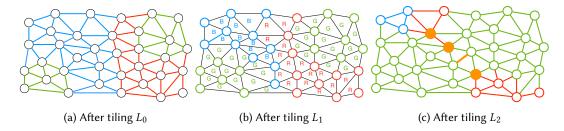

(a) A snapshot of the mesh after tiling  $L_0$ .

(c) A snapshot of the mesh after tiling  $L_1$ .

(b) The vertices are written by  $L_0$ , so a projection must be computed before tiling  $L_1$ . Here, the projection is represented as colored vertices.

(d) A snapshot of the mesh after tiling  $L_2$ .

Fig. 4. Four passes of the inspection algorithm for shared-memory parallelism.

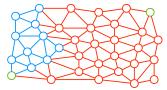

# 3.2 Inspection for Shared-Memory Parallelism

Similarly to OP2, to achieve shared-memory parallelism we use coloring. Two tiles that are given the same color can be executed in parallel by different threads. Two tiles can have the same color if they are not connected, because this ensures the absence of race conditions through indirect memory accesses during parallel execution. In the example we can use three colors: red (R), green (G), and blue (B).  $T_0$  and  $T_3$  are not connected, so they are assigned the same color. The colored tiles are shown in Figure 4a. In the following, with the notation  $T_i^c$  we indicate that the i-th tile has color c.

To populate  $[T_0^G, T_1^B, T_2^R, T_3^G]$  with iterations from  $L_1$  and  $L_2$ , we first have to establish a total ordering for the execution of partitions with different colors. Here, we assume the following order: green (G), blue (B), and red (R). This implies, for instance, that *all iterations* assigned to  $T_1^B$  must be executed *before all iterations* assigned to  $T_2^R$ . By "all iterations" we mean the iterations from  $L_0$  (determined by the seed partitioning) as well as the iterations that will later be assigned from tiling  $L_1$  and  $L_2$ . We assign integer positive numbers to colors to reflect their ordering, where a smaller number means higher execution priority. We can assign, for example, 0 to green, 1 to blue, and 2 to red.

1:8 F. Luporini et al.

To schedule the iterations of  $L_1$  to  $[T_0^G, T_1^B, T_2^R, T_3^G]$ , we need to compute a *projection* for any write or local reduction performed by  $L_0$ . The projection required by  $L_0$  is a function  $\phi: V \to \mathbb{T}$  mapping the vertices in V – as indirectly incremented during the execution of  $L_0$ , see Figure 2a – to a tile  $T_i^c \in \mathbb{T}$ . Consider the vertex  $v_0$  in Figure 4b.  $v_0$  has 7 incident edges, 2 of which belong to  $T_0^G$ , while the remaining 5 to  $T_1^B$ . Since we established that G < B,  $v_0$  can only be read after  $T_1^B$  has finished executing the iterations from  $L_0$  (i.e., the 5 incident blue edges). We express this condition by setting  $\phi(v_0) = T_1^B$ . Observe that we can compute  $\phi$  by iterating over V and, for each vertex, applying the maximum function (MAX) to the color of the adjacent edges.

We now use  $\phi$  to schedule  $L_1$ , a loop over cells, to the tiles. Consider again  $v_0$  and the adjacent cells  $[c_0, c_1, c_2]$  in Figure 4b. These three cells have in common the fact that they are adjacent to both green and blue vertices. For  $c_1$ , and similarly for the other cells, we compute  $\text{MAX}(\phi(v_0), \phi(v_1), \phi(v_2)) = \text{MAX}(B, G, G) = B = 1$ . This establishes that  $c_1$  must be assigned to  $T_1^B$ , because otherwise  $(c_1$  assigned instead to  $T_0^G$ ) a read to  $v_0$  would occur before the last increment from  $T_1^B$  took place. Indeed, we recall that the execution order, for correctness, must be "all iterations from  $[L_0, L_1, L_2]$  in the green tiles before all iterations from  $[L_0, L_1, L_2]$  in the blue tiles". The scheduling of  $L_1$  to tiles is displayed in Figure 4c.

To schedule  $L_2$  to  $[T_0^G, T_1^B, T_2^R, T_3^G]$  we employ a similar process. Vertices are again written by  $L_1$ , so a new projection over V will be necessary. Figure 4d shows the output of this last phase.

Fig. 5. Tiling the program in Figure 2a for shared-memory parallelism can lead to conflicts. Here, the two green tiles eventually become adjacent, creating race conditions.

Conflicting Colors. It is worth noting how  $T_2^R$  "consumed" the frontier elements of all other tiles every time a new loop was scheduled. Tiling a loop chain consisting of k loops has the effect of expanding the frontier of a tile of at most k vertices. With this in mind, we re-inspect the loop chain of the running example, although this time employing a different execution order – blue (B), red (R), and green (G) – and a different seed partitioning. Figure 5 shows that, by applying the same procedure described in this section,  $T_0^G$  and  $T_3^G$  will eventually become adjacent. This violates the precondition that tiles can be given the same color, and thus run in parallel, as long as they are not adjacent. Race conditions during the execution of iterations belonging to  $L_2$  are now possible. This problem will be solved in Section 5.

# 3.3 Inspection for Distributed-Memory Parallelism

In the case of distributed-memory parallelism, the mesh is partitioned and distributed to a set of processes. Neighboring processes typically exchange (MPI) messages before executing a loop  $L_j$ . A message includes all "dirty" dataset values required by  $L_j$  modified by any  $L_k$ , with  $L_k < L_j$ . In the running example,  $L_0$  writes to vertices, so a subset of values associated with border vertices must be communicated prior to the execution of  $L_1$ . To apply sparse tiling, the idea is to push all communications to the beginning of the loop chain: as we shall see, this increases the amount

of data to be communicated at a time, but also reduces the number of synchronizations (only 1 synchronization between each pair of neighboring processes per loop chain execution).

From Section 2 it is known that, in a loop chain, a set is logically split into three regions, *core*, *boundary*, and *non-exec*. The boundary tiles, which originate from the seed partitioning of the boundary region, will include all iterations that cannot be executed until the communications have terminated. The procedure described for shared-memory parallelism – now performed individually by each process on a partition of the input mesh – is modified as follows:

- (1) The core region of the seed loop L<sub>0</sub> is partitioned into tiles. Unless aiming for a mixed distributed/shared-memory scheme, there is no need to assign identical colors to unconnected tiles, as a process will execute its own tiles sequentially. Colors are assigned increasingly, with T<sub>i</sub> given color i. As long as tiles with contiguous ID are also physically contiguous in the mesh, this assignment retains memory access locality when "jumping" from executing T<sub>i</sub> to T<sub>i+1</sub>.

- (2) The same process is applied to the boundary region. Thus, a situation in which a tile includes iterations from both the core and the boundary regions is prevented by construction. Further, all tiles within the boundary region are assigned colors higher than those used for the core tiles. This constrains the execution order: no boundary tiles will be executed until all core tiles are computed.

- (3) We map the whole non-exec region of  $L_0$  to a single special tile,  $T_{ne}$ . This tile has the highest color and will actually never be executed.

Fig. 6. A snapshot of the two mesh partitions on Process 0 and Process 1 after inspecting the seed loop  $L_0$  for distributed-memory parallelism. On each process, there are five tiles in total: two in the core region (green and violet), two in the boundary region (red and light blue), and  $T_{ne}$ . The boundary tiles can safely cross the owned and exec sub-regions (i.e., the local iterations and the iterations to be redundantly computed, respectively). However, no tile can include iterations from both the core and the boundary regions.

From this point on, the inspection proceeds as in the case of shared-memory parallelism. The application of the MAX function when scheduling  $L_1$  and  $L_2$  makes higher color tiles (i.e., those having lower priority) "expand over" lower color ones.

In Figure 6, a mesh is partitioned over two processes and a possible seed partitioning and tiling of  $L_0$  illustrated. We observe that the two boundary tiles (the red and light blue ones) will expand over the core tiles as  $L_1$  and  $L_2$  are tiled, which eventually results in the scheduling illustrated in Figure 7. Roughly speaking, if a loop chain consists of n loops and, on each process, n-1 extra layers of iterations are provided (the exec regions in Figure 6), then all boundary tiles are correctly computed.

1:10 F. Luporini et al.

Fig. 7. A snapshot of the two mesh partitions on Process 0 and Process 1 at the end of the inspection for distributed-memory parallelism.  $T_{ne}$  expands over the boundary region, which minimizes the amount of redundant computation to be performed. At the end of the execution phase, the orange edges will contain "dirty values", but correctness is not affected as the exec region only includes off-process data. The boundary tiles expand over the core region: this is essential for correctness since none of the red and blue entities from  $[L_0, L_1, L_2]$  can be executed until the MPI communications have terminated.

The schedule produced by the inspector is subsequently used by the executor. On each process, the executor starts with triggering the MPI communications required for the computation of boundary tiles. All core tiles are then computed, since no data from the boundary region is necessary. Hence, computation is overlapped with communication. As all core tiles are computed and the MPI communications terminated, the boundary tiles can finally be computed.

Efficiency considerations. The underlying hypothesis is that the increase in data locality will outweigh the overhead induced by the redundant computation and by the bigger volume of data exchanged. This is motivated by several facts: (i) the loops being memory-bound; (ii) the core region being much larger than the boundary region; (iii) the amount of redundant computation being minimized through the special tile  $T_{ne}$ , which progressively expands over the boundary region, thus avoiding unnecessary calculations.

## 4 DATA DEPENDENCY ANALYSIS

The loop chain abstraction, described in Section 2, provides the information to construct an inspector capable of analyzing data dependencies and thus build a legal sparse tiling schedule. The dependencies between two different loops may be of type flow (read after write), anti (write after read), or output (write after write). Further, there may be "reduction dependencies" between iterations of the same loop.

## 4.1 Cross-Loop Dependences

Assume that loop  $L_x$ , having iteration space  $S_x$ , precedes loop  $L_y$ , having iteration space  $S_y$ , in the loop chain. Let  $e_x$  be a generic iteration in  $S_x$ . Let M be a map of arity a between two iteration spaces. Let mode  $\in \{w, r, i\}$  indicate whether an iteration is written, read, or incremented. We represent direct and indirect accesses as follows.

**Direct access**  $\perp_{S_x}^{\text{mode}}(e_x) \to \{\{e_x\},\emptyset\}$ . In particular, if  $\perp_{S_x}^{\text{mode}}(e_x) = \emptyset$ , then no direct write/read/increment is performed by  $e_x$  when computing  $L_x$ .

Indirect access  $M_{S_x \to S_y}^{\text{mode}}(e_x) \to \{\{e_{y_0}, ..., e_{y_{a-1}}\}, \emptyset\}$ . As per direct accesses,  $M_{S_x \to S_y}^{\text{mode}}(e_x) = \emptyset$  means that  $e_x$  does not indirectly write/read/increment  $S_y$  when computing  $L_x$ .

A direct access is a special case of indirect access when y = x and  $M_{S_x \to S_y}$  is the identity mapping. However, we here keep the distinction between the two types of access explicit due to their relevance in the sparse tiling algorithms, as explained in Section 5.

By considering pairs of points  $(e_x, e_y)$  in the iteration spaces of the two loops  $L_x$  and  $L_y$ , namely  $e_x \in S_x$  and  $e_y \in S_y$ , we can enumerate all possible dependences. For brevity, we do not distinguish between increments and writes; we also assume that at least one of the two loops accesses data indirectly. Let  $S_z$  be a generic iteration space in the loop chain. Hence, the flow dependences are:

$$\{e_x \to e_y \mid \underbrace{(\bot_{S_x}^w(e_x) \cap M_{S_y \to S_x}^r(e_y))}_{\text{@ direct w. indirect r}} \cup \underbrace{(M_{S_x \to S_y}^w(e_x) \cap \bot_{S_y}^r(e_y))}_{\text{@ indirect w. direct r}} \cup \underbrace{(M_{S_x \to S_z}^w(e_x) \cap M_{S_y \to S_z}^r(e_y))}_{\text{@ indirect w. indirect r}} \neq \emptyset\}.$$

In essence, there is a flow dependence between two iterations from different loops when one of those iterations writes to an element and the other iteration reads from the same element, directly or indirectly. To capture all these flow dependences, the inspection algorithm builds *projections* from one loop to another. We saw an example in Section 3.2: the loop over cells  $(S_x)$  performed an indirect increment to a dataset associated with vertices  $(S_z)$ , which was then read by the subsequent loop over edges  $(S_y)$ . Such flow dependence was of type  $\mathfrak{G}$  (see definition above). For each vertex  $e_z \in S_z$ , the projection (illustrated in Figure 4b) captured the *last tile* indirectly writing to (incrementing)  $e_z$ , exploiting the color (i.e., the scheduling priority) of the source iterations. A flow dependence of type  $\mathfrak{T}$  would be even simpler to deal with, as it would not require the use of the indirect map  $M_{S_X \to S_z}$  to update the color of the iterations.

Likewise, we can enumerate the anti and output dependences:

$$\{e_x \to e_y \mid (\bot_{S_x}^r(e_x) \cap M_{S_y \to S_x}^w(e_y)) \cup (M_{S_x \to S_y}^r(e_x) \cap \bot_{S_y}^w(e_y)) \cup (M_{S_x \to S_z}^r(e_x) \cap M_{S_y \to S_z}^w(e_y)) \neq \emptyset \}.$$

$$\{e_x \to e_y \mid (\bot_{S_x}^w(e_x) \cap M_{S_y \to S_x}^w(e_y)) \cup (M_{S_x \to S_y}^w(e_x) \cap \bot_{S_y}^w(e_y)) \cup (M_{S_x \to S_z}^w(e_x) \cap M_{S_y \to S_z}^w(e_y)) \neq \emptyset \}.$$

Projections for this type of dependences are built analogously to that described above.

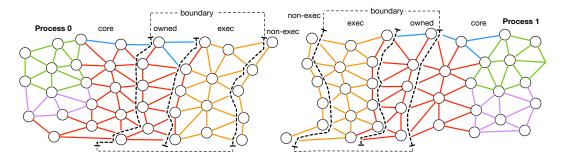

The inspection algorithm building projections for all flow, anti, and output dependences is provided in Algorithm 3 and discussed in Section 5.1.4. How the inspector leverages data dependence analysis (i.e., projections) to schedule iterations to tiles (i.e., the tiling function) is formalized in Algorithm 4 and commented in Section 5.1.5.

## 4.2 Intra-Loop Dependences

There also are local reductions, or "reduction dependencies", between two or more iterations of the same loop when those iterations increment the same location(s); that is, when they read, modify with a commutative and associative operator, and write to the same location(s). The reduction dependencies in  $L_x$  are:

$$\{e_{x_1} \to e_{x_2} \mid M^i_{S_x \to S_z}(e_{x_1}) \cap M^i_{S_x \to S_z}(e_{x_2}) \neq \emptyset\}.$$

A reduction dependency between two iterations within the same loop indicates that those two iterations must be executed atomically with respect to each other. As we explained in Section 3.2, the inspection algorithm uses coloring to ensure atomic increments.

#### 5 ALGORITHMS

The pseudo-code for the sparse tiling inspector is shown in Algorithm 1. Given a loop chain and a seed tile size, the algorithm produces a schedule suitable for mixed distributed/shared-memory parallelism. This schedule – in essence, a set of populated tiles – is used by the executor to perform the sparse-tiled computation. The executor pseudo-code is displayed in Algorithm 2. The next two

1:12 F. Luporini et al.

| Symbol                                   | Meaning                                                     |  |

|------------------------------------------|-------------------------------------------------------------|--|

| L                                        | The loop chain                                              |  |

| $L_j$                                    | The $j$ -th loop in $\mathbb L$                             |  |

| seed                                     | The index of the seed loop                                  |  |

| $S_j$                                    | The iteration space of $L_j$                                |  |

| $S_i^c, S_i^b, S_i^{\text{ne}}$          | The core, boundary, and non-exec regions of $S_j$           |  |

| $\stackrel{\circ}{D}$                    | A descriptor of a loop                                      |  |

| T                                        | The collection of tiles                                     |  |

| $\mathbb{T}[i]$                          | Accessing the $i$ -th tile, or $T_i$                        |  |

| $T_i^c, T_i^b, T_i^{\text{ne}}$ $\phi_S$ | The core, boundary, and non-exec regions of $T_i$           |  |

| $\dot{\phi}_S$                           | A projection $\phi_S : S \to \mathbb{T}$                    |  |

| Φ                                        | The collection of projections                               |  |

| $\sigma_i$                               | A tiling function $\sigma_i : S_i \to \mathbb{T}$ for $L_i$ |  |

| ts                                       | The seed tile size                                          |  |

| C                                        | The matrix of conflicting colors                            |  |

| Ax:y                                     | Algorithm x, line y                                         |  |

Table 1. Summary of the notation used throughout Section 5.

sections elaborate on the main steps of these algorithms. The notation is summarized in Table 1; the syntax Ax:y is a shortcut for "Algorithm x, line y". The implementation is discussed in Section 6.

```

ALGORITHM 1: The inspection algorithm

ALGORITHM 2: The executor algorithm

Input: The loop chain \mathbb{L}=[L_0,\ L_1,\ \ldots,\ L_{n-1}], a seed tile size ts Output: A collection of tiles \mathbb{T}, populated with iterations from \mathbb{L}

Input: A collection of tiles T

Result: Execute the loop chain

\text{1} \quad \mathbb{T}^c, \mathbb{T}^b \leftarrow \text{group\_tiles\_by\_region}(\mathbb{T});

1 seed \leftarrow 0, \Phi \leftarrow \emptyset, C \leftarrow \bot;

2 \sigma_{\text{seed}}, \mathbb{T} \leftarrow \text{partition}(S_{\text{seed}}, \text{ts});

2 start MPT comm():

seed_map \leftarrow find_map(S_{seed}, \mathbb{L});

4

3 foreach color do

conflicts \leftarrow false:

foreach T \in \mathbb{T}^c s.t. T.color == color do

color(T, seed map);

6

execute_tile(T);

7

for j = 1 to n - 1 do

6

end

project(L_{j-1}, \sigma_{j-1}, \Phi, C);

8

7 end

\sigma_i \leftarrow \mathsf{tile}(L_i, \Phi);

\operatorname{assign}(\sigma_j, \mathbb{T});

10

8 end MPT comm():

11

end

12

if has_conflicts(C) then

9 foreach color do

foreach T \in \mathbb{T}^b s.t. T.color == color do

10

add_fake_connection(seed_map, C);

14

11

execute\_tile(T);

15

end

12

end

16 while conflicts;

13 end

17 compute_local_maps(T);

18 return T

```

#### 5.1 Inspector

5.1.1 Choice of the seed loop. The seed loop  $L_{\rm seed}$  is used to initialize the tiles. Theoretically, any loop in the chain can be chosen as seed. Supporting distributed-memory parallelism, however, is cumbersome if  $L_{\rm seed} \neq L_0$ . This is because more general schemes for partitioning and coloring would be needed to ensure that no iterations in any  $S_j^b$  are assigned to a core tile. A limitation of our inspector algorithm in the case of distributed-memory parallelism is that it must be  $L_{\rm seed} = L_0$ .

In the special case in which there is no need to distinguish between core and boundary tiles (because a program is executed on a single shared-memory system),  $L_{\rm seed}$  can be chosen arbitrarily. If we however pick  $L_{\rm seed}$  in the middle of the loop chain, that is  $L_0 < ... < L_{\rm seed} < ... < L_{n-1}$ , a mechanism for constructing tiles in the reverse direction ("backwards"), from  $L_{\rm seed}$  towards  $L_0$ , is necessary. In [34], we propose two "symmetric" algorithms to solve this problem, forward tiling and backward tiling, with the latter using the MIN function in place of MAX when computing

projections. For ease of exposition, and since in the fundamental case of distributed-memory parallelism we are imposing  $L_{\text{seed}} = L_0$ , we here neglect this distinction<sup>1</sup>.

5.1.2 Tiles initialization. Let ts be the user-specified seed tile size. The algorithm starts with partitioning  $S_{\text{seed}}^c$  into m subsets  $\{P_0, P_1, ..., P_{m-1}\}$  such that  $|P_i| = ts$  (except possibly for  $P_{m-1}$ ),  $P_i \cap P_j = \emptyset$ , and  $\bigcup_{i=0}^{m-1} P_i = S_{\text{seed}}^c$ . Among all possible legal partitionings, we choose the one that splits  $S_{\text{seed}}^c$  into blocks of ts contiguous iterations, with  $P_0 = \{0, ..., ts-1\}$ ,  $P_1 = \{ts, ..., 2ts-1\}$ , and so on. We analogously partition  $S_{\text{seed}}^b$  into k subsets. We create m+k+1 tiles, one for each of these partitions and one extra tile for  $S_{\text{seed}}^{\text{ne}}$ , namely  $\mathbb{T} = [T_0^c, ..., T_{m-1}^c, T_m^b, ..., T_{m+k-1}^b, T_{m+k}^{\text{ne}}]$ . At this point we have an assignment of iterations to tiles for  $L_{\text{seed}}$ ; that is, a tiling function  $\sigma_{\text{seed}}: S_{\text{seed}} \to \mathbb{T}$ . This initial partitioning phase occurs at A1: 2.

A tile  $T_i$  has four fields, as summarized in Table 2.

- The *region* is used by the executor to schedule tiles in a given order. This field is set right after the partitioning of  $L_{\text{seed}}$ , as a tile (by construction) exclusively belongs to  $S_{\text{seed}}^c$ , or  $S_{\text{seed}}^{\text{ne}}$ .

- The *iteration lists* contain the iterations in  $\mathbb{L}$  that  $T_i$  will have to execute. There is one *iteration list* for each  $L_j \in \mathbb{L}$ , indicated as  $[T_i]_j$ . At this stage of the inspection we have  $[T_i]_{\text{seed}} = [T_i]_0 = P_i$ , whereas still  $[T_i]_j = \emptyset$  for j = 1, ..., n 1.

- Local maps may be used for performance optimization by the executor in place of the global maps provided through the loop chain; this will be discussed in more detail in Section 7 and in the Supplementary Materials.

- The *color* provides a tile with a scheduling priority. If shared-memory parallelism is requested, adjacent tiles are given different colors (the adjacency relation is determined through the maps available in  $\mathbb{L}$ ). Otherwise, colors are assigned in increasing order (i.e.,  $T_i$  is given color i). The boundary tiles are always given colors higher than that of core tiles; the non-exect tile has the highest color. The assignment of colors is carried out by A1:6.

| Field            | Possible values                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------|

| region           | core, boundary, non-exec                                                                        |

| iterations lists | one list of iterations $[T_i]_i$ for each $L_i \in \mathbb{L}$                                  |

| local maps       | one list of local maps for each $L_i \in \mathbb{L}$ ; one local map for each map used in $L_i$ |

| color            | an integer representing the execution priority                                                  |

Table 2. The tile data structure.

- 5.1.3 The inspection loop. The inspection loop, starting at A1:7, schedules the remaining  $L_j \in \mathbb{L}$  by alternating dependence analysis and construction of tiling functions. The input is  $\sigma_{\text{seed}}$ . As seen in the previous sections, a projection is a function  $\phi_S: S \to \mathbb{T}$  that captures data dependences across loops. Initially, the projections set  $\Phi$  is empty (A1:1). Once a new loop is tiled,  $\Phi$  is updated by adding new projections or changing existing ones (see Section 5.1.4). Using  $\Phi$ , a new tiling function  $\sigma_i$  for  $L_i$  is derived (see Section 5.1.5).

- 5.1.4 Deriving a projection from a tiling function. Algorithm 3 takes as input (the descriptors of) an  $L_j$  and its tiling function  $\sigma_j : S_j \to \mathbb{T}$  to update  $\Phi$ . The algorithm also updates the conflicts matrix  $C \in \mathbb{N}^{m \times m}$ , which indicates whether two tiles having the same color will become adjacent.

A new projection  $\phi_S$  is needed if S is written by  $L_j$ . As explained in Section 4,  $\phi_S$  carries the necessary information to tile a subsequent loop accessing S. Let us consider the non-trivial case in

<sup>&</sup>lt;sup>1</sup>The algorithm implemented in SLOPE, the library presented in Section 6.1, supports backwards tiling for shared-memory parallelism.

1:14 F. Luporini et al.

which  $L_j$  writes indirectly to S through a map  $M: S_j \to S^a$ . To compute  $\phi_S$ , we first determine the inverse map  $M^{-1}$  (A3:5; an example is shown in Figure 8). Then, we iterate over all elements  $e \in S$  and we set  $\phi_S[e]$  to the last tile writing to e. This is accomplished by applying the MAX function over the color of the tiles accessing e (see A3:11), obtained through  $M^{-1}$ . This procedure was used, for example, to compute the projection in Figure 4b.

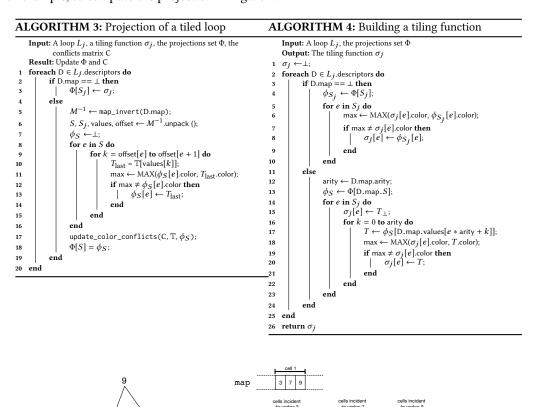

Fig. 8. Representation of an inverse map. The original map shows that the triangular cell 1 is adjacent to three vertices, namely 3, 7, and 9. The inverse map associates vertices to cells. Since the mesh is unstructured, different vertices can be incident to a different number of cells. The array offset provides the distance between two consecutive vertices in the inverse map. For instance, all entries in the inverse map between offset[3] and offset[4] are cells incident to vertex 3.

map

5.1.5 Deriving a tiling function from the available projections. Using  $\Phi$ , we compute  $\sigma_j$  as described in Algorithm 4. The algorithm is similar to the projection of a tiled loop (e.g., maps are used to access the neighborhood of a target iteration). The main difference is that now the projections in  $\Phi$  are used, rather than computed, to schedule iterations to tiles so that data dependences are honored. Finally,  $\sigma_j$  is used to populate the iteration lists  $[T_i]_j$ , for all  $T_i \in \mathbb{T}$  (see A1:10).

1

- 5.1.6 Detection of conflicts. If C indicates the presence of at least one conflict, say between  $T_{i_1}$  and  $T_{i_2}$ , we add a "fake connection" between these two tiles and loop back to the coloring stage.  $T_{i_1}$  and  $T_{i_2}$  are now connected, so they will be assigned different colors.

- 5.1.7 On the history of the algorithm. The first algorithm for generalized sparse tiling inspection was introduced in [34]. In this section, a new, enhanced version of that algorithm has been presented. In essence, the major differences are: (i) support for distributed-memory parallelism; (ii) use of coloring instead of a task graph for tile scheduling; (iii) speculative inspection with backtracking if a coloring conflict is detected; (iv) use of sets, instead of datasets, for data dependency analysis; (v) use of inverse maps for parallelization of the projection and tiling routines; (vi) computation of local maps. Most of these changes contributed to reduce the inspection cost, as discussed later.

#### 5.2 Executor

The sparse tiling executor is illustrated in Algorithm 2. It consists of four main phases: (i) exchange of halo regions amongst neighboring processes through non-blocking communications; (ii) execution of core tiles (in overlap with communication); (iii) wait for the termination of the communications; (iv) execution of boundary tiles.

As explained in Sections 3.3, a sufficiently deep halo region enables correct computation of the boundary tiles. Further, tiles are executed atomically, meaning that all iterations in a tile are computed without ever synchronizing with other processes. The depth of the boundary region, which affects the amount of off-process data to be redundantly computed, increases with the number n of loops to be fused. In the example in Figure 6, there are n = 3 loops, and three "strips" of extra vertices are necessary for correctly computing the fused loops without tile-to-tile synchronizations.

We recall from Section 2 that the *depth* of the loop chain indicates the extent of the boundary region. This parameter imposes a limit to the number of fusible loops. If  $\mathbb L$  includes more loops than the available boundary region – that is, if n > depth – then  $\mathbb L$  will have to be split into shorter loop chains, to be fused individually. As we shall see (Section 6), in our inspector/executor implementation the *depth* is controlled by the Firedrake's DMPlex module.

# 6 IMPLEMENTATION: SLOPE, PYOP2, AND FIREDRAKE

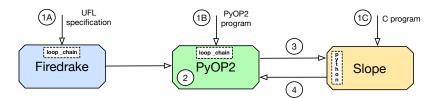

The implementation of automated sparse tiling is distributed over three open-source software modules.

**Firedrake** An established framework for the automated solution of PDEs through the finite element method [28].

**PyOP2** A module used by Firedrake to apply numerical kernels over sets of mesh components. Parallelism is handled at this level.

**SLOPE** A library for writing inspector/executor schemes, with primary focus on sparse tiling. PyOP2 uses SLOPE to apply sparse tiling to loop chains.

The SLOPE library is an open source embodiment of the algorithms presented in this article. The interplay amongst Firedrake, PyOP2 and SLOPE is outlined in Figure 9 and discussed in more detail in the following sections.

# 6.1 SLOPE: a Library for Sparse Tiling Irregular Computations

SLOPE is an open source software that provides an interface to build loop chains and to express inspector/executor schemes for sparse tiling<sup>2</sup>.

<sup>&</sup>lt;sup>2</sup>SLOPE is available at https://github.com/coneoproject/SLOPE

1:16 F. Luporini et al.

Fig. 9. Sparse tiling in the Firedrake-PyOP2-SLOPE framework. There are three ways of sparse tiling a loop chain: decorating a Firedrake program (1A), decorating a sequence of loops in a PyOP2 program (1B), writing both the loop chain and the inspector/executor codes explicitly in C through calls to SLOPE (1C). Both (1A) and (1B) use the *loop\_chain* interface (details in Section 6.2). PyOP2 derives the loop chain (2), essentially sets, maps and loops (see Section 2 and example in Figure 2b), from the kernels produced within the *loop\_chain* context. The loop chain is provided to SLOPE through its Python interface (3). SLOPE performs the inspection and returns its output, a tiles schedule, to PyOP2 (4). Eventually, the executor is generated and run by PyOP2.

The loop chain abstraction implemented by SLOPE has been formalized in Section 2. In essence, a loop chain comprises some sets (including the separation into core, boundary, and non-exec regions), maps between sets, and a sequence of loops. Each loop has one or more descriptors specifying what and how different sets are accessed. The example in Figure 2b illustrates the interface exposed by the library. SLOPE implements Algorithms 1, 3 and 4 from Section 5. Further, it provides additional features to estimate the effectiveness and to verify the correctness of sparse tiling, including generation of VTK files (suitable for Paraview [2]), to visualize the partitioning of the mesh into colored tiles, as well as insightful inspection summaries (showing, for example, number and average size of tiles, total number of colors used, time spent in critical inspection phases).

In the case of shared-memory parallelism, the following sections of code are parallelized through OpenMP:

**Inspection** The projection and tiling algorithms; in particular, the loops over set elements in Algorithm 3 and Algorithm 4).

**Execution** The computation of same colored tiles; that is, the two loops over tiles in Algorithm 2.

## 6.2 PyOP2: Lazy Evaluation and Interfaces

PyOP2 is a Python library offering abstractions to model an unstructured mesh – in terms of *sets* (e.g. vertices, edges), *maps* between sets (e.g., a map from edges to vertices to express the mesh topology), and *datasets* associating data to each set element (e.g. 3D coordinates to each vertex) – and applying numerical kernels to sets of entities [28]. In this section, we focus on the three relevant contributions to PyOP2 made through our work: (i) the interface to identify loop chains; (ii) the lazy evaluation mechanism that allows loop chains to be built; (iii) the interaction with SLOPE to automatically build and execute inspector/executor schemes.

To apply sparse tiling to a sequence of loops, the *loop\_chain* interface was added to PyOP2. This interface, exemplified in Figure 10, is also exposed to the higher layers, for example in Firedrake. In the listing, the name uniquely identifies a loop chain. Other parameters (most of them optional) are useful for performance evaluation and performance tuning. Amongst them, the most important are the tile\_size and the fusion\_scheme. The tile\_size specifies the initial average size for the seed partitions. The fusion\_scheme allows to specify how to break a long sequence of loops into

smaller loop chains, which makes it possible to experiment with a full set of sparse tiling strategies without having to modify the source code.

```

with loop_chain(name, tile_size, fusion_scheme, ...):

<some PyOP2 parallel loops are expressed/generated here>

```

Fig. 10. The *loop\_chain* interface in PyOP2.

PyOP2 exploits lazy evaluation of parallel loops to generate an inspector/executor scheme. The parallel loops encountered during the program execution – or, analogously, those generated through Firedrake – are pushed into a queue, instead of being executed immediately. The sequence of parallel loops in the queue is called the trace. If a dataset f needs to be read, for example because a user wants to inspect its values or a global linear algebra operation is performed, then the trace is traversed – from the most recent parallel loop to the oldest one – and a new sub-trace produced. The sub-trace includes all parallel loops that must be executed to evaluate f correctly. The sub-trace can then be executed or further pre-processed.

All loops in a trace that were created within a *loop\_chain* scope are sparse tiling candidates. In detail, the interaction between PyOP2 and SLOPE is as follows:

- (1) Figure 10 shows that a  $loop\_chain$  defines a new scope. As this scope is entered, a stamp  $s_1$  of the trace is generated. This happens "behind the scenes", because the  $loop\_chain$  is a Python context manager, which can execute pre-specified routines prior and after the execution of the body. As the  $loop\_chain$ 's scope is exited, a new stamp  $s_2$  of the trace is computed. All parallel loops in the trace generated between  $s_1$  and  $s_2$  are placed into a sub-trace for pre-processing.

- (2) The pre-processing consists of two steps: (i) "simple" fusion consecutive parallel loops iterating over the same iteration space that do not present indirect data dependencies are merged; (ii) generation of a loop chain representation for SLOPE.

- (3) In (ii), PyOP2 inspects the sequence of parallel loops and translates their metadata (sets, maps, loops) into a format suitable for the SLOPE's Python interface. SLOPE performs an inspection for the received loop chain and returns a tiles schedule to PyOP2 (i.e., it runs Algorithm 1).

- (4) A "software cache" mapping *loop\_chains* to *inspections* is used. This whole process needs therefore be executed only once for a given *loop\_chain*.

- (5) The executor is generated, compiled and run directly by PyOP2, with the help of an API provided by SLOPE. To run the executor, the tiles schedule produced in (3) is used.

# 6.3 Firedrake/DMPlex: the S-depth Mechanism for Extended Halo Regions

Firedrake uses DMPlex [23] to handle meshes. DMPlex is responsible for partitioning, distributing over multiple processes, and locally reordering a mesh. The MPI parallelization is therefore managed through Firedrake/DMPlex.

During the start-up phase, each MPI process receives a contiguous partition of the original mesh from DMPlex. The required PyOP2 sets, which can represent either topological components (e.g., cells, vertices) or function spaces, are created. As intuitively shown in Figure 1, these sets distinguish between multiple regions: core, owned, exec, and non-exec. Firedrake initializes the four regions exploiting the information provided by DMPlex.

To support the loop chain abstraction, Firedrake must be able to allocate arbitrarily deep halo regions. Both Firedrake and DMPlex have been extended to support this feature [19]. A parameter called *S-depth* (the name has historical origins, see for instance [7]) regulates the extent of the halo

1:18 F. Luporini et al.

regions. A value S-depth = n indicates the presence of n strips of off-process data elements in each set. The default value is S-depth = 1, which enables computation-communication overlap when executing a single loop at the price of a small amount of redundant computation along partition boundaries. This is the default execution model in Firedrake.

#### 7 PERFORMANCE EVALUATION

# 7.1 The Seigen Computational Framework

Seigen is a seismological modelling framework capable of solving the elastic wave equation on unstructured meshes. Exploiting the well-known velocity-stress formulation [39], the seismic model is expressible as two first-order linear PDEs, which we refer to as velocity and stress. These governing equations are discretized in space through the discontinuous-Galerkin finite element method. The evolution over time is obtained by using a fourth-order explicit leapfrog scheme based on a truncated Taylor series expansion of the velocity and stress fields. The particular choice of spatial and temporal discretizations has been shown to be non-dissipative [8]. More details can be found in [17]. Seigen, which is built on top of Firedrake, is part of OPESCI, an ecosystem of software for seismic imaging based on automated code generation [15].

Seigen has a set of test cases, which differ in various aspects, such as the initial conditions of the system and the propagation of waves. However, they are all based upon the same seismological model; from a computational viewpoint, this means that, in a time step, the same sequence of loops is executed. In the following, we focus on the explosive\_source test case (see the work by [12] for background details).

# 7.2 Implementation and Validation

In a time loop iteration, eight linear systems need to be solved, four from velocity and four from stress. Each solve consists of three macro-steps: assembling a global matrix A; assembling a global vector b; computing x in the system Ax = b. There are two global "mass" matrices, one for velocity and one for stress. Both matrices are time invariant, so they are assembled before entering the time loop, and block-diagonal, as a consequence of the spatial discretization employed (a block belongs to an element in the mesh). The inverse of a block-diagonal matrix is again block-diagonal and is determined by computing the inverse of each block. The solution of the linear system Ax = b, expressible as  $x = bA^{-1}$ , can therefore be evaluated by looping over the mesh and computing a "small" matrix-vector product in each element, where the matrix is a block in  $A^{-1}$ . Assembling the global vectors boils down to executing a set of loops over mesh entities, particularly over cells, interior facets, and exterior facets. Overall, twenty-five loops are executed in a time loop iteration. Thanks to the hierarchy of "software caches" employed by Firedrake, the translation from mathematical syntax into loops is only performed once.

Introducing sparse tiling into Seigen was relatively straightforward. Three steps were required: (i) embedding the time stepping loop in a *loop\_chain* context (see Section 6.2), (ii) propagating user input relevant for performance tuning, (iii) creating a set of *fusion schemes*. A fusion scheme establishes which sub-sequences of loops within a *loop\_chain* will be fused and the respective seed tile sizes. If no fusion schemes were specified, all of the twenty-five loops would be fused using a default tile size. As we shall see, operating with a set of small loop chains and heterogeneous tile sizes is often more effective than fusing long sequences of loops.

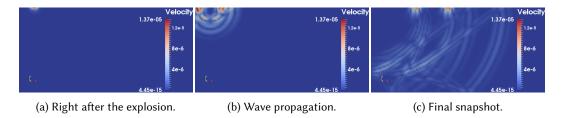

Seigen has several mechanisms to validate the correctness of the seismological model and the test cases. The numerical results of all code versions (with and without tiling) were checked and compared. Paraview was also used to verify the simulation output. Snapshots of the simulation output are displayed in Figure 11.

Fig. 11. Three phases of the explosive\_source test case in Seigen, following an explosion at a point source.

# 7.3 Computational Analysis of the Loops

We here discuss computational aspects of the twenty-five fusible loops. The following considerations derive from an analytical study of the data movement in the loop chain, extensive profiling through the Intel VTune Amplifier tool [16], and roofline models (available in [17]).

Our initial hypothesis was that Seigen would have benefited from sparse tiling. Not only does data reuse arise within single loops (e.g., by accessing vertex coordinates from adjacent cells), but also across consecutive loops, through indirect data dependencies. This seemed to make Seigen a natural fit for sparse tiling. The eight "solver" loops perform matrix-vector multiplications in each mesh element. It is well established that linear algebra operations of this kind are memory-bound. Four of these loops arise from velocity, the others from stress. There is significant data reuse amongst the four velocity loops and amongst the four stress loops, since the same blocks in the global inverse matrices are accessed. We therefore hypothesized performance gains if these loops were fused through sparse tiling.

We also observed that because of the particular mesh employed, the exterior facet loops, which implement the boundary conditions of the variational problems, have negligible cost. However, the cells and facets loops do have significant cost, and data reuse across them arises. Six loops iterate over the interior mesh facets to evaluate facet integrals, which ensure the propagation of information between adjacent cells in discontinuous-Galerkin methods. The operational intensity of these loops is much lower than that of cell loops, and memory-boundedness is generally expected. Consecutive facet and cell integral loops share fields, which creates cross-loop data reuse opportunities, thus strengthening the hypothesis about the potential of sparse tiling in Seigen.

All computational kernels generated in Seigen are optimized through COFFEE [24], a system used in Firedrake that, in essence, (i) minimizes the operation count by restructuring expressions and loop nests, and (ii) maximizes auto-vectorization opportunities by applying transformations such as array padding and by enforcing data alignment.

## 7.4 Setup and Reproducibility

There are two parameters that we can vary in explosive\_source: the polynomial order of the method, q, and the input mesh. We test the spectrum  $q \in \{1, 2, 3, 4\}$ . To test higher polynomial orders, changes to both the spatial and temporal discretizations would be necessary. For the spatial discretization, the most obvious choice would be tensor product function spaces, which at the moment of writing is still unavailable in Firedrake. We use as input a two-dimensional rectangular domain of fixed size  $300\times150$  tessellated with unstructured triangles (explosive\_source only supports two-dimension domains); to increase the number of elements in the domain, thus allowing to weak scale, we vary the mesh spacing h.

The generality of the sparse tiling algorithms, the flexibility of the *loop\_chain* interface, and the *S-depth* mechanism made it possible to experiment with a variety of fusion schemes without

1:20 F. Luporini et al.

changes to the source code. Five fusion schemes were devised, based on the following criteria: (i) amount of data reuse, (ii) amount of redundant computation over the boundary region, (iii) memory footprint (the larger, the smaller the tile size to fit in cache). The fusion schemes are summarized in Table 4. The full specification, along with the seed tile size for each sub loop chain, is available at [46].

The experimentation was conducted on two platforms, whose specification is reported in Table 3. The two platforms, Erebus (the "development machine") and Helen (a Broadwell-based architecture in the Helen cluster [33]) were idle and exclusive access had been obtained when the runs were performed. Support for shared-memory parallelism is discontinued in Firedrake, so only distributed-memory parallelism with 1 MPI process per physical core was tested. The MPI processes were pinned to cores. The hyperthreading technology was tried, but found to be generally non-profitable. The code used for running the experiments was archived with the Zenodo data repository service: Firedrake [42], PETSc [43], PETSc4py [44], FIAT [41], UFL [49], TSFC [48], PyOP2 [45], COFFEE [40], SLOPE [47], and Seigen [46].

| System |                 | Erebus                           | Helen                                      |  |  |

|--------|-----------------|----------------------------------|--------------------------------------------|--|--|

|        | Node            | 1x4-core<br>Intel I7-2600 3.4GHz | 2x14-core<br>Intel Xeon E5-2680 v4 2.40GHz |  |  |

|        | DRAM            | 16 GB                            | 128 GB (node)                              |  |  |

|        | Cache hierarchy | L1=32KB, L2=256KB, L3=8MB        | L1=32KB, L2=256KB,<br>L3/socket=35MB       |  |  |

|        | Compilers       | Intel icc 16.0.2                 | Intel icc 16.0.3                           |  |  |

|        | Compiler flags  | -03 -xHost -ip                   | -03 -xHost -ip                             |  |  |

|        | MPI version     | Open MPI 1.6.5                   | SGI MPT 2.14                               |  |  |

| Fusion<br>scheme | Number of loop chains | Criterion                             | S-depth |

|------------------|-----------------------|---------------------------------------|---------|

| fs1              | 3                     | Fuse costly cells<br>and facets loops | 2       |

| fs2              | 8                     | More aggressive<br>than fs1           | 2       |

| fs3              | 6                     | fs2, include all<br>solver loops      | 2       |

| fs4              | 3                     | More aggressive<br>than fs3           | 3       |

| fs5              | 2                     | velocity, stress                      | 4       |

Table 4. Fusion schemes summary.

In the following, for each experiment, we collect three measurements.

**Overall completion time – OT** Used to compute the maximum application speed-up when sparse tiling is applied.

Average compute time – ACT Sparse tiling impacts the kernel execution time by increasing data locality. Communication is also influenced, especially in aggressive fusion schemes: the rounds of communication decrease, while the data volume exchanged may increase. ACT isolates the gain due to increased data locality from (i) the communication cost and (ii) any other action performed in Firedrake (executing Python code) between the invocation of kernels. This value is averaged across the processes.

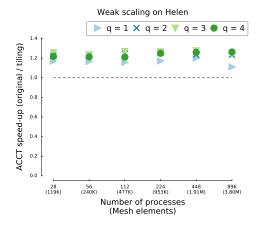

**Average compute and communication time – ACCT** As opposed to ACT, the communication cost is also included in ACCT. By comparing ACCT and ACT, the communication overhead can be derived.

As we shall see, all of these metrics will be essential for a complete understanding of the sparse tiling performance.

To collect OT, ACT and ACCT, the following configuration was adopted. All experiments were executed with "warm cache"; that is, with all kernels retrieved directly from the Firedrake's software cache of compiled kernels, so code generation and compilation times are not counted. All of the non-tiled explosive\_source tests were repeated three times. The minimum times are reported (negligible variance). The cost of global matrix assembly – an operation that takes place before entering the time loop – *is not* included in OT. Firedrake needs to be extended to assemble block-diagonal matrices directly into vectors (an entry in the vector would represent a matrix block). Currently, this is instead obtained in two steps: first, by assembling into a CSR matrix; then, by

| h   | q | OT original (s) | OT tiled (s) | $\Omega^{OT}$ | $\Omega^{ACT}$ | $\Omega^{ACCT}$ |

|-----|---|-----------------|--------------|---------------|----------------|-----------------|

| 1.0 | 1 | 687             | 596          | 1.15          | 1.17           | 1.16            |

|     | 2 | 1453            | 1200         | 1.21          | 1.25           | 1.25            |

|     | 3 | 3570            | 2847         | 1.25          | 1.28           | 1.27            |

|     | 4 | 7057            | 5827         | 1.21          | 1.22           | 1.22            |

| 1.2 | 1 | 419             | 365          | 1.15          | 1.17           | 1.16            |

|     | 2 | 870             | 715          | 1.22          | 1.26           | 1.26            |

|     | 3 | 1937            | 1549         | 1.25          | 1.28           | 1.27            |

|     | 4 | 4110            | 3390         | 1.21          | 1.23           | 1.22            |

Table 5. OT, ACT and ACCT on Erebus, with 1 MPI process per core.

explicitly copying the diagonal into a vector (a Python operation). The assembly per se never takes more than 3 seconds, so it was reasonable to exclude this temporary overhead from our timing. The inspection cost due to sparse tiling is included in OT, and its overhead will be discussed appropriately in a later section. Extra costs were minimized: no check-pointing, only two I/O sessions (at the beginning and at the end of the computation), and minimal logging. The time loop has a fixed duration, while the time step depends on the mesh spacing h to satisfy the Courant-Friedrichs-Lewy necessary condition (i.e., CFL limit) for the numerical convergence. In essence, finer meshes require proportionately smaller time steps to ensure convergence.

We now proceed with discussing the achieved results. Below, a generic instance of explosive\_source optimized with sparse tiling will be referred to as a "tiled version", otherwise the term "original version" will be used.

# 7.5 Single-node Experimentation

Hundreds of single-node experiments were executed on Erebus, which was easily accessible in exclusive mode and much quicker to use for VTune profiling. The rationale of these experiments was to assess how sparse tiling impacts the application performance by improving data locality.

We only show parallel runs at maximum capacity (1 MPI process per physical core); the benefits of sparse tiling in sequential runs tend to be negligible (if any), because (i) the memory access latency is only marginally affected when a large proportion of bandwidth is available to a single process, (ii) hardware prefetching is impaired by the small iteration space of tiles, (iii) translation lookaside buffer (TLB) misses are more frequent due to tile expansion. Points (ii) and (iii) will be elaborated upon.

Table 5 reports execution times and speed-ups, indicated with the symbol  $\Omega$ , of the tiled version over the original version for the three metrics OT, ACT and ACCT. We report the best speed-up obtained after varying a number of parameters (tile size, fusion scheme and other optimizations discussed below).

The parameters that we empirically varied to obtain these results were: (i) the fusion scheme, fsX,  $X \in \{1, 2, 3, 4, 5\}$ , see Table 4; (ii) the seed tile size – for each fs and q, up to four different values chosen to maximize the likelihood of fitting in L2 or L3 cache, were tried<sup>3</sup>.

Further, a smaller experimentation varying (i) type of indirection maps (local or global, see Section 5) and (ii) tile shape (through different mesh partitioning algorithms), as well as introducing (iii) software prefetching and (iv) extended boundary region (to minimize redundant computation) led to the conclusion that these optimizations may either improve or worsen the execution time, in ways that are too difficult to predict beforehand. We therefore decided to exclude these parameters from the full search space. This simplifies the analysis that will follow and also allowed the

<sup>&</sup>lt;sup>3</sup>A less extensive experimentation with "more adverse" tile sizes showed that: (i) a very small value causes dramatic slow-downs (up to 8× slower than the original versions); (ii) larger values cause proportionately greater performance drops.

1:22 F. Luporini et al.

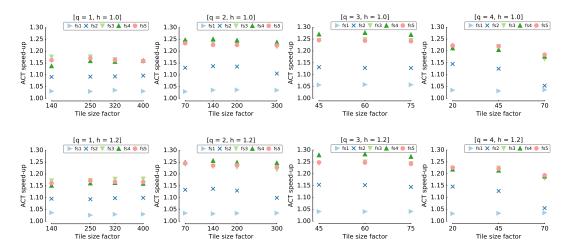

Fig. 12. Search space exploration on Erebus, with  $h \in \{1.0, 1.2\}$  and  $q \in \{1, 2, 3, 4\}$ . Each plot shows the average compute time (ACT) speed-up achieved by multiple tiled versions over the original (non-tiled) version. The seed tile size of a loop chain in an fs, in terms of seed loop iterations, is the product of the "tile size factor" (x-axis) and a pre-established multiplier (an integer in the range [1, 4]; full list available at [46]).

execution of the whole test suite in less than five days. The interested reader is invited to refer to the Supplementary Materials attached to this article for more information.

In Figure 12, we summarize the results of the search space exploration. A plot shows the ACT speed-ups achieved by multiple tiled versions over the non-tiled version for given q and h. In these single-node experiments, the ACCT trend was basically identical (as one can infer from Table 5), with variations in speed-up smaller than 1%.

PyOP2 was enhanced with a *loop chain analyzer* (LCA) capable of estimating the best- and worst-case tile memory footprint, as well as the percentage of data reuse ideally achievable<sup>4</sup>. We use this tool, as well as Intel VTune, to explain the results shown in Figure 12. We make the following observations.

- fs, unsurprisingly, is the parameter having largest impact on the ACT. By influencing the fraction of data reuse convertible into data locality, the amount of redundant computation and the data volume exchanged, fusion schemes play a fundamental role in sparse tiling. This makes automation much more than a desired feature: without any changes to the source code, multiple sparse tiling strategies could be studied and tuned. Automation is one of our major contributions, and this performance exploration justifies the implementation effort.