On the Ferroelectric Polarization Switching of Hafnium

Zirconium Oxide in Ferroelectric/Dielectric Stack

Mengwei Si, Xiao Lyu, and Peide D. Ye

School of Electrical and Computer Engineering and Birck Nanotechnology Center, Purdue

University, West Lafayette, Indiana 47907, United States

\* Address correspondence to: yep@purdue.edu (P.D.Y.)

**ABSTRACT**

The ferroelectric polarization switching in ferroelectric hafnium zirconium oxide

(Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>, HZO) in the HZO/Al<sub>2</sub>O<sub>3</sub> ferroelectric/dielectric stack is investigated systematically

by capacitance-voltage and polarization-voltage measurements. The thickness of dielectric layer

is found to have surprisingly unexpected but significant impact on the ferroelectric polarization

switching of ferroelectric HZO. A suppression of ferroelectricity is observed with thick dielectric

layer. The difference between thick and thin dielectric layer is attributed to the leakage-current-

assist switching through the dielectric layer and a theoretical explanation is provided. The

interfacial coupling effect between the ferroelectric layer and dielectric layer is also observed,

showing a capacitance enhancement compared to ferroelectric capacitor and dielectric capacitor

in series. This work unveils some of the critical parts of the long-standing confusions and

debating related to negative capacitance field-effect transistors (NC-FETs) concepts and

experiments. It also addresses an important question that ferroelectric field-effect transistors can

1

offer DC enhancement from the perspective of ferroelectric switching only, suggesting the potential of using ferroelectric-gated field-effect transistors for low-power logic applications.

KEYWORDS: Ferroelectric, HZO, Fe-FET, Negative capacitance, Steep-slope.

## MAIN TEXT

A ferroelectric material has two stable polarization states with different directions, which are switchable by the external electric field, and thus is extensively explored for non-volatile memory applications. Using ferroelectric field-effect transistors (Fe-FETs) as FET-type ferroelectric memory is a promising ferroelectric memory architecture, because of its high density and non-destructive readout.<sup>1-4</sup> Recently, using a ferroelectric-gated transistor as a negative capacitance field-effect transistor (NC-FET) has attracted tremendous attention as a novel steep-slope device.<sup>5–9</sup> In both cases, a ferroelectric (FE) insulator and linear dielectric (DE) insulator bilayer stack is an important structure that is applied in both Fe-FETs and NC-FETs. The necessity of such a linear DE layer is because an interfacial oxide layer between semiconductor channel and FE insulator is required to improve the ferroelectric/semiconductor interface and meanwhile provide sufficient capacitance matching if quasi-static negative capacitance (QSNC) concept is applied for the development of NC-FETs.<sup>5</sup> One important fact, which has been overlooked in the past several years, is that the FE/DE stack capacitor is fundamentally different from a FE capacitor and DE capacitor in series. 10,11 Therefore, the complete understanding of the impact of DE layer on the ferroelectric properties of a FE/DE stack is crucial to understand the ferroelectric switching mechanism in Fe-FETs and NC-FETs.

Ferroelectric hafnium oxide, such as hafnium zirconium oxide (Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>, HZO), has been recently discovered as an ultrathin CMOS compatible high performance ferroelectric

insulator.<sup>12,13</sup> Therefore, HZO is chosen as the FE insulator for this study and Al<sub>2</sub>O<sub>3</sub> is chosen as the linear DE insulator to study the ferroelectric polarization switching in the FE/DE stack. As is well-known that ferroelectric HZO has a thickness-dependent remnant polarization ( $P_r$ ) at about 10-30  $\mu$ C/cm<sup>2</sup>.<sup>14,15</sup> However, a conventional dielectric insulator cannot support such a large charge density. For example, Al<sub>2</sub>O<sub>3</sub> has a typical dielectric constant (k) of 8 and a breakdown electric field less than 1 V/nm.<sup>16</sup> The calculated charge density at breakdown electric field is about 7  $\mu$ C/cm<sup>2</sup>, which is the maximum charge density ( $Q_{max}$ ) for ideal Al<sub>2</sub>O<sub>3</sub> to be able to support without breakdown. Note that in reality, this value for  $Q_{max}$  is much smaller. As can be see that, even in ideal case, there is a big gap between the remnant polarization in HZO and the maximum charge density in Al<sub>2</sub>O<sub>3</sub>. This fact can also be generally applied to other FE/DE stack systems. Thus, this puzzle and confusion in the field, which has not been clarified, is that how can ferroelectric polarization switching happen in a FE/DE stack without sufficient charge balance? And can the ferroelectric polarization switching in FE insulator eventually break down the DE insulator due to the high charge density?

Here, to address this puzzle, the ferroelectric polarization switching of HZO in the HZO/Al<sub>2</sub>O<sub>3</sub> FE/DE stack is investigated systematically by capacitance-voltage (C-V) and polarization-voltage (P-V) measurements. The thickness of dielectric layer is found to have unexpected but significant impact on the ferroelectric polarization switching of ferroelectric HZO. The suppression of ferroelectricity is observed with thick dielectric layer. The difference between thick and thin dielectric layer is attributed to the leakage-current-assist switching through the linear dielectric layer and a theoretical explanation is provided. It is confirmed that the charge needed for ferroelectric polarization switching comes from the leakage current

through the thin dielectric layer. Without such leakage current, the FE HZO cannot be fully polarized.

The capacitances of DE layer, FE layer and FE/DE stack are studied and compared. The interfacial coupling effect between the ferroelectric layer and dielectric layer is also observed for the first time in HZO system, showing a capacitance enhancement compared to ferroelectric capacitor and dielectric capacitor in series. A QCNC enhancement in HZO/Al<sub>2</sub>O<sub>3</sub> stack is not observed with the same conclusion as the measurement of DE capacitor and FE capacitor externally connected. This experimental result is only suitable in multi-domain ferroelectric insulator such as HZO system, being different from other materials systems.<sup>17</sup> It is still unclear whether in single domain case OCNC enhancement exists or not.<sup>11,18-20</sup>

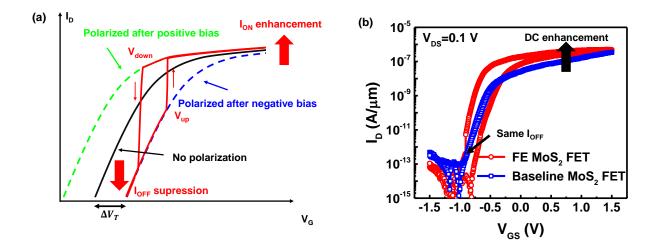

It is clear that ferroelectric polarization switching can lead to the sub-60 mV/dec subthreshold slope (SS) in ferroelectric-gated transistors. But hysteresis in transfer characteristics is unavoidable, if not considering charge trapping process. <sup>21,22</sup> Note that the concept of transient NC effect in Fe-FETs<sup>21,22</sup> is fundamentally different from the concept of QSNC effect in NC-FETs. But it is unclear whether performance benefit is achievable or not with a hysteretic and sub-60 mV/dec device. Here, the authors want to emphasize that ferroelectric polarization switching and polarization charge in Fe-FETs can offer DC enhancement (I<sub>OFF</sub> reduction and I<sub>ON</sub> enhancement simultaneously), with the existence of hysteresis and without incorporating QSNC explanation. All transient effects of ferroelectric dynamic polarization switching<sup>23–26</sup> are negligible in DC condition discussed in this work. Meanwhile, the hysteresis might not have serious impact in logic circuits if it is matched in between zero voltage and supply voltage (V<sub>DD</sub>).

offer DC enhancement from the perspective of ferroelectric polarization switching only, suggesting the potential of using ferroelectric-gated transistor for low-power logic applications.

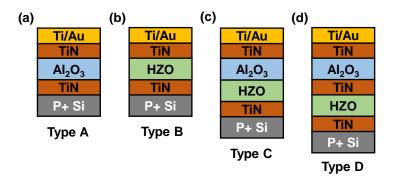

Fig. 1 shows the experimental device structures. Four types of capacitor structures are used in this work: (a) TiN/Al<sub>2</sub>O<sub>3</sub>/TiN (type A), (b) TiN/HZO/TiN (type B), (c) TiN/Al<sub>2</sub>O<sub>3</sub>/HZO/TiN (type C), and (d) TiN/Al<sub>2</sub>O<sub>3</sub>/TiN/HZO/TiN (type D). The device fabrication process started with the standard solvent cleaning of heavily p-doped Si substrates (resistivity  $< 0.005 \ \Omega \cdot cm$ ). TiN was deposited by atomic layer deposition (ALD) at 250 °C, using [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Ti (TDMAT, heated up to 60 °C) and NH<sub>3</sub> as the Ti and N precursors, respectively. All TiN layers are metallic and 30 nm thick. Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> film was deposited by ALD at 200 °C, using [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Hf (TDMAHf, heated up to 60 °C), [(CH<sub>3</sub>)<sub>2</sub>N]<sub>4</sub>Zr (TDMAZr, heated up to 75 °C), and H<sub>2</sub>O as the Hf, Zr, and O precursors, respectively. The Hf<sub>1-x</sub>Zr<sub>x</sub>O<sub>2</sub> film with x = 0.5was achieved by controlling HfO<sub>2</sub>:ZrO<sub>2</sub> cycle ratio of 1:1. The ALD deposition of TiN and HZO were in two separated ALD chambers to avoid cross-contamination. The two ALD chambers are connected externally by Ar environment in a glove box to avoid the environmental contamination. After the deposition of type A-D structures, the samples were annealed at 500 °C in N<sub>2</sub> environment for 1 min by rapid thermal annealing. Then, Ti/Au top electrodes were deposited by e-beam evaporation. CF<sub>4</sub>/Ar dry etching was done to remove top TiN layer for device isolation for type A-C capacitors. For type D capacitors, BCl<sub>3</sub>/Ar dry etching was used to remove the top Al<sub>2</sub>O<sub>3</sub> layer and CF<sub>4</sub>/Ar dry etching was used to remove the top and middle TiN layers. All electrical measurements were done at room temperature in a cascade summit probe station. C-V measurement was performed using an Agilent E4980A LCR meter and P-V measurement was carried out using a Radiant RT66C ferroelectric tester.

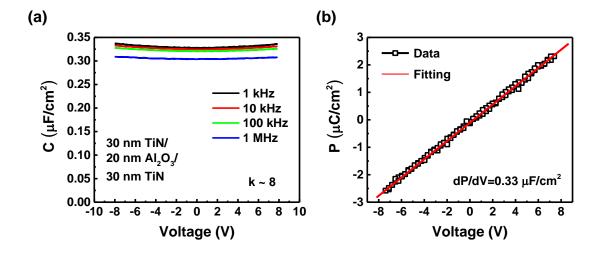

Fig. 2(a) shows the C-V measurement of type A capacitor with 20 nm Al<sub>2</sub>O<sub>3</sub>, from 1 kHz to 1 MHz. Fig. 2(b) shows the P-V measurement of the same type A capacitor, showing a linear dielectric hysteresis loop. Both measurements (small signal C-V, dP/dV in P-V) give consistent capacitance values for the type A dielectric capacitor with a capacitance of ~0.33 μF/cm<sup>2</sup> and a corresponding dielectric constant of ~8. Fig. 3(a) shows the C-V measurement of type B capacitor with 20 nm HZO, from 1 kHz to 1 MHz. The C-V measurement of a type B capacitor shows signature two peaks in the C-V hysteresis loop, which is also ferroelectric characteristics. The different capacitances at different voltages in C-V are attributed to the different dielectric constant due to the difference in atomic structures during the ferroelectric structural phase transition. The corresponding dielectric constants are calculated, as also shown in the right axis. Fig. 3(b) shows the P-V measurement of the same type B capacitor, showing a ferroelectric hysteresis loop. Fig. 3(c) shows the dP/dV versus applied voltage of the P-V loop in Fig. 3(b). The dP/dV values (up to  $\sim 15 \mu F/cm^2$ ) are significantly larger than the capacitance in C-V measurement (less than 1  $\mu$ F/cm<sup>2</sup>), suggesting two ferroelectric switching events in the hysteresis loop.

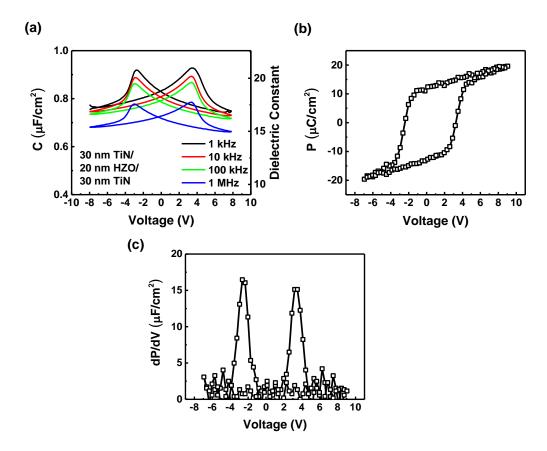

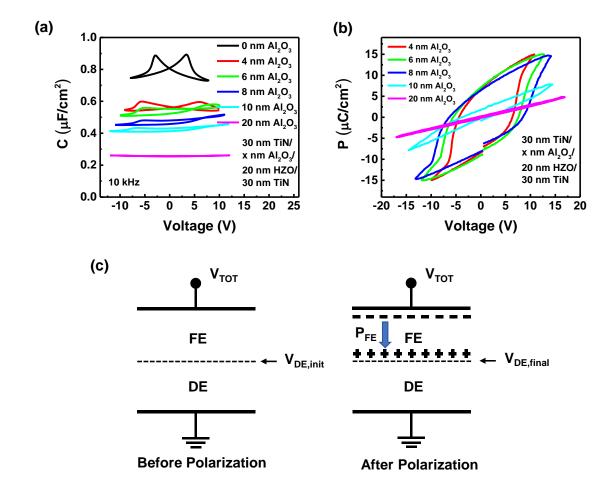

Fig. 4(a) shows the C-V measurements of type C capacitors with 20 nm HZO and Al<sub>2</sub>O<sub>3</sub> from 0 nm to 20 nm, measured at 10 kHz. The capacitances of type C capacitors decrease with thicker Al<sub>2</sub>O<sub>3</sub> as expected. The signature two capacitance peaks due to ferroelectricity in the C-V hysteresis loop decrease and eventually disappear in 20 nm HZO/20 nm Al<sub>2</sub>O<sub>3</sub> stack, suggesting the reduction of ferroelectricity in thick DE layer and FE layer stack. This feature is even clearly presented in Fig. 4(b) which shows the P-V measurements of type C capacitors with 20 nm HZO and Al<sub>2</sub>O<sub>3</sub> from 4 nm to 20 nm. The applied voltage ranges are maximized in P-V measurement before the leakage current has essential impact. The significant decrease of remnant polarization

in P-V hysteresis loops is observed with thicker DE layer. The C-V measurements and P-V measurements consistently confirm that thick DE layer can suppress the ferroelectricity in FE/DE stack. This is the surprising and central observation of this work.

To further understand the physics behind the DE layer thickness dependence in the ferroelectricity of FE/DE stack, a theoretical analysis is provided, as shown in Fig. 4(c). To understand the dynamic process of ferroelectric switching, this process is plotted by a two-step process: before ferroelectric polarization switching and after ferroelectric polarization switching. As is well-known, the ferroelectric polarization switching is a structural phase transition, so it is always slower than the electron re-distribution. Thus, the two-step assumption is valid. For simplicity, it is assumed the FE layer has a dielectric constant of  $\epsilon_{FE}$  (without considering ferroelectric polarization) and a thickness of  $t_{FE}$ ; the DE layer has a dielectric constant of  $\epsilon_{DE}$  and a thickness of  $t_{DE}$ . This situation is similar to two high-k dielectric stack. We define  $V_{TOT}$  to be the voltage applied to the FE/DE stack,  $V_{DE}$  to be the voltage across the DE layer and  $V_{FE}$  to be the voltage across the FE layer. Therefore, before the ferroelectric polarization switching, the voltage across the DE layer is

$$V_{DE,init} = \frac{V_{TOT}\epsilon_{FE}t_{DE}}{\epsilon_{DE}t_{FE}+\epsilon_{FE}t_{DE}} \tag{1}$$

$$V_{FE,init} = \frac{V_{TOT} \epsilon_{DE} t_{FE}}{\epsilon_{DE} t_{FE} + \epsilon_{FE} t_{DE}}$$

(2)

There are totally three different cases according to the different DE thickness. Here, we first assume the leakage current is zero and then discuss the impact of leakage current. Firstly, if  $t_{DE}$  is very thick, then  $V_{FE,init}$  can be sufficiently small so that it is smaller than the coercive voltage ( $V_c$ ) of the FE layer, according to eqn. (2). Thus, no polarization switching can happen. So, the C-V and P-E characteristics behave like a linear dielectric insulator. Secondly, if  $V_{FE,init}$  >  $V_c$  but  $t_{DE}$  is sufficiently thick, the FE layer cannot be fully polarized. As the polarization

switching happens,  $V_{DE}$  increases until  $V_{FE}$  reaches  $V_c$  and the polarization process cannot continue. In this case, the total polarization charge in FE layer ( $P_{FE}$ ) can be approximated as  $\epsilon_{DE}(V_{TOT}-V_c)/t_{DE}$ , where we have  $P_{FE} < P_r$  and  $V_{DE,final}=P_{FE}/(\epsilon_{DE}/t_{DE})$ . Thirdly, if the DE layer is thin enough, so that the second criterial does not meet anymore, we can have the FE layer fully polarized. So that  $V_{DE}$  can be calculated as  $P_{FE}=P_r$  and  $V_{DE,final}=P_r/(\epsilon_{DE}/t_{DE})$ . It is clear that if  $P_{FE}$  is larger than the maximum charge density in DE layer,  $V_{DE,final}$  will be larger than the breakdown voltage ( $V_{BD}$ ) of the DE layer, which of course cannot happen. What is really happening in this process (if  $V_{DE,final} > V_{BD}$ ) is when  $V_{DE}$  rises from  $V_{DE,final}$  to  $V_{DE,final}$ , the DE layer first becomes leaky and these leakage charge will become the ferroelectric polarization charge so that  $V_{DE}$  cannot reach  $V_{BD}$ . All the ferroelectric polarization charges are balanced by the charge from leakage current instead of the charge in DE layer. Therefore, in thin DE limit, the ferroelectric polarization switching process is a leakage-current-assist process. At the extremely leaky limit, it becomes almost as metal-FE-metal structure. Here's a summary of all three cases,

Case 1: thick DE limit, no polarization switching

$$V_{FE.init} < V_c \tag{3}$$

Case 2: moderate DE thickness, partial switching (by dielectric charge or leakage)

$$V_{FE.init} > V_c \text{ and } P_r > \epsilon_{DE} (V_{TOT} - V_c) / t_{DE}$$

(4)

$$P_{FE} = \epsilon_{DE} (V_{TOT} - V_c) / t_{DE} \tag{5}$$

$$V_{DE,final} = P_{FE} / \frac{\epsilon_{DE}}{t_{DE}} \tag{6}$$

Case 3: ultra-thin DE limit, leakage-current-assist switching

$$P_r < \epsilon_{DE} (V_{TOT} - V_c) / t_{DE} \tag{7}$$

$$P_{FE} = P_r \tag{8}$$

$$V_{DE,final} = P_r / \frac{\epsilon_{DE}}{t_{DE}} \tag{9}$$

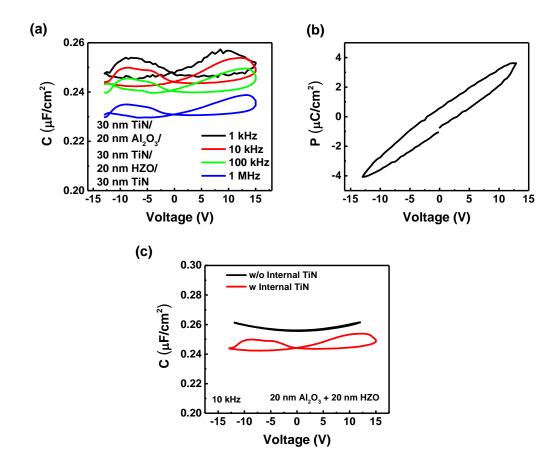

Fig. 5(a) shows the C-V measurement of a type D capacitor with 20 nm HZO and 20 nm Al<sub>2</sub>O<sub>3</sub>, measured from 1 kHz to 1 MHz. The signature two capacitance peaks in the C-V hysteresis loop are observed. Fig. 5(b) shows the P-V measurement of a type D capacitor with 20 nm HZO and 20 nm Al<sub>2</sub>O<sub>3</sub>, where a weak ferroelectric hysteresis loop is achieved. Fig. 5(c) shows the comparison of C-V measurements of type C and type D capacitors with 20 nm HZO and 20 nm Al<sub>2</sub>O<sub>3</sub>. Although same thicknesses of HZO and Al<sub>2</sub>O<sub>3</sub> are used, a type D capacitor still exhibits weak ferroelectricity in C-V and P-V characteristics, suggesting that the charge in the internal metal can assist the ferroelectric switching process, in great contrast to the result from a type C capacitor. Fig. 5(c) concludes the FE/DE stack with internal metal and without internal metal are physically very different.

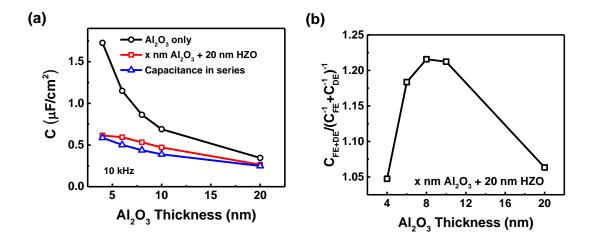

Fig. 6(a) shows the capacitance versus Al<sub>2</sub>O<sub>3</sub> thickness characteristics of three types of capacitors, Al<sub>2</sub>O<sub>3</sub> only (type A), Al<sub>2</sub>O<sub>3</sub>/20 nm HZO stack (type C) and the capacitance value of measured Al<sub>2</sub>O<sub>3</sub> (type A) and HZO (type B) capacitors in series. Experimentally, capacitance of type C capacitor is lower than type A capacitor with same Al<sub>2</sub>O<sub>3</sub> thickness. But a capacitance enhancement of type C capacitor is observed to be larger than the capacitance value in series, as shown in Fig. 6(b). Over 20% capacitance enhancement is observed with 8 and 10 nm Al<sub>2</sub>O<sub>3</sub>/20 nm HZO stack. This also suggests the FE/DE stack with internal metal and without internal metal are physically different from another aspect, indicating the existence of interfacial coupling between the Al<sub>2</sub>O<sub>3</sub> layer and HZO layer. This interface coupling effect or capacitance enhancement were observed in the previous reports <sup>10,27-30</sup> and is fundamentally different from the QSNC effect.

The above understanding of ferroelectric switching process helps to address an important question here, that is, can a ferroelectric-gated FET offer DC enhancement using the FE/DE stack from the perspective of ferroelectric polarization switching? The answer is yes. The Fe-FET can provide effective DC enhancement for the future low-power CMOS logic applications if the switch speed is not the final limitation. In a CMOS logic circuit, a lower off-state current (I<sub>OFF</sub>) and higher on-state current (I<sub>ON</sub>) is preferred. The DC enhancement here is defined as at the same I<sub>OFF</sub> and a given supply voltage (V<sub>DD</sub>), the transistor can have higher I<sub>ON</sub>. Whether hysteresis exists or not between zero voltage and V<sub>DD</sub> is not important if lower I<sub>OFF</sub> and higher  $I_{ON}$  can be achieved simultaneously and hysteresis occurs lower than half of the  $V_{DD}$ . As shown in Fig. 7(a), the black line is the transfer characteristics of the baseline FET without ferroelectric polarization. If a high gate voltage is applied, the transfer curve shift to the left as the green curve. If a low gate voltage is applied, the transfer curve shift to the right as the blue curve. The amount of threshold voltage shift ( $\Delta V_T$ ) is determined by the remnant polarization, the capacitance of dielectric layer (C<sub>DE</sub>) and the ratio of ferroelectric capacitor area (A<sub>FE</sub>) and the dielectric capacitor area (A<sub>DE</sub>) (assuming the existence of an internal metal layer). Note that the conclusion is still valid in FE/DE stack without internal metal, but the area ratio of AFE and ADE becomes one. The threshold voltage shift becomes

$$\Delta V_T \sim \frac{P_{FE} A_{DE}}{C_{DE} A_{FE}} \tag{10}$$

The transfer characteristics of the Fe-FET switches between the polarization up and polarization down transfer curves and the switching voltages ( $V_{up}$ ,  $V_{down}$ ) are determined by the coercive voltages. The coercive voltages can be tuned by the thickness of the FE layer, so  $V_{up}$  and  $V_{down}$  can be tuned accordingly. Therefore, if we plot the full bi-directional transfer characteristics, as the red line in Fig. 7(a), a reduction in  $I_{OFF}$  and an enhancement in  $I_{ON}$  are achieved

simultaneously. This exactly shows the DC enhancement can be achieved using a Fe-FET structure. The difficulty in realization of such performance is that the  $P_r$  in conventional ferroelectric insulator material is so high that the hysteresis window become too large for logic applications. However, by using a DE layer for capacitance matching and using an internal metal gate to modulate the area ratio of  $A_{FE}$  and  $A_{DE}$  if it is needed, we can effectively reduce the hysteresis window, achieve DC enhancement in Fe-FET, design hysteresis occurring lower than half of  $V_{DD}$  for logic switches.

Such experimental structure and experimental results were already reported in our previous publication with  $A_{FE}/A_{DE} \sim 100$ , as shown in Fig. 7(b). It is a MoS<sub>2</sub> ferroelectric-gate FET with internal metal gate structure. Subthreshold slope (SS) of 37.6 mV/dec in forward sweep and SS of 42.2 mV/dec in reverse sweep are achieved. More importantly, a clear  $I_{ON}$  enhancement is achieved with same  $I_{OFF}$  so that this is an obvious DC enhancement. From the perspective of ferroelectric polarization switching, such DC enhancement can be explained without invoking QSNC concept. Therefore, the application of ferroelectric-gated FETs with small hysteresis and enhanced DC performance could have the potential for future low-power device applications. The operation speed of such transistors could be eventually limited by the ferroelectric switching speed  $^{31}$ , which needs to be thoroughly investigated also.

In conclusion, the ferroelectric polarization switching in FE HZO in the HZO/Al<sub>2</sub>O<sub>3</sub> FE/DE stack is investigated systematically by C-V and P-V measurements. The thickness of dielectric layer is found to have significant impact on the ferroelectric polarization switching of HZO. The suppression of ferroelectricity is observed with a thick linear dielectric layer. The difference between thick and thin dielectric layer is attributed to the leakage-current-assist switching through the dielectric layer and a theoretical explanation is provided. The interfacial

coupling effect between the ferroelectric HZO layer and the linear dielectric layer is observed for the first time, showing a capacitance enhancement compared to ferroelectric capacitor and dielectric capacitor in series. This work also addresses that ferroelectric field-effect transistors can offer DC enhancement from the perspective of ferroelectric switching only, suggesting the potential of using ferroelectric-gated transistor for low-power logic device applications.

**AUTHOR INFORMATION**

**Corresponding Author**

\*E-mail: yep@purdue.edu

**Author Contributions**

P.D.Y. conceived the idea of FE/DE stack and supervised the experiments. M.S. and X.L. did the

ALD deposition and device fabrication. M.S. and X.L. performed DC electrical measurements

and analysis. P.D.Y. and M.S. proposed the idea of DC enhancement on Fe-FETs. M.S. and

P.D.Y. co-wrote the manuscript and all authors commented on it.

**Notes**

The authors declare no competing financial interest.

**ACKNOWLEDGEMENTS**

The authors would like to thank Muhammad Ashraful Alam and Suman Datta for valuable

discussions. The work was supported in part by the Semiconductor Research Corporation (SRC)

and DARPA.

REFERENCES

(1) Ishiwara, H. Ferroelectric Random Access Memories. J. Nanosci. Nanotechnol. 2012, 12,

7619–7627.

Müller, J.; Böscke, T. S.; Schröder, U.; Hoffmann, R.; Mikolajick, T.; Frey, L. (2)

Nanosecond Polarization Switching and Long Retention in a Novel MFIS-FET Based on

Ferroelectric HfO<sub>2</sub>. *IEEE Electron Device Lett.* **2012**, *33*, 185–187.

13

- (3) Yoo, H. K.; Kim, J. S.; Zhu, Z.; Choi, Y. S.; Yoon, A.; MacDonald, M. R.; Lei, X.; Lee, T. Y.; Lee, D.; Chae, S. C.; et al. Engineering of Ferroelectric Switching Speed in Si Doped HfO<sub>2</sub> for High-Speed 1T-FERAM Application. In *IEEE Intl. Electron Devices Meet.*; 2017; pp 481–484.

- (4) Dünkel, S.; Trentzsch, M.; Richter, R.; Moll, P.; Fuchs, C.; Gehring, O.; Majer, M.; Wittek, S.; Müller, B.; Melde, T.; et al. A FeFET Based Super-Low-Power Ultra-Fast Embedded NVM Technology for 22nm FDSOI and Beyond. In *IEEE Intl. Electron Devices Meet.*; 2017; pp 485–488.

- (5) Salahuddin, S.; Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. *Nano Lett.* **2008**, *8*, 405–410.

- (6) Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H.; et al. Sub-60mV-Swing Negative-Capacitance FinFET without Hysteresis. In *IEEE Intl. Electron Devices Meet.*; 2015; pp 620–623.

- (7) Lee, M. H.; Fan, S.-T.; Tang, C.-H.; Chen, P.-G.; Chou, Y.-C.; Chen, H.-H.; Kuo, J.-Y.; Xie, M.-J.; Liu, S.-N.; Liao, M.-H.; et al. Physical Thickness 1.x Nm Ferroelectric HfZrOx Negative Capacitance FETs. In *IEEE Intl. Electron Devices Meet.*; 2016; pp 306–309.

- (8) Si, M.; Su, C.-J.; Jiang, C.; Conrad, N. J.; Zhou, H.; Maize, K. D.; Qiu, G.; Wu, C.-T.; Shakouri, A.; Alam, M. A.; et al. Steep-Slope Hysteresis-Free Negative Capacitance MoS<sub>2</sub> Transistors. *Nat. Nanotechnol.* **2018**, *13*, 24–29.

- (9) Si, M.; Jiang, C.; Su, C.; Tang, Y.; Yang, L.; Chung, W.; Alam, M. A.; Ye, P. D. Sub-60 mV/Dec Ferroelectric HZO MoS<sub>2</sub> Negative Capacitance Field-Effect Transistor with Internal Metal Gate: The Role of Parasitic Capacitance. In *IEEE Intl. Electron Devices*

- Meet.; 2017; pp 573–576.

- (10) Sun, F. C.; Kesim, M. T.; Espinal, Y.; Alpay, S. P. Are Ferroelectric Multilayers Capacitors in Series? *J. Mater. Sci.* **2016**, *51*, 499–505.

- (11) Liu, Z.; Bhuiyan, M. A.; Ma, T. P. A Critical Examination of 'Quasi-Static Negative Capacitance' (QSNC) Theory. In IEEE Intl. Electron Devices Meet.; 2018; pp 711–714.

- (12) Böescke, T. S.; Müller, J.; Bräuhaus, D.; Schröder, U.; Böttger, U. Ferroelectricity in Hafnium Oxide: CMOS Compatible Ferroelectric Field Effect Transistors. In *IEEE Intl. Electron Devices Meet.*; 2011; pp 547–550.

- (13) Muller, J.; Boscke, T. S.; Schroder, U.; Mueller, S.; Brauhaus, D.; Bottger, U.; Frey, L.; Mikolajick, T. Ferroelectricity in Simple Binary ZrO<sub>2</sub> and HfO<sub>2</sub>. Nano Lett. 2012, 12, 4318–4323.

- (14) Park, M. H.; Kim, H. J.; Kim, Y. J.; Lee, W.; Moon, T.; Hwang, C. S. Evolution of Phases and Ferroelectric Properties of Thin Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> films According to the Thickness and Annealing Temperature. *Appl. Phys. Lett.* **2013**, *102*, 242905.

- (15) Tian, X.; Shibayama, S.; Nishimura, T.; Yajima, T.; Migita, S.; Toriumi, A. Evolution of Ferroelectric HfO<sub>2</sub> in Ultrathin Region down to 3 nm. *Appl. Phys. Lett.* **2018**, *112*, 102902.

- (16) Lin, H. C.; Ye, P. D.; Wilk, G. D. Leakage Current and Breakdown Electric-Field Studies on Ultrathin Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub> on GaAs. *Appl. Phys. Lett.* **2005**, *87*, 182904.

- (17) Khan, A. I.; Bhowmik, D.; Yu, P.; Kim, S. J.; Pan, X.; Ramesh, R.; Salahuddin, S. Experimental Evidence of Ferroelectric Negative Capacitance in Nanoscale Heterostructures. Appl. Phys. Lett. 2011, 99, 113501.

- (18) Appleby, D. J. R.; Ponon, N. K.; Kwa, K. S. K.; Zou, B.; Petrov, P. K.; Wang, T.; Alford,N. M.; O'Neill, A. Experimental Observation of Negative Capacitance in Ferroelectrics at

- Room Temperature. *Nano Lett.* **2014**, *14*, 3864–3868.

- (19) Gao, W.; Khan, A.; Marti, X.; Nelson, C.; Serrao, C.; Ravichandran, J.; Ramesh, R.; Salahuddin, S. Room-Temperature Negative Capacitance in a Ferroelectric-Dielectric Superlattice Heterostructure. *Nano Lett.* 2014, 14, 5814–5819.

- (20) Hoffmann, M.; Max, B.; Mittmann, T.; Schroeder, U.; Slesazeck, S.; Mikolajick, T. Demonstration of High-speed Hysteresis-free Negative Capacitance in Ferroelectric Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub>. In *IEEE Intl. Electron Devices Meet.*; 2018; pp 727–730.

- (21) Van Houdt, J.; Roussel, P. Physical Model for the Steep Subthreshold Slope in Ferroelectric FETs. *IEEE Electron Device Lett.* **2018**, *39*, 877–880.

- (22) Kittl, J. A.; Obradovic, B.; Reddy, D.; Rakshit, T.; Hatcher, R. M.; Rodder, M. S. On the Validity and Applicability of Models of Negative Capacitance and Implications for MOS Applications. *Appl. Phys. Lett.* **2018**, *113*, 042904.

- (23) Kim, Y. J.; Park, H. W.; Hyun, S. D.; Kim, H. J.; Kim, K. D.; Lee, Y. H.; Moon, T.; Lee, Y. B.; Park, M. H.; Hwang, C. S. Voltage Drop in a Ferroelectric Single Layer Capacitor by Retarded Domain Nucleation. *Nano Lett.* 2017, 17, 7796–7802.

- (24) Saha, A. K.; Datta, S.; Gupta, S. K. "Negative Capacitance" in Resistor-Ferroelectric and Ferroelectric-Dielectric Networks: Apparent or Intrinsic? *J. Appl. Phys.* **2018**, *123*, 105102.

- Obradovic, B.; Rakshit, T.; Hatcher, R.; Kittl, J. A.; Rodder, M. S. Ferroelectric Switching Delay as Cause of Negative Capacitance and the Implications to NCFETs. In *VLSI Tech*. *Dig.*; 2018; pp 51–52.

- (26) Hoffmann, M.; Khan, A. I.; Serrao, C.; Lu, Z.; Salahuddin, S.; Pešić, M.; Slesazeck, S.; Schroeder, U.; Mikolajick, T. Ferroelectric Negative Capacitance Domain Dynamics. *J.*

- Appl. Phys. 2018, 123, 184101.

- (27) Tsang, C. H.; Chew, K.-H.; Ishibashi, Y.; Shin, F. G. Structure of Interfaces in Layered Ferroelectrics of First and/or Second Order Transition. *J. Phys. Soc. Jpn.* **2004**, *73*, 3158–3165.

- (28) Dawber, M.; Lichtensteiger, C.; Cantoni, M.; Veithen, M.; Ghosez, P.; Johnston, K.; Rabe, K. M.; Triscone, J.-M. Unusual Behavior of the Ferroelectric Polarization in PbTiO<sub>3</sub>/SrTiO<sub>3</sub> Superlattices. *Phys. Rev. Lett.* 2005, 95, 177601.

- (29) Zhou, Y. Enhancement of Dielectric and Ferroelectric Properties in Ferroelectric Superlattices. *Solid State Commun.* **2010**, *150*, 1382–1385.

- (30) Salev, P.; Mahayni, A.; Grigoriev, A. Polarization Coupling Transition in BaTiO<sub>3</sub>/PbZr<sub>0.2</sub>Ti<sub>0.8</sub>O<sub>3</sub> Ferroelectric Bilayers. *Phys. Rev. B* **2016**, *93*, 041423.

- (31) Chung, W.; Si, M.; Shrestha, P. R.; Campbell, J. P.; Cheung, K. P.; Ye, P. D. First Direct Experimental Studies of Hf<sub>0.5</sub>Zr<sub>0.5</sub>O<sub>2</sub> Ferroelectric Polarization Switching Down to 100-picosecond in Sub-60mV/dec Germanium Ferroelectric Nanowire FETs. In *VLSI Tech. Dig.*; 2018; pp 89–90.

## **Figures**

**Figure 1.** Capacitor structures used in this work (a) Al<sub>2</sub>O<sub>3</sub> only (type A), (b) HZO only (type B), (c) Al<sub>2</sub>O<sub>3</sub> and HZO stack without internal metal (type C), and (d) Al<sub>2</sub>O<sub>3</sub> and HZO stack with TiN layer as the internal metal (type D).

**Figure 2.** (a) C-V measurement and (b) P-V measurement on a type A capacitor with 20 nm Al<sub>2</sub>O<sub>3</sub>.

**Figure 3.** (a) C-V measurement, (b) P-V measurement and (c) dP/dV versus voltage characteristics of a type B capacitor with 20 nm HZO.

**Figure 4.** (a) C-V measurements and (b) P-V measurements on type C capacitors with different Al<sub>2</sub>O<sub>3</sub> thickness and 20 nm HZO. (c) Illustration of electrostatics in FE/DE stack capacitor before and after ferroelectric polarization switching.

**Figure 5.** (a) C-V measurement and (b) P-V measurement on a type D capacitor with 20 nm  $Al_2O_3$  and 20 nm HZO. (c) C-V measurements comparison of a type C and a type D capacitor with 20 nm  $Al_2O_3$  and 20 nm HZO.

**Figure 6.** (a) Capacitance of type C capacitor versus Al<sub>2</sub>O<sub>3</sub> thickness, by both experimental measurements (red squares) and calculated total capacitance (blue triangles). The calculated total capacitance in series is based on the experimental measurements of type A and type B capacitors, using the maximum capacitance in the measured C-V curves. The capacitance values of measured type A capacitors with different Al<sub>2</sub>O<sub>3</sub> thicknesses are presented as black circles. (b) The ratio of experimental capacitances of type C capacitor over capacitance in series versus different Al<sub>2</sub>O<sub>3</sub> thickness.

**Figure 7.** (a) Illustration of DC enhancement of a ferroelectric-gated FET. (b) Experimental results of a MoS<sub>2</sub> ferroelectric-gated FET with internal metal gate and the baseline FET measured using internal metal gate on exact same MoS<sub>2</sub> channel. The experimental results confirm that the DC enhancement by a ferroelectric-gated FET is possible. For the real logic applications, the hysteresis and threshold voltage need to be designed and optimized.