# MaD: Mapping and debugging framework for implementing deep neural network onto a neuromorphic chip with crossbar array of synapses

Roshan Gopalakrishnan

Institute for Infocomm Research (I2R)

ASTAR

Singapore

roshan@i2r.a-star.edu.sg

Ashish Jith Sreejith Kumar

School of Electrical and Electronic Engineering

Nanyang Technological University

Singapore

ashishji001@e.ntu.edu.sg

Yansong Chua

Institute for Infocomm Research (I2R)

ASTAR

Singapore

chuays@i2r.a-star.edu.sg

Abstract-Neuromorphic systems or dedicated hardware for neuromorphic computing is getting popular with the advancement in research on different device materials for synapses, especially in crossbar architecture and also algorithms specific or compatible to neuromorphic hardware. Hence, an automated mapping of any deep neural network onto the neuromorphic chip with crossbar array of synapses and an efficient debugging framework is very essential. Here, mapping is defined as the deployment of a section of deep neural network layer onto a neuromorphic core and the generation of connection lists among population of neurons to specify the connectivity between various neuromorphic cores on the neuromorphic chip. Debugging is the verification of computations performed on the neuromorphic chip during inferencing. Together the framework becomes Mapping and Debugging (MaD) framework. MaD framework is quite general in usage as it is a Python wrapper which can be integrated with almost every simulator tools for neuromorphic chips. This paper illustrates the MaD framework in detail, considering some optimizations while mapping onto a single neuromorphic core. A classification task on MNIST and CIFAR-10 datasets are considered for test case implementation of MaD framework.

Index Terms—mapping, debugging, neuromorphic computing, neuromorphic chip, spiking neuron, synapse, crossbar array, deep neural network, MNIST, CIFAR-10

### I. INTRODUCTION

Edge computing is one of the recent developments in the field of artificial intelligence. The amount of data being processed with the ever increasing inter-connectivity of devices and internet of things, ranging from sensors to autonomous vehicles, demand for high real time data processing at the edge. The edge devices are usually selected from neuromorphic chips, embedded devices, FPGA, GPU/CPU etc depending on the application. Among these devices, neuromorphic chip

This research is supported by Programmatic grant no. A1687b0033 from the Singapore governments Research, Innovation and Enterprise 2020 plan (Advanced Manufacturing and Engineering domain). A version of this paper is submitted to IJCNN 2019.

has proven to be the efficient or potential candidate in terms of computational power and latency. Neuromorphic chips are developed in digital [1], analog or mixed signal [2] [3] [4] integrated circuit designs. Usual design trend is that mostly the computation and memory section is done in analog domain whereas, the communication between cores are maintained in digital domain.

The neuromorphic chip discussed in this paper is based on crossbar architecture [5] of non volatile memory synapses. However, one of the main challenges is to efficiently map the neurons on to the neuromorphic chip with hardware constraints such as core size, number of cores and fan-in/fanout [11]. The existing neuromorphic chips have a mapping framework which is more hardware specific. IBM's TrueNorth chip [6] uses corelet language [7] based on MATLAB, a programming language specific to their hardware. Within this MATLAB framework, a mapping technique is integrated as a minimization problem [6]. SpiNNaker and BrainScaleS uses a simulator-independent language, PyNN [8] based on Python. Sequential mapping is used in SpiNNaker. Neural engineering framework (NEF) is developed for Neurogrid [10]. Neutrams [11] addresses an optimized mapping technique based on graph partition problem: Kernighan-Lin (KL) partitioning strategy for network on chips. Even though, every neuromorphic chip simulator tools are addressing certain mapping techniques, optimized mapping onto a single neuromorphic core is often neglected and left unexplored by default. Most of these mapping techniques are hidden within a neuromorphic hardware specific simulators, which mitigate the requirement of an algorithm developer to understand the details of a neuromorphic chip. But, for an optimized co-development of a neural network model for a specific neuromorphic chip, the knowledge of hardware constraints is a must.

Over the years, convolutional neural networks evolved to

become more deep and wide with respect to the evolution of different classication tasks i.e. from simple MNIST handwritten digit classification to much more complex ImageNet image classification. For MNIST classification task, as the neural network is small, the neurons can be mapped manually onto a neuromorphic core. But, for large networks in the case of ImageNet classification, it is near impossible to manually mention how the neurons in every layers are mapped to each core in a neuromorphic chip. Hence, an automated procedure is necessary for identifying the neuron addresses with corresponding synaptic weights and input values.

In this paper, aforementioned issues are mitigated with the help of MaD framework and its optimizations. MaD framework is a generic Python wrapper which has an optimized algorithm for mapping any feed forward neural network such as MLP, CNN, SNN onto a crossbar array of synapses with corresponding synaptic weights, thereby fitting the neurons in minimum possible number of neuromorphic cores. Python wrapper is also suitable as a debugging tool for verification of the inferencing of neural network architectures on the neuromorphic chip. Thus together the framework is called as mapping and debugging (MaD) framework. This Python wrapper is developed in connection with the simulator in [12], where most of the techniques are quite similar to Neutrams [11].

The paper is organized as follows. Section II briefly describe about the crossbar array of synapses and the spiking neuron in a neuromorphic chip. Section III illustrates the details of MaD framework. Section IV shows the implementation of MNIST and CIFAR-10 classification task on MaD framework. Finally the paper is concluded with discussion in section V.

## II. MATERIALS AND METHOD

# A. Spiking Neuron

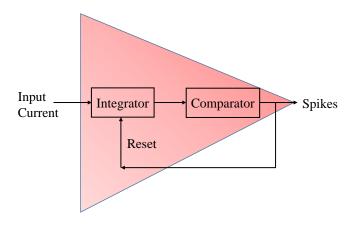

Fig. 1. Block diagram of a spiking neuron.

Biological neuron computes the signal received through multiple dendrites and transmits the output signal through axons to other neurons connected in the network [13]. Fig 1 shows a block diagram representation of the biological neuron. Neuron has mainly two blocks, an integrator and a comparator. The integrator sums up all the input currents (excitatory post-synaptic current, EPSC) and build up the membrane potential. This membrane potential is being monitored by the comparator to cross certain threshold. If the membrane potential crosses the set threshold, neuron emits an output spike and then resets the membrane potential back to its initial value. The communication between neurons in the biological network or in a spiking neural network (SNN) is with the help of these output spikes. The entire mechanism of a spiking neuron can be modelled with the leaky integrate and fire neuron model and its mathematical expression [14] is given below:

$$\tau_m \frac{du}{dt} = -[u(t) - u_{rest}] + RI(t) \tag{1}$$

Where,

$\tau_m$  = RC, is the membrane time constant of leaky integrator.

u(t) = membrane potential

I(t) = synaptic current

$u_{rest}$  = membrane resting potential

# B. Crossbar Array of Synapses

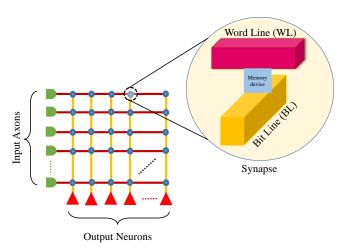

Fig. 2. Crossbar array of synapses in a neuromorphic core.

Fig. 2 shows a crossbar array of synapses. The crossbar structure is very suitable for performing matrix dot vector multiplication (MVM) [15] along each column in a crossbar architecture. For instance, a neuromorphic core with a core size of 256×256, input voltages from respective axons out of 256 are given through word line. Bit line collects all the weighted current at each synaptic nodes (256×256) and delivers to respective output neurons (256) for integration. The weighted current depends on the memory element used in the intersection of word line and bit line as synapse. The synaptic weights, which draws analogy to conductances, are represented in the form of blue dots at the cross points. From Kirchoffs current law, the total current flowing into each neuron from respective bit lines is the sum of currents flowing through each intersection in every column. In fact, in conventional neural networks, total current of a particular column is the value of

a single neuron activation in a particular layer, formed by summation of products of input voltages and corresponding synaptic weights (conductances) taking part in convolution operation.

#### III. MAD FRAMEWORK

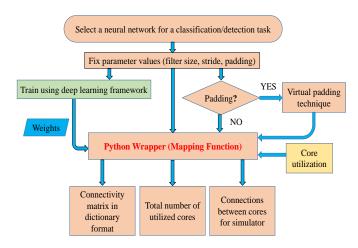

This section illustrates the details of the construction of MaD framework. The complete usage of the framework is explained with a flowchart as shown in fig. 3. A particular neural network is chosen for a classification or a detection task. The parameters like filter size, strides and padding among each layers are fixed. The chosen network is trained using deep learning tool for obtaining the weight files to be given as input to the mapping function. Core utilization is defined as the number of axons and neurons utilized in a single neuromorphic core. Core utilization, as shown in the flowchart, is an output from another function which calculates the number of axons and number of neurons used for mapping a section of particular layer onto a single core. Core utilization is represented as [axons  $\times$  neurons]. The details of the mapping function, core utilization and padding techniques are given in the subsequent subsections. This section is ended by including optimizations to be considered while mapping.

Fig. 3. **Flowchart of Python wrapper:** The details of the Python wrapper is shown with a flowchart. The input and output of the mapping function that is used in the python wrapper is illustrated in the flowchart. The core utilization and weight files are marked in different color to show that these inputs are the results from other functions.

## A. Mapping Function

The mapping function is the core of the Python wrapper as shown in fig. 3. Fig. 3 shows the input and output of the mapping function. The inputs to mapping function are input size, filter size, stride, padding, core utilization and weight files. The input size is the size of the input datasets, for eg.  $28 \times 28$  in the case of MNIST or  $32 \times 32$  in the case of CIFAR-10. Filter size is the size of filters used for convolution in each layers, here it is selected as  $3 \times 3$  throughout the layers of the chosen neural networks in section IV. Stride and padding depends on the layers of the convolutional neural

network. The detailed calculation of the core utilization is mentioned in subsection III-B. Weight files are the weights obtained after training the chosen neural network using deep learning tool. The output section in fig. 3 shows the necessary outputs that is obtained from the mapping function. There are mainly three outputs, a connectivity matrix for verifying the interconnectivity between the cores and within the core, to verify the cores utilized and an automated generation of connection list for simulator.

The steps for mapping are as follows:

- 1. All the neurons are first named to follow a regular pattern eg. L1-F1-N[1,1] this implies layer:1, feature map:1, and neuron in row:1 and column:1.

- 2. Prepare a connectivity list of population of neurons in a particular layer connected to the previous layer.

- 3. Choose a population of neurons from a particular layer, based on the core utilization, to be mapped on to a particular core.

- 4. Repeat this process until entire neurons in every layers are completely mapped onto the core. Since the naming and connectivity list are fixed at the beginning, the neurons and axons will be automatically duplicated among the cores for mapping.

#### B. Core Utilization

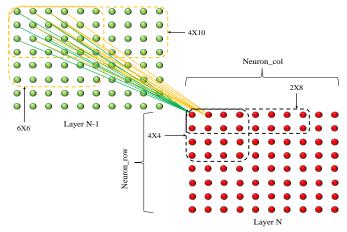

Fig. 4. Two layers of convolution layer to illustrate the optimization of core utilization. Layer N-1 neurons are in green, whereas layer N neurons are in red. Synaptic connections are shown for two neurons in layer N.

Consider two layers of a convolutional neural network shown in fig 4. The neurons in layer N is marked as red and neurons in layer N-1 is marked as green. First two neurons in layer N is connected to layer N-1 and the synaptic connections are shown with straight lines. The convolution filter size used is 3×3, hence you can see 9 connections from each red neurons in layer N to 9 green neurons in layer N-1. Likewise, the synaptic connections can be imagined throughout the layer with respect to the kernel size and strides used for convolution. While mapping these two layers in fig. 4 onto a core with crossbar array, the green neurons in layer N-1 will be the

axons and the red neurons in layer N will be the neurons as in fig 2. Notice the overlap of filter window when it strides across the layer. In fact these overlapped green neurons can be mapped onto the crossbar array connections without any duplication. Duplicating the axons, while one to one mapping of neurons connected to axons onto a core, is not a good design with respect to core utilization as input needs to be duplicated into many axons and also mapping requires bigger core sizes and ends up utilizing many cores [16]. Hence, the toeplitz matrix method is utilized for efficient mapping of these layers onto a neuromorphic core without input duplication. Toeplitz method for convolution is illustrated in [17] [18]. Inorder to calculate the core utilization, the number of neurons and axons connected together has to be chosen which could be entirely mapped onto a single core. The number of axons can be evaluated as an algorithmic condition in the mapping function as there are overlapping axons whereas neurons selection become bit straight forward. The overlapping axons are defined as the axons which share connections with more than a single neuron, the term overlapping is because of the overlapping nature of the axons with the neighbourhood of the kernel filter with respect to strides (see layer N-1 in fig. 4, the overlapping axons among the green and yellow synaptic connections are 3). Depending on this overlap, kernel filter size and strides, the total number of axons to be selected follows the formula as given below:

$$\begin{split} N\_axons &= KXK + KXSX(Neuron\_col - 1) + \\ SXSX(Neuron\_col - 1)X(Neuron\_row - 1) + \\ KXSX(Neuron\_row - 1) \end{split} \tag{2}$$

Where,

$N_axons = total$  number of axons to be selected

K = convolution filter size

S = stride

$Neuron\_row$  = number of neurons across row

$Neuron\_col$  = number of neurons across column

The selection of neurons,  $Neuron\_row$  and  $Neuron\_col$ , in a layer depends on the condition: number of axons,  $N\_axons <=$  number of physical axons (eg. 256 or 512 or 1024) in the neuromorphic core. Eq. 2 is considering only a single feature map, this can be easily extended to multiple feature maps by multiplying with respective channel size.

### C. MaD Framework Optimizations

1) Core Utilization: Referring to fig. 4, consider a case for calculating core utilization, suppose 16 neurons has to be chosen from layer N for mapping onto a core. This can be done by choosing 2 rows and 8 columns of neurons or 4 rows and 4 columns of neurons. Here, rows and columns of neurons correspond to  $Neuron\_row$  and  $Neuron\_col$  in eq.2. If the convolution kernel size, K used is  $3\times3$  and stride, S is 1, then for 2 rows and 8 columns of neurons the axons required are 4 rows and 10 columns, similarly for 4 rows and 4 columns of neurons the axons required are 6 rows and 6 columns. This can

be easily estimated from the formula to calculate the output size of convolutions as given below:

$$O_{-}width = \frac{I_{-}width - F_{-}width}{Stride_{-}width} + 1$$

$$O_{-}height = \frac{I_{-}height - F_{-}height}{Stride_{-}height} + 1$$

(3)

Where,

O\_width and O\_height = Width and height of the convolution output respectively

$I\_width \ and \ I\_height$  = Input width and height respectively  $F\_width \ and \ F\_height$  = Width and height of filter kernel  $S\_width \ and \ S\_height$  = Width and height of strides

The above case suggest that choosing neurons from 4 rows and 4 columns are much better for core utilization than from 2 rows and 8 columns as input number of axons in former case is only 36 whereas, in the later case it is 40. That means the core utilization is  $[36 \times 16]$  in the former case and  $[40 \times 16]$  in the later case. The intuition from this example case is that the neurons to be selected for mapping onto the core is better to be in square shape than in rectangular shape. The section below provides a mathematical proof for choosing square shape rather than rectangular shape while mapping:

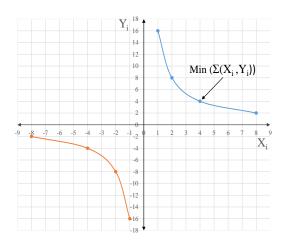

Fig. 5. Graphical illustration of the theorem.

Theorem: Given 'a', find  $X_i$  and  $Y_i$  such that:  $X_i \times Y_i = a$  and minimum of  $\sum (X_i, Y_i)$ .

*Proof*: The graphical illustration of the theorem is shown in fig. 5.

Consider

$$XY = a$$

and  $X + Y = Z$

where  $Z$  is a real number

$$X + \frac{a}{X} = Z$$

$$\frac{dZ}{dX} = 1 - \frac{a}{X^2}$$

at minima  $\frac{dZ}{dX} = 0$ , (4)

$$\therefore 1 - \frac{a}{X^2} = 0$$

$$X = + -\sqrt{a}$$

If  $X > 0$ ,  $Z$  is minimum  $\therefore X = \sqrt{a}$

also  $Y = \sqrt{a}$  and  $X + Y$  is the minimum.

2) Padding: Padding is a common technique used in deep learning for maintaining the shape of the convolution layers throughout the network. Padding simply adds extra zeros around the input activations in a convolution layer during convolution operation. In fact such added zeros doesn't provide any computational significance as mathematically zeros are multiplied and added. While mapping, these padded zeros are in fact physical neurons, but need not be participating in computation. If these neurons are considered as physical neurons during mapping, then there will be a lot of wastage on axon usage. This will reduce the optimized utilization of core. Hence, as shown in fig. 3 (mentioned as virtual padding technique), when padding is used in a particular convolution layer, a virtually padded neuron address is created and is assigned in the connectivity list. Later, while mapping onto the core these virtually padded neurons are removed from the connectivity list, reducing the fan in connection of those particular neurons in the periphery of a layer connected to those padded neurons in the previous layer.

#### IV. RESULTS

This section mainly provides an instance of the utilization of neuromorphic chip using a classification task on MNIST and CIFAR-10 datasets through the parameters, core utilization and number of cores utilized. Here, the focus is not on improving the accuracies, but to show the neuromorphic core utilization while mapping, with a much simpler handcrafted neural network. All the accuracies mentioned in this section is iterated for ten times and then averaged it out. Two sets of experiments are done for that purpose, one is to choose a particular neural network architecture for classification task on MNIST and CIFAR-10 datasets and keep that architecture constant among different core sizes. Different core sizes chosen here are  $[256 \times 256]$ ,  $[512 \times 512]$  and  $[1024 \times 1024]$  (core sizes need not be in square shape but any other shapes are also possible). Here, the accuracy will be same, as architecture is constant, while the core utilization and number of cores utilized will be different among different core sizes. Second set of experiment is to change the neural network architecture for different core sizes. This will change the accuracy of neural network architectures for different core sizes, but the number of cores utilized will remain same.

TABLE I Neural network (NN) architecture for MNIST dataset

| NN           | Core Size |          |           |  |

|--------------|-----------|----------|-----------|--|

| Architecture | 256×256   | 512×512  | 1024×1024 |  |

| Input        | 28×28×1   | 28×28×1  | 28×28×1   |  |

| Layer 1      | 28×28×8   | 28×28×16 | 28×28×32  |  |

| Layer 2      | 14×14×16  | 14×14×32 | 14×14×64  |  |

| Layer 3      | 6×6×64    | 6×6×128  | 6×6×256   |  |

TABLE II

NEURAL NETWORK (NN) ARCHITECTURE FOR CIFAR-10 DATASET

| NN           | Core Size |                          |           |  |

|--------------|-----------|--------------------------|-----------|--|

| Architecture | 256×256   | 512×512                  | 1024×1024 |  |

| Input        | 32×32×3   | 32×32×3                  | 32×32×3   |  |

| Layer 1      | 30×30×8   | 30×30×16                 | 30×30×32  |  |

| Layer 2      | 14×14×16  | $14 \times 14 \times 32$ | 14×14×64  |  |

| Layer 3      | 6×6×64    | 6×6×128                  | 6×6×256   |  |

1) Keeping architecture constant: Consider the architecture shown in table I and II. The softmax classifier output layer is not shown in the tables. For this set of experiment, the architecture is maintained same irrespective of different core sizes - neural network architecture chosen for MNIST and CIFAR-10 datasets are given in the first column under the core size, 256×256 respectively in both tables I and II. The neural network architecture is kept constant while mapping onto other core sizes as well. The convolutional filter size used is  $3\times3$  throughout the layers. In table I, between input layer and layer 1, stride used is 1 and with padding in the input activations. Between layer 1 and layer 2, stride used is 2 and with padding in the input. Between layer 2 and layer 3, stride used is again 2 but without padding in the input. In table II, between input layer and layer 1, stride used is 1 and without any padding in the input. Between layer 1 and layer 2, stride used is 2 and without padding in the input. Between layer 2 and layer 3, stride used is again 2 but with padding in the input. From table III and IV, the results for MNIST and CIFAR-10 classification accuracy is constant among all the core sizes as the architecture remains same, while the core utilization and number of cores utilized changes with core sizes.

TABLE III

KEEPING ARCHITECTURE CONSTANT: MNIST DATASET

| Acc   | Core Size |             |       |             |       |             |

|-------|-----------|-------------|-------|-------------|-------|-------------|

| (%)   | 024       | 1024×1      | 12    | 512×5       | 56    | 256×2       |

| 1     | No of     | Core        | No of | Core        | No of | Core        |

|       | cores     | utilization | cores | utilization | cores | utilization |

|       | 7         | [180,1024]  | 15    | [100,512]   | 28    | [60,256]    |

| 98.64 | 10        | [968,400]   | 25    | [504,192]   | 49    | [200,64]    |

|       | 3         | [1008,768]  | 9     | [400,256]   | 18    | [240,128]   |

| Total |           |             |       |             |       |             |

| cores | 20        |             | 49    |             | 95    |             |

TABLE IV

KEEPING ARCHITECTURE CONSTANT: CIFAR-10 DATASET

| Core Size   |       |             |       |             | Acc   |       |

|-------------|-------|-------------|-------|-------------|-------|-------|

| 256×2       | 256   | 512×5       | 512   | 1024×1      | 024   | (%)   |

| Core        | No of | Core        | No of | Core        | No of |       |

| utilization | cores | utilization | cores | utilization | cores |       |

| [180,240]   | 30    | [300,512]   | 14    | [540,1024]  | 7     |       |

| [200,64]    | 49    | [504,192]   | 17    | [968,400]   | 10    | 61.41 |

| [240,128]   | 18    | [400,256]   | 9     | [1008,768]  | 3     |       |

|             |       |             |       |             |       | Total |

|             | 97    |             | 40    |             | 20    | cores |

2) Keeping architecture different: The different neural network architectures chosen for MNIST and CIFAR-10 datasets for different core sizes are shown in table I and II. For this set of experiment, the architecture is changed slightly to fit onto the respective core sizes. The modification of the network is only done on the number of feature maps or channels in different layers. This modification will not really affect the mapping much. But, rather better accuracies are obtained with same number of cores utilized. The convolutional filter size used is  $3\times3$  throughtout the layers. The strides and padding used between all the layers are exactly same as mentioned in the previous subsection. From table V and VI, the results for MNIST and CIFAR-10 classification accuracy is shown for different core sizes and can be seen that the accuracy improves with increase in core sizes. This is obvious that bigger network can be mapped on to neuromorphic chips with bigger core sizes, bigger the network, better the accuracy. The core utilization varies with mapping but the number of cores utilized remains same with core sizes.

TABLE V

KEEPING ARCHITECTURE DIFFERENT: MNIST DATASET

|           | No: of    |           |         |

|-----------|-----------|-----------|---------|

| 256×256   | 512×512   | 1024×1024 | (cores) |

| [60,256]  | [60,512]  | [60,1024] | 28      |

| [200,64]  | [400,128] | [800,256] | 49      |

| [240,128] | [480,256] | [960,512] | 18      |

|           |           |           | Acc     |

| 98.64     | 98.75     | 98.89     | %       |

TABLE VI

KEEPING ARCHITECTURE DIFFERENT: CIFAR-10 DATASET

|           | No: of    |            |         |

|-----------|-----------|------------|---------|

| 256×256   | 512×512   | 1024×1024  | (cores) |

| [180,256] | [180,512] | [180,1024] | 30      |

| [200,64]  | [400,128] | [800,256]  | 49      |

| [240,128] | [480,256] | [960,512]  | 18      |

|           |           |            | Acc     |

| 61.41     | 64.39     | 66.25      | %       |

## V. DISCUSSION AND CONCLUSION

Random access memories are popular in terms of inmemory computation. Resistive random access memory

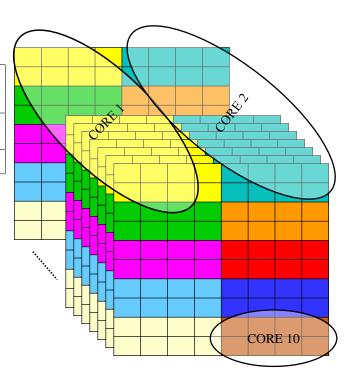

Fig. 6. Division of a convolutional neural network layer into different neuromorphic cores.

(RRAM) became more popular in the field of neuromorphic computing chips with the capability of doing both computation and memory at the same time. These two terminal RRAM devices are very much compatible with the crossbar array of synapses architecture, which enhanced its acceptance in the field of neuromorphic chips. Apart from RRAM, there are other devices like floating-gate MOSFET [19] [20] [21] [22], memristors [23] [24] [25], thin-film devices [26] and spin devices [27] to be the contender of synaptic devices in a neuromorphic chip.

The mapping of different portions of a convolutional layer onto different cores is shown in the fig. 6. Different colors within the layer shows that those neurons are mapped onto particular core. For example, neurons in yellow are mapped onto core 1 and neurons in brown are mapped onto core 10 etc.

The challenges in mapping onto a single neuromorphic core are mainly explained in the section for optimizations. One of the major priority while mapping is to choose the shape of the neurons in a layer that the chosen neurons and its corresponding axons could map completely onto a neuromorphic core without splitting the matrix between cores. Another concern is to avoid the padded neurons while inferencing or mapping as these padded neurons during training is necessary to keep the size of the input activations but during inference these padded neurons become hardware overhead. In this paper, these two challenges are mitigated using simple techniques in the mapping function.

From the results, it can be seen that bigger the core size,

easier to map a bigger network and better the accuracy. Similarly, if the accuracy is fixed, then the lesser number of cores are utilized in a neuromorphic chip with bigger core size. This is infact better compared to usage of more number of cores in a neuromorphic chip with smaller core sizes because the communication between neuromorphic cores will consume more power than the computations. Eventhough the neuromorphic chip with bigger core size is preferable, the bottleneck is the design possibility of such bigger crossbar array of synapses with the latest CMOS technology. Number of cores in a neuromorphic chip depends on the core size and the available silicon area for the chip. Hence, number of cores and core size become a neuromorphic hardware constraint other than the major hardware constraints like synaptic noise. precision of weight and outputs. This paper gives an overview of mapping in neuromorphic chip with respect to the utilization of number of cores. The python wrapper for MaD framework can output a visual representation of each core in a format easily verifiable by the users (.csv or .xls). The verification of network activations and inferencing becomes quite simple as well. The code for python wrapper can be shared upon request.

#### ACKNOWLEDGMENT

#### REFERENCES

- [1] Eustace Painkras, Luis A. Plana, Jim Garside, Steve Temple, Simon Davidson, Jeffrey Pepper, David Clark, Cameron Patterson and Steve Furber, "SpiNNaker: A multi-core System-on-Chip for massively-parallel neural net simulation," Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, pp. 1-4, San Jose, CA, 2012.

- [2] Ben Varkey Benjamin, Peiran Gao, Emmett McQuinn, Swadesh Choudhary, Anand R. Chandrasekaran, Jean-Marie Bussat, Rodrigo Alvarez-Icaza, John V. Arthur, Paul A. Merolla and Kwabena Boahen, "Neurogrid: A Mixed-Analog-Digital Multichip System for Large-Scale Neural Simulations," Proceedings of the IEEE, vol. 102, issue. 5, pp. 699-716, 2014.

- [3] J. Schemmel, D. Briiderle, A. Griibl, M. Hock, K. Meier and S. Millner, "A wafer-scale neuromorphic hardware system for large-scale neural modeling," Proceedings of IEEE 2010 International Symposium on Circuits and Systems, pp. 1947-1950, Paris, 2010.

- [4] J. s. Seo, B. Brezzo, Y. Liu, B. D. Parker, S. K. Esser, R. K. Montoye, B. Rajendran, J. A. Tierno, L. Chang, D. S. Modha, and D. J. Friedman, "A 45nm cmos neuromorphic chip with a scalable architecture for learning in networks of spiking neurons," In 2011 IEEE Custom Integrated Circuits Conference (CICC), pp. 1-4, Sept 2011.

- [5] M. Prezioso, F. Merrikh-Bayat, B. D. Hoskins, G. C. Adam, K. K. Likharev and D. B. Strukov, "Training and operation of an integrated neuromorphic network based on metal-oxide memristors," Nature vol. 521, pp. 61-64, May 2015.

- [6] F. Akopyan et al., "TrueNorth: Design and Tool Flow of a 65 mW 1 Million Neuron Programmable Neurosynaptic Chip," in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 34, no. 10, pp. 1537-1557, Oct. 2015.

- [7] Arnon Amir, Pallab Datta, William P. Risk, Andrew S. Cassidy, Jeffrey A. Kusnitz, Steve K. Esser, Alexander Andreopoulos, Theodore M. Wong, Myron Flickner, Rodrigo Alvarez-Icaza, Emmett McQuinn, Ben Shaw, Norm Pass, and Dharmendra S. Modha, "Cognitive computing programming paradigm: a corelet language for composing networks of neurosynaptic cores," IEEE International Joint Conference on Neural Networks (IJCNN), pp. 1-10, Aug, 2013.

- [8] Davison AP, Brderle D, Eppler JM, Kremkow J, Muller E, Pecevski DA, Perrinet L and Yger P, "PyNN: a common interface for neuronal network simulators," Front. Neuroinform., 2009. 2:11 doi:10.3389/neuro.11.011.2008

- [9] Pande, S., Morgan, F., Cawley, S., McGinley, B., Carrillo, S., Harkin, J., and McDaid, L., "EMBRACE-SysC for analysis of NoC-based spiking neural network architectures," In System on chip (SoC), 2010 international symposium on IEEE, pp. 139-145, Sep, 2010.

- [10] A. R. Voelker, B. V. Benjamin, T. C. Stewart, K. Boahen and C. Eliasmith, "Extending the neural engineering framework for nonideal silicon synapses," IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1-4, Baltimore, MD, 2017.

- [11] Yu Ji, YouHui Zhang, ShuangChen Li, Ping Chi, CiHang Jiang, Peng Qu, Yuan Xie and WenGuang Chen, "NEUTRAMS: Neural network transformation and co-design under neuromorphic hardware constraints," In The 49th Annual IEEE/ACM International Symposium on Microarchitecture (p. 21). IEEE Press.

- [12] M.K.F. Lee, Y. Cui, T. Somu, T. Luo, J. Zhou, W.T. Tang, W.F. Wong, and R.S.M. Goh, "A System-level Simulator for RRAM-based Neuromorphic Computing Chips," accepted by ACM Transactions on Architecture and Code Optimization (TACO).

- [13] Jacek M. Zurada, "Introduction to Artificial Neural System," West Publishing Company, St. Paul, MN, 1992.

- [14] Wulfram Gerstner, Werner M. Kistler, Richard Naud and Liam Paninski, Neuronal Dynamics, Cambridge University Press, July 2014.

- [15] M. Hu et al., "Dot-product engine for neuromorphic computing: Programming 1T1M crossbar to accelerate matrix-vector multiplication," 53nd ACM/EDAC/IEEE Design Automation Conference (DAC), pp. 1-6, Austin, TX, 2016.

- [16] Alom, M. Z., Josue, T., Rahman, M. N., Mitchell, W., Yakop-cic, C., and Taha, T. M. "Deep versus wide convolutional neural networks for object recognition on neuromorphic system," In 2018 International Joint Conference on Neural Networks (IJCNN). 18. doi:10.1109/IJCNN.2018.8489635

- [17] Rathinakumar Appuswamy and Tapan K. Nayak and John V. Arthur and Steven K. Esser and Paul Merolla and Jeffrey L. McKinstry and Timothy Melano and Myron Flickner and Dharmendra S. Modha, "Structured Convolution Matrices for Energy-efficient Deep learning," CoRR, ARXIV, 2016.

- [18] R. M. Gray, "Toeplitz and Circulant Matrices: A Review." Now Publishers, 2006.

- [19] Roshan Gopalakrishnan and Arindam Basu, "Robust doublet STDP in a floating-gate synapse, in Proceedings of the International Joint Conference on Neural Networks, pp. 4296-4301, Beijing, China, Jul. 2014

- [20] Roshan Gopalakrishnan and Arindam Basu, "On the Non-STDP Behavior and Its Remedy in a Floating-Gate Synapse, IEEE Transactions on Neural Networks and Learning Systems, vol. 26, no. 99, pp. 2596-2601, Feb. 2015.

- [21] Roshan Gopalakrishnan and Arindam Basu, "Triplet spike time dependent plasticity in a floating-gate synapse, in Proceedings of the International Symposium on Circuits and Systems, pp. 710-713, Lisbon, Portugal, May. 2015.

- [22] Roshan Gopalakrishnan and Arindam Basu, "Triplet spike time dependent plasticity in a floating-gate synapse, IEEE Transactions on Neural Networks and Learning Systems, vol. 28, no. 4, pp. 778-790, April 2017.

- [23] S. Sagui, C. Mayr, T. Serrano-Gotarredona, H. Schmidt, G. Lecerf, J. Tomas, J. Grollier, S. Boyn, A. Vincent, D. Querlioz, S. La Barbera, F. Alibart, D. Vuillaume, O. Bichler, C. Gamrat, and B. Linares-Barranco, "Plasticity in memristive devices for Spiking Neural Networks," Frontiers in Neuromorphic Engineering. Front. Neurosci. 9:51, 2-March-2015.

- [24] M. Rahimi Azghadi, B. Linares-Barranco, D. Abbott and P. H.W. Leong, "A Hybrid CMOS-memristor Neuromorphic Synapse," IEEE Trans. on Biomedical Circuits and Systems, vol. 11, No. 2, pp. 434-445, April 2017

- [25] Jose M Cruz-Albrecht, Timothy Derosier, and Narayan Srinivasa. "A scalable neural chip with synaptic electronics using cmos integrated memristors," Nanotechnology, 24(38):384011, 2013.

- [26] Rohit Abraham John, Fucai Liu, Nguyen Anh Chien, Mohit R. Kulkarni, Chao Zhu, Qundong Fu, Arindam Basu, Zheng Liu, and Nripan Mathews, "Synergistic Gating of Electro-Iono-Photoactive 2D Chalcogenide Neuristors: Coexistence of Hebbian and Homeostatic Synaptic Metaplasticity," Advanced Materials, 30(25), May, 2018.

- [27] A. Sengupta, K. Yogendra and K. Roy, "Spintronic devices for ultralow power neuromorphic computation (Special session paper)," 2016 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 922-925, Montreal, QC, 2016.