# Quantum circuit optimizations for NISQ architectures

Beatrice Nash, 1,2,3,\* Vlad Gheorghiu, 3,4,5,† and Michele Mosca 3,4,6,7

<sup>1</sup>Department of Physics, Massachusetts Institute of Technology, Cambridge, MA, USA

<sup>2</sup>Department of Computer Science, Harvard University, Cambridge, MA, USA

<sup>3</sup>Institute for Quantum Computing, University of Waterloo, Waterloo, ON, N2L 3G1, Canada

<sup>4</sup>Department of Combinatorics & Optimization, University of Waterloo, Waterloo, ON, N2L 3G1, Canada

<sup>5</sup>softwareQ Inc., Kitchener, ON, Canada

<sup>6</sup>Perimeter Institute for Theoretical Physics, Waterloo, ON, N2L 6B9, Canada

<sup>7</sup>Canadian Institute for Advanced Research, Toronto, ON, M5G 1Z8, Canada

(Dated: Version of November 26, 2021)

Currently available quantum computing hardware platforms have limited 2-qubit connectivity among their addressable qubits. In order to run a generic quantum algorithm on such a platform, one has to transform the initial logical quantum circuit describing the algorithm into an equivalent one that obeys the connectivity restrictions.

In this work we construct a circuit synthesis scheme that takes as input the qubit connectivity graph and a quantum circuit over the gate set generated by  $\{CNOT, R_Z\}$  and outputs a circuit that respects the connectivity of the device. As a concrete application, we apply our techniques to Google's Bristlecone 72-qubit quantum chip connectivity, IBM's Tokyo 20-qubit quantum chip connectivity, and Rigetti's Acorn 19-qubit quantum chip connectivity. In addition, we also compare the performance of our scheme as a function of sparseness of randomly generated quantum circuits, and discuss how to apply our techniques as a subroutine for the more general mapping problem over universal set of gates (Clifford + T).

### I. INTRODUCTION

Near-term quantum devices, such as Noisy Intermediate Scale Quantum Computers (NISQ) [1], are limited by sparse qubit connectivity, and many current compilers require that the input circuit takes into account the allowed connectivity of the hardware. In this paper we introduce a circuit synthesis method that takes as input the connectivity of the hardware and the desired transformation that can be produced using gates from the set  $\{\text{CNOT}, R_Z\}$ , where  $R_Z$  denotes an arbitrary rotation about the Z axis of the Block sphere and outputs a circuit that respects the connectivity of the device. Our results show a significant decrease in CNOT count compared to circuit synthesis methods currently in use and allows for efficient circuit synthesis given any arbitrary connectivity. The method we present is a heuristic: finding the exact optimal solution appears intractable [2].

The concept behind our approach is to take circuit synthesis methods that optimize the CNOT count of the output circuit that perform well under the assumption of full connectivity ([3] for CNOT circuits and [4] for CNOT+ $R_Z$  circuits) and modify them to take into account connectivity constraints. We compare the results to first synthesizing the circuit using the original methods and then accounting for the constraints and found that our approach of considering connectivity constraints and synthesizing the circuit simultaneously produced sizable reductions. These reductions depend on the sparseness of the connectivity and the complexity of the input transformation, as shown in our Results section.

Our method is effective and simple to implement, taking as input the desired transformation (the exact form of which is

described in detail in the Section II - Methods) and the graph representing the connectivity of the device and outputting a circuit that respects the allowed connectivity.

The reminder of this paper is organized as follows. In Sec. II we describe our methodology, followed by our results in Sec. III. In Sec. IV we show how to apply our techniques to arbitrary circuits composed of gates from a universal set, discuss the limitations and also compare with state-of-the art methods of general compilers such as the one implemented in Qiskit [5]. In Sec. V we conclude our manuscript and raise a series of open questions. A fully worked out example that illustrates our methods is depicted in Appendix A.

Note: Recently, the authors of [6] independently presented a similar optimization scheme. Our work is independent of [6], being a longer version of the seminar presented by Beatrice Nash at the Dagstuhl Seminar 18381: Quantum Programming Languages, pg. 120, September 2018, Dagstuhl, Germany [7], slide deck available online at https://materials.dagstuhl.de/files/18/18381/18381.BeatriceNash.Slides.pdf.

### II. METHODS

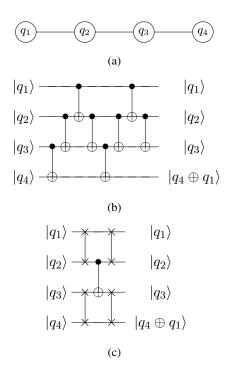

In order to perform a CNOT operation between logical qubits mapped to non-adjacent qubits, a sequence of CNOT gates between adjacent qubits is required to indirectly perform the desired operation. If we have linear nearest-neighbor connectivity, then to perform a CNOT between  $q_1$  and  $q_4$  can be achieved using the example circuits shown in Fig. 1.

These general templates can be extended to work for any physical qubit connectivity graph. While performing a CNOT operation between any two qubits is possible, it is expensive. The circuit depicted in Fig. 1 (b) requires 4(l-1) CNOT gates to perform the operation, where l is the distance between the

<sup>\*</sup> Electronic address: beatricenash@fas.harvard.edu

<sup>†</sup> Electronic address: vlad.gheorghiu@uwaterloo.ca

FIG. 1: a) 4-qubit linear nearest neighbor physical qubit connectivity. b), c) Circuits for performing a CNOT operation with  $q_1$  as the control and  $q_4$  as the target using the connectivity shown in a).

two qubits. The naïve swap circuit in Fig. 1 (c) requires 1+6(l-1) gates. For circuits that dynamically reassign physical and logical qubits, the last two swap gates in Fig. 1 (c) can be removed.

The best current circuit synthesis methods do not account for qubit connectivity when determining the output circuit. CNOT operations in the optimized output circuit must be replaced by templates such as those shown previously to account for the connectivity of the physical device. Given the sparsity of connectivity graphs of near-term quantum devices, this step increases the CNOT count drastically.

### A. Linear reversible circuit synthesis

The first class of circuits we look at synthesizing are linear reversible circuits consisting of only CNOT gates. In the Clifford + T universal gate set, the only two-qubit gate needed to achieve universal quantum computation is the CNOT gate, and therefore the efficient synthesis of CNOT circuits is useful for optimizing broader classes of circuits given restricted connectivity. Additionally, CNOT gates are far noisier than single qubit gates, and thus minimizing the number of CNOT gates in a circuit is helpful for reducing errors.

Patel, Markov and Hayes give in [3] an asymptotically optimal algorithm for synthesizing linear reversible circuits assuming full connectivity. The result is a  $O(\frac{n^2}{\log n})$  size circuit in the worst case, where n is the number of qubits. In [8] it is

proven that, for n qubits, there exists a linear transformation for which the optimal circuit producing that transformation (again, assuming full connectivity) is size  $\Omega(\frac{n^2}{\log_2 n})$ ; hence, the method in [3] is optimal in the worst case to within a multiplicative constant. However, each single CNOT gate in the output circuit using method [3] becomes O(n) gates using the template in Fig 1. b to account for connectivity constraints. Thus, the resulting circuit increases to size  $O(\frac{n^3}{\log n})$  in the worst-case under connectivity constraints. The algorithm we propose in this section improves on this performance, achieving an  $O(n^2)$  worst-case bound on the size of the resulting circuit, regardless of connectivity.

The algorithm in [3], which is the foundation for that proposed here, takes as input an arbitrary linear transformation represented by a  $n \times n$  binary matrix and outputs a circuit that produces the desired transformation.

The initial state of the n qubits is represented by the  $n \times n$  identity matrix and each CNOT applied produces a row operation. Specifically, a CNOT with target i and control j multiplies the matrix representation of the circuit by the elementary matrix  $A_{i,j}$ , which is the matrix with all elements on the diagonal and (i,j) equal to 1 and all others equal to 0. This results in the bitwise addition of row i to row j. Hence, each row corresponds to the parity of the associated qubit. An example is given in Fig. 2.

The idea behind the process is to reverse engineer a circuit from the matrix representation of the transformation. The algorithm from [3] is an optimized version of the Gaussian elimination approach to synthesizing the circuit. The steps are as follows:

- 1. Reduce the matrix to upper-triangular form. Each row operation corresponds to a CNOT in the output circuit.

- 2. Transpose the resulting matrix and repeat, resulting in the identity matrix.

- 3. Construct the output circuit from the operations performed in the following order: first, the operations done in 2) with their control/targets flipped and in the same order in which they were performed, and second, the operations done 1), with their control/targets preserved but the order in which they were performed flipped.

The  $O(\frac{n^2}{\log n})$  upper bound on the number of operations required for this process, as opposed to the  $O(n^2)$  operations required for row reduction via Gaussian elimination, is achieved by partitioning. The matrix is divided into  $\frac{n}{\log_2 n}$  sections of size  $\log_2 n \times n$ . Starting with the first section–after placing a 1 on the diagonal, if necessary–eliminate duplicate sub-rows within that section before performing row reduction normally. Then move on to the next section and do the same for the rows below the first  $\log_2 n$ . Continue in this way until the matrix is in upper triangular form, then transpose and repeat.

The algorithm we propose does not make use of the partitioning (although it can be easily altered to do so), because it takes advantage of grouping multiple row operations to perform together. We found that while partitioning works well when physical qubits are fully or very nearly fully connected

$$\begin{pmatrix} 1 & 0 & 0 & 1 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix} \times \begin{pmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 1 \end{pmatrix} \times \begin{pmatrix} 1 & 0 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{pmatrix} = \begin{pmatrix} 1 & 0 & 1 & 1 \\ 1 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 1 & 1 \end{pmatrix}$$

$$(a)$$

FIG. 2: a) Matrix operations corresponding to CNOTs in circuit in b).

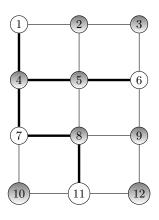

FIG. 3: a) Matrix representation of linear transformation; b) Connectivity of physical qubits.

$(\gtrsim 85\%)$ , for connectivity as sparse as that of near-term devices our algorithm works best without the use of partitioning. Therefore, we do not go into more details of the process; for more information, see [3].

Now, we give the intuition for the motivation for our method, using an example of a linear transformation on 6 qubits and their connectivity given in Fig. 3 (see Appendix A for the fully worked-out example). To eliminate the ones in the first column below the first row, the method in [3] uses row 1 as the control for each of the operations. Thus, using this example, the sequence of operations for the first columnrepresented as (control, target)-is (1,3), (1,4), (1,5). Under the assumption of full connectivity, this makes no difference. However, with restricted connectivity, each operation requires 4(l-1) CNOT gates when using the template in Fig 1.b, where l > 1 is the length of the shortest path between the two physical qubits. Thus, this sequence of operations requires 4 + 8 + 4 = 16 CNOT gates. However, if we are to instead perform the row operations (4,5), (3,4), (1,3), the ones below entry (1,1) are still eliminated, and instead of 16 CNOT gates, only 1 + 1 + 4 = 6 are required.

Give a connectivity graph and a set of rows, our goal is to find the shortest set of paths through the graph that effectively hits each of the nodes associated with those rows. Then, we want to convert that path into a sequence of operations that effectively eliminates each of the rows, while leaving the rest unchanged.

FIG. 4: A solution to the Steiner tree problem on this graph, with each edge having weight 1. The non-shaded nodes are the terminals. The bold edges are those included in the solution. Nodes 4, 5, and 8 are Steiner nodes.

### B. Steiner tree problem reduction

This problem reduces to the *Steiner tree* problem on the connectivity graph G with edge weights of 1 and the set S equal to the nodes associated with the control and the set of rows to be eliminated. The Steiner tree problem is that of finding the minimum weight tree, T, that is a subgraph of G and includes, but is not limited to including, all nodes in S. Nodes in S are called terminals, and nodes in T but not in S are known as Steiner nodes. An example is shown in Fig. 4. The reason for this reduction, perhaps not instantly clear, will become so once shown how to transform a tree into a sequence of row operations.

We want to translate this tree,  $T_{\{c,S\}}$ , where c is the control, into a sequence of operations that effectively eliminates each row in  $S \setminus \{c\}$  using only operations between adjacent nodes.  $S \setminus \{c\}$  is the set of rows in the linear transformation matrix with ones in their cth entry. We now describe in detail the process of converting a tree to a sequence of row operations. Note that the process differs between whether the row operations are performed before or after the transpose step.

In order to convert the tree into a sequence of row operations, we first separate it into a set of edge disjoint subtrees  $\{T_{\{c_i,S_i\}}\}$  with root  $c_i\epsilon S$  and leaves  $S_i\setminus\{c_i\}\subset S$ . The remaining nodes in each sub-tree are Steiner nodes. The first sub-tree,  $T_{\{c_1,S_1\}}$ , is rooted at c. Starting from c, grow

FIG. 5: Resulting sequence of operations from the tree in Fig 4.

the sub-tree by traversing  $T_{\{c,S\}}$  in breadth first search order. When arriving at a non-leaf terminal u, add u to  $T_{\{c_1,S_1\}}$  as a leaf and create a new sub-tree containing a copy of u as a root. Once the sub-tree rooted at c is complete, build the sub-trees rooted at its leaves. Continue until all the edges in  $T_{\{c,S\}}$  have been added to a sub-tree. The root of each sub-tree will be used as the control to eliminate each of its leaves.

Compute the sequence of row operations as follows. Starting with the *last* sub-tree constructed, traverse the tree in reverse depth first search order. When traversing an edge (u, v), where u is closer to the root than v, add a row operation to the sequence with u as the control and v the target. Once the top of the tree is reached, we have a sequence of operations R. Let R' = reverse(R - R[j]), where R[j] is the last operation in R. Now, create  $R^*$  by removing from R + R' those operations with terminals as the targets. R + R' applies the row eliminations, while  $R^*$  undoes those performed on the Steiner nodes, leaving them unchanged.  $R + R' + R^*$  gives the completed sequence of operations for that sub-tree. Add  $R + R' + R^*$  to the overall sequence of operations and move on to the prior sub-tree until all have been traversed.

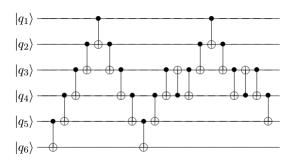

We give an example in Fig. 5 for the resulting sequence of operations for the tree in Fig. 4 (assuming before the transpose step), using node 1 as the overall control. Each CNOT in the circuit shown corresponds to a row operation with the same control and target; they are shown this way to help visualize the result. In the resulting circuit, just as in the original algorithm, if these eliminations are performed before the matrix is transposed, their order will be flipped in the resulting circuit. If they occur after, their control/targets will be flipped, but their order will be preserved.

Each edge will be traversed exactly once in this process. Thus, the total number of gates required will be approximately 4\*(l-d), where d is the number of terminals (excluding the control) and l is the number of edges in the tree. It is clear that for minimum l, this is the optimal solution; hence the reduction to the Steiner tree problem.

The minimal Steiner tree problem, however, is NP-hard. There are approximation algorithms that come close to optimal the best being within a factor of 1.39, given in [9], which improved on the previous bound of 1.55, given in [10]. How-

ever, their run-time is insufficient for our algorithm, which requires many iterations, two for each row. The algorithm we use, given in [11], is somewhat of a combination between the better-performing and more efficient approximation algorithms.

Given a set of terminals and a connectivity graph, the algorithm performs breadth-first search outwards from each of the terminals. When the paths collide, the nodes along that path consolidate into a single node and all the edges adjacent to the consolidated nodes are placed adjacent to this new node. The process is restarted with this node as a new terminal. The total time will therefore be O(d\*(|V|+|E|)), where d is the number of terminals. The resulting Steiner tree is within a factor of  $O(1-\frac{1}{l})$  times the size of the optimal tree, where  $O(1-\frac{1}{l})$  is the number of leaves in the optimal tree. From many trials, it seems that this approximation is sufficient to see a large reduction in the CNOT count of the output circuit. The choice of Steiner tree approximation algorithm for this purpose depends on the user's efficiency and performance requirements; a survey is given in [12].

The algorithm thus far works as follows:

- 1. Start with column i = 1.

- If entry (i, i) = 0, find all rows j such that (j, i) = 1 and j > i. Choose j with the shortest path in the connectivity graph to i, and use this path to perform a series of allowed row operations that adds row j to row i.

- 3. Find rows below row i with entry in column i equal to 1. Create set of terminals S from nodes associated with those rows in addition to node i.

- 4. Find Steiner graph approximation with connectivity graph G and terminals S.

- 5. Compute row operations using this graph that eliminate those rows with constraints on allowed row operations. Perform those operations and compute resulting matrix.

- 6. Repeat steps 2-5 on the next columns, until the matrix is in upper-triangular form.

- 7. Transpose the matrix and repeat.

After the matrix is transposed, we must alter step 5 in the process slightly. Now, say that a row operation is effectively performed between (i,j), with i as the control, and j as the target. If i>j, then the lower-triangular form of the matrix is ruined. Thus, we have to alter the algorithm so as to only allow effective row operations with a lower index row as the control and a higher index as the target.

To do this, perform the Steiner tree algorithm as before, except use the smallest node as the control for all of the operations. Fig. 6 shows how to eliminate two rows on the same path, which is never necessary before the transpose step. From Fig. 6 it is clear that the maximum number of additional gates required to ensure this requirement is 4 \* d.

Let the output sequence of operations before the transpose step be a list A and after the transpose step be a list B. When

adding each operation to the output sequence B, flip the control and target. The output circuit will be: B + reverse(A).

The Steiner tree approximations will always be size O(n). Since the number of operations is O(4\*(size of tree)), then the operations required will be O(n). Since there are O(n) trees computed in total throughout the execution of the algorithm (O(1) per column), then the overall number of operations is  $O(n^2)$ , regardless of connectivity.

### C. CNOT + phase circuit synthesis

The other class of circuits we look at synthesizing given connectivity constraints are those consisting of CNOT gates and Z-basis rotations of arbitrary angles. Amy, Azimzadeh, and Mosca give in [4] a heuristic algorithm for the efficient synthesis of CNOT count optimized circuits in this class assuming full connectivity. The results in [4] show a 23% decrease in the CNOT count on average for a suite of Clifford+T benchmark circuits.

The  $\{CNOT, R_z\}$  circuit to be synthesized is described by its *phase polynomial* f and matrix A representing the overall linear transformation on the basis states. (f, A), known as the *sum-over-paths* form, fully defines the desired unitary transformation applied by the output circuit,  $U_C$ . For a size n-qubit circuit:

$$U_C = \sum_{\mathbf{x} \in \mathbb{F}_2^n} e^{2\pi i f(\mathbf{x})} |A\mathbf{x}\rangle \langle \mathbf{x}|,$$

where  $\mathbb{F}_2^n$  is the set of all length n bit strings, and  $f(\mathbf{x})$  is given by:

$$f(\mathbf{x}) = \sum_{\mathbf{y} \in \mathbb{F}_2^n} \hat{f}(\mathbf{y})(x_1 y_1 \oplus x_2 y_2 \oplus ... \oplus x_n y_n).$$

$f(\mathbf{x})$  is the Fourier expansion of f with Fourier coefficients  $\hat{f}(\mathbf{y})$ . Let the support of  $\hat{f}$ , supp $(\hat{f})$ , be the parities with nonzero Fourier coefficient. Since the application of a CNOT gate with control  $x_1$  and target  $x_2$  maps  $|x_1, x_2\rangle$  to  $|x_1, x_1 \oplus x_2\rangle$ , the state of each qubit can be mapped to a bit string representing a parity. Each  $R_Z$  gate is determined by the parity of the state of the qubit on which it is applied at that point in the circuit. The coefficients for each parity  $\mathbf{y} \in \mathbb{F}_2^n$ ,  $\hat{f}(\mathbf{y})$ , are given by the sum of the Z rotation angles on that

FIG. 6: Circuit that produces CNOT operations between both  $q_1,q_3$  and  $q_1,q_6$

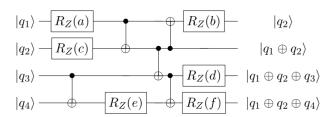

FIG. 7: CNOT + phase circuit example

parity. Hence  $R_Z$  gates acting on the same parity can be combined. For example, the phase polynomial f and basis state transformation A associated with the circuit shown in Fig. 7 is:

$$f = a(x_1) + (b+c)(x_2) + d(x_1 \oplus x_2 \oplus x_3) + e(x_3 \oplus x_4) + f(x_1 \oplus x_2 \oplus x_4)$$

$$A = \begin{pmatrix} 0 & 1 & 0 & 0 \\ 1 & 1 & 0 & 0 \\ 1 & 1 & 1 & 0 \\ 1 & 1 & 0 & 1 \end{pmatrix}$$

The method in [4] first synthesizes a circuit with the input phase polynomial f, then uses the method in [3] to produce the basis state transformation given by input matrix A. To do the former, the goal is to compute a minimal parity network. A parity network is a circuit in which every parity in a set S appears. In our case,  $S = \operatorname{supp}(\hat{f})$ . By applying  $R_Z(\theta)$ , with  $\theta = \hat{f}(\mathbf{y})$ , to each parity  $\mathbf{y} \epsilon S$ , the resulting circuit will have the desired phase polynomial. To apply the linear transformation to the basis states given by A, first compute the linear transformation C resulting from the parity network. Using the method described previously, compute the circuit the linear transformation  $AC^{-1}$  and append it to the end of the existing circuit

To find the exact minimal parity network, however, is NP-hard; a a heuristic for synthesizing an approximation is given in [4]. The algorithm works as follows:

Represent the set of parities as a matrix P, where each column corresponds to a parity and each row to a qubit.

For example, P associated with the circuit given in Fig. 7 is

$$\begin{pmatrix} 1 & 0 & 1 & 1 & 0 \\ 0 & 1 & 1 & 1 & 0 \\ 0 & 0 & 1 & 0 & 1 \\ 0 & 0 & 0 & 1 & 1 \end{pmatrix}$$

where the first column corresponds to parity  $x_1$ , the second to parity  $x_2$ , the third to parity  $x_1 \oplus x_2 \oplus x_3$ , the fourth to parity  $x_1 \oplus x_2 \oplus x_4$ , and the last to parity  $x_3 \oplus x_4$ .

2. Find the row j (of those not yet recursed on) such that:

$$j = \mathrm{arg} \ \mathrm{max}_{i \epsilon \mathrm{cols}(P)} \mathrm{max}_{x \epsilon \{0,1\}} \{|P_{j,i} = x|\}.$$

- 3. Separate P into  $P^0$ , the columns i with  $P_{j,i}=0$ , and  $P^1$ , those with  $P_{j,i}=1$ .

- 4. Recurse on  $P^0$ .

- 5. For  $P^1$ , find row  $i \neq j$  such that all elements in row i of  $P^1$  equal 1. Add a CNOT with control i and target j to our parity network. Set  $P_i = P_i + P_j$ . Repeat until no more such rows are found.

- 6. Recurse on  $P^1$ .

A detailed example of this process can be found in [4]. Our method performs the same series of steps, except step 5 is modified as follows:

5. Compute the approximate Steiner tree of the connectivity graph G with S equal to the set of rows  $\{i\}$  such that each element in row i of  $P^1$  equals 1. Using row j as the control, eliminate them all together in the same manner described in the previous section.

In this case, whether the control bit has greater index than the target is not relevant.

Each parity in  $\operatorname{supp}(\hat{f})$  will appear at least once in this circuit. For each  $\mathbf{y} \in \operatorname{supp}(\hat{f})$ , apply gate  $R_Z(\hat{f}(\mathbf{y}))$  to the qubit with incoming parity  $\mathbf{y}$ . Lastly, append the circuit producing linear transformation  $AC^{-1}$ , taking into account connectivity constraints, using the algorithm described previously.

## III. RESULTS

In this section we compare the size of the output circuits generated using the algorithm described in the previous sections to those generated by first synthesizing the circuit using the method in [3] (for linear reversible circuits) or [4] (for CNOT + T circuits) without taking into account connectivity constraints, then, once the circuit has been synthesized, using the template given in Fig. 1 (b) to take into account the connectivity. In both cases, after the circuit has been synthesized, we further optimize the size of the resulting circuit by commuting operators and canceling where possible.

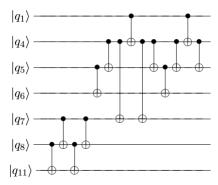

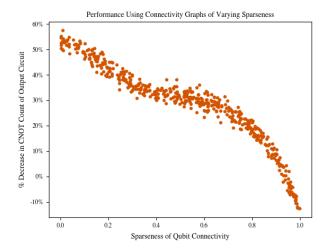

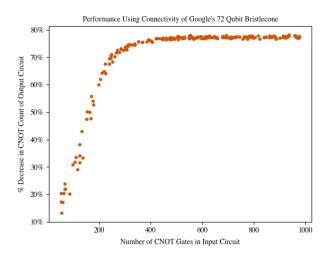

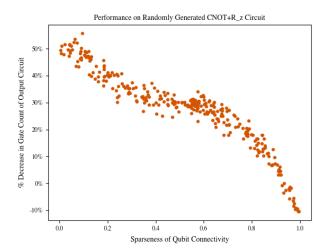

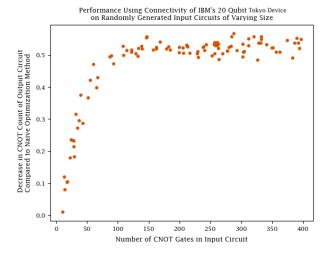

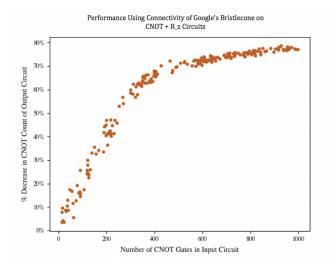

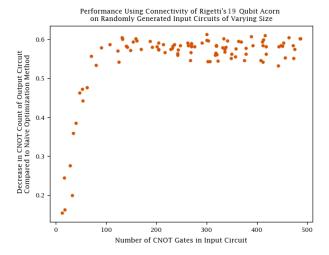

We investigate random circuits on 20 qubits with varying connectivity (results depicted in Fig. 8 and Fig. 10), the Google Bristlecone 72 qubit architecture (results depicted in Fig. 9 and Fig. 11), the IBM Tokyo 20 qubit architecture (results depicted in Fig. 12, and the Rigetti's Acorn 19 qubit architecture (results depicted in Fig. 13.

## IV. UNIVERSAL GATE SETS

We briefly discuss extending the applications of the method described in this paper to universal gate sets. Circuits consisting of CNOT and phase gates alone are not sufficient for universal quantum computing. Adding the Hadamard gate,

FIG. 8: Results for the synthesis of CNOT circuits producing a randomly generated linear transformation on 20 qubits for connectivity of varying sparseness. We repeatedly generate random connected graphs of sparseness between 0.0 and 1.0, where sparseness is defined as the probability that an edge is placed between two qubits. Sparseness of 1.0 is a fully connected graph. The size of the output circuit is compared against the size of the circuit produced by first using the method in [3] (with partitioning) to synthesize a circuit assuming full connectivity and then taking into account connectivity constraints. The reason that our method performs worse than the method in [3] for nearly complete connectivity is due to partitioning, which our method does not use, but which achieves an improvement when the qubits are nearly fully connected. Since qubits in NISQ devices only have nearest-neighbor connectivity, their connectivity is very sparse.

FIG. 9: Results for the synthesis of CNOT circuits producing randomly generated linear transformations of various size on Google's Bristlecone 72-qubit topology. The performance is calculated as described in the caption of Fig. 8.

FIG. 10: Results for the synthesis of CNOT+ $R_Z$  circuits producing a randomly generated linear transformation and Z-axis rotation on 20 qubits for connectivity of varying sparseness. The size of the output circuit is compared against the size of the circuit produced by first using the method in [4] to synthesize a circuit assuming full connectivity and then taking into account connectivity constraints.

FIG. 12: Results for the synthesis of CNOT+ $R_Z$  circuits producing randomly generated transformations for IBM's Tokyo 20-qubit topology.

$H=rac{1}{\sqrt{2}}inom{1}{1}-1$ , to the  $\{\mathrm{CNOT},R_z\}$  gate set makes it universal. Without compromising the universality of the set, we restrict to specific z-rotation gates:

$$S = \begin{pmatrix} 1 & 0 \\ 0 & i \end{pmatrix} , T = \begin{pmatrix} 1 & 0 \\ 0 & e^{\frac{i\pi}{4}} \end{pmatrix}$$

and their conjugate transposes. Let  $\mathbb U$  be the set of circuits composed solely of these gates.

We can apply the methods described here to this more powerful class of circuits as follows. Given a circuit C in  $\mathbb{U}$ , we

FIG. 11: Results for the synthesis of  $CNOT+R_Z$  circuits producing randomly generated transformations for Google's Bristlecone 72-qubit topology. The size of the output circuit is compared against the size of the circuit produced by first using the method in [4] to synthesize a circuit assuming full connectivity and then taking into account connectivity constraints.

FIG. 13: Results for the synthesis of CNOT+ $R_Z$  circuits producing randomly generated transformations for Rigetti's Acorn 19-qubit topology.

can optimize for the number of H gates in the circuit using the "merge and delete" method [13]. Then, partition C into 2\*k segments  $S_{a,b}$ ,  $1 \le a \le k$ ,  $b \in \{\text{CNOT}, H\}$ , such that

$$S_{k,\text{CNOT}}S_{k,H}...S_{1,\text{CNOT}}S_{1,H} = C \tag{1}$$

and each  $S_{i,H}$  contains only H gates while each  $S_{i,\text{CNOT}}$  contains only gates from  $\{\text{CNOT}, S, T, S^\dagger, T^\dagger\}$ . Next, we can apply the methods discussed in previous sections to each of the  $S_{i,\text{CNOT}}$  segments in order to account for connectivity constraints. As discussed in the previous section, our method performs better as gate count increases, so, ideally, we want

to partition the input circuit so that the  $S_{i,CNOT}$  segments are large.

To do so, we use a simple heuristic technique: first, naively partition the input circuit. Say that the size of C, excluding H gates, is n. Then, for i=n to 1, commute gate  $v_i \in \{\text{CNOT}, S, T, S^\dagger, T^\dagger\}$  forward through the circuit until reaching a gate with which it does not commute. Keep track of the largest segment  $S_{i_{\max},\text{CNOT}}$  that  $v_i$  can belong to. Once reaching the end of the circuit or a non-commuting gate, insert  $v_i$  into  $S_{i_{\max},\text{CNOT}}$ . Once  $v_1$  has been reached, repeat this process but in the opposite direction, from i=1 to n, this time commuting backwards instead of forwards.

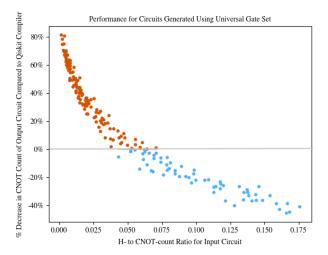

The output circuit could then be further optimized using methods that preserve the allowed two-qubit gates, based on templates, for example, or those that dynamically re-allocate physical and logical qubits [14–16]. Of course, our method works best when the segments consisting of CNOT gates are large (many important circuits, such as quantum Fourier transform, fall under this category, increasingly so as the number of qubits increases [17]). The results are shown in Figure 14 compared to IBM's Qiskit transpiler and demonstrate that for input circuits with  $\lesssim 0.05 - 0.07$  Hadamard to CNOT ratio, this method consistently outperforms the Qiskit compiler, while it does increasingly worse as the ratio grows larger. The input circuits have 1000 gates and do not take into account connectivity. To generate the initial circuit, each gate is chosen from the set {CNOT,  $S, T, S^{\dagger}, T^{\dagger}, H$ } with respective probabilities  $\{p_{\text{CNOT}}, p_S, p_T, p_{S^{\dagger}}, p_{T^{\dagger}}, p_H\}$ . For this experiment,  $p_S=p_T=p_{S^\dagger}=p_{T^\dagger}=0.01,\,p_H\in[0,0.2],\,$  and  $p_{\text{CNOT}}=1-\sum_{i\in\{S,T,S^\dagger,T^\dagger,H\}}p_i.$

## V. CONCLUSIONS AND OPEN QUESTIONS

We constructed a circuit synthesis scheme that takes as input the qubit connectivity graph and a quantum circuit over the gate set generated by  $\{\text{CNOT}, R_Z\}$  and outputs a circuit that respects the connectivity of the device. We applied our techniques to Google's Bristlecone 72-qubit quantum chip connectivity, IBM's Tokyo 20-qubit quantum chip connectivity, and Rigetti's Acorn 19-qubit quantum chip connectivity. We also compared the performance of our methods as a function of sparseness of random quantum circuits of 20 qubits.

Since in practice different CNOT gates can be affected by different amount of noise, an idea for further work would be to weight the edges based on the error rate of the CNOT gate between the respective qubits. Techniques adapted from [4]

could potentially be integrated into the methods given in this paper to produce circuits with lower error rates. In addition, we plan to improve on efficiency and quality of the results produced by our scheme.

We show how the method can be applied to broader classes of circuits comprising of universal set of gates, however our scheme performs (as expected) less optimally than compilers designed specifically for that task, while over-performing the latter for circuits comprising of  $\{CNOT, R_Z\}$ .

FIG. 14: Using the method described in section IV, then by generating circuits from the set U with varied Hadamard to CNOT gate ratios, we can clearly see that while the method works well compared to IBM's compiler for circuits that are mainly composed of CNOT gates, its performance decreases as the ratio of Hadamard to CNOT gates increases. Red solid

circles represent data points in which our scheme over-performs Qiskit, whereas the blue solid circles represent data points in which our scheme performs worse than Qiskit. The "sweet-spot" seem to be around 5%-7% Hadamard to CNOT ratio.

### **ACKNOWLEDGMENTS**

We thank Matt Amy for very useful comments and discussions. We acknowledge support from NSERC and CIFAR. IQC is supported in part by the Government of Canada and the Province of Ontario.

We also want to thank the anonymous referees for the their very helpful suggestions for improving the quality of this manuscript.

<sup>[1]</sup> J. Preskill, Quantum 2, 79 (2018).

<sup>[2]</sup> D. Herr, N. Franco, and S. Devitt, npj Quantum Information 3 (2017).

<sup>[3]</sup> K. Patel, I. Markov, and J. Hayes, Quantum Information and Computation 8, 282 (2008).

<sup>[4]</sup> M. Amy, D. Maslov, and M. Mosca, Computer-Aided Design

of Integrated Circuits and Systems, IEEE Transactions on 33, 1476 (2014).

<sup>[5]</sup> H. Abraham, I. Y. Akhalwaya, G. Aleksandrowicz, T. Alexander, G. Alexandrowics, E. Arbel, A. Asfaw, C. Azaustre, P. Barkoutsos, G. Barron, L. Bello, Y. Ben-Haim, D. Bevenius, L. S. Bishop, S. Bosch, D. Bucher, CZ, F. Cabrera,

P. Calpin, L. Capelluto, J. Carballo, G. Carrascal, A. Chen, C.-F. Chen, R. Chen, J. M. Chow, C. Claus, C. Clauss, A. J. Cross, A. W. Cross, J. Cruz-Benito, Cryoris, C. Culver, A. D. Córcoles-Gonzales, S. Dague, M. Dartiailh, A. R. Davila, D. Ding, E. Dumitrescu, K. Dumon, I. Duran, P. Eendebak, D. Egger, M. Everitt, P. M. Fernández, A. Frisch, A. Fuhrer, I. GOULD, J. Gacon, Gadi, B. G. Gago, J. M. Gambetta, L. Garcia, S. Garion, Gawel-Kus, J. Gomez-Mosquera, S. de la Puente González, D. Greenberg, J. A. Gunnels, I. Haide, I. Hamamura, V. Havlicek, J. Hellmers, Ł. Herok, H. Horii, C. Howington, S. Hu, W. Hu, H. Imai, T. Imamichi, R. Iten, T. Itoko, A. Javadi-Abhari, Jessica, K. Johns, N. Kanazawa, A. Karazeev, P. Kassebaum, A. Kovyrshin, V. Krishnan, K. Krsulich, G. Kus, R. LaRose, R. Lambert, J. Latone, S. Lawrence, D. Liu, P. Liu, P. B. Z. Mac, Y. Maeng, A. Malyshev, J. Marecek, M. Marques, D. Mathews, A. Matsuo, D. T. McClure, C. McGarry, D. McKay, S. Meesala, A. Mezzacapo, R. Midha, Z. Minev, M. D. Mooring, R. Morales, N. Moran, P. Murali, J. Müggenburg, D. Nadlinger, G. Nannicini, P. Nation, Y. Naveh, Nick-Singstock, P. Niroula, H. Norlen, L. J. O'Riordan, P. Ollitrault, S. Oud, D. Padilha, H. Paik, S. Perriello, A. Phan, M. Pistoia, A. Pozas-iKerstjens, V. Prutyanov, J. Pérez, Quintiii, R. Raymond, R. M.-C. Redondo, M. Reuter, D. M. Rodríguez, M. Ryu, M. Sandberg, N. Sathaye, B. Schmitt, C. Schnabel, T. L. Scholten, E. Schoute, I. F. Sertage, N. Shammah, Y. Shi, A. Silva, Y. Siraichi, S. Sivarajah, J. A. Smolin, M. Soeken, D. Steenken, M. Stypulkoski, H. Takahashi, C. Taylor, P. Taylour, S. Thomas, M. Tillet, M. Tod, E. de la Torre, K. Trabing, M. Treinish, TrishaPe, W. Turner, Y. Vaknin, C. R. Valcarce, F. Varchon, D. Vogt-Lee, C. Vuillot, J. Weaver, R. Wieczorek, J. A. Wildstrom, R. Wille, E. Winston, J. J. Woehr, S. Woerner, R. Woo, C. J. Wood, R. Wood, S. Wood, J. Wootton, D. Yeralin, J. Yu. L. Zdanski, Zoufalc, anedumla,

- azulehner, bcamorrison, brandhsn, dennis-liu 1, drholmie, el-frocampeador, fanizzamarco, gruu, kanejess, klinvill, lerongil, ma5x, merav aharoni, mrossinek, ordmoj, strickroman, tigerjack, yang.luh, and yotamvakninibm, "Qiskit: An open-source framework for quantum computing," (2019).

- [6] A. Kissinger and A. M. van de Griend, "Cnot circuit extraction for topologically-constrained quantum memories," ArXiv:1904.00633.

- [7] M. Mosca, M. Roetteler, and P. Selinger, Dagstuhl Reports 8, 112 (2019).

- [8] V. Shende, A. Prasad, I. Markov, and J. Hayes, IEEE Trans. on CAD, 710 (2003).

- [9] J. Byrka, F. Grandoni, T. Rothvoß, and L. Sanita, Proc. of STOC, 583 (2010).

- [10] G. Robins and A. Zelikovsky, 7th Annual ACM-SIAM Symposium on Discrete Algorithms (2000).

- [11] S. Wang, Proc. International Workshop on Graphtheoretic Concepts in Computer Science, 387 (1985).

- [12] F. Hwang and K. Richards, Networks 22, 55 (1992).

- [13] International Conference on Reversible Computation, Lecture Notes in Computer Science 8507, 149 (2014).

- [14] G. Li, Y. Ding, and Y. Xie, "Tackling the qubit mapping problem for nisq-era quantum devices," (2018), arXiv:1809.02573 [cs.ET].

- [15] P. Murali, J. M. Baker, A. Javadi-Abhari, F. T. Chong, and M. Martonosi, in *Proceedings of the Twenty-Fourth Interna*tional Conference on Architectural Support for Programming Languages and Operating Systems, ASPLOS 19 (Association for Computing Machinery, New York, NY, USA, 2019) p. 10151029.

- [16] W. Finigan, M. Cubeddu, T. Lively, J. Flick, and P. Narang, "Qubit allocation for noisy intermediate-scale quantum computers," (2018), arXiv:1810.08291 [quant-ph].

- [17] Y. Nam, N. J. Ross, Y. Su, A. M. Childs, and D. Maslov, npj Quantum Information 4, 23 (2018).

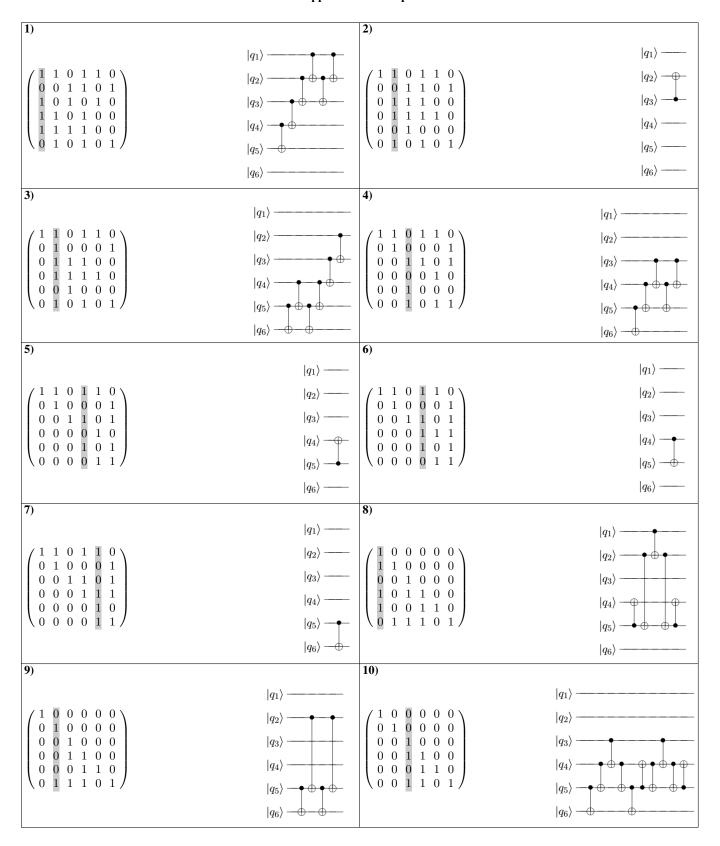

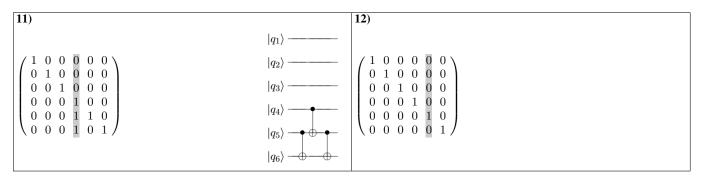

# Appendix A: Example

FIG. 15: Worked through example of circuit synthesis producing the linear transformation given Fig. 3 (a) on connectivity given in Fig. 3 (b). Fully synthesized circuit can be produced by putting together the gates from steps 8-11 and switching the controls and targets, then putting together the gates from steps 1-7 and reversing them, leaving the controls and targets as shown.