# **Atomic-scale Control of Tunnel Coupling**

Xiqiao Wang<sup>1,2,3</sup> #, Jonathan Wyrick<sup>1</sup> #, Ranjit V. Kashid<sup>1</sup>, Pradeep Namboodiri<sup>1</sup>, Scott W. Schmucker<sup>3</sup>, Andrew Murphy<sup>1</sup> ^, M. D. Stewart, Jr.<sup>1</sup>, Neil Zimmerman<sup>1</sup>, and Richard M. Silver<sup>1\*</sup>

Atomically precise silicon-phosphorus (Si:P) quantum systems are actively being pursued to realize universal quantum computation<sup>1</sup> and analog quantum simulation.<sup>2</sup> Atomically precise control of the tunneling coupling strength is critical to spin-exchange operations in tunnel-coupled quantum dots and spin-selective tunneling for initialization and read-out. <sup>3</sup>, <sup>4,5</sup> It was shown by Pok <sup>6</sup> and Fuhrer *et al.*<sup>7</sup> that engineering the nanogap geometry, can affect the tunnel barriers and the tunnel rates in STM-patterned devices: even a ~1 nm difference in the tunnel gap distance can drastically change the tunnel coupling and transport properties in atomically precise Si:P devices. <sup>8</sup> However, critical challenges in atomically precise fabrication have meant systematic, atomic scale control of the tunneling coupling has not been demonstrated. Here using a room-temperature grown locking layer and precise control over the atomic-scale fabrication process, we demonstrate atomic-scale control of the tunnel coupling in atomically precise single electron transistors (SETs). Using the naturally occurring Si (100) 2×1 surface reconstruction lattice as an atomically-precise ruler, we systematically vary the number of lattice counts within the tunnel junction gaps and demonstrate exponential scaling of the tunneling resistance at the atomic limit. We

<sup>&</sup>lt;sup>1</sup> National Institute of Standards and Technology, 100 Bureau Dr., Gaithersburg, Maryland 20899, USA

<sup>&</sup>lt;sup>2</sup> Chemical Physics Program, University of Maryland, College Park, Maryland 20742, USA

<sup>&</sup>lt;sup>3</sup> Joint Quantum Institute, University of Maryland, College Park, Maryland 20742, USA

<sup>#</sup> These authors contributed equally to this work

<sup>&</sup>lt;sup>^</sup>Current address: Johns Hopkins University Applied Physics Laboratory, Laurel, Maryland 20723, USA

characterize the tunnel coupling asymmetry in a pair of nominally identical tunnel gaps and show a resistance difference of four that corresponds to half a dimer row difference in the effective tunnel gap - the intrinsic limit of hydrogen lithography precision on Si (100) 2×1 surfaces. Our results demonstrate the key capability to do atom-scale design and engineering of the tunnel coupling.

In this study, we overcome previous challenges by uniquely combining atomically abrupt hydrogen lithography <sup>9, 10</sup> with recent progress in low-temperature epitaxial overgrowth using a locking-layer technique <sup>11, 12, 13</sup> and silicide electrical contact formation <sup>14</sup> to substantially reduce unintentional dopant movement. These advances have allowed us to demonstrate the exponential scaling of the tunneling resistance on the tunnel gap distance at the atomic limit in a systematic and reproducible manner. We define the tunnel gaps with atomically abrupt edges using ultra-clean hydrogen lithography while utilizing the Si (100) surface reconstruction lattice to quantify the tunnel gap distances with atomic accuracy. We suppress unintential dopant movement at the atomic scale using an optimized, room-temperature grown locking layer, which not only locks the dopant position within lithographically defined regions during encapculation overgrowth but also improves device reproducibility by minimizing the impact of overgrowth temperature variations on dopant confinement profiles. <sup>11</sup> Furthermore, our recent development of a high-yield, low-temperature method for forming ohmic contact to burried atomic devices enables robust electrical characteriation of STM-patterned devices with minimum thermal impact on dopant confinement.<sup>14</sup> With improved capabilities to define and maintain atomically abrupt dopant confinement in silicon, we fabricated a series of STM-patterned Si:P single electron transistors (SETs), where we systematically vary the tunnel junction gap distance with atomic precision, and have used them to demonstrate and explore atomic-scale control of the tunnel

coupling. Instead of geometrically simpler single tunnel junctions, we chose SETs in this study because observation of the Coulomb blockade signature is a direct indication that conductance is through the STM-patterned tunnel junctions.

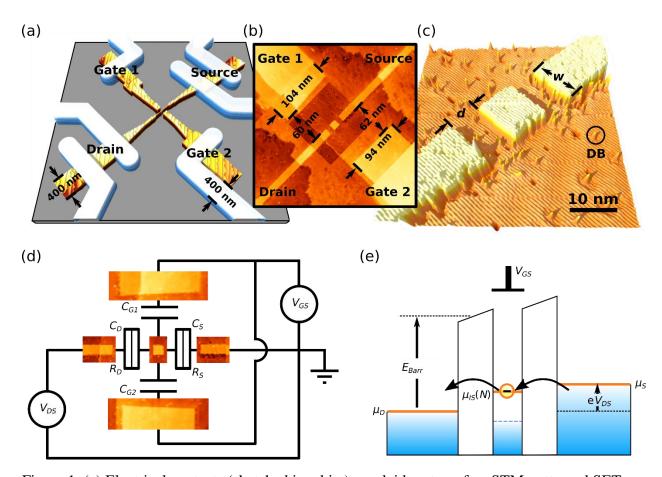

Figure 1. (a) Electrical contacts (sketched in white) overlaid on top of an STM-patterned SET device. (b) STM image of the central device region of a typical SET device acquired immediately following hydrogen lithography. The bright areas are STM-patterns where the hydrogen-resist has been removed, exposing the chemically reactive dangling bonds. The central device region shows a central island that is tunnel coupled with source and drain leads and capacitively coupled to two in-plane gates. Gate 2 is patterned with a deliberate shift towards the source electrode to allow tuning the tunnel coupling symmetry. A high-resolution STM image at the center region is overlaid on a large-scale lower-resolution STM image. (c) Atomic resolution STM image of an SET pattern (SET-C in Figure 2) where the tunnel gaps are defined with atomic precision. The imaged rows running from upper left to lower right are  $2 \times 1$  surface reconstruction dimer rows on the Si (100) surface. The junction gap distance, d, and junction width, w, are marked in the image. The circle marks the image of a single dangling bond (DB).

The STM image is taken at -2 V sample bias and 0.1 nA setpoint current. (d) An equivalent circuit diagram for the SET, where tunnel junctions are treated as a tunneling resistance and capacitance connected in parallel and the combined coupling of the two gates to the SET island is treated as a capacitor. (e) The energy diagram of an SET, where  $\mu_S$  and  $\mu_D$  are the chemical potentials of the source and drain leads respectively;  $\mu_{IS}(N)$  is the chemical potential of the island that is occupied with N excess electrons.  $E_{Barr}$  is the barrier height defined by the energy difference between the electrodes' Fermi levels and the conduction band edge of the substrate. We assume a rectangular barrier shape in this study.

Figure 1 (b) shows an STM image of the atomically precise central region of a typical SET device after hydrogen-lithography, but before phosphine dosing. P dopants only incorporate into the bright regions where the STM tip has removed H surface termination atoms and exposed chemically reactive Si-dangling bonds. The Si (100) 2x1 surface reconstruction features dimer rows of pitch 0.77 nm that can serve as a natural "atomic ruler" allowing us to define the critical dimensions with atomic precision. (Figure 1 (c)) The planar source and drain, island (quantum dot), and gates are saturation-dosed resulting in degenerate dopant densities over three orders of magnitude beyond the Mott metal-insulator transition. <sup>15</sup> The island is capacitively coupled to the two in-plane gates through an effective capacitance  $C_G$  and to the source (drain) electrodes through tunnel barriers represented by a tunneling resistance  $R_S(R_D)$  and a capacitance  $C_S(C_D)$ , where each resistance is coupled in parallel with its respective capacitance (Figure 1 (d)). The gate voltages applied to both gates tune the local electrochemical potential of the island and modulate the source-drain current flowing through the central island. Single electrons tunnel sequentially through both barriers due to the electron addition energy (charging effect) on the island.<sup>16</sup> (Figure 1 (e))

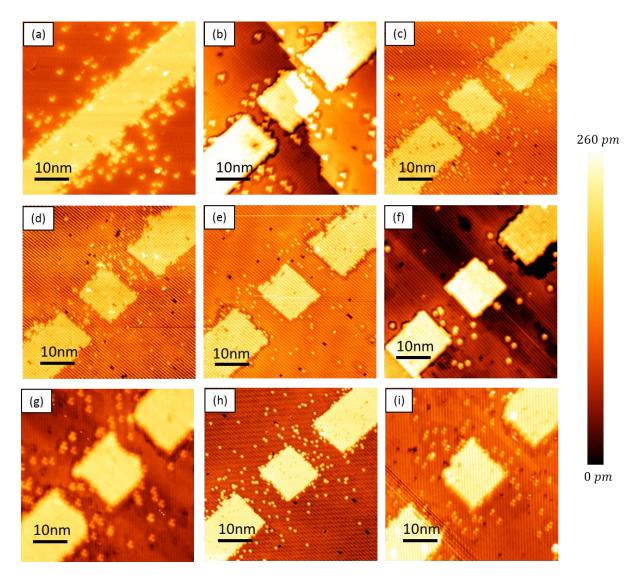

Figure 2. High-resolution STM topography images of the hydrogen-lithography patterns of the wire and SET devices in this study. The devices are named as Wire-A, and SET-B to SET-I according to the figure labels. The drain/source electrodes are oriented in the [110] lattice direction for all cases except for SET-G and SET-I whose drain/source electrodes are oriented in the [100] lattice direction (45° to the [110] direction). Different STM tips/tip conditions are used for the STM images under imaging conditions: -2 V sample bias and 0.1 or 0.05 nA setpoint current.

| Device | Gap distance d (dimer rows) | Lead/island<br>width w<br>(dimer rows) | Island length<br>(dimer rows) | # of squares<br>in leads | $R_{ m S} + R_{ m D} \ (M\Omega)$ |

|--------|-----------------------------|----------------------------------------|-------------------------------|--------------------------|-----------------------------------|

| Wire-A | 0                           | 15.5±1.4                               | N/A                           | 57±4                     | N/A                               |

| SET-B  | 7.4±0.6                     | 15.3±0.6                               | 15.2±0.8                      | 74±6                     | 0.011±0.009                       |

| SET-C  | 9.5±0.7                     | 15.7±0.7                               | 13.1±0.6                      | 56±4                     | 0.113±0.061                       |

| SET-D | 11.1±0.7 | 15.0±0.8 | 14.3±0.6 | 52±4 | 0.340±0.101 |

|-------|----------|----------|----------|------|-------------|

| SET-E | 11.7±0.4 | 17.5±1.0 | 14.9±0.5 | 56±4 | 2.06±0.69   |

| SET-F | 11.8±0.6 | 15.2±0.4 | 15.3±0.4 | 62±5 | 2.49±0.63   |

| SET-G | 12.2±1.4 | 18.8±1.2 | 17.0±1.5 | 49±4 | 5.55±2.91   |

| SET-H | 13.5±0.6 | 15.1±0.3 | 15.4±0.7 | 52±4 | 127±59      |

| SET-I | 16.2±0.6 | 17.6±0.7 | 16.3±0.7 | 48±4 | 764±250     |

Table 1. Critical dimensions of the hydrogen lithography patterns from the high-resolution STM images (shown in Figure 2), where STM image-broadening artifacts have been corrected. The total pattern areas (in units of squares, or the length-width aspect ratio of the STM-patterned leads) from the source and drain leads between the two inner contact probes (see Figure 1 (a)) are also given. The uncertainties in the number of squares is dominated by the uncertainty in the e-beam alignment between the electrical contacts and the STM-patterned contact pads. The rightmost column of the table lists the measured total junction resistances  $(R_S + R_D)$ , where corrections have been taken to eliminate contributions from the source and drain lead sheet resistance. The  $R_S + R_D$  for SET-B represents an ohmic resistance where the uncertainty is dominated by uncertainty in estimating the number of squares in the source/drain leads. The  $R_S + R_D$  for SET-C to SET-I represents tunneling resistances where the error bars include contributions from both the variation (one standard deviation) in the Coulomb oscillation peak height over the corresponding gating range (-200 mV to 200 mV, see Figure 3 (b)) from multiple gate sweeps and the uncertainty in the subtracted source and drain leads resistance. The uncertainty in the reported dimensions and tunneling resistance values are given as one standard deviation in the distribution of measurement samples.

Figure 2 shows a series of STM images acquired following hydrogen-lithography with surface reconstruction dimer rows clearly visible. Although not all device drain/source electrodes are aligned to the [110] lattice direction, we observe optimal atomic precision lithography by orienting the device in the [110] lattice direction and aligning the geometries of the critical device region (island and tunnel junctions) with the underlying surface reconstructed lattice. For SET-G and SET-I whose tunnel gaps are in the [100] direction, we have corrected for the 45° angle relative to the [110] direction when counting the number of dimer rows in their junction gaps. While attempting to keep lead width and island size identical, we systematically increase the number of dimer row counts within the tunnel junction gap starting from a continuous wire with zero gaps up to SET tunnel gap distances of ~16.2 dimer rows, covering a

large range of SET device operation characteristics with respect to tunnel junctions used in QI applications. Because isolated single dangling bonds do not allow dopants to incorporate, we disregard them in quantifying the device geometry. The critical dimensions after STM-imaging correction are summarized in Table 1 for all devices in this study (See Methods for details).

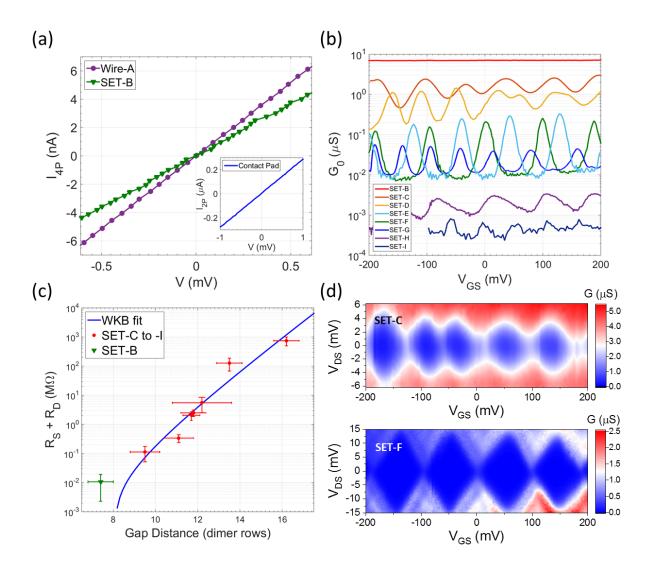

Figure 3. Electrical characterization of the set of devices using a cryostat with a base-temperature of 4 K. (a) Four-point  $I_{DS} - V_{DS}$  measurement of Wire-A and SET-B while keeping the gates grounded. Inset: Representative 2-point I-V characteristics (3.5  $k\Omega$ ) of a device contact pad. (b)

Differential conductance at zero drain-source bias ( $G_0$ ) of the set of SET devices that are measured at T = 4 K. For SET-B to SET-G,  $G_0$  is measured using 0.1 mV AC excitation at 11 Hz. For SET-H and SET-I,  $G_0$  is numerically estimated from the measured DC charge stability diagrams. From top to bottom: SET-B (red) to SET-I (dark blue). The difference in the oscillation period in gate voltage is due to the variations in gate designs that alter the gate capacitance. (c) The measured total tunneling resistance values  $R_S + R_D$  as a function of the lithographically-defined tunnel gap distances. The WKB-fitting is based on the tunneling resistance values from SET-C to SET-I, where the lateral electrical seam width of the electrodes and the rectangular barrier height are taken as free fitting parameters. (d) The measured differential conductance  $dI_{DS}/dV_{DS}$  (on a color linear scale) charge stability diagram of SET-C (upper panel) and SET-F (lower panel) at T = 4 K.

In Figure 3 (a), the I-V characteristics of Wire-A exhibit Ohmic behavior with a 4-point resistance of 96.8  $k\Omega$ . Considering the actual STM-patterned wire geometry (approximately  $57 \pm 4$  squares between the e-beam patterned voltage contact probes, see Figure 2(a)), this corresponds to a sheet resistance of  $1.70 \pm 0.15 \ k\Omega$  in the STM-patterned electrodes, in excellent agreement with previous results on metallically doped Si:P delta layers. The Given the ultrahigh carrier density and small Thomas Fermi screening length in this saturation-doped Si:P system and the relatively large island size of the SETs, we treat the energy spectra in the islands and source and drain leads as continuous ( $\Delta E \ll k_B T$ , where  $\Delta E$  is the energy level separation in the island and source and drain reservoirs) and adopt a metallic description of SET transport. The tunneling rates,  $\Gamma_{S,D}$ , and the tunneling resistances,  $R_{S,D} = \hbar/(2\pi e^2|A|^2D_iD_f)$ , across the source and drain tunnel barriers can be described using Fermi's golden rule, where  $\Delta E$  is the tunneling matrix element,  $\Delta E$  is the initial and final density of states,  $\Delta E$  is the reduced Plank's constant, and  $\Delta E$  is the charge of an electron.

In the following, we show that the total tunneling resistance  $R_S + R_D$  of an SET can be extracted by measuring, at zero drain-source DC-bias, the peak amplitudes of the differential conductance Coulomb oscillations, as shown in Figure 3 (b). At  $V_{DS} = 0$  V, the differential

conductance Coulomb blockade oscillations reach peaks at  $V_{GS} = V_{GS}^{peak} = \left(N + \frac{1}{2}\right)\frac{e}{c_G}$ , where N is an integer and  $\left(N + \frac{1}{2}\right)e$  represents the effective gating charge when the island Fermi level  $\mu_{IS}(N)$  aligns with  $\mu_S$  and  $\mu_D$ . At low temperatures and in the metallic regime,  $\Delta E \ll k_B T \ll E_C$ , where  $E_C = e^2/C_\Sigma$  is the charging energy, and  $C_\Sigma = C_S + C_D + C_G$  is the total capacitance (see Table S1 in the supplementary information), and assuming energy independent tunnel rates and density of states in a linear response regime, Beenakker and co-workers  $^{20,21}$  have shown that the peak amplitude of the zero-bias differential conductance oscillations in an SET reduces to the following temperature independent expression for arbitrary  $R_S$  and  $R_D$  values,

$$\frac{dI_{DS}}{dV_{DS}}\Big|_{V_{CS}^{peak}} = \frac{e^2\rho}{2} \frac{\Gamma_S \Gamma_D}{\Gamma_S + \Gamma_D} = \frac{1}{2} \frac{G_S G_D}{G_S + G_D} = \frac{1}{2(R_S + R_D)}$$

## Equation 1

where  $G_S$  and  $G_D$  are conductances through the source and the drain tunnel barriers,  $\rho$  is the density of state in the metallic island, and the density of states in the leads is embedded in the tunneling rates.

In Figure 3 (b) we observe Coulomb blockade oscillations in all SETs except SET-B. The small gap distance ( $\sim$ 7.4 dimer rows  $\approx$  5.7 nm) in SET-B is comparable to twice the Bohr radius,  $r\sim$ 2.5 nm, of an isolated P atom in bulk Si,<sup>22</sup> indicating significant wavefunction overlap within the gap regions between the island and the source/drain reservoir. Given that SET-B does not exhibit single electron tunneling behavior (Coulomb oscillations), we estimate the resistance at the junction gaps in this device using 4-point I-V measurement. As shown in Figure 3 (a), SET-B has a linear I-V behavior with the 4-point resistance of 136.7  $k\Omega$ . Subtracting the

resistance contribution from the source/drain leads ( $\sim$ 74 squares) using the estimated sheet resistance ( $\sim$ 1.7  $k\Omega$ ) from Wire-A, we obtain a junction resistance value of  $\sim$ 5.5  $\pm$  4.5  $k\Omega$  per junction in SET-B, which does indeed fall below the resistance quantum ( $\sim$ 26  $k\Omega$ ), and explains the absence of Coulomb blockade behavior. We emphasize that, due to the absence of the Coulomb blockade effect, the estimated resistance at the junctions in SET-B is an ohmic resistance, which should not be confused with the tunneling resistance.

For the rest of the SETs, we extract the total tunneling resistance,  $R_S + R_D$ , from the Coulomb oscillation peak heights following Equation 1. Figure 3 (c) summarizes the measured junction resistance values (after sheet resistance correction from the source and drain leads) as a function of the averaged gap distances. The tunneling resistance follows a clear exponential relationship with the gap distances. It is notable that a change of only nine dimer rows gives rise to over four orders of magnitude change in the junction resistance. Increasing the gap distance over a small range (from ~7 dimer rows in the gap to ~12) dramatically changes the SET operation from a linear conductance regime (no sign of Coulomb oscillations at ~7 dimer rows separation in SET-B) to a strong tunnel coupling regime (at ~9.5 dimer rows separation in SET-C) to a weak tunnel coupling regime (at ~12 dimer rows separation in SET-F). The relatively strong tunnel coupling in SET-C (see Figure 3(d) upper panel) blurs the charge quantization on the island and introduces finite conductance within the Coulomb diamonds through higher order tunneling processes (co-tunneling).<sup>23</sup> In the weak tunnel coupling regime in SET-F (see Figure 3(d) lower panel), the Coulomb blockade diamonds become very well established. Tuning the tunnel coupling between strong and weak coupling regimes in atomic devices is an essential capability: e.g. for simulating non-local coupling effects in frustrated systems. <sup>24</sup>

It has been found essential for capacitance modeling (See Table S1 in supplementary information) to add a lateral electrical seam <sup>25</sup> and a vertical electrical thickness <sup>26</sup> to the STMpatterned hydrogen-lithography geometry (Figure 2) to account for the Bohr radius and yield the actual "electrical geometry" of the device. We fit the total tunneling resistance  $(R_S + R_D)$  from SET-B to SET-H as a function of the tunnel gap distance by simulating a single tunnel junction's tunneling resistance (multiplied by two to account for the presence of two junctions) using the WKB method assuming a rectangular barrier shape. <sup>27</sup> (See supplementary information for detailed WKB formulation.) Due to the linear dependence of the WKB tunneling resistance on the tunnel junction cross-sectional area, we ignore the small variations in the STM-patterned junction width, w, (see column 3 in Table 1) and adopt an averaged value of w = 12 nm in the WKB simulation. We account for the "electrical geometry" of the devices by assuming an electrical thickness of z = 2 nm, <sup>26</sup> while treating the lateral electrical seam width, s, and the rectangular barrier height,  $E_{barr}$ , as fitting parameters. We obtain  $100 \pm 50 \ meV$  as the best-fit barrier height (uncertainty represents two  $\sigma$ ), which is in good agreement with the theoretically predicted range of Fermi levels below the Si conduction band edge in highly  $\delta$ -doped Si:P systems, ~80 meV to ~130 meV, from tight-binding <sup>26</sup> and density functional theory <sup>22</sup> calculations. A similar barrier height value (~80 meV) has also been experimentally determined in a Fowler-Nordheim tunneling regime by Fuhrer's group using a similar STM-patterned Si:P device. We obtain  $3.1 \pm 0.4$  nm as the best-fit seam width (uncertainty represents two  $\sigma$ ), which is in good agreement with the Bohr radius of isolated single phosphorus donors in bulk silicon  $(r\sim 2.5 nm)$ . <sup>22</sup> Using the best-fit seam width from the WKB simulation, we also find good agreement between the experimental and simulated capacitance values from the SETs. (see Table S1 in the supplementary information)

Figure 3 (c) is a key result of this study, clearly demonstrating an exponential scaling of tunneling resistance to the atomic limit. In addition, the data suggests that to obtain tunneling resistance values comparable to those reported in the literature from similar STM-patterned tunnel junctions, <sup>6, 28, 29</sup> we need to pattern our tunnel gaps with smaller gap distances in general. This further emphasizes the improved dopant confinement in the our STM-patterned devices. We highlight that the series of devices shown in Figure 2 were fabricated in series from two different UHV-STM systems. This is important as it further demonstrates atom scale control across similar but non-identical hardware platforms using the same nominal methods and processes.

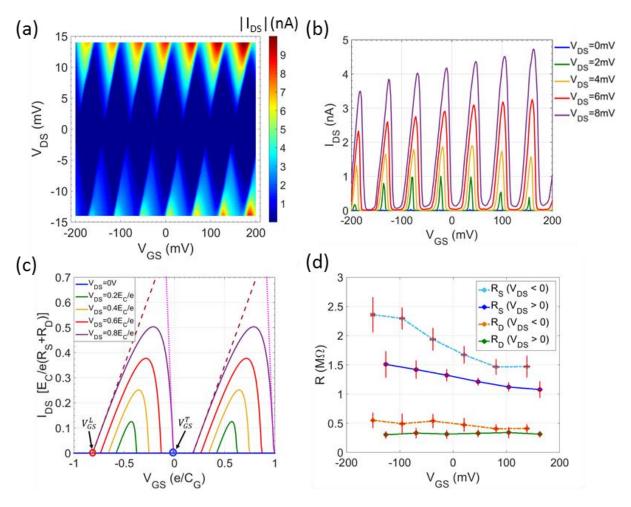

Figure 4. DC measurement of SET-G using a dilution refrigerator with a base-temperature of ~10 mK. (a) The DC-measured charge stability diagram, where the drain-source current  $I_{DS}$  is plotted as the absolute values for clarity. (b) The measured Coulomb blockade oscillations at selected drain-source biases. (c) Simulated Coulomb blockade oscillations at positive drain-source bias, assuming asymmetric junction resistances  $R_S = 9R_D$ . At  $V_{DS} = 0.8E_C/e$ , the dotted and dashed lines plot the simulated tunneling current through the rate-limiting source and drain tunnel junctions at the leading and trailing edges of the Coulomb oscillation peaks respectively, while ignoring the other junction in series. (d) The extracted junction resistances from Coulomb oscillation peaks along the gate voltage axis. The horizontal and vertical uncertainties at the data points are calculated by averaging the oscillation peak positions and the tunneling resistances at different drain-source biases.

Having demonstrated atom scale control of the tunnel coupling, we now take an additional step to characterize the junction resistance difference in a pair of nominally identical tunnel junctions in SET-G, where both the tunnel gaps have irregular edges and the tunnel gap distances are less

well-defined when compared with the tunnel gaps in the other SETs, representing a lower bound of controllability among the SET devices in this study. We present the measured charge stability diagram and finite bias Coulomb oscillations in Figure 4 (a) and (b). In Figure 4 (b), the Coulomb oscillation peaks are asymmetric across the gate voltage. For positive drain-source bias, at the leading edge of the Coulomb oscillation peak of  $N \leftrightarrow N+1$  transition, the island spends most of the time unoccupied (N). So, the total tunneling rate is limited by tunneling from the source to the island, and thus the total tunneling resistance is dominated by  $R_S$ . The other three cases are analogous. Figure 4 (c) takes  $V_{DS} > 0$  for instance and shows a numerical simulation (at T = 0 K) of  $I_{DS} vs. V_{GS}$  at different drain-source bias. The dashed and dotted lines in Figure 4 (c) illustrate the asymptotic slopes at the leading and trailing edges of the Coulomb oscillation peaks at  $V_{DS} = 0.8E_C/e$ , which also represent the tunneling current through the ratelimiting source and drain tunnel junctions, respectively, while ignoring the other junction in series. At T = 0 K, the source and drain junction resistances can be derived from the right derivative at the leading edge, where  $V_{GS} = V_{GS}^L = \left(N + \frac{1}{2}\right) \frac{e}{c_G} - \frac{c_D}{c_G} V_{DS}$ , and from the left derivative at the trailing edge, where  $V_{GS} = V_{GS}^T = \left(N + \frac{1}{2}\right) \frac{e}{c_G} + \frac{(c_S + c_G)}{c_G} V_{DS}$ , of a Coulomb oscillation peak in  $I_{DS}$ . This is shown in Equation 2 (see supplementary information for mathematical derivations), again, taking positive drain-source biases for example,

$$\left. \frac{\partial_{+} I_{DS}}{\partial V_{GS}} \right|_{V_{GS}^{L}} = \lim_{\Delta V_{GS} \to 0} \frac{I_{DS}(V_{GS}^{L} + \Delta V_{GS}) - I_{DS}(V_{GS}^{L})}{\Delta V_{GS}} = \frac{C_{G}}{R_{S} C_{\Sigma}}$$

$$\left. \frac{\partial_{-}I_{DS}}{\partial V_{GS}} \right|_{V_{GS}^{T}} = \lim_{\Delta V_{GS} \to 0} \frac{I_{DS}(V_{GS}^{T}) - I_{DS}(V_{GS}^{T} - \Delta V_{GS})}{\Delta V_{GS}} = -\frac{C_{G}}{R_{D}C_{\Sigma}}$$

#### Equations 2.

See Table S1 in the supplementary information for the gate and total capacitances,  $C_G$  and  $C_\Sigma$ . To estimate the drain and source tunneling resistances from the Coulomb oscillation peaks that are measured at finite temperatures (Figure 4 (b)), we approximate the asymptotic slopes at the leading and trailing edges by fitting the leading and trailing slopes of the measured Coulomb oscillation peaks and average over a range of  $V_{DS}$  bias. (see Figure 4 (d)) We find a factor of approximately four difference in the source and drain tunneling resistances. Possible contributions to this resistance difference include atomic-scale imperfections in the hydrogen lithography of tunnel gaps, the randomness in the dopant incorporation sites within the patterned regions, and unintentional, albeit greatly suppressed, dopant movement at the atomic-scale during encapsulation overgrowth. From the exponential dependence in Figure 3 (c), a factor of four corresponds to an uncertainty in the gap distance of only about half of a dimer row pitch distance, which represents the ultimate spatial resolution (a single atomic site on the Si (100) 2×1 reconstruction surface) and the intrinsic precision limit for the atomically precise hydrogen-lithography.

In summary, we have reported atomic scale control over the tunnel coupling in STM-patterned Si:P single electron transistors. By using the natural surface reconstruction lattice as an atomic ruler, we systematically varied the tunneling gap distances with atomic precision and demonstrated exponential scaling of tunneling resistance to the atomic limit. We emphasize that, critical fabrication steps, such as a defect- and contaminant-free silicon substrate and hydrogen resist formation, atomically abrupt and ultra-clean hydrogen lithography, with dopant incorporation, epitaxial overgrowth, and electrical contact formation that suppress dopant movement at the atomic scale, are all necessary to realize atomic precision devices. This study

represents an important step towards fabricating key components needed for high-fidelity silicon quantum circuitry that demands unprecedented precision and reproducibility.

### **Methods**

The Si:P single electron transistors (SETs) are fabricated on a hydrogen-terminated Si (100) 2×1 substrate (3  $\times$  10<sup>15</sup>/cm<sup>3</sup> boron doped) in an ultrahigh vacuum (UHV) environment with a base pressure below  $4 \times 10^{-9}$  Pascal (3 × 10<sup>-11</sup> Torr). Detailed sample preparation, UHV sample cleaning, hydrogen-resist formation, and STM tip fabrication and cleaning procedures have been published elsewhere. <sup>10, 30, 31</sup> A low 1×10<sup>-11</sup> Torr UHV environment and contamination-free hydrogen-terminated Si surfaces and STM tips are critical to achieving high-stability imaging and hydrogen lithography operation. The device geometry is defined by selectively removing hydrogen resist atoms using an STM tip in the low-bias ( $3\sim5~V$ ) and high-current ( $15\sim50~\text{nA}$ ) regime where the small tip-sample separation allows for a spatially focused tunneling electron beam under the atomic-scale tip apex, creating hydrogen lithographic patterns with atomically abrupt edges. For complete hydrogen desorption within the patterned regions, the typical tip scan velocity and scan-line spacing are 100 nm/sec and 0.5 nm/line respectively. We then saturationdose the patterned device regions with PH<sub>3</sub> followed by a rapid thermal anneal at 350 °C for 1 min to incorporate the P dopant atoms into the Si surface lattice sites while preserving the hydrogen resist to confine dopants within the patterned regions. The device is then epitaxially encapsulated with intrinsic Si by using an optimized locking layer process to suppress dopant movement at the atomic-scale during epitaxial overgrowth. 11, 13 The sample is then removed from the UHV system and Ohmic-contacted with e-beam defined palladium silicide contacts. 14 Low-temperature transport measurements are performed using either a closed-cycle cryostat at a base temperature of 4 K or a dilution refrigerator at a base temperature of ~10 mK. For SET-B to SET-G, the zero-DC bias differential conductance ( $G_0$ ) are measured using 0.1 mV AC excitation at 11 Hz. For SET-H and SET-I,  $G_0$  is numerically estimated from the measured DC charge stability diagrams. The gate leakage currents are on the order of ~10 pA or less within the gating range used in this study.

We estimate the critical dimensions of the STM-patterned tunnel junctions in a SET from the STM topography images in Figure 2 of the main text, where the gap-distance, d, is the average across the full junction width, w, using both junctions. The junction width is the average over the island and the first 15 nm of the source and drain leads near the island. The hydrogen lithography and STM-imaging are carried out using different tips and/or under different tip conditions. To eliminate the STM image-broadening due to the convolution between the wavefunctions of the tip apex and Si danging bonds and extract the boundary of the hydrogen-depassivated surface lattice sites, we estimate the image-brodening,  $\Delta b$ , from the difference between the imaged single dangling bond size, b, (full-width at half maximum (FWHM)) and the size of a single

dangling bond lattice site,  $b_0$ , where we have assumed  $b_0$  equals half a dimer row pitch. (see Figure 1 (c) in the main text). The image-broadening,  $\Delta b = b - b_0$ , is then used to correct the critical dimensions that are read out from the half-maximum height positions in the STM topography images.

The theoretical analysis of the transport through SETs is based on an equivalent circuit model (see Figure 1 (d)) under a constant interaction approximation. The analytical expressions regarding the equilibrium drain-source conductance in the main text are derived using the standard Orthodox theory under a two-state approximation. <sup>18, 32</sup>

# **Supplementary Information**

### Modeling the Tunnel Barriers Using the WKB Method

We fit the measured tunneling resistance  $R_S + R_D$  as a function of the STM-patterned tunnel gap distance, d, using the well-known Simmons' WKB formulation in the low-bias (linear response) regime. <sup>27, 33</sup> We adopt an ideal rectangular barrier shape ignoring the image force correction to the barrier potential when an electron approaches the dielectric barrier interface. The barrier height,  $E_{barr}$ , is defined as the energy difference between the electrode reservoirs' Fermi level and the conduction band minimum. We expect exponential dependence of the tunnel conductance on both the barrier height and barrier width, whereas a linear dependence on the tunneling cross-section area is expected. Therefore, the slight width variation among the fabricated tunneling junctions is assumed to have minor effects on the tunnel conductance. We assume a uniform electrical thickness z = 2 nm for the STM-patterned device components. To account for the finite electron density extension beyond the hydrogen-lithography patterns in the lateral directions, we add a uniform lateral seam, s, to the device pattern. We adopt an averaged width of w = 12 nm as the STM-patterned junction width. Therefore, the electrical junction width and the electrical junction gap distance are expressed as (w + 2s) and (d - 2s)respectively. (w + 2s)z represents the electrical tunnel junction cross-sectional area. The lateral seam width, s, and the rectangular tunnel barrier height,  $E_{barr}$ , are treated as fitting parameters. The WKB tunneling resistance,  $R_T$ , in the low-bias regime is expressed in Equation S1.<sup>27, 33</sup>

$$\frac{1}{R_T} = \frac{[(w+2s)z]\sqrt{2m^*E_{barr}}}{(d-2s)} \left(\frac{e}{h}\right)^2 \exp\left[-\frac{4\pi(d-2s)}{h}\sqrt{2m^*E_{barr}}\right]$$

Equation S1.

Where h is Plank's constant, e is the charge of a single electron, and  $m^*$  is the effective mass of the conducting electrons. Conductivity in the degenerately  $\delta$ -doped Si:P electrodes is assumed to be dominated by the lowest energy sub-bands, with effective mass  $m^* = 0.21 m_e$  as measured by Miwa  $et\ al.$  using direct spectroscopic measurement in blanket  $\delta$ -doped Si:P layers,  $^{34}$  where  $m_e$

is the free electron mass. We point out that, at a given barrier height  $E_{barr}$ , the dependence of WKB tunneling resistance,  $R_T$ , on the gap distance, d, deviates from an ideal exponential behavior, especially at small gap distances, due to the pre-factor in front of the exponential term in Equation S1.

# Comparison between the Measured and Simulated Capacitances in STM-patterned SET Devices

Capacitance modeling of STM-patterned Si:P devices has demonstrated success in accurately predicting the device electrostatics down to the atomic scale. Table S1 compares the experimentally observed SET capacitances and the simulated capacitances, where the device components are treated as metallic sheets in the shape of the "electrical geometry" of the device. A uniform electrical thickness of z=2 nm in the z-direction is assumed for both the Simulation 1 and Simulation 2. No lateral electrical seam is added to the hydrogen lithography pattern in Simulation 1. The simulated capacitances from Simulation 1 agree poorly with the measured capacitances. In Simulation 2, a lateral electrical seam width of 3.1 nm from the WKB tunneling resistance fit is added to the STM-patterned device geometry, which significantly improves the agreement between the simulated and measured capacitances.

|                                       | $E_{\rm C}$ (meV) | $C_{\Sigma}$ (aF) | $C_{G}$ (aF)  | $C_{\rm S}$ (aF) | $C_{\mathrm{D}}$ (aF) |

|---------------------------------------|-------------------|-------------------|---------------|------------------|-----------------------|

| Experiment                            | $11.9 \pm 0.3$    | $13.5 \pm 0.3$    | $2.8 \pm 0.2$ | $5.0 \pm 0.3$    | 5.7 ± 0.3             |

| Simulation 1 (no seam)                | 19.5              | 8.2               | 2.6           | 2.8              | 2.8                   |

| Simulation 2<br>(with 3.1 nm<br>seam) | 10.5              | 15.3              | 3.2           | 6.0              | 6.1                   |

Table S1. The experimental and simulated charging energy and capacitances of SET-G. The experimental capacitances are extracted using the height and width of the measured Coulomb diamonds (Figure 4 (a)) as well as the slopes of the positive and negative diamond edges. <sup>16</sup> The uncertainties result from the experimental determination of the Coulomb diamond dimensions from the measured charge stability diagrams while extracting the experimental capacitances. The capacitance simulation is carried out using a finite-element 3D Poisson solver, FastCap. <sup>36,37</sup>

## **Quantifying Individual Junction Resistances in a Metallic SET**

Following the well-established Orthodox theory for a metallic SET,  $^{19}$  the tunneling resistance across the individual tunnel barriers can be extracted from the peak shapes of Coulomb oscillations in  $I_{DS}$ . In this section, we derive the explicit expressions in Equation 2 of the main text using an analytical model that was first proposed by Inokawa and Takahashi.  $^{32}$

The tunneling probability through an SET is determined by the change in the SET's Helmholtz's free energy F = U - W, where U is the total electrostatic energy stored in the system and W is

the work done by voltage sources, due to a single electron tunneling event. Following the constant interaction model in a metallic regime (See Figure 1 (d) in the main text), the change in F when an electron tunnels from the source/drain electrodes to the island and transitions the number of excess electrons on the island from N to N+1 can be expressed as  $\Delta F_{S,D}^{N+1,N} = -\mu_{S,D} + \mu_{IS}(N)$ , where  $\mu_{S,D}$  and  $\mu_{IS}(N)$  are the chemical potential of the source/drain leads and an SET island with N excess electrons.<sup>38</sup>

In the zero-temperature limit, T = 0 K, the tunneling rates can be expressed using Fermi's golden rule.

$$\Gamma_{S,D}^{N+1,N} = \frac{1}{R_{S,D}e^2} (-\Delta F_{S,D}^{N+1,N}) \Theta(\Delta F_{S,D}^{N+1,N})$$

$$\Gamma_{S,D}^{N,N+1} = \frac{1}{R_{S,D}e^2} (-\Delta F_{S,D}^{N,N+1}) \Theta(\Delta F_{S,D}^{N,N+1})$$

Equation S2

Where  $\Theta(x)$  is a unit step function. For simplicity, we have assumed the single electron tunneling events to be elastic without electromagnetic interactions between the tunneling electron and the environmental impedance. <sup>39</sup>

In an equilibrium condition, the stationary occupancy probability, P(N), of the SET island (with N excess electrons) can be derived by requiring dP(N)/dt = 0 in a steady state master equation and obtaining  $P(N)(\Gamma_S^{N+1,N} + \Gamma_D^{N+1,N}) = P(N+1)(\Gamma_S^{N,N+1} + \Gamma_D^{N,N+1})$ . At low-temperatures where  $k_BT \ll E_C$ , only the two most-probable charge states dominate the SET island occupancy at a given bias. Adopting a two-state approximation, P(N) + P(N+1) = 1, an analytical expression of the total drain-source current through the SET can be obtained,

$$\begin{split} I_{DS}(N) &= -eP(N) \; \Gamma_D^{N+1,N} \; + eP(N+1) \Gamma_D^{N,N+1} \\ &= e \frac{\Gamma_D^{N,N+1} \Gamma_S^{N+1,N} - \Gamma_D^{N+1,N} \Gamma_S^{N,N+1}}{\Gamma_D^{N+1,N} + \Gamma_S^{N+1,N} + \Gamma_D^{N,N+1} + \Gamma_S^{N,N+1}} \end{split}$$

Equation S3

Using the expression of  $\mu_{IS}(N)$  from the constant interaction model,<sup>38</sup> we have,

$$\begin{split} &I_{DS}|_{T=0} \\ &= \frac{1}{C_{\Sigma}} \frac{\left[\frac{e}{2} + (Ne - Q_0) + (C_S + C_G)V_{DS} - C_GV_{GS}\right] \left[\frac{e}{2} + (Ne - Q_0) - C_DV_{DS} - C_GV_{GS}\right]}{R_D \left[\frac{e}{2} + (Ne - Q_0) - C_DV_{DS} - C_GV_{GS}\right] - R_S \left[\frac{e}{2} + (Ne - Q_0) + (C_S + C_G)V_{DS} - C_GV_{GS}\right]} \end{split}$$

Equation S4

where  $Q_0$  ( $|Q_0| \le \frac{e}{2}$ ) represents a fractional electron charge that is present on the island when the voltage electrodes are floating, typically due to background charges from the environment.

Taking  $V_{DS} > 0$  at T = 0 K for instance, the source and drain junction tunneling resistances can be derived from the right derivative at the leading edge, where  $V_{GS} = V_{GS}^L = \left(N + \frac{1}{2}\right)\frac{e}{c_G} - \frac{c_D}{c_G}V_{DS}$ , and from the left derivative at the trailing edge, where  $V_{GS} = V_{GS}^T = \left(N + \frac{1}{2}\right)\frac{e}{c_G} + \frac{(c_S + c_G)}{c_G}V_{DS}$ , of a Coulomb oscillation peak in  $I_{DS}(V_{GS})$ . According to Equation S4 (assuming  $Q_0 = 0$ ), the right derivative at the leading edge, where  $V_{GS} = V_{GS}^L$ , has the following expression,

$$\frac{\partial_{+}I_{DS}}{\partial V_{GS}}\Big|_{V_{GS}^{L}} = \lim_{\Delta V_{GS} \to 0} \frac{I_{DS}(V_{GS}^{L} + \Delta V_{GS}) - I_{DS}(V_{GS}^{L})}{\Delta V_{GS}} \\

= \lim_{\Delta V_{GS} \to 0} \frac{1}{C_{\Sigma}\Delta V_{GS}} \frac{(C_{\Sigma}V_{DS} - C_{G}\Delta V_{GS})(-C_{G}\Delta V_{GS})}{R_{D}(-C_{G}\Delta V_{GS}) - R_{S}(C_{\Sigma}V_{DS} - C_{G}\Delta V_{GS})} = \frac{C_{G}}{R_{S}C_{\Sigma}}$$

Equation S5

Similarly, the left derivative at the trailing edge, where  $V_{GS} = V_{GS}^T$ , has the following expression,

$$\begin{split} \frac{\partial_{-}I_{DS}}{\partial V_{GS}}\Big|_{V_{GS}^{T}} &= \lim_{\Delta V_{GS} \to 0} \frac{I_{DS}(V_{GS}^{T}) - I_{DS}(V_{GS}^{T} - \Delta V_{GS})}{\Delta V_{GS}} \\ &= \lim_{\Delta V_{GS} \to 0} \frac{-1}{C_{\Sigma} \Delta V_{GS}} \frac{(C_{G} \Delta V_{GS})(C_{G} \Delta V_{GS} - C_{\Sigma} V_{DS})}{R_{D}(C_{G} \Delta V_{GS} - C_{\Sigma} V_{DS}) - R_{S}(C_{G} \Delta V_{GS})} = \frac{-C_{G}}{R_{D}C_{\Sigma}} \end{split}$$

Equation S6

To estimate the drain and source tunneling resistances from the Coulomb oscillation peaks that are measured at finite temperatures, we approximate the asymptotic slopes at the leading and trailing edges by fitting the leading and trailing slopes of the measured Coulomb oscillation peaks.

### **Conflicts of Interest**

There are no conflicts of interest to declare.

# Acknowledgements

This work was sponsored by the Innovations in Measurement Science (IMS) program at NIST: Atom-based Devices: single atom transistors to solid state quantum computing. This work is also funded in part by the Department of Energy. We thank Daniel Walkup and John Kramar for valuable comments and discussions. This work was performed in part at the Center for Nanoscale Science and Technology NanoFab at NIST.

### **Author Contributions**

X.W. conceived of the experiment under the guidance of R.M.S. In situ device fabrication was performed by X.W. and J.W. Ex situ sample preparation and electrical contact fabrication was carried out by P.N., S.W.S, M.D.S. Jr, J.W., and X.W. Low-temperature transport measurement was carried out by R.K., A.M, and X.W. Data analysis and calculations were carried out by X.W., J.W., and R.M.S. The manuscript was prepared by X.W., J.W., and R.M.S. with input from all authors.

# References

- 1. Hill CD, Peretz E, Hile SJ, House MG, Fuechsle M, Rogge S, et al. A surface code quantum computer in silicon. *Science Advances* 2015, **1**(9): e1500707.

- 2. Dusko A, Delgado A, Saraiva A, Koiller B. Adequacy of Si:P chains as Fermi–Hubbard simulators. npj Quantum Information 2018, **4**(1).

- 3. Koiller B, Hu X, Das Sarma S. Exchange in silicon-based quantum computer architecture. *Phys Rev Lett* 2002, **88**(2): 027903.

- 4. Wang Y, Tankasala A, Hollenberg LCL, Klimeck G, Simmons MY, Rahman R. Highly tunable exchange in donor qubits in silicon. *npj Quantum Information* 2016, **2**(1).

- 5. Broome MA, Watson TF, Keith D, Gorman SK, House MG, Keizer JG, et al. High-Fidelity Single-Shot Singlet-Triplet Readout of Precision-Placed Donors in Silicon. *Physical Review Letters* 2017, **119**(4): 046802.

- 6. Pok W. Atomically abrupt, highly-doped, coplanar nanogaps in silicon. Ph.D. thesis, University of New South Wales, Sydney, 2011.

- 7. Pascher N, Hennel S, Mueller S, Fuhrer A. Tunnel barrier design in donor nanostructures defined by hydrogen-resist lithography. *New Journal of Physics* 2016, **18**(8).

- 8. Watson TF, Weber B, Miwa JA, Mahapatra S, Heijnen RMP, Simmons MY. Transport in Asymmetrically Coupled Donor-Based Silicon Triple Quantum Dots. *Nano Letters* 2014, **14**(4): 1830-1835.

- 9. Shen TC, Wang C, Abeln GC, Tucker JR, Lyding JW, Avouris P, et al. Atomic-Scale Desorption Through Electronic and Vibrational Excitation Mechanisms. *Science* 1995, **268**(5217): 1590.

- 10. Wyrick J, Wang X, Namboodiri P, Schmucker SW, Kashid RV, Silver RM. Atom-by-Atom Construction of a Cyclic Artificial Molecule in Silicon. *Nano Letters* 2018, **18**(12): 7502-7508.

- 11. Wang X, Hagmann JA, Namboodiri P, Wyrick J, Li K, Murray RE, et al. Quantifying atom-scale dopant movement and electrical activation in Si:P monolayers. *Nanoscale* 2018, **10**(9): 4488-4499.

- 12. Hagmann JA, Wang X, Namboodiri P, Wyrick J, Murray R, Stewart MD, *et al.* High resolution thickness measurements of ultrathin Si:P monolayers using weak localization. *Applied Physics Letters* 2018, **112**(4): 043102.

- 13. Keizer JG, Koelling S, Koenraad PM, Simmons MY. Suppressing Segregation in Highly Phosphorus Doped Silicon Monolayers. *ACS Nano* 2015, **9**(12): 12537-12541.

- 14. Schmucker SW, Namboodiri PN, Kashid R, Wang X, Hu B, Wyrick JE, et al. Low-Resistance, High-Yield Electrical Contacts to Atom Scale Si:P Devices Using Palladium Silicide. *Physical Review Applied* 2019, **11**(3): 034071.

- 15. Weber B, Mahapatra S, Ryu H, Lee S, Fuhrer A, Reusch TCG, et al. Ohm's Law Survives to the Atomic Scale. *Science* 2012, **335**(6064): 64.

- 16. Grabert H, Devoret MH. Single charge tunneling: Coulomb blockade phenomena in nanostructures. Springer; 1992.

- 17. Goh KEJ, Oberbeck L, Simmons MY, Hamilton AR, Butcher MJ. Influence of doping density on electronic transport in degenerate Si:P delta-doped layers. *Physical Review B* 2006, **73**(3): 035401.

- 18. Likharev KK. Single-electron devices and their applications. *Proceedings of the IEEE* 1999, **87**(4): 606-632.

- 19. Wasshuber C. About single-electron devices and circuits. Technische Univ. Wien, 1997.

- 20. Beenakker CWJ. Theory of Coulomb-blockade oscillations in the conductance of a quantum dot. *Physical Review B* 1991, **44**(4): 1646-1656.

- 21. Van Houten H, Beenakker CWJ, Staring AAM. Coulomb-Blockade Oscillations in Semiconductor Nanostructures. In: Grabert H, Devoret MH (eds). *Single Charge Tunneling: Coulomb Blockade Phenomena In Nanostructures*. Springer US: Boston, MA, 1992, pp 167-216.

- 22. Qian G, Chang Y-C, Tucker JR. Theoretical study of phosphorous delta-doped silicon for quantum computing. *Physical Review B* 2005, **71**(4): 045309.

- 23. Lee WCT, Scappucci G, Thompson DL, Simmons MY. Development of a tunable donor quantum dot in silicon. *Applied Physics Letters* 2010, **96**(4): 043116.

- 24. Barthelemy P, Vandersypen LMK. Quantum Dot Systems: a versatile platform for quantum simulations. *Annalen der Physik* 2013, **525**(10-11): 808-826.

- 25. Weber B, Mahapatra S, Watson TF, Simmons MY. Engineering Independent Electrostatic Control of Atomic-Scale (~4 nm) Silicon Double Quantum Dots. *Nano Letters* 2012, **12**(8): 4001-4006.

- 26. Carter DJ, Warschkow O, Marks NA, McKenzie DR. Electronic structure models of phosphorusδ-doped silicon. *Physical Review B* 2009, **79**(3).

- 27. Simmons JG. Generalized Formula for the Electric Tunnel Effect between Similar Electrodes Separated by a Thin Insulating Film. *Journal of Applied Physics* 1963, **34**(6): 1793-1803.

- 28. House MG, Peretz E, Keizer JG, Hile SJ, Simmons MY. Single-charge detection by an atomic precision tunnel junction. *Applied Physics Letters* 2014, **104**(11): 113111.

- 29. Rueß FJ, Pok W, Goh KEJ, Hamilton AR, Simmons MY. Electronic properties of atomically abrupt tunnel junctions in silicon. *Physical Review B* 2007, **75**(12): 121303.

- Wang X, Namboodiri P, Li K, Deng X, Silver R. Spatially resolved scanning tunneling spectroscopy of single-layer steps on Si(100) surfaces. *Physical Review B* 2016, **94**(12): 125306.

- 31. Deng X, Namboodiri P, Li K, Wang X, Stan G, Myers AF, et al. Silicon epitaxy on H-terminated Si (100) surfaces at 250°C. *Applied Surface Science* 2016, **378**: 301-307.

- 32. Inokawa H, Takahashi Y. A compact analytical model for asymmetric single-electron tunneling transistors. *IEEE Transactions on Electron Devices* 2003, **50**(2): 455-461.

- 33. Matthews N, Hagmann MJ, Mayer A. Comment: "Generalized formula for the electric tunnel effect between similar electrodes separated by a thin insulating film" [J. Appl. Phys. 34, 1793 (1963)]. *Journal of Applied Physics* 2018, **123**(13): 136101.

- 34. Miwa JA, Warschkow O, Carter DJ, Marks NA, Mazzola F, Simmons MY, et al. Valley Splitting in a Silicon Quantum Device Platform. *Nano Letters* 2014, **14**(3): 1515-1519.

- 35. Watson TF, Weber B, Miwa JA, Mahapatra S, Heijnen RM, Simmons MY. Transport in asymmetrically coupled donor-based silicon triple quantum dots. *Nano Lett* 2014, **14**(4): 1830-1835.

- 36. Nabors K, White J. FastCap: a multipole accelerated 3-D capacitance extraction program. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* 1991, **10**(11): 1447-1459.

- 37. Certain commercial equipment, instruments, or materials are identified in this paper to foster understanding. Such identification does not imply recommendation or endorsement by the National Institute of Standards and Technology, nor does it imply that the materials or equipment identified are necessarily the best available for the purpose.

- 38. Hanson R, Kouwenhoven LP, Petta JR, Tarucha S, Vandersypen LMK. Spins in few-electron quantum dots. *Reviews of Modern Physics* 2007, **79**(4): 1217-1265.

- 39. Devoret MH, Esteve D, Grabert H, Ingold G, Pothier H, Urbina C. Effect of the electromagnetic environment on the Coulomb blockade in ultrasmall tunnel junctions. *Phys Rev Lett* 1990, **64**(15): 1824-1827.