# Characterising Quantum Devices at Scale with Custom Cryo-CMOS

S. J. Pauka,<sup>1, \*</sup> K. Das,<sup>2, \*</sup> J. M. Hornibrook,<sup>2</sup> G. C. Gardner,<sup>3, 4</sup>

M. J. Manfra,<sup>5,3,4,6</sup> M. C. Cassidy,<sup>2</sup> and D. J. Reilly<sup>1,2,†</sup>

<sup>1</sup>ARC Centre of Excellence for Engineered Quantum Systems,

School of Physics, The University of Sydney, Sydney, NSW 2006, Australia.

<sup>2</sup>Microsoft Quantum Sydney, The University of Sydney, Sydney, NSW 2006, Australia.

<sup>3</sup>Birck Nanotechnology Center, Purdue University, West Lafayette, IN 47907, USA.

<sup>4</sup>Microsoft Quantum Purdue, Purdue University, West Lafayette, IN 47907, USA.

<sup>5</sup>Department of Physics and Astronomy, Purdue University, West Lafayette, IN 47907, USA.

<sup>6</sup>School of Materials Engineering and School of Electrical and Computer Engineering,

Purdue University, West Lafayette, IN 47907, USA.

(Dated: November 5, 2021)

We make use of a custom-designed cryo-CMOS multiplexer (MUX) to enable multiple quantum devices to be characterized in a single cool-down of a dilution refrigerator. Combined with a packaging approach that integrates cryo-CMOS chips and a hot-swappable, parallel device test platform, we describe how this setup takes a standard wiring configuration as input and expands the capability for batch-characterization of quantum devices at milli-Kelvin temperatures and high magnetic fields. The architecture of the cryo-CMOS multiplexer is discussed and performance benchmarked using few-electron quantum dots and Hall mobility-mapping measurements.

#### I. INTRODUCTION

Developing large-scale quantum machines brings new and distinct challenges not apparent in earlydemonstration experiments with single devices or fewqubit systems<sup>1–3</sup>. Although many fundamental scientific barriers stand in the path to scale-up, significant progress is likely if engineering methodologies<sup>4,5</sup> can be leveraged to establish processes that reliably and repeatedly produce devices and subsystems with high-yield and deterministic performance. Key to such approaches is the ability to fabricate and characterize statistically significant numbers of devices, a major challenge when electrical measurements must be performed at milli-Kelvin temperatures in the presence of high magnetic fields.

Standard techniques for electrical test, such as the use of wafer-scale probe-stations, are challenging to implement in the deep-cryogenic environment. These difficulties are not fundamental barriers but rather technical, for instance, the challenge of connecting room temperature electronics to a large number of devices-under-test below 1 K. A brute force approach, in which each device is independently connected to test electronics via its own wiring, becomes problematic for large wire-counts due to the thermal leak of the wiring  $itself^6$ , the footprint of bulky connectors, and the likelihood of failure that stems from using meters of cabling across large temperature gradients. Together these aspects usually lead to device characterization proceeding via serial cool-downs of a dilution refrigerator, with each cycle taking several davs.

Overcoming the challenge of multiple cool-downs, the need to perform high-throughput characterization has motivated previous work in realizing multiplexing devices and circuits. These include approaches that directly integrate the multiplexing switches into the quantum device chip<sup>7–9</sup> using the same technology. Embedding the multi-

plexer in this way however, increases the complexity and adds further steps to the fabrication process for quantum devices.

Here we describe a platform that decouples the quantum device and multiplexing circuit, fabricating a largenumber of multiplexer chips via tape-out to a commercial CMOS foundry. This platform enables multiple quantum devices to be characterized in a single cool-down and with a standard cryostat wiring configuration. Our multiplexer (MUX) is based on custom cryo-CMOS technology and specifically designed for operation below 100 mK. In the particular implementation reported here, 16 independent 1:5 MUX switches per die are configured by a room temperature microcontroller. The switches are based on parallel NMOS and PMOS transistors connected in a transmission gate (TG) topology, allowing for full rail-torail voltage swing of both the inputs and outputs. Our design further allows ad-hoc reconfiguration and daisy chaining of the multiplexer to suit particular device characterization needs.

Demonstrating both control of high-impedance bias lines and low-impedance transport measurements, we tune a GaAs quantum dot to the few electron regime via the Cryo-CMOS MUX, and measure the Hall mobility across a 2" InAs heterostructure. By making many parallel mobility measurements in a single cool-down we are able to map the variation in mobility across a wafer, enabling fast feedback between the growth of materials and device performance, an advantage for realizing and optimizing topological quantum devices.

# **II. DEVICE DETAILS**

A schematic of the experimental setup is shown in Fig. 1 (a). Room temperature electronics are used to generate and measure voltages and currents in a circuit

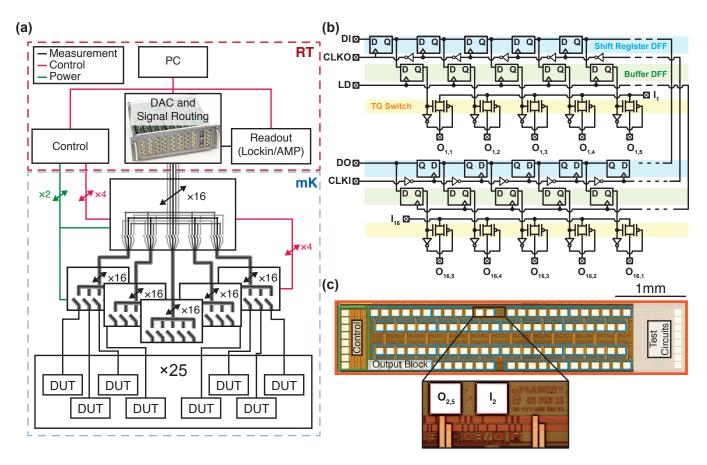

FIG. 1. (a) Experimental setup employing our Cryo-CMOS multiplexer chip to allow the simultaneous characterization of up to 25 DUTs at milli-kelvin temperature in a single cool-down. (b) Circuit block diagram of the multiplexer chip. Power supply pins  $V_{DD}$  and  $V_{SS}$  are not shown in the diagram, but can be set such that both negative and positive bias voltages may be applied, such that  $V_{SS} <= V_{out} <= V_{DD}$ . (c) Die photo of the fabricated chip. Inset shows part of the core switching circuit.

that comprises the device under test (DUT). The MUX chip is located at the milli-Kelvin stage of a dilution refrigerator, on a sample circuit board (PCB) adjacent to the DUT, and routes signals to and from it. Each MUX chip consists of 16 instances of a 1:5 analog multiplexing switch made from a 0.35 µm AMS CMOS process<sup>10</sup>. The input of one multiplexer can be connected to any of the 5 outputs or disconnected entirely. MUX chips are controlled by a total of 6 control lines, including 2 power supply lines, and may be daisy chained together to increase the switch count. Software control over the switching topology is provided by a microprocessor<sup>11</sup> located at room temperature.

A circuit block diagram of the CMOS MUX is shown in Fig. 1 (b). The multiplexing switches are of transmission gate (TG) topology, consisting of parallel NMOS and PMOS transistors of length 0.7 µm and width 40 µm and 120 µm respectively. The TG switch structure allows for a maximum rail-to-rail input and output voltage swing of  $V_{DD} - V_{SS} = 3.3$  V. For our initial characterization,  $V_{DD}$  is set to 3.3 V and  $V_{SS}$  is set to 0 V, and are the MUX chip's high and low power supply respectively. We emphasize that by the use of lower values for  $V_{SS}$  and  $V_{DD}$ , the MUX can be used to provide negative bias voltages. The use of a TG switch structure is necessary to ensure operation across the entire supply range. While using a single transistor switch design reduces the layout area and eliminates the need for complementary control signals, it limits the maximum output voltage swing to between  $V_{SS}$  and  $V_{DD} - V_{th,n}$  if a single NMOS transistor is used, or  $V_{SS} + V_{th,p}$  and  $V_{DD}$  if a single PMOS transistor is used, where  $V_{th,n(p)}$  are the threshold voltage for NMOS (PMOS). The output swing can potentially become even more limited as the devices are cooled due to an increase in  $V_{th,n(p)}$  as the intrinsic carrier density of the bulk,  $n_i$ , is exponentially dependent on temperature. As such,  $n_i$  drops sharply at deep cryogenic temperatures  $(< 40 \,\mathrm{K})$  due to bandgap widening and bulk carrier freeze out. This causes the bulk Fermi-level to increase, resulting in an increase in  $V_{th,n(p)}^{12,13}$ . The shift in threshold voltage,  $\Delta V_{th,n(p)}$  depends on n-doping (p-doping) concentration. For the 0.35 µm AMS process used for our devices, our measurements on transistor test structures indicate that  $V_{th.n}$  increases from 0.5 V to 0.75 V as the chip is cooled from room temperature to T = 6 K (similar measurements were reported in<sup>14</sup>). The shift in  $V_{th,p}$  is

more severe, rising from 0.8 V at 300 K to 1.35 V at 6 K. Crucially, the threshold voltage of PMOS devices does not saturate at deep cryogenic temperatures but rather continues to increase as the temperature is lowered.

An optical micrograph of the die, shown in Fig. 1(c), highlights the key regions of the multiplexer. The power supply and digital control pins are placed on the left hand side of the chip, and the multiplexing circuit and IO pads are laid out in a symmetrical staggered arrangement taking up  $3.1 \times 0.8 \,\mathrm{mm}$  of the core area. We note that the majority of this area is dominated by IO pads, whose area may be further miniaturized through the use of high-density interconnect technologies such as flip-chip bonding<sup>15</sup>. The control interface is a simple shift register (edge triggered D flip-flop, DFF) bank with serial data (DI) and clock (CLKI) inputs from an external controller (see Fig. 1 (b)). A second row of registers is used to buffer the switch controls. This enables the switch configuration to be modified without affecting the state of the outputs. The change takes effect concurrently only at the rising edge of a global load (LD) signal. Notwithstanding comprehensive low temperature models and rigorous timing analysis, it was imperative to improve the circuit's immunity to timing violation by design. Therefore DI is shifted from left to right of the flip-flop chain whereas CLK is buffered inside each flip-flop and passed onto the cell to its left. Though the cost of this design is extra logic gates and delay, propagating the DI and CLKI signals from opposite direction guarantees proper logic operation because data always arrives before the rising edge of the clock. Further, the clocking events and subsequent logic changes in each flip-flop are then slightly staggered. This disperses the sudden draw of large load current from the power supply that would have otherwise occurred if all the flip-flops were clocked simultaneously. This is a pragmatic design, driven by the unique challenges of cryogenic measurements that involve power supply or digital signals being fed from room temperature instrumentation via meters of cables. In such setups, maintaining stringent delay matching or supply regulation can be difficult when compared to conventional room temperature bench-top configurations.

By appropriate choice of topology, MUX chips may be chained together arbitrarily with no increase in the number of control lines. This is facilitated by the chaining of shift registers between chips, since the CLKI and DI pins are buffered and brought off chip on the clock out (CLKO) and data out (DO) pins respectively (see Fig. 1 (b)). Power supply and LD signals may be shared between dies. For example, the chip may be converted to a 1:80 multiplexer by tying all inputs together. Alternatively, by the use of 6 chips, it is possible to create  $16 \times 1$ : 25 multiplexers in the arrangement shown in Fig. 1 (a). Thus, the design is modular, allowing both the number of inputs and outputs to be increased without a corresponding increase in control lines, at the cost of a linear reduction at the rate that the state of the MUX may be changed.

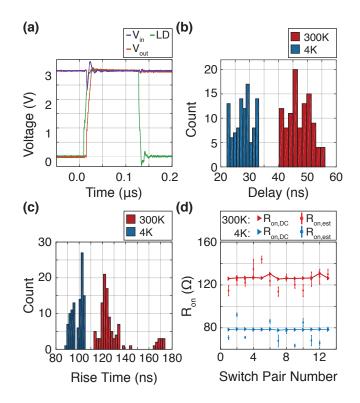

FIG. 2. Characterization of the performance of the MUX chip at T = 300 K and 4 K. (a) Multiplexing at 4 K with a scope trace showing  $V_{out}$  connecting to  $V_{in} = 3$  V when the MUX switch is turned on. (b) Delay and (c) rise time through the MUX switches at T = 300 K and 4 K. (d) On-state resistance estimated from delay and rise-time data,  $R_{on,est}$ , or measured directly using a lock-in amplifier,  $R_{on,DC}$ , at T = 300 K and 4 K.

The switches in the MUX chip are designed to drive both high-impedence bias lines, such as the bias gates of a quantum dot device, as well as to probe transport phenomena through devices, while maintaining a low onstate resistance (< 200  $\Omega$ ). The actual on-state resistance of the TG switch will be a function of applied source and drain voltage,  $V_{SD}$ , of the transistors. In steady state operation, for both biasing and transport applications, the transistors in the on-state are expected to have a negligibly small drain-source voltage,  $V_{DS} \ll 10 \text{ mV}$ , where they are designed operate in the ohmic region. The onstate resistance of the transistor can be expressed as,

$$R_{on} \sim \frac{W}{\mu C_{ox} L (V_{GS} - V_{th})} \tag{1}$$

where  $\mu$  is carrier mobility,  $C_{ox}$  is gate capacitance per unit area, W, L are transistor width and length, and  $V_{GS}$ is gate to source voltage. The effect of  $V_{DS}$  is negligible in the limit that  $V_{GS} - V_{th} \gg V_{DS}$ .

At fixed temperature  $R_{on}$  is a non-linear function of input voltage  $V_{in}$ , and supply voltages  $V_{DD}$  and  $V_{SS}$ . Furthermore, the competing effect of increased  $V_{th}$  and  $\mu$  with cooling will cause  $R_{on}$  to vary depending on operating temperature<sup>13,16</sup>. The ratio of on-resistance at T = 300 K and 4 K,  $\gamma = R_{on,4K}/R_{on,300K}$ , for both NMOS and PMOS transistors operating in the ohmic region can be expressed as:

$$\gamma_n = \frac{\mu_{n,300K}}{\mu_{n,4K}} \times \frac{1}{1 - \frac{\Delta V_{th,n}}{VDD - V_{in} - V_{th,n.300K}}}$$

(2)

$$\gamma_p = \frac{\mu_{p,300K}}{\mu_{p,4K}} \times \frac{1}{1 - \frac{\Delta V_{th,p}}{V_{in} - |V_{th,p,300K}|}} \tag{3}$$

Here  $\Delta V_{th,n(p)}$  is defined as  $V_{th,n(p),4K} - V_{th,n(p),300K}$ . The operating temperature and corresponding transistor type is denotes in the symbol subscript. We measure  $\mu_{p,4K}$  to have increased by a factor of 2.4, whereas  $\mu_{n,300K}$  is measured to be 4 times higher compared to its room temperature value<sup>14</sup>. Lower  $\mu$  together with higher  $V_{th}$  will cause  $R_{on,p,4K}$  to be much higher than  $R_{on,n,4K}$ .

To experimentally verify the performance of the Cryo-CMOS MUX chip at cryogenic temperatures, we wirebond the dies to a test PCB for measurement at T =300 K and 4 K. The outputs of 13 pairs of switches were wirebonded in series to measure the performance of the switches through the cryostat. The supply voltages for the test were set to  $V_{DD} = 3 V$  and  $V_{SS} = 0 V$  respectively. In addition, a pair of lines were shorted directly on the PCB, and used to calibrate the fixed resistance and delay through the cryostat. A representative trace, showing the output voltage  $V_{out}$  being pulled high as the switch is closed, is shown in Fig. 2 (a). A slight delay between the LD pin being asserted and  $V_{out}$  being pulled high is visible, as well as a finite rise time which is set by the resistance of the switch and capacitance of wiring through the fridge. Histograms of delay and rise time across multiple switches in shown in Fig. 2 (b) and Fig. 2 (c) respectively at both 300 K (red), and 4 K (blue). A faster response is observed at 4 K, which we attribute to the reduction of  $R_{on}$ , leading to a faster switching time.

Finally, we measure the on-state resistance,  $R_{on}$ , of the switches in two ways. First, we directly measure the onstate resistance of the switches using conventional lock-in techniques, with a 100 µV excitation, through a shorted pairs of switches. To find the individual switch resistance,  $R_{on,DC}$ , the previously calibrated resistance of the cryostat wiring is subtracted, and the result is divided by 2. Second, we extract the on-state resistance from the measurement of rise time across the 13 pairs, using the measurement equipment, which we denote  $R_{on,est}$ . The measured values across all switches is plotted in Fig. 2 (d), with both techniques yielding values in good agreement with each other.

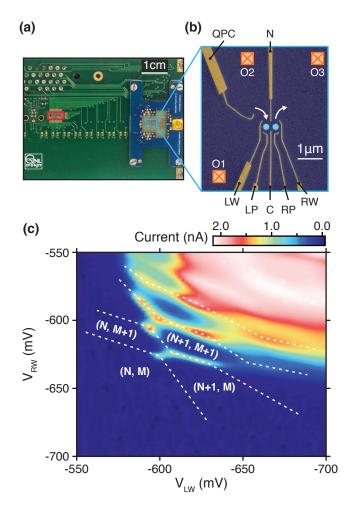

FIG. 3. (a) Photograph of the multiplexer characterization PCB showing the MUX chip (red), and an equivalent quantum dot connected to filtered DC lines via the MUX chip (blue). (b) False-color SEM of a quantum dot device, fabricated on a GaAs/(Al,Ga)As heterostructures. Ti/Au surface gates (gold) are used to define two quantum wells (blue dots). Locations of contacts to 2-dimensional electron gas are indicated in orange boxes. (c) Charge stability diagram of a double quantum dot showing the characteristic honeycomb pattern of a double quantum dot. White dashed lines indicate charge transitions and are a guide to the eye.

#### **III. EXPERIMENTAL APPLICATIONS**

# A. Quantum Dots

In order to determine the suitability of our multiplexer for quantum device characterization, we connect it to the gates and ohmic contacts of a quantum dot device and perform transport measurements. A typical quantum dot device will have charging energies of around  $100 \,\mu eV^{17}$ . For a well defined quantum dot to be formed, the electrical noise and heat introduced by our proximal Cryo-CMOS multiplexer must be negligible relative to the charging energy<sup>18</sup>, thus quantum dot measure-

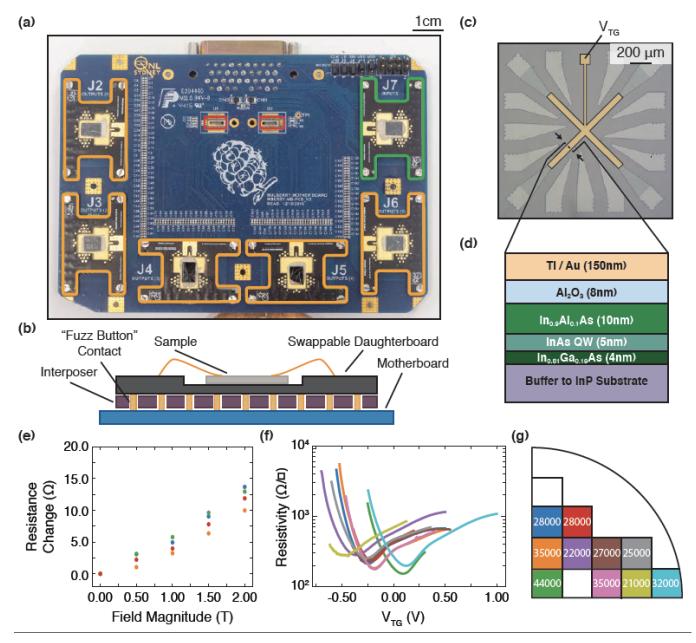

FIG. 4. (a) Photograph of multiplexed characterization PCB showing MUX die (red) with 5 daughter-boards (orange) allowing measurements, and an additional daughter-board (green), that has a connection to the fridge wiring bypassing the MUX chip. (b) Cross-section of mother-board, interposer and swappable daughter-board. (c) Optical micrograph of Hall bar device for characterizing mobility. A top gate (gold) allows for tuning of the density in the device. (d) Cross section of measured InAs heterostructure. (e) Resistance of shorted MUX lines as a function of perpendicular magnetic field, measured across four separate pairs of switches. (f) Hall resistivity as a function of  $V_{TG}$  for n=9 Hall bar devices, measured across two cool-downs. (g) Extracted mobility as a function of position on growth wafer.

ments provide a means of determining the suitability of our MUX for purpose. The quantum dot device is fabricated on an MBE grown GaAs/(Al,Ga)As heterostructure, which forms a 2-dimensional electron gas (2DEG) 91 nm below the surface. TiAu gates are patterned on the surface to define the dots, separated by an 10 nm HfO<sub>2</sub> dielectric. An optical micrograph of the device is shown in Fig. 3 (a), with the MUX chip highlighted in the red box and the quantum dot device highlighted in the blue box. A false-color SEM of a similar device is shown in Fig 3 (b). The sample is mounted at the milli-Kelvin stage of a dilution refrigerator with a base temperature of 8 mK. Negative voltages are applied to the surface gates (gold) to create quantum dots (blue) containing a discrete number of electrons. The occupancy of each dot is denoted (N, M) where N(M) is the number of elecussed (c-d)). An 8 nm , O2 induce supercondu

trons on the left (right) quantum dot. Current is passed through the quantum dot via contacts to the 2DEG, O2 and O3, where current is only able to flow when there are available electron states in both the left and the right quantum dot. In order to allow negative bias voltages to be used, the MUX chip is operated with  $V_{SS} = -2$  V and  $V_{DD} = 1$  V.

In Figure 3(c), the current through the quantum dot is shown, with both gates and ohmic contacts routed through the Cryo-CMOS MUX chip. Conventional lockin techniques are used for current readout with an excitation voltage of 100  $\mu$ V across the device. A honeycomb pattern characteristic of a double quantum dot is visible, with charge transitions indicated by dotted lines. Similar measurements were carried out for different gate configurations. In the steady-state we find the additional heat or noise generated by the MUX chip to be negligible, with the base temperature of the cryostat unaffected by the multiplexer.

## B. Mobility Characterization

Finally, we demonstrate the use of our multiplexer for performing batch materials characterization of InAs heterostructures, of interest for the purpose of realizing topological qubits<sup>19</sup>. Here we are focused on determining how parameters such as the carrier mobility of the electron gas varies across a wafer, a key metric for device performance<sup>20</sup>. To carryout batch-style measurements we have developed a device packaging approach that allows many quantum devices to be bonded onto separate daughter PCBs<sup>21</sup>, that are collectively mounted on a motherboard that also houses the CMOS MUX chips, as shown in Fig. 4(a). This setup allows mounting of five dies, each containing 4 devices, in the dilution refrigerator in a single cool-down, with an additional sixth die configured such that its electrical connections bypass the cyro-CMOS MUX. The daughter-boards are connected to the motherboard via an interposer, that allows for samples to be rapidly interchanged in between cool-downs<sup>21</sup> (Fig. 4 (b)).

In our demonstration the heterostructure consists of a InAlAs/InAs/InGaAs quantum well grown 10 nm below the surface on a 2" (100) InP substrate (Fig. 4

(c-d)). An 8 nm layer of Al was deposited in-situ to induce superconductivity in the quantum well via the proximity effect. Hall bar devices were defined across a quarter wafer of heterostructure, and the Al removed in the active area both by standard wet etching techniques. A global ALD  $Al_2O_3$  gate dielectric was then deposited, followed by a Ti/Au top gate defined by e-beam lithography. Magnetoconductance measurements of the Hall bar were performed simultaneously as a function of top gate voltage in a perpendicular magnetic field using standard lock-in techniques. Fig. 4 (f) shows the extracted resistivity as a function of top gate voltage for 9 samples, obtained across two cool-downs. No degradation in device performance is seen compared to devices measured without the Cryo-CMOS MUX in-line. Using this technique, we can map out the mobility as a function of position of the die on the growth wafer, as indicated in Fig. 4 (g). We observe that dies coming from the edge of the wafer suffer a degradation of mobility by a factor of two  $(27000 \,\mathrm{cm^2/(V \,s)})$  compared to dies near the center of the wafer  $(44\,000\,\mathrm{cm}^2/(\mathrm{V\,s}))$ . The magnetoconductance measurements also allow us to study the additional inline resistance that emerges as a function of magnetic field. As shown in Fig. 4 (e), we observe an additional linear resistance of  $6 \,\Omega \,\mathrm{T}^{-1}$  within the magnetic field range of -2T to 2T studied in this work.

*Note:* In the final stage of submitting this manuscript a preprint describing similar work using commercial off-the-shelf CMOS multiplexing circuits has appeared<sup>22</sup>.

# ACKNOWLEDGMENTS

This research was supported by Microsoft Corporation and the ARC Centre of Excellence for Engineered Quantum Systems. We thank Y. Yang, X. Croot, and A. Moini for technical assistance and useful discussions. We acknowledge the facilities as well as the scientific and technical assistance of the Research & Prototype Foundry Core Research Facility at the University of Sydney, part of the Australian National Fabrication Facility (ANFF), and the NSW node of ANFF at the University of New South Wales.

- \* These authors contributed equally to this work

- <sup>†</sup> david.reilly@sydney.edu.au

- <sup>1</sup> D. Rosenberg, S. Weber, D. Conway, D. Yost, J. Mallek, G. Calusine, R. Das, D. Kim, M. Schwartz, W. Woods, J. L. Yoder, and W. D. Oliver, 3D integration and packaging for solid-state qubits, arXiv e-prints, arXiv:1906.11146 (2019), arXiv:1906.11146 [quant-ph].

- <sup>2</sup> M. Veldhorst, H. G. J. Eenink, C. H. Yang, and A. S. Dzurak, Silicon cmos architecture for a spin-based quantum computer, Nature Communications 8, 1766 (2017).

- <sup>3</sup> J. M. Hornibrook, J. I. Colless, I. D. Conway Lamb, S. J. Pauka, H. Lu, A. C. Gossard, J. D. Watson, G. C. Gardner, S. Fallahi, M. J. Manfra, and D. J. Reilly, Cryogenic control architecture for large-scale quantum computing, Phys. Rev. Applied **3**, 024010 (2015).

- <sup>4</sup> R. Mead, The Design of Experiments: Statistical Principles for Practical Applications (Cambridge University Press,, 1990).

- <sup>5</sup> G. Tennant, Six Sigma: SPC and TQM in Manufacturing and Services (Gower Publishing Ltd., 2001).

- <sup>6</sup> S. Krinner, S. Storz, P. Kurpiers, P. Magnard, J. Heinsoo, R. Keller, J. Lütolf, C. Eichler, and A. Wallraff, Engineering cryogenic setups for 100-qubit scale superconducting circuit systems, EPJ Quantum Technology 6, 2 (2019).

- <sup>7</sup> S. Schaal, A. Rossi, V. N. Ciriano-Tejel, T.-Y. Yang, S. Barraud, J. J. L. Morton, and M. F. Gonzalez-Zalba, A cmos dynamic random access architecture for radiofrequency readout of quantum devices, Nature Electronics 2, 236 (2019).

- <sup>8</sup> D. R. Ward, D. E. Savage, M. G. Lagally, S. N. Coppersmith, and M. A. Eriksson, Integration of on-chip fieldeffect transistor switches with dopantless Si/SiGe quantum dots for high-throughput testing, Appl. Phys. Lett. **102**, 213107 (2013).

- <sup>9</sup> H. Al-Taie, L. W. Smith, B. Xu, P. See, J. P. Griffiths, H. E. Beere, G. A. C. Jones, D. A. Ritchie, M. J. Kelly, and C. G. Smith, Cryogenic on-chip multiplexer for the study of quantum transport in 256 split-gate devices, Appl. Phys. Lett. **102**, 243102 (2013).

- <sup>10</sup> AMS SG. https://ams.com/. Shuttle run on 29 Feb, 2016.

- <sup>11</sup> Cypress Semiconductor CY8C5888LTI-LP097.

- <sup>12</sup> A. Beckers, F. Jazaeri, and C. Enz, Cryogenic mosfet threshold voltage model, arXiv preprint arXiv:1904.09911 (2019).

- <sup>13</sup> G. Ghibaudoand F. Balestra, Low temperature characterization of silicon cmos devices, Microelectronics Reliability **37**, 1353 (1997).

- <sup>14</sup> N. C. Dao, A. E. Kass, M. R. Azghadi, C. T. Jin, J. Scott, and P. H. W. Leong, An enhanced mosfet threshold voltage model for the 6300k temperature range, Microelectronics Reliability **69**, 36 (2017).

- <sup>15</sup> R. Das, J. Yoder, D. Rosenberg, D. Kim, D. Yost, J. Mallek, D. Hover, V. Bolkhovsky, A. Kerman, and

W. Oliver, Cryogenic qubit integration for quantum computing, in 2018 IEEE 68th Electronic Components and Technology Conference (ECTC) (2018) pp. 504–514.

- <sup>16</sup> K. Dasand T. Lehmann, Effect of deep cryogenic temperature on silicon-on-insulator cmos mismatch: A circuit designers perspective, Cryogenics **62**, 84 (2014).

- <sup>17</sup> X. Croot, S. Pauka, J. Watson, G. Gardner, S. Fallahi, M. Manfra, and D. Reilly, Device architecture for coupling spin qubits via an intermediate quantum state, Phys. Rev. Applied **10**, 044058 (2018).

- <sup>18</sup> R. Hanson, L. P. Kouwenhoven, J. R. Petta, S. Tarucha, and L. M. K. Vandersypen, Spins in few-electron quantum dots, Rev. Mod. Phys. **79**, 1217 (2007).

- <sup>19</sup> R. M. Lutchyn, E. P. A. M. Bakkers, L. P. Kouwenhoven, P. Krogstrup, C. M. Marcus, and Y. Oreg, Majorana zero modes in superconductor–semiconductor heterostructures, Nature Reviews Materials **3**, 52 (2018).

- <sup>20</sup> A. T. Hatke, T. Wang, C. Thomas, G. C. Gardner, and M. J. Manfra, Mobility in excess of  $1 \times 10^6$  cm<sup>2</sup> v<sup>-1</sup> s<sup>-1</sup> in inas quantum wells grown on lattice mismatched InP substrates, Applied Physics Letters **111**, 142106 (2017), https://doi.org/10.1063/1.4993784.

- <sup>21</sup> J. I. Collessand D. J. Reilly, Modular cryogenic interconnects for multi-qubit devices, Review of Scientific Instruments 85, 114706 (2014), https://doi.org/10.1063/1.4900948.

- <sup>22</sup> B. Paquelet Wuetz, P. L. Bavdaz, L. A. Yeoh, R. Schouten, H. van der Does, M. Tiggelman, D. Sabbagh, A. Sammak, C. G. Almudever, F. Sebastiano, J. S. Clarke, M. Veldhorst, and G. Scappucci, Multiplexed quantum transport using commercial off-the-shelf CMOS at sub-kelvin temperatures, arXiv e-prints, arXiv:1907.11816 (2019), arXiv:1907.11816 [cond-mat.mes-hall].