# Threshold Voltage variation with respect to Gate geometry in Nano-scale MOSFETS

# Raja N. Mir

*Abstract*— The tremendous progress in Metal Oxide Semiconductor (MOS) technology has been a direct consequence of device scaling for past several decades. But as we have entered the nanometer era many problems related to leakage currents and other issues related to variability impacting the yield are of concern. Herein we have investigated how the change in the Fin Architecture and Gate Length of the MOS device impacts the Threshold Voltage.

*Keywords*— MOS, Leakage, MOSFET, NANO, Ivy Bridge, Threshold Voltage.

#### I. INTRODUCTION

With ever increasing digital performance and application, the demands are very high for better and higher performance digital semiconductor devices. This is directly dependent on the semiconductor industry being able to scale the Metal Oxide Semiconductor Field Effect Transistor (MOSFET). With many innovations in the gate-stack technology, we are able to push the physical gate length 14 nm and this will go well beyond this scale. The High K metal gate reduces the gate leakage significantly by improving the electrostatics within the MOSFET channel. Another way to improve the electrostatic situation in the MOSFET channel is to optimize the MOSFET channel structure or geometry. The further scaling will continue to face increasing number of technological and physical challenges, among these the structural optimization of the channel is also one of the major concerns. The other challenges being able to control the variability in doping, poly-silicon granularity, random grain orientation within the High-K dielectric [1-3].

In the present work we have full three-dimensional simulation of the gate-structure impact on the nano-scale MOSFET threshold characteristics. We have also done some experimental studies of this phenomena. In addition, there are full-bandstructure tight binding calculations which can provide further insight but are not discussed in this paper [4-13]. In the next section we describe the simulation setup, and results of the gate structure changes on the transistor threshold voltage (Vt).

### II. SIMULATION SETUP

TCAD based tools[14] are widely used to simulate electrical characteristics of MOS transistors, e.g:- Vth, SS, Ion, Ioff , gm, gds etc. These characteristics are very important metrics of device behavior and are used to compare and contrast different devices. Within the framework of TCAD they are determined by first doing the process simulation then doing a device simulation and finally an extraction from the the results of the device simulation. We compared the behavior of four devices: planar MOSFET, triangular bulk 3D-MOSFET, rectangular bulk 3D-MOSFET and rectangular SOI 3D-MOSFET. These analyses will indicate the superiority of the 3D-MOSFET over the planar device. The 3D-MOSFET height is equal to 24 nm, the base width is 10.7 nm. The angle of the fin in the triangular 3D-MOSFET is equal to 84 degrees. These devices have the same underlying process. The planar device is obtained by modifying the 3D-MOSFET, by reducing the fin height(H) and stretching the fin width(W) equal to the (2 \* H + W). The doping concentration in the source and the drain is 1020 cm<sup>3</sup> and that in the channel region is 1018 cm3. We have closely tried to follow Intel Ivy Bridge [1] device dimensions.

Figure 1: TEM Lattice image of NMOS fin structure. Adapted from [15]

III. RESULTS

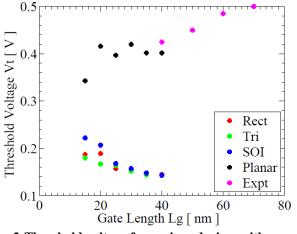

In the Figure:2 we see that the threshold voltage of the 3D-MOSFET's is very close as we move down the gate length. We observe a voltage rollon trend, which is there because of the fact that the halo implants overlap as the source and the drain come closer together. In case of the planar device the threshold voltage is more than 3D-MOSFET's. Overall a voltage rolloff in case of the planar device is observed but the rolloff is not very clear as there are two competing effects going on in the MOSFET. One is that the Drain Induced Barrier Lowering (DIBL) effect will tend to give a rolloff but on the other hand due to source and drain halo implants the voltage rollon should take place. The combined result of these two effects in this specific case resulted in overall lowering of the threshold voltage as we move down the gate length.

Figure 2: Threshold voltage for various devices with similar gate lengths and widths.

## IV. CONCLUSION

It is clearly seen that the threshold voltage of the 3D-MOSFET is better than the planar counterpart. The voltage roll-on for the 3D MOSFET is evident as the channel is reduced, the roll-off for the planar counter part is also observed to some degree.

#### REFERENCES

- D. James. Intel ivy bridge unveiled x2014; the first commercial tri-gate, high-k, metalgate cpu. In Custom Integrated Circuits Conference (CICC), 2012 IEEE, pages 1–4, 2012.

- [2] Fu-Liang Yang, Haur-Ywh Chen, Fang-Cheng Chen, Yi-Lin Chan, Kuo-Nan Yang, Chih-Jian Chen, Hun-Jan Tao, Yang-Kyu Choi, Mong-Song Liang, and Chenming Hu. 35 nm cmos finfets. In VLSI Technology, 2002. Digest of Technical Papers. 2002 Symposium on, pages 104–105, 2002.

- [3] K. von Arnim, E. Augendre, A.C. Pacha, T. Schulz, K.T. San, F. Bauer, A. Nackaerts, R. Rooyackers, T. Vandeweyer, B. Degroote, N. Collaert, A. Dixit, R. Singanamalla, W. Xiong, A. Marshall, C. R. Cleavelin, K. Schrufer, and M. Jurczak. A low-power multi-gate fet cmos technology with 13.9ps inverter delay, large-scale integrated high performance digital circuits and sram. In VLSI Technology, 2007 IEEE Symposium on, pages 106–107, 2007.

- [4] W. R. Frensley, R. N. Mir. "Simple remedy for spurious states in discrete K.P models of semiconductor structures." arXiv:1412.7201, Dec 22, 2014.

- [5] R. N. Mir, WR Frensley, S. Shichijo, P. A. Blakey, "Computational technique for probing terminal control mechanisms inside threedimensional nano-scale MOSFET." pp.2, Electronics Letters, May 2014.

- [6] R. N. Mir, W. R. Frensley, "Electrical design of InAs-Sb/GaSb superlattices for optical detectors using full bandstructure sp3s\* tightbinding method and Bloch boundary conditions.", pp.1, Journal of Applied Physics, October 2013.

- [7] R. N. Mir "Electronic structure of III-V broken gap materials and terminal control in three dimensional nano-scale MOSFETs." Thesis, The University of Texas at Dallas; 2014.

- [8] Mir RN. "Bulk bandstructure computation of III-V compounds using the K P method." Thesis, The University of Texas at Dallas; 2009.

- [9] R. N. Mir and W. R. Frensley, "Quantifying the local influence of terminal voltages within an electron device," pp.3, 2018 Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, Texas.

- [10] R. N. Mir, "Linearization Approach for 5G Millimeter-Wave N-Array Beamforming Device", pp.1, 2019 IEEE Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS)

- [11] RN Mir, WR Frensley arXiv preprint arXiv:1909.04718, 2019 arxiv.org

- [12] Craig S. Lent and David J. Kirkner. The quantum transmitting boundary method. Journal of Applied Physics, 67(10), 1990.

- [13] F. Sols, M. Macucci, U. Ravaioli, and K. Hess, Appl. Phys. Lett. 54, 350 (1989).

- [14] Synopsys. TCAD Sentaurus. Synopsys, Inc.,

- [15] Dick James. Intels 22-nm tri-gate transistors exposed. http://www.chipworks.com/en/technical-competitiveanalysis/resources/blog/intels-22-nm-tri-gate-transistors-exposed, 2012.