# T-count and Qubit Optimized Quantum Circuit Designs of Carry Lookahead Adder

Himanshu Thapliyal, Edgard Muñoz-Coreas, Vladislav Khalus

Abstract-Quantum circuits of arithmetic operations such as addition are needed to implement quantum algorithms in hardware. Quantum circuits based on Clifford+T gates are used as they can be made tolerant to noise. The tradeoff of gaining fault tolerance from using Clifford+T gates and error correcting codes is the high implementation overhead of the T gate. As a result, the T-count performance measure has become important in quantum circuit design. Due to noise, the risk for errors in a quantum circuit computation increases as the number of gate layers (or depth) in the circuit increases. As a result, low depth circuits such as quantum carry lookahead adders (QCLA)s have caught the attention of researchers. This work presents two QCLA designs each optimized with emphasis on T-count or qubit cost respectively. In-place and out-of-place versions of each design are shown. The proposed QCLAs are compared against the existing works in terms of T-count. The proposed QCLAs for out-of-place addition achieve average T gate savings of 54.34% and 37.21%, respectively. The proposed QCLAs for in-place addition achieve average T gate savings of 72.11% and 35.87% respectively.

## I. INTRODUCTION

Quantum circuits of arithmetic operations are needed to design quantum hardware for implementing quantum algorithms such As integer factoring, searching and quantum mechanical simulation. Quantum circuits for addition are fundamental building blocks crucial to implementing these quantum algorithms [1] [2] [3] [4] [5]. Thus, researchers have invested considerable effort in designing quantum adders such as ripple carry adders or carry lookahead adders (QCLAs) [6] [7] [8] [9] [10] [11].

Quantum circuits possess properties that make them distinct from circuits for other technologies. For example, there is a one-to-one relationship between the inputs and outputs in a quantum circuit. As a result, the quantum circuit designer will face additional sources of circuit overhead such as ancillae and garbage output. Ancillae are constant inputs to the quantum circuit. Garbage output are any circuit output that is not a circuit input or needed output. To make full use of the qubit resources of the quantum machine, the garbage output will need to be cleared. This process will add to the overall qubit cost and gate cost of a quantum circuit and is discussed in [12].

Physical quantum computers are prone to noise errors [13] [14] [15]. Quantum circuits based on Clifford+T gates have caught the attention of researchers because can be made

Himanshu Thapliyal, Edgard Muñoz-Coreas and Vladislav Khalus are with the Department of Electrical and Computer Engineering, University of Kentucky, Lexington, KY, USA.

Email: hthapliyal@uky.edu

fault tolerant with quantum error correcting codes permitting reliable and scalable quantum computation [15] [16]. This set is universal and has been used to realize basic reversible logic gates and larger functional blocks [17] [18] [16] [19] [20]. However, fault tolerance comes with increased implementation overhead especially the overhead associated with implementing the T gate [16] [21] [22]. The high cost to implement the T gate has caused the measures of T-count and T-depth to become important measures to evaluate quantum circuit cost [17] [14] [23] [9].

QCLAs have caught the interest of researchers because they perform the addition operation in order  $\mathcal{O}(log(n))$  circuit depth (while the ripple carry adder has a depth of  $\mathcal{O}(n)$ ). Lowdepth circuits such as QCLAs have use in quantum hardware applications where longer computation time increases the risk of errors [24] [25] [26]. Several QCLA designs have been proposed in the literature such as [27] or [8]. Designs that return the sum on ancillae (or out-of-place QCLA) and designs that replace one of the primary inputs with the sum (or in-place QCLA) have been proposed. Table I and Table II summarizes the existing work. Table I presents existing out-of-place QCLAs and Table II presents in-place QCLAs. Further discussion on the existing work is in Section VII.

TABLE I: Details of Existing Out-of-Place QCLAs

| Design                    | T-count                   | qubits                    | gates used                                                      | garbage? |

|---------------------------|---------------------------|---------------------------|-----------------------------------------------------------------|----------|

| Draper et al. ([28])      | $\mathcal{O}(35 \cdot n)$ | $\mathcal{O}(4 \cdot n)$  | CNOT, Toffoli                                                   | no       |

| Babu et al.*<br>([29])    | $\mathcal{O}(54 \cdot n)$ | $\mathcal{O}(12 \cdot n)$ | PFA <sup>1</sup> , CNOT,<br>MIG <sup>2</sup> , NFT <sup>3</sup> | yes      |

| Trisetyarso et al. ([30]) | $\mathcal{O}(35 \cdot n)$ | $\mathcal{O}(4 \cdot n)$  | NOT, CNOT,<br>Toffoli,<br>Hadamard,<br>DCZ <sup>4</sup>         | no       |

| Lisa et al.*<br>([31])    | $\mathcal{O}26 \cdot n)$  | $\mathcal{O}(6 \cdot n)$  | CNOT, RPA <sup>5</sup> ,<br>Fredkin <sup>7</sup>                | yes      |

| Thapliyal et al. ([32])   | $\mathcal{O}(35 \cdot n)$ | $\mathcal{O}(4 \cdot n)$  | CNOT,<br>Toffoli,<br>Peres <sup>6</sup>                         | no       |

The PFA gate decomposes into two V gates, a V+ gate and six CNOT gates. Each V gate and V+ gate has a T-count of 3. [29] [33] [18]

The MIG gate decomposes into two V gates, a V+ gate and four CNOT gates. [33]

<sup>&</sup>lt;sup>3</sup> The NFT gate decomposes into two V gates, a V+ gate and seven CNOT gates [34]

The DCZ or double controlled Z gate has a T-count of seven. [35]

<sup>&</sup>lt;sup>5</sup> The RPA gate decomposes into a V gate, a V+ gate and three CNOT gates [31]

gates. [31]

<sup>6</sup> The Peres gate has a T-count of seven. [18]

<sup>&</sup>lt;sup>7</sup> The Fredkin gate has a T-count of seven. [18]

<sup>\*</sup> T-count and qubit cost are for the circuit after being modified to remove garbage output. We use the methodology outlined in [12] to remove the garbage outputs

TABLE II: Details of Existing In-Place QCLAs

| Design                       | T-count                            | qubits                           | gates used                           | garbage? |

|------------------------------|------------------------------------|----------------------------------|--------------------------------------|----------|

| Draper et al. ([28])         | $\mathcal{O}(70 \cdot n)$          | $\mathcal{O}(4 \cdot n)$         | NOT, CNOT,<br>Toffoli                | no       |

| Trisetyarso<br>et al. ([30]) | $\mathcal{O}(70 \cdot n)$          | $\mathcal{O}(4 \cdot n)$         | NOT, CNOT,<br>Toffoli,               | no       |

| (1.17)                       |                                    |                                  | Hadamard,<br>DCZ <sup>1</sup>        |          |

| Thapliyal et al. ([32])      | $\approx \mathcal{O}(51 \cdot n)$  | $\mathcal{O}(4 \cdot n)$         | NOT, CNOT,<br>Toffoli,               | no       |

| un ([32])                    |                                    |                                  | Peres <sup>2</sup> , TR <sup>3</sup> |          |

| Takahashi                    | $\approx \mathcal{O}(196 \cdot n)$ | $\approx \mathcal{O}(5 \cdot n)$ | NOT, CNOT,<br>Toffoli                | no       |

| et al.([8])<br>Takahashi     | ~. (0(40)                          | ~ (O(F)                          |                                      |          |

| et al.([36])                 | $\approx \mathcal{O}(49 \cdot n)$  | $\approx \mathcal{O}(5 \cdot n)$ | NOT, CNOT,<br>Toffoli                | no       |

| Cheng et al.                 | $\mathcal{O}(n^3)$                 | $\mathcal{O}(3 \cdot n)$         | CNOT,                                | no       |

| ([27])                       |                                    |                                  | Toffoli,                             |          |

|                              |                                    |                                  | $MCT^4$                              |          |

| Mogenson                     | $\approx \mathcal{O}(42 \cdot n)$  | $\mathcal{O}(3 \cdot n)$         | CNOT,                                | no       |

| 1 ([37])                     |                                    |                                  | Toffoli,                             |          |

|                              |                                    |                                  | Fredkin <sup>5</sup>                 |          |

| Mogenson                     | $\approx \mathcal{O}(42 \cdot n)$  | $\mathcal{O}(3 \cdot n)$         | CNOT,                                | no       |

| 2 ([37])                     |                                    |                                  | Toffoli,                             |          |

|                              |                                    |                                  | Fredkin <sup>5</sup>                 |          |

<sup>&</sup>lt;sup>1</sup> The DCZ or double controlled Z gate has a T-count of seven. [35]

To overcome shortcomings in existing works, this work proposes a family of designs for QCLAs. The first design (FT-QCLA1) is optimized with an emphasis on T-count. The second design (FT-QCLA2) is optimized with an emphasis on number of qubits. All proposed designs enjoy reduced T gate cost and qubit cost compared to the existing works. In-place QCLA implementations (In-FT-QCLA1 and In-FT-QCLA2) and outof-place QCLA implementations (Out-FT-QCLA1 and Out-FT-QCLA2) for each design are shown. All proposed QCLAs can be made fault tolerant with error correcting codes. The proposed QCLA designs are based on the NOT gate, CNOT gate, Toffoli gate, logical AND gate and uncomputation gate. The logical AND gate and uncomputation gate are presented in [19] and [23]. The proposed QCLAs are compared against existing works and shown to be superior in terms of qubit cost and T-count.

This work is organized as follows: Section II provides background on the Clifford+T quantum gate set, introduces the logical AND gate and the uncomputation gate. Section III presents the proposed out-of-place QCLAs. Each design (Out-FT-QCLA1 and Out-FT-QCLA2) is addressed in its own subsection within Section III. Section IV illustrates the comparison of the proposed out-of-place QCLAs against existing out-of-place QCLAs. Section V presents the proposed in-place QCLAs. Each design (In-FT-QCLA1 and In-FT-QCLA2) is addressed in its own subsection within Section V. Section VI illustrates the comparison of the proposed in-place QCLAs against existing in-place QCLAs. Section VII provides a review of the existing work in quantum carry lookahead addition.

## II. BACKGROUND

## A. Quantum Gates

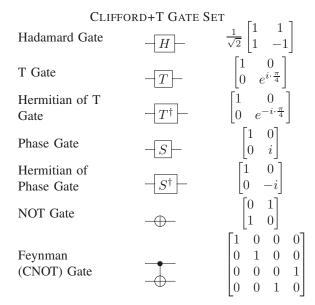

Fig. 1: The quantum gate set used in this work.

The proposed QCLA circuits in this work are based on the Clifford+T quantum gate set shown in Figure 1. The Clifford+T gates have caught the interest of researchers because the gate set can be made tolerant to noise errors [13] [14] [15]. The Clifford+T gate set is universal in nature permitting the fault tolerant quantum realization of any function of interest [39] [17]. However, the fault-tolerance comes with the tradeoff of the high implementation costs of the T gate relative to the Clifford gates. Details on the fault tolerant implementation of the T gate (and its associated costs) are in [21] [22]. The T gate is required because the Clifford gates by themselves are not universal [17] [14] [39] [16]. The high implementation cost of the T gate has made T-count and T-depth metrics of interest to evaluate quantum circuit performance. Existing quantum computers (such as those shown in [25]) have a small number of qubits available. As a result, the number of qubits in a quantum circuit is an important cost measure. We now define the T-count, T-depth and qubit cost resource measures.

- T-count: T-count is the total number of T gates used in the quantum circuit.

- T-depth: T-depth is the number of T gate layers in the circuit, where a layer consists of quantum operations that can be performed simultaneously.

- Qubit cost: Qubit cost is the total number of qubits required to design the quantum circuit.

The Clifford+T gates can be combined to build logic gates which can in turn be used to implement quantum circuits such as the proposed QCLAs. The proposed QCLA circuits are based on the NOT gate, CNOT gate, Toffoli gate, temporary logical-AND gate and uncomputation gate. The NOT gate and CNOT gate are members of the Clifford+T gate set. The Toffoli gate, temporary logical-AND gate and uncomputation gates must be constructed from Clifford+T gates. We use the Clifford+T implementations of the Toffoli gate designed in

<sup>&</sup>lt;sup>2</sup> The Peres gate has a T-count of seven. [18]

<sup>&</sup>lt;sup>3</sup> The TR gate decomposes into two V gates, a V+ gate and a CNOT gate.

Each V gate and V+ gate has a T-count of 3. [38] [18]  $^4$  The MCT or Multiple-Control Toffoli gate decomposes into  $2\cdot n-3$

Toffoli gates. The T-count is  $14 \cdot n - 21$ .

<sup>&</sup>lt;sup>5</sup> The Fredkin gate has a T-count of seven. [18]

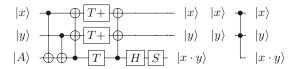

(a) The temporary logical-AND gate and its Clifford+T gate implementation. This Clifford+T gate implementation of the temporary logical-AND gate has a T-count of 4.  $|A\rangle$  is an ancillae in the state  $\frac{1}{\sqrt{2}}(|0\rangle+e^{\frac{i-\pi}{4}}|1\rangle).$  Source: [23]

(b) The uncomputation gate and its Clifford+T gate implementation. This Clifford+T gate implementation of the uncomputation gate has a T-count of 0. Source [23]

Fig. 2: Clifford+T gate implementation of the uncomputation gate and logical-AND gate used in this work.

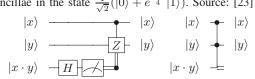

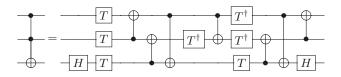

Fig. 3: The Clifford+T gate implementation of the Toffoli gate design presented in [18]. This fault tolerant Clifford + T gate implementation of the Toffoli gate has a T-count of 7.

[18] for this work (see figure 3). Figure 2 shows the temporary logical-AND gate and the uncomputation gates used in this work. The Clifford+T implementation and the graphical image are shown for each gate. The design of the logical-AND gate used in this work is presented in [23]. The T-count for these logical gates is as follows: The Toffoli gate implementation designed in [18] has a T-count of 7, the temporary logical-AND gate has a T-count of 4 and the uncomputation gate has a T-count of 0.

### B. Carry Look Ahead Addition

Carry look ahead addition (CLA) has caught the attention of researchers because carry lookahead addition can perform addition in  $\mathcal{O}(log(n))$  time while alternative adders such as ripple carry addition requires  $\mathcal{O}(n)$  time. Thus a CLA circuit can complete the addition operation with a critical path depth of order  $\mathcal{O}(log(n))$  whereas the critical path for ripple carry addition has a depth of order  $\mathcal{O}(n)$ . The decrease in computation depth comes at the cost of added circuitry.

Given two n bit inputs a and b, the CLA circuit generates the sum of a and b by executing the CLA algorithm illustrated in Figure 4. The CLA algorithm is an established technique to quickly perform addition [40] [41]. The CLA algorithm can be divided into two basic steps: (i) implement generate  $(g_i)$  and propagate bits  $(p_i)$  for each bit of the inputs a and b and (ii) compute the sum s by computing  $c_{i+1} = p_i \wedge c_i \vee g_i$  for  $1 \leq i \leq n$ .

# Algorithm 1: Carry lookahead Addition

```

Function CLA(a, b)

Requirements:

//Takes 2 n bit values a and b as input.

//Returns the sum as an n+1 bit number s.

1

//create carry generate and carry propagate bits.

2

3

For i = 0 to n - 1

4

p_i = a_i \oplus b_i

5

g_i = a_i \wedge b_i

6

7

8

//synthesize sum.

9

10

c_0 = g_0 //no carry-in

11

s_0 = p_0

12

For i = 1 to n - 1

13

c_i = p_{i-1} \wedge c_{i-1} \vee g_{i-1}

14

s_i = c_i \oplus a_i \oplus b_i

15

End

16

s_n = p_{n-1} \wedge c_{n-1} \vee g_{n-1}

17

18

Return s

```

Fig. 4: The carry lookahead addition algorithm implemented by the circuits in this work.

# III. PROPOSED DESIGNS OF OUT-OF-PLACE QCLA CIRCUITS

We now show our proposed out-of-place QCLA circuits. The proposed QCLA circuits have lower T-count and qubit cost than existing works. The QCLA designs save T gates by using the temporary logical-AND gate, the existing uncomputation gate or proposed uncomputation gate where possible. The out of place FT-QCLA1 (or Out-FT-QCLA1) is optimized for T-count. We also propose an out of place FT-QCLA2 (or Out-FT-QCLA2) which is optimized for qubit cost. The design methodologies of the proposed QCLAs are generic and each can be used to implement a QCLA circuit of any size.

The proposed out-of-place QCLA circuits operate as follows: Given 2 values a and b (each n bits wide) stored in quantum registers A and B as well as n+1 ancillae stored in register X.  $X_0$  is set to 0 and the remaining locations are set to A (where  $A = \frac{1}{\sqrt{2}} \left( |0\rangle + e^{\frac{i\pi}{4}} |1\rangle \right)$ ). Lastly, Out-FT-QCLA2 requires a register Z with  $n-w(n)-\lfloor log(n)\rfloor$  elements (where  $w(n)=n-\sum_{y=1}^{\infty}\lfloor \frac{n}{2^y}\rfloor$  and is the number of ones in the binary expansion of n) all set to A (where  $A=\frac{1}{\sqrt{2}}\left(|0\rangle + e^{\frac{i\pi}{4}}|1\rangle\right)$ ). Out-FT-QCLA1 requires a register Z with  $3\cdot n-2\cdot w(n)-2\lfloor log(n)\rfloor$  ancillae set to A. At the end of computation, A and B are restored to their initial values and X will contain the sum of the addition of a and b. Lastly, Z is transformed into a register of classical states. These qubits can be restored to computational basis values for

reuse as ancillae.

This Section is organized as follows: The proposed design of Out-FT-QCLA1 is shown in Section III-A. The proposed design of Out-FT-QCLA2 is shown in Section III-B.

# A. Proposed Out-of-Place FT-QCLA1 Design (Out-FT-QCLA1)

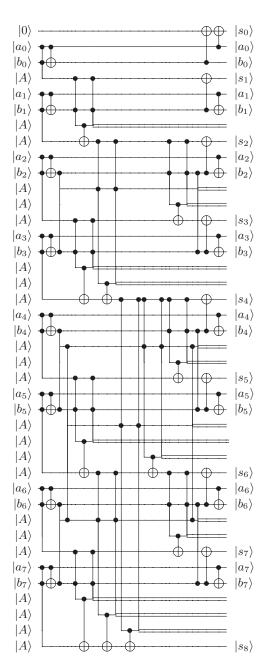

The out-of-place FT-QCLA1 (Out-FT-QCLA1) is optimized for T-count. The proposed QCLA is based on the quantum NOT gate, CNOT gate, logical AND gate and uncomputation gate. The steps of the proposed design methodology to realize Out-FT-QCLA1 are shown along with an illustrative example of the QCLA circuit in Figure 5.

- Step 1: For i = 0 to n-1, apply the logical AND gate at locations A[i], B[i] and an ancillae such that locations A[i] and B[i] are unchanged. The ancillae will have the result of computation. The ancillae will be renamed to the value g[i, i+1].

- **Step 2:** For i = 1 to n-1. At the locations A[i] and B[i] apply a CNOT gate such that A[i] is unchanged and location B[i] will have the result of computation. Location B[i] will be renamed p[i, i+1].

- Step 3 (P-rounds): We use a nested loop in this step. For t=1 to  $\lfloor log(n) \rfloor -1$  and For m=1 to  $\lfloor \frac{n}{2^t} \rfloor -1$ : At locations p[j,l], p[l,k] and at an ancillae apply a logical AND gate such that locations p[j,l] and p[l,k] are unchanged and the ancillae will have the result of computation. The ancillae will be renamed p[j,k]. The equation for indexes are  $j=2^t \cdot m, \ k=2^t \cdot m+2^t$ , and  $l=2^t \cdot m+2^{t-1}$ , respectively.

- Step 4 (G-rounds): We use a nested loop in this step. For t = 1 to ⌊log(n)⌋ and For m = 0 to ⌊n/2t⌋ − 1: At locations g[j, l], p[l, k], and g[l, k] apply a Logical AND gate and uncomputation gate pair such that locations g[j, l] and p[l, k] are unchanged and location g[l, k] will have the result of computation. Location g[l, k] is renamed to g[j, k]. The equation for indexes are j = 2t ⋅ m, k = 2t ⋅ m + 2t, and l = 2t ⋅ m + 2t − 1, respectively.

- Step 5 (C-rounds): We use a nested loop in this step. For  $t = \lfloor log\left(\frac{2\cdot n}{3}\right)\rfloor$  to 1 and For m=1 to  $\lfloor \frac{(n-2^{t-1})}{2^t}\rfloor$ : At locations g[0, l], p[l,k], and g[l,k] apply a Logical AND gate and uncomputation gate pair such that locations g[0, l] and p[l,k] are unchanged and location g[l,k] will have the result of computation. The equation for indexes are  $l=2^t\cdot m$  and  $k=2^t\cdot m+2^{t-1}$ .

- Step 6 (P-erase-rounds): We use a nested loop in this step. For  $t=\lfloor log(n)\rfloor-1$  to 1 and For m=1 to  $\lfloor \frac{n}{2^t}\rfloor-1$ .

- At locations p[j, l], p[l, k], and p[j, k] apply a uncomputation gate such that locations p[j, l] and p[l,k] are unchanged and location p[j, k] will be restored to its original value. The equation for indexes  $j = 2^t \cdot m$ ,  $k = 2^t \cdot m + 2^t$ , and  $l = 2^t \cdot m + 2^{t-1}$ .

- Step 7: This step has two sub-steps:

- **Sub-step 1:** For i = 1 to n-1, At locations p[i, i + 1] and g[0, i] apply a CNOT gate such that location

Fig. 5: Proposed out-of-place FT-QCLA1 (Out-FT-QCLA1) circuit for the case of adding two 8 bit values a and b.

- p[i, i +1] is unchanged and g[0, i] has the result of computation. After this step, location g[0, i] will have the sum bit  $s_i$ . The sum bit  $s_n$  is at location g[0, n].

- **Sub-step 2:** At locations p[0, 1] and an ancillae apply a CNOT gate such that location p[0, 1] and the ancillae will have the value B[0].

- Step 8: This step has two sub-steps:

- **Sub-step 1:** For i = 1 to n-1, At locations p[i, i + 1] and A[i] apply a CNOT gate such that A[i] is unchanged and p[i, i + 1] is restored to its original value  $(b_i)$ .

Sub-step 2: At locations Z and A[0] apply a CNOT gate such that A[0] is unchanged and Z will have the sum bit so

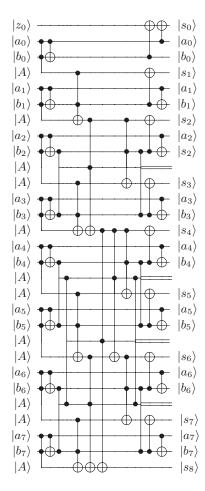

# B. Proposed Out-of-Place FT-QCLA2 Design (Out-FT-QCLA2)

Out-FT-QCLA2 is optimized for qubit cost. A trade-off for the reduced qubit count is an increase in the T gate cost of Out-FT-QCLA2. We reduce the qubit cost by replacing logical AND gate and uncomputation gate pairs with alternative Toffoli gate implementations such as the design in [18] were appropriate. To retain a low T-count, Out-FT-QCLA2 does still incorporate logical AND gate and uncomputation gate pairs. We save qubits because the logical AND gate and uncomputation gate pairs have a qubit cost of 4 while implementations of the Toffoli gate (like the design in [18]) have a qubit cost of 3. However, alternative Toffoli gate implementations have higher T-counts (such as the design in [18] with a T-count of 7). The design methodology for Out-FT-QCLA2 is identical to the methodology for Out-FT-QCLA1 except Step 4 and Step 5. In Step 4 and Step 5, Toffoli gates based on the design in [18] are used. An illustrative example of Out-FT-QCLA2 is in Figure 6.

Fig. 6: Proposed out-of-place FT-QCLA2 (Out-FT-QCLA2) for the case of adding two 8 bit values a and b.

# IV. PERFORMANCE OF PROPOSED OUT-OF-PLACE QCLA

# A. T-count analysis of Out-FT-QCLA-1

The T-count of Out-FT-QCLA-1 is shown for each Step of the proposed design methodology. Total T-count is determined by summing the T-count for each Step of the proposed design methodology. This design uses logical AND gate and uncomputation gate pairs to implement the Toffoli gate as shown in [19] and [23]. The pair has a T-count of 4. The total T-count is  $16 \cdot n - 8 \cdot w(n) - 8 \cdot \lfloor log(n) \rfloor - 4$  where  $w(n) = n - \sum_{y=1}^{\infty} \left \lfloor \frac{n}{2y} \right \rfloor$ .

- Step 1 uses n logical AND gates. The T-count for this step is  $4 \cdot n$ .

- Step 2 does not need T gates.

- Step 3 uses  $n w(n) \lfloor log(n) \rfloor$  logical AND gates. The T-count for this step is  $4 \cdot (n w(n) \lfloor log(n) \rfloor)$ .

- Step 4 uses n w(n) logical AND gate and uncomputation gate pairs. The T-count for this step is  $4 \cdot (n w(n))$ .

- Step 5 uses  $n \lfloor log(n) \rfloor 1$  logical AND gate and uncomputation gate pairs. The T-count for this step is  $4 \cdot (n \lfloor log(n) \rfloor 1)$ .

- Steps 6 through 8 does not need T gates.

#### B. T-count analysis of Out-FT-QCLA-2

The T-count of Out-FT-QCLA-2 is shown for each Step of the proposed design methodology. Total T-count is determined by summing the T-count for each Step of the proposed design methodology. This design uses the Toffoli gate implementation in [18] which has a T-count of 7. The total T-count is  $22 \cdot n - 11 \cdot w(n) - 11 \cdot \lfloor log(n) \rfloor - 7$  where  $w(n) = n - \sum_{y=1}^{\infty} \lfloor \frac{n}{2^y} \rfloor$ .

- Step 1 uses n logical AND gates. The T-count for this step is  $4 \cdot n$ .

- Step 2 does not need T gates.

- Step 3 uses  $n-w(n)-\lfloor log(n)\rfloor$  logical AND gates. The T-count for this step is  $4\cdot (n-w(n)-\lfloor log(n)\rfloor)$ .

- Step 4 uses n-w(n) Toffoli gates. The T-count for this step is  $7 \cdot (n-w(n))$ .

- Step 5 uses  $n \lfloor log(n) \rfloor 1$  Toffoli gates. The T-count for this step is  $7 \cdot (n \lfloor log(n) \rfloor 1)$ .

- Steps 6 through 8 does not need T gates.

## C. Cost Comparison of Proposed Out-of-place QCLAs

1) Cost Comparison in Terms of T-count: Table III indicates that all proposed out-of-place QCLAs have T-count costs of order  $\mathcal{O}(n)$ . The existing works also have T-counts of order  $\mathcal{O}(n)$ . All proposed QCLAs have a reduced T-count compared to the existing work. Of the proposed QCLAS, Out-FT-QCLA1 requires the fewest T gates.

The Out-FT-QCLA1 requires roughly 70.37% fewer T gates than the design by Babu et al., 38.46% fewer T gates than the design by Lisa et al., 54.29% fewer T gates than the designs by Draper et al., Thapliyal et al. and Trisetyarso et al.

The proposed Out-FT-QCLA2 requires 59.26% fewer T gates than the design by Babu et al., 15.38% fewer T gates than the design by Lisa et al., 37.14% fewer T gates than the designs by Draper et al., Thapliyal et al. and Trisetyarso et al.

TABLE III: Cost Comparison of Out-of-place QCLAs

| Design                                                                                                                        | T-count Equation                                                                                                  | Qubit Equation                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| Draper et al. ([28])<br>Trisetyarso et al. ([30])<br>Thapliyal et al. ([32])                                                  | $ 35n - 21w(n) - 21\lfloor log(n) \rfloor - 7  35n - 21w(n) - 21\lfloor log(n) \rfloor - 7  35n - 14 $            | $4n - w(n) - \lfloor log(n) \rfloor + 1$ $4n - w(n) - \lfloor log(n) \rfloor + 1$ $4n + 1$                       |

| Babu et. al. ([29]) <sup>1</sup><br>Lisa et al. ([31]) <sup>1</sup><br>Out-FT-QCLA1 <sup>2</sup><br>Out-FT-OCLA2 <sup>3</sup> | $54 \cdot n  26 \cdot n  16n - 8w(n) - 8\lfloor log(n) \rfloor - 4  22n - 11w(n) - 11 \lfloor log(n) \rfloor - 7$ | $12 \cdot n + 1$ $6 \cdot n + 1$ $6n - 2w(n) - 2\lfloor log(n) \rfloor$ $4n - w(n) - \lfloor log(n) \rfloor + 1$ |

$w(n) = n - \sum_{y=1}^{\infty} \left\lfloor \frac{n}{2^y} \right\rfloor$

2) Cost Comparison in Terms of Qubits: Table III indicates that all proposed out-of-place QCLAs have qubit costs of order  $\mathcal{O}(n)$ . The existing works also have a T-count of order  $\mathcal{O}(n)$ . Out-FT-QCLA1 requires  $2 \cdot n + w(n) + \lfloor log(n) \rfloor - 1$  additional ancillae compared to Out-FT-QCLA2. The added qubit cost of Out-FT-QCLA1 illustrates the trade-off between qubits and T gates that occurs when logical AND gate and uncomputation gate pairs are replaced by Toffoli gates in the QCLA implementation.

Out-FT-QCLA2 requires  $w(n) + \lfloor log(n) \rfloor$  fewer qubits than the design by Thapliyal et al. and has the same qubit cost as the designs by Draper et al. and Trisetyarso et al. Further, the proposed Out-FT-QCLA2 requires  $8 \cdot n + w(n) + \lfloor log(n) \rfloor$  fewer qubits than the design by Babu et al. and  $2 \cdot n + w(n) + \lfloor log(n) \rfloor$  fewer qubits than the design by Lisa et al. In contrast, the out-of-place Out-FT-QCLA1 requires  $6 \cdot n + 2 \cdot w(n) + 2 \cdot \lfloor log(n) \rfloor + 1$  fewer qubits than the design by Babu et al. and  $2 \cdot w(n) + 2 \cdot \lfloor log(n) \rfloor + 1$  fewer qubits than the work by Lisa et al.

## V. PROPOSED IN-PLACE QCLA CIRCUITS

We now show our proposed in-place quantum carry lookahead (QCLA) circuits. The proposed QCLA circuits have lower T-count and qubit costs than existing works. The proposed in-place FT-QCLA1 (or In-FT-QCLA1) and the proposed in-place FT-QCLA2 (or In-FT-QCLA2) save T gates by using the temporary logical-AND gate and uncomputation gate where possible. In-FT-QCLA2 is optimized for qubit cost and the In-FT-QCLA1 is optimized for T gates. The methodologies of the proposed in-place QCLAs are generic and each can be used to implement a QCLA circuit of any size.

The proposed QCLA circuits operate as follows: Given 2 values a and b (each n bits wide) stored in quantum registers A, B and an n bit register Z of ancillae set to a where  $A = \frac{1}{\sqrt{2}}\left(|0\rangle + e^{\frac{i\pi}{4}}|1\rangle\right)$ . Lastly, In-FT-QCLA2 QCLA requires a  $n-w(n)-\lfloor log(n)\rfloor$  (where  $w(n)=n-\sum_{y=1}^{\infty}\lfloor \frac{n}{2^y}\rfloor$  and is the number of ones in the binary expansion of n) bit register of ancillae (X) set to  $\frac{1}{\sqrt{2}}\left(|0\rangle + e^{\frac{i\pi}{4}}|1\rangle\right)$ . In contrast, register X of the In-FT-QCLA1 has  $3\cdot n-2\cdot w(n)-2\lfloor log(n)\rfloor$  ancillae set to A. At the end of computation, A is restored to their initial values and B will contain sum bits 0 through n-1 of the addition of a and b. For each QCLA, at the end of computation, Z will contain the sum bit  $s_n$  and the remaining locations in

Z are transformed into a register of classical states. These qubits can be restored to initial values for reuse as ancillae. In-FT-QCLA1 and In-FT-QCLA2 will transform the remaining locations in X to a register of classical states. These qubits can be restored to initial values for reuse as ancillae. This Section is organized as follows: In-FT-QCLA1 is shown in Section V-A. The In-FT-QCLA2 is shown in Section V-B.

# A. Methodology of the Proposed In-Place FT-QCLA1 (In-FT-QCLA1)

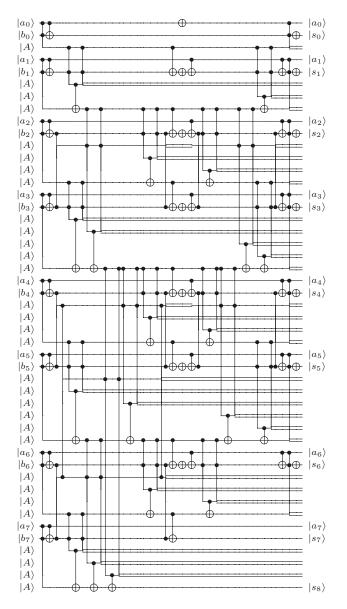

The T gate optimized fault tolerant QCLA is targeted for quantum hardware that can support the resource requirements needed for fault tolerant quantum computation. Because of the high implementation cost of the fault tolerant T gate, this QCLA is optimized for T-count. The proposed QCLA is based on the quantum NOT gate, CNOT gate, logical AND gate and the uncomputation gate presented in [23]. The steps of the methodology to implement the proposed In-FT-QCLA1 are shown along with an illustrative example of the QCLA circuit in Figure 7.

- Step 1: For i = 0 to n-1, apply the logical AND gate at locations A[i], B[i] and an ancillae such that locations A[i] and B[i] are unchanged. The ancillae will have the result of computation. The ancillae will be renamed to the value g[i, i + 1].

- Step 2: For i = 1 to n-1: At locations of A[i] and B[i] apply a CNOT gate such that location A[i] is unchanged and location B[i] will have the result of computation. Location B[i] is renamed to the value p[i, i+1].

- Step 3 (P-rounds): We use a nested loop in this step. For t=1 to  $\lfloor log(n) \rfloor -1$  and For m=1 to  $\lfloor \frac{n}{2^t} \rfloor -1$ : At locations p[j,l], p[l,k] and an ancillae apply a logical AND gate such that locations p[j,l] and p[l,k] are unchanged. The ancillae will have the result of computation and will be renamed to the value p[j,k]. The equations for the indexes are  $j=2^t\cdot m, \ k=2^t\cdot m+2^t$  and  $l=2^t\cdot m+2^{t-1}$ .

- Step 4 (G-rounds): We use a nested loop in this step.

For t = 1 to ⌊log(n)⌋ and For m = 0 to ⌊n/2t⌋ − 1:

At locations g[j, l], p[l, k], and g[l, k] apply a Toffoli gate such that locations g[j, l] and p[l, k] pass through unchanged. Location g[l, k] holds the result of computation

<sup>&</sup>lt;sup>1</sup> Circuits modified to remove garbage output. We use the method-

ology in [12] to remove the garbage output.

<sup>&</sup>lt;sup>2</sup> Out-FT-QCLA1 is optimized emphasizing T-count.

$<sup>^{\</sup>rm 3}$  Out-FT-QCLA2 is optimized emphasizing qubit cost.

Fig. 7: In-place FT-QCLA1 (In-FT-QCLA1) for the case of adding two 8 bit values a and b.

and will be renamed to the value  $\mathbf{g}[j,k]$ . The equations for the indexes are  $j=2^t\cdot m,\ k=2^t\cdot m+2^t,$  and  $l=2^t\cdot m+2^{t-1}.$

- Step 5 (C-rounds): We use a nested loop in this step. For  $t = \lfloor log\left(\frac{2n}{3}\right)\rfloor$  to 1 and For m=1 to  $\lfloor \frac{n-2^{t-1}}{2^t}\rfloor$ : At locations g[0, l], p[l,k], and g[l,k] apply a Toffoli gate such that locations g[0, l] and p[l,k] are unchanged. Location g[l,k] will hold the result of computation and will be renamed to the value g[0, k]. The equations for the indexes are  $l=2^t\cdot m$  and  $k=2^t\cdot m+2^{t-1}$ .

- Step 6 (P-erase-rounds): We use a nested loop in this step. For  $t=\lfloor log(n)\rfloor-1$  to 1 and For m=1 to  $\lfloor \frac{n}{2^t}\rfloor-1$ .

At locations p[j, l], p[l, k] and p[j, k] apply a uncomputation gate such that locations p[j, l] and p[l, k] are unchanged. Location p[j, k] will be restored to its original

- value. The equation for the indexes are  $j=2^t \cdot m$ ,  $k=2^t \cdot m+2^t$  and  $l=2^t \cdot m+2^{t-1}$ .

- **Step 7:** For i = 1 to n-1: at locations p[i, i + 1] and g[0, i] apply a CNOT gate such that location g[0, i] is unchanged. Location p[i, i + 1] will have the result of computation.

- Step 8: This step has the following two sub-steps:

- **Sub-step 1:** At location B[ $\theta$ ] apply a NOT gate. The location B[ $\theta$ ] will be renamed to the value p[ $\theta$ , 1]

- **Sub-step 2:** For i = 1 to n-2: At location p[i, i + 1] apply a NOT gate.

- Step 9: For i = 1 to n-2: At locations A[i] and p[i, i + 1] apply the CNOT gate such that location A[i] is unchanged and p[i, i + 1] has the result of computation.

- Step 10 (Reverse of P-erase-rounds): We use a nested loop in this step. For t=1 to  $\lfloor log(n) \rfloor -1$  and For m=1 to  $\lfloor \frac{n}{2^t} \rfloor -1$ :

At locations p[j,l], p[l,k] and an ancillae apply a logical AND gate such that locations p[j,l] and p[l,k] are unchanged. The ancillae will hold the result of computation and the ancillae is renamed to the value p[j,k]. The equations for the indexes are  $j = 2^t \cdot m$ ,  $k = 2^t \cdot m + 2^t$ , and  $l = 2^t \cdot m + 2^{t-1}$ .

• Step 11 (Reverse of C-rounds): We use a nested loop in this step. For t=1 to  $\lfloor \log\left(\frac{2n}{3}\right) \rfloor$  and For m=1 to  $\lfloor \frac{(n-2^{t-1})}{2^t} \rfloor$ :

At locations g[0,l], p[l,k], and g[0,k] apply a Toffoli gate such that locations g[0,l] and p[l,k] are unchanged. Location g[0,k] will have the result of computation and the location will be renamed to the value g[l,k]. The equations for the indexes are  $l=2^t \cdot m$  and  $k=2^t \cdot m+2^{t-1}$ .

• Step 12 (Reverse of G-rounds): We use a nested loop in this step. For  $t = \lfloor log(n) \rfloor$  to 1 and For m = 0 to  $\lfloor \frac{n}{2^t} \rfloor - 1$ :

At locations g[j,l], p[l,k] and g[j,k] apply a Toffoli gate such that locations g[j,l] and p[l,k] are unchanged. Location g[j,k] will have the result of computation and the location is renamed to the value g[l,k]. The equations for the indexes are  $j=2^t\cdot m,\ k=2^t\cdot m+2^t$  and  $l=2^t\cdot m+2^{t-1}$ .

- Step 13 (Reverse of P-rounds): We use a nested loop in this step. For  $t = \lfloor log(n) \rfloor 1$  to 1 and For m = 1 to  $\lfloor \frac{n-1}{2^t} \rfloor 1$ :

- At locations p[j,l], p[j,k], and p[l,k] apply a uncomputation gate such that locations p[j,l] and p[l,k] are unchanged. Location p[j,k] will be restored to its original value. The equations for the indexes are  $j=2^t \cdot m$ ,  $k=2^t \cdot m+2^t$  and  $l=2^t \cdot m+2^{t-1}$

- Step 14: For i=1 to n-2: At locations A[i] and p[i, i +1], apply a CNOT gate such that location A[i] would be unchanged and location p[i, i +1] will have the result of computation.

- Step 15: For i=0 to n-2: at locations A[i], p[i, i+1], and g[i, i+1], apply an uncomputation gate such that locations a[i] and p[i, i+1] are unchanged and g[i, i+1] will be restored to its original value.

- Step 16: Location p[n-1, n] has the sum bit  $s_{n-1}$  and g[0, n]

n] has the sum bit  $s_n$ . For i=0 to n-2: At location p[i, i +1] apply a NOT gate. Location p[i, i +1] will have the sum bit  $s_i$ .

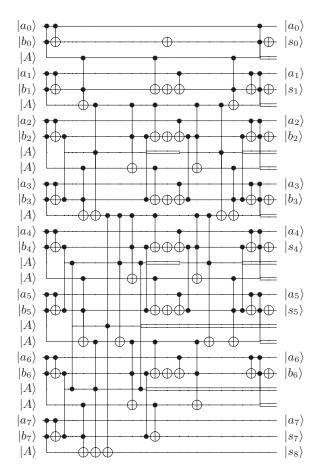

# B. Proposed In-Place FT-QCLA2 Design (In-FT-QCLA2)

In-FT-QCLA1 is optimized for T-count. A trade-off for the reduced T-count of In-FT-QCLA1 is an increase in the qubit cost of In-FT-QCLA1. We can reduce the qubit cost by replacing logical-AND gate and uncomputation gate pairs with alternative Toffoli gates implementations (such as the design in [18]) where appropriate. We save qubits because the logical AND gate and uncomputation gate pairs have a qubit cost of 4 while implementations like the design in [18] have a qubit cost of 3. However, alternative Toffoli gate implementations have higher T-counts (such as the design in [18] with a T-count of 7).

The steps of the methodology to implement In-FT-QCLA2 are identical to the methodology to implement In-FT-QCLA1. To implement In-FT-QCLA2, replace the logical AND gate, uncomputation gate pairs with a Toffoli gate in Step 4, Step 5, Step 11 and Step 12. An illustrative example of the In-FT-QCLA2 circuit is in Figure 8.

Fig. 8: In-place FT-QCLA2 (In-FT-QCLA2) for the case of adding two 8 bit values a and b.

# VI. PERFORMANCE OF PROPOSED IN-PLACE QCLA

## A. T-count analysis of In-FT-QCLA1

The T-count of In-FT-QCLA1 is shown for each Step of the proposed design methodology. Total T-count is determined by summing the T-count for each Step of the proposed design methodology. The total T-count is  $20 \cdot n - 8 \cdot w(n) - 4 \cdot \lfloor log(n) \rfloor - 8 \cdot w(n-1) - 4 \cdot \lfloor log(n-1) \rfloor - 8$  where  $w(n) = n - \sum_{y=1}^{\infty} \lfloor \frac{n}{2^y} \rfloor$ .

- Step 1 uses n logical AND gates. The T-count for this step is  $4 \cdot n$ .

- Step 2 does not need T gates.

- Step 3 uses  $n w(n) \lfloor log(n) \rfloor$  logical AND gates. The T-count for this step is  $4 \cdot (n w(n) \lfloor log(n) \rfloor)$ .

- Step 4 uses n w(n) Toffoli gates. The T-count for this step is  $4 \cdot (n w(n))$ .

- Step 5 uses  $n \lfloor log(n) \rfloor 1$  Toffoli gates. The T-count for this step is  $4 \cdot (n \lfloor log(n) \rfloor 1)$ .

- Steps 6 through 9 does not need T gates.

- Step 10 uses  $n-1-w(n-1)-\lfloor log(n-1)\rfloor$  logical AND gates. The T-count for this step is  $4\cdot (n-1-w(n-1)-\lfloor log(n-1)\rfloor)$ .

- Step 11 uses  $n \lfloor log(n-1) \rfloor 2$  Toffoli gates. The T-count for this step is  $4 \cdot (n \lfloor log(n-1) \rfloor 2)$ .

- Step 12 uses n-1-w(n-1) Toffoli gates. The T-count for this step is  $4 \cdot (n-1-w(n-1))$ .

- Steps 13 through 16 does not need T gates.

# B. T-count analysis of In-FT-QCLA2

The T-count of In-FT-QCLA2 is shown for each Step of the proposed design methodology. Total T-count is determined by summing the T-count for each Step of the proposed design methodology. The total T-count is  $40 \cdot n - 11 \cdot w(n) - 11 \cdot \lfloor log(n) \rfloor - 11 \cdot w(n-1) - 11 \cdot \lfloor log(n-1) \rfloor - 32$  where  $w(n) = n - \sum_{y=1}^{\infty} \lfloor \frac{n}{2^y} \rfloor$ .

- Step 1 uses n logical AND gates. The T-count for this step is  $4 \cdot n$ .

- Step 2 does not need T gates.

- Step 3 uses  $n w(n) \lfloor log(n) \rfloor$  logical AND gates. The T-count for this step is  $4 \cdot (n w(n) \lfloor log(n) \rfloor)$ .

- Step 4 uses n w(n) Toffoli gates. The T-count for this step is  $7 \cdot (n w(n))$ .

- Step 5 uses  $n \lfloor log(n) \rfloor 1$  Toffoli gates. The T-count for this step is  $7 \cdot (n \lfloor log(n) \rfloor 1)$ .

- Steps 6 through 9 does not need T gates.

- Step 10 uses  $n-1-w(n-1)-\lfloor log(n-1)\rfloor$  logical AND gates. The T-count for this step is  $4\cdot (n-1-w(n-1)-\lfloor log(n-1)\rfloor)$ .

- Step 11 uses  $n \lfloor log(n-1) \rfloor 2$  Toffoli gates. The T-count for this step is  $7 \cdot (n \lfloor log(n-1) \rfloor 2)$ .

- Step 12 uses n-1-w(n-1) Toffoli gates. The T-count for this step is  $7 \cdot (n-1-w(n-1))$ .

- Steps 13 through 16 does not need T gates.

# C. Cost Comparison of Proposed In-Place QCLAs

1) Cost Comparison in Terms of T-count: Table IV indicates that all proposed in-place QCLAs have T-count costs of

TABLE IV: Cost Comparison of In-Place QCLAs

| Design                                  | T-count Equation                                                                     | Qubit Equation                            |

|-----------------------------------------|--------------------------------------------------------------------------------------|-------------------------------------------|

| Draper et al. ([28])                    | $70n - 21w(n) - 21 \log(n)  - 21w(n-1) - 21 \log(n-1)  - 49$                         | $4n - w(n) - \lfloor \log(n) \rfloor + 1$ |

| Trisetyarso et al. ([30])               | 70n - 21w(n) - 21[log(n)] - 21w(n-1) - 21[log(n-1)] - 49                             | $4n - w(n) - \lfloor log(n) \rfloor + 1$  |

| Thapliyal et al. ([32])                 | $\frac{203}{4}n - 28$                                                                | 4n + 1                                    |

| Takahashi et al.([8])                   | $\stackrel{\scriptscriptstyle T}{\approx} 196n$                                      | $\approx 5n$                              |

| Takahashi et al.([36])                  | $\approx 49n$                                                                        | $\approx 5n$                              |

| Cheng et al. ([27])                     | $\frac{14}{6}n^3 + \frac{21}{6}n^2 - \frac{49}{6}n$                                  | $3 \cdot n + 1$                           |

| Mogenson (Design 1) <sup>1</sup> ([37]) | $\approx 84 \cdot n - 56$                                                            | $3 \cdot n - 1$                           |

| Mogenson (Design 2) $^2$ ([37])         | $\approx 84 \cdot n - 56$                                                            | $3 \cdot n - log(n) - 1$                  |

| In-FT-QCLA1 <sup>3</sup>                | $20n - 8w(n) - 8w(n-1) - 4 \log(n)  - 4 \log(n-1)  - 8$                              | $6n-2w(n)-2 \log(n) $                     |

| In-FT-QCLA2 <sup>4</sup>                | $40n - 11w(n) - 11\lfloor log(n)\rfloor - 11w(n-1) - 11\lfloor log(n-1)\rfloor - 32$ | $4n - w(n) - \lfloor log(n) \rfloor + 1$  |

order  $\mathcal{O}(n)$ . The existing works also have a T-count of order  $\mathcal{O}(n)$  with the exception of Cheng et al. where the T-count is of order  $\mathcal{O}(n^3)$ . Of the proposed designs, In-FT-QCLA1 has the lowest T-count.

In-FT-QCLA2 requires roughly 79.59% fewer T gates than the design by Takahashi et al. in [8], 18.37% fewer T gates than the design by Takahashi et al. in [36], 52.38% fewer T gates than the designs by Mogenson and 42.86% fewer T gates than the designs by Draper et al. and Trisetyarso et al. and 21.18% fewer T gates than the Thapliyal et al.

The Proposed In-place In-FT-QCLA1 requires roughly 89.80% fewer T gates than the design by Takahashi et al. in [8], 59.18% fewer T gates than the design by Takahashi et al. in [36], 76.19% fewer T gates than the design by Mogenson and 71.43% fewer T gates than the designs by Draper et al. and Trisetyarso et al. and 60.59% fewer T gates compared to the design by Thapliyal et al. The In-FT-QCLA1 and In-FT-QCLA2 also achieve an order of magnitude reduction in T gates compared to the design by Cheng et al.

2) Cost Comparison in Terms of Qubits: Table IV indicates that the proposed in-place QCLAs have qubit costs of order  $\mathcal{O}(n)$ . The existing works also have a T-count of order  $\mathcal{O}(n)$ . In-FT-QCLA2 requires w(n) + |log(n)| fewer qubits than the design by Thapliyal et al. and has the same qubit cost as the designs by Draper et al. and Trisetyarso et al. Further, In-FT-QCLA2 requires n + w(n) + |log(n)| - 1 fewer qubits than the designs by Takahashi et al. in [8] and [36]. In-FT-QCLA1 achieves its T gate savings with only an order  $\mathcal{O}(1)$  increase in qubits compared to the existing work.

#### VII. EXISTING WORK

Quantum carry lookahead adders (QCLA) have caught the attention of researchers and many have contributed many designs to the literature. Several designs such as [29] [31] target reversible computing and, therefore, produce significant garbage output. Other designs such as [42] present promising designs but they are not generic, prohibiting scaling the designs to alternative input qubit lengths. Designs that can be implemented on quantum hardware include [29] and [28]. In-place and out-of-place QCLAs have been proposed. We discuss the existing work for in-place and out-of-place QCLAs in separate sections.

## A. Out-of-Place QCLAs

Existing out-of-place QCLAs that can be implemented on quantum hardware include [29] [31] [28] [30] [32]. Table I summarizes important performance measures for these QCLAs. T-count, qubit cost, gates used and if the design produces garbage output are shown. The designs in [29] and [31] produce garbage output and must be made garbageless before use in quantum algorithms. As a result, the T-count cost is doubled and the qubit cost is increased by at least n+1. The reported T-count and qubit cost reflect the added cost from removing garbage outputs. The designs in [28] [30] and [32] have no garbage outputs and can be used as is. The design in [31] offers the lowest T-count in exchange for a  $\mathcal{O}(1)$  increase in qubit cost compared to existing works. The designs in [28] [30] and [32] achieve the lowest qubit cost with only a modest  $\mathcal{O}(1)$  increase in T-count compared to more T-count efficient works such as [31]. The design in [29] has the highest resource costs of the existing works. These are all interesting works that offer options with reduced qubit or T gate costs. However, with advances such as recent T gate efficient Toffoli gate implementations shown in [23], we have designed quantum QCLAs that have reduced T-count compared to these works. Further, we can design quantum QCLAs that offer T-count savings yet maintain comparable qubit costs.

#### B. In-Place QCLAs

Existing in-place QCLAs that can be implemented on quantum hardware include [28] [8] [30] [32] [27] and [37]. Table II summarizes important performance measures for these QCLAs. T-count, qubit cost, gates used and if the design produces garbage output are shown. All the designs have no garbage outputs and can be used as is. The in-place QCLA in [27] is based on CNOT, Toffoli gates and Multiple Control Toffoli gates. To decompose a multiple control Toffoli gate into quantum gates, first the multiple control Toffoli

$<sup>\</sup>begin{array}{l} w(n) = n - \sum_{y=1}^{\infty} \left \lfloor \frac{n}{2^y} \right \rfloor \\ ^1 \text{ Mogenson (Design 1) can accept a carry in bit } c_0. \end{array}$

<sup>&</sup>lt;sup>2</sup> Mogenson (Design 2) does not accept a carry in bit.

<sup>&</sup>lt;sup>3</sup> In-FT-QCLA1 is optimized emphasizing T-count.

<sup>&</sup>lt;sup>4</sup> In-FT-QCLA2 is optimized emphasizing qubit cost.

gate must be decomposed into Toffoli gates. One multiple control Toffoli gate translates into  $2 \cdot n - 3$  Toffoli gates which has a corresponding T-count of  $14 \cdot n - 21$  (using the Toffoli gate implementation in [18]). As a consequence, the design in [27] has a T-count of order  $\mathcal{O}(n^3)$  which becomes prohibitively costly for large n. The other existing works have more reasonable T gate costs of order  $\mathcal{O}(n)$ . Of these works, the designs by Mogenson have the lowest T-count and can perform their operation with only  $3\mathcal{O}(n)$  qubits. Among the works with T gate costs of order  $\mathcal{O}(n)$ , the design in [8] is the most costly in terms of T-count and qubit costs. Prior works such as [30] [32] and [37] present QCLAs that offer low T-count, low qubit cost and no garbage outputs. However, with the recent T gate efficient Toffoli gate implementations shown in [23], we have designed quantum QCLAs that have reduced T-count compared to these works. Further, we have designed quantum QCLAs that offer T-count reduction with only a modest  $\mathcal{O}(1)$  qubit cost increase compared to existing work.

#### VIII. CONCLUSION

In this work, we propose quantum circuits for carry lookahead addition. We present proposed designs for in-place QCLAs and out-of-place QCLAs. We present three designs for in-place QCLAs and three designs for the out-of-place QCLAs. The in-place FT-QCLA1 (In-FT-QCLA1) and out-ofplace FT-QCLA1 (Out-FT-QCLA1) are optimized for T-count. The in-place FT-QCLA2 (In-FT-QCLA2) and out-of-place FT-QCLA2 (Out-FT-QCLA2) are optimized for qubit cost while providing low T gate cost. The proposed QCLAs are based on NOT gates, CNOT gates, Toffoli gates, logical AND gates, uncomputation gates as well as a proposed uncomputation gate for near term quantum hardware. These designs are compared and shown to have reduced T gate and qubit costs compared to the existing work. We conclude that the proposed inplace QCLAs and out-of-place QCLAs can be used in larger quantum data-path circuits where gate count and/or qubit cost is of concern. We also conclude that the proposed QCLAs can be used to increase the amount of computation possible on quantum hardware with limited coherence times.

#### REFERENCES

- [1] A. M. Childs and N. Wiebe, "Hamiltonian simulation using linear combinations of unitary operations," *Quantum Information and Computation*, vol. 12, no. 11-12, pp. 901–924, 2012.

- [2] P. Shor, "Algorithms for quantum computation: discrete logarithms and factoring," in *Proceedings 35th Annual Symposium on Foundations of Computer Science*. IEEE Comput. Soc. Press, 1994, pp. 124–134.

- [3] L. Novo and D. Berry, "Improved hamiltonian simulation via a truncated taylor series and corrections," *Quantum Information and Computation*, vol. 17, no. 7-8, pp. 623–635, 2017.

- [4] S. Hallgren, "Polynomial-time quantum algorithms for pell's equation and the principal ideal problem," J. ACM, vol. 54, no. 1, pp. 4:1–4:19, Mar. 2007. [Online]. Available: http://doi.acm.org/10.1145/1206035.1206039

- [5] A. M. Childs and G. Ivanyos, "Quantum computation of discrete logarithms in semigroups," *Journal of Mathematical Cryptology*, vol. 8, no. 4, 2014.

- [6] L. Ruiz-Perez and J. Garcia-Escartin, "Quantum arithmetic with the quantum fourier transform," *Quantum Information Processing*, vol. 16, no. 6, pp. 1–14, 2017.

- [7] S. A. Cuccaro, T. G. Draper, S. A. Kutin, and D. Petrie Moulton, "A new quantum ripple-carry addition circuit," arXiv e-prints, Oct 2004. [Online]. Available: https://arxiv.org/abs/quant-ph/0410184

- [8] Y. Takahashi and N. Kunihiro, "A fast quantum circuit for addition with few qubits," *Quantum Information and Computation*, vol. 8, no. 6-7, pp. 636–649, 2008.

- [9] E. Muñoz-Coreas and H. Thapliyal, "Quantum circuit design of a t-count optimized integer multiplier," *IEEE Transactions on Computers*, vol. 68, no. 5, pp. 729–739, May 2019.

- [10] P. Selinger et al., The Quipper System, 2016, available at: http://www.mathstat.dal.ca/ selinger/quipper/doc/.

- [11] D. Wecker et al., Language-Integrated Quantum Operations: LIQUi|>, 2016, available at: https://www.microsoft.com/en-us/research/project/language-integrated-quantum-operations-liqui/.

- [12] C. H. Bennett, "Logical reversibility of computation," *IBM J. Res. Dev.*, vol. 17, no. 6, pp. 525–532, Nov. 1973. [Online]. Available: http://dx.doi.org/10.1147/rd.176.0525

- [13] S. Bravyi and A. Kitaev, "Universal quantum computation with ideal clifford gates and noisy ancillas," *Phys. Rev.* A, vol. 71, p. 022316, Feb 2005. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.71.022316

- [14] M. Amy, D. Maslov, and M. Mosca, "Polynomial-time t-depth optimization of clifford+t circuits via matroid partitioning," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 33, no. 10, pp. 1476–1489, Oct 2014.

- [15] A. Paler, I. Polian, K. Nemoto, and S. J. Devitt, "Fault-tolerant, high-level quantum circuits: form, compilation and description," *Quantum Science and Technology*, vol. 2, no. 2, p. 025003, 2017. [Online]. Available: http://stacks.iop.org/2058-9565/2/i=2/a=025003

- [16] X. Zhou, D. W. Leung, and I. L. Chuang, "Methodology for quantum logic gate construction," *Phys. Rev. A*, vol. 62, p. 052316, Oct 2000. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.62.052316

- [17] D. Gosset, V. Kliuchnikov, M. Mosca, and V. Russo, "An algorithm for the t-count," *Quantum Info. Comput.*, vol. 14, no. 15-16, pp. 1261–1276, Nov. 2014. [Online]. Available: http://dl.acm.org/citation.cfm?id=2685179.2685180

- [18] M. Amy, D. Maslov, M. Mosca, and M. Roetteler, "A meet-in-the-middle algorithm for fast synthesis of depth-optimal quantum circuits," IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 32, no. 6, pp. 818–830, June 2013.

- [19] C. Jones, "Low-overhead constructions for the fault-tolerant toffoli gate," *Phys. Rev. A*, vol. 87, p. 022328, Feb 2013. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.87.022328

- [20] D. Miller, M. Soeken, and R. Drechsler, "Mapping nev circuits to optimized clifford+t circuits," in *Reversible Computation*, ser. Lecture Notes in Computer Science, S. Yamashita and S.-i. Minato, Eds. Springer International Publishing, 2014, vol. 8507, pp. 163–175.

- [21] S. J. Devitt, A. M. Stephens, W. J. Munro, and K. Nemoto, "Requirements for fault-tolerant factoring on an atom-optics quantum computer," *Nature Communications*, vol. 4, 2013.

- [22] A. G. Fowler, M. Mariantoni, J. M. Martinis, and A. N. Cleland, "Surface codes: Towards practical large-scale quantum computation," *Phys. Rev. A*, vol. 86, p. 032324, Sep 2012. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.86.032324

- [23] C. Gidney, "Halving the cost of quantum addition," Quantum, vol. 2, p. 74, Jun. 2018. [Online]. Available: https://doi.org/10.22331/q-2018-06-18-74

- [24] R. V. Meter and M. Oskin, "Architectural implications of quantum computing technologies," *J. Emerg. Technol. Comput. Syst.*, vol. 2, no. 1, pp. 31–63, Jan. 2006.

- [25] IBM, *Quantum Computing IBM Q*, 2017, available at: https://www.research.ibm.com/ibm-q/.

- [26] C.-J. Yu, M. J. Graham, J. M. Zadrozny, J. Niklas, M. D. Krzyaniak, M. R. Wasielewski, O. G. Poluektov, and D. E. Freedman, "Long coherence times in nuclear spin-free vanadyl qubits," *Journal of the American Chemical Society*, vol. 138, no. 44, pp. 14678–14685, 2016, pMID: 27797487. [Online]. Available: https://doi.org/10.1021/jacs.6b08467

- [27] K.-W. Cheng and C.-C. Tseng, "Quantum plain and carry look-ahead adders," 2002. [Online]. Available: https://arxiv.org/abs/quant-ph/0206028

- [28] T. G. Draper, S. A. Kutin, E. M. Rains, and K. M. Svore, "A logarithmic-depth quantum carry-lookahead adder," *Quantum Information and Computation*, vol. 6, no. 4-5, pp. 351–369, 2006.

- [29] H. Babu, L. Jamal, and N. Saleheen, "An efficient approach for designing a reversible fault tolerant n-bit carry look-ahead adder." IEEE Computer Society, 2013, pp. 98–103.

- [30] A. Trisetyarso and R. Van Meter, "Circuit design for a measurement-based quantum carry-lookahead adder," *International Journal of Quantum Information*, vol. 8, no. 05, p. 843867, 2009.

- [31] N. J. Lisa and H. M. H. Babu, "Design of a compact reversible carry look-ahead adder using dynamic programming," in 2015 28th International Conference on VLSI Design, vol. 2015-, no. February. IEEE, 2015, pp. 238–243.

- [32] H. Thapliyal, H. Jayashree, A. Nagamani, and H. Arabnia, "Progress in reversible processor design: A novel methodology for reversible carry look-ahead adder," *Lecture Notes in Computer Science (including subseries Lecture Notes in Artificial Intelligence and Lecture Notes in Bioinformatics*), vol. 7420, pp. 73–97, 2013.

- [33] L. Jamal, M. M. Rahman, and H. M. H. Babu, "An optimal design of a fault tolerant reversible multiplier," in 2013 IEEE International SOC Conference, Sep. 2013, pp. 37–42.

- [34] S. K. Mitra and A. R. Chowdhury, "Minimum cost fault tolerant adder circuits in reversible logic synthesis," in 2012 25th International Conference on VLSI Design, Jan 2012, pp. 334–339.

- [35] P. Selinger, "Quantum circuits of *t*-depth one," *Phys. Rev. A*, vol. 87, p. 042302, Apr 2013. [Online]. Available: https://link.aps.org/doi/10.1103/PhysRevA.87.042302

- [36] Y. Takahashi, S. Tani, and N. Kunihiro, "Quantum addition circuits and unbounded fan-out," *Quantum Information and Computation*, vol. 10, no. 9-10, pp. 872–890, 2010.

- [37] T. Æ. Mogensen, "Reversible in-place carry-lookahead addition with few ancillae," in *Reversible Computation*, M. K. Thomsen and M. Soeken, Eds. Cham: Springer International Publishing, 2019, pp. 224–237.

- [38] H. Thapliyal and N. Ranganathan, "Design of efficient reversible logic-based binary and bcd adder circuits," *J. Emerg. Technol. Comput. Syst.*, vol. 9, no. 3, pp. 17:1–17:31, Oct. 2013. [Online]. Available: http://doi.acm.org/10.1145/2491682

- [39] P. Boykin, T. Mor, M. Pulver, V. Roychowdhury, and F. Vatan, "A new universal and fault-tolerant quantum basis," *Information Processing Letters*, vol. 75, no. 3, pp. 101 – 107, 2000. [Online]. Available: http://www.sciencedirect.com/science/article/pii/S0020019000000843

- [40] O. Spaniol, Computer arithmetic: logic and design, ser. Wiley series in computing. Chichester [West Sussex]; New York: Wiley, 1981.

- [41] B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs. New York: Oxford University Press, 2000.

- [42] A. N. Nagamani, C. K. Kavyashree, R. M. Saraswathy, C. H. V. Kartika, and V. K. Agrawal, "Design of reversible floating point adder for dsp applications," in *Proceedings of the International Conference on Signal, Networks, Computing, and Systems*, D. K. Lobiyal, D. P. Mohapatra, A. Nagar, and M. N. Sahoo, Eds. New Delhi: Springer India, 2016, pp. 123–135.