# HPC AI500: The Methodology, Tools, Roofline Performance Models, and Metrics for Benchmarking HPC AI Systems

#### AUTHORS' CONTRIBUTION

SECTION 1 IS CONTRIBUTED BY JIANFENG ZHAN AND ZIHAN JIANG. SECTION 2 IS CONTRIBUTED BY JIANFENG ZHAN, ZIHAN JIANG, AND FEI TANG. SECTION 3 IS CONTRIBUTED BY JIANFENG ZHAN. SECTION 4 IS CONTRIBUTED BY XINGWANG XIONG, ZIHAN JIANG, LEI WANG, WANLING GAO, AND JIANFENG ZHAN. SECTION 5 IS CONTRIBUTED BY ZIHAN JIANG, LEI WANG, CHUNJIE LUO, WANLING GAO, JIANFENG ZHAN, AND HONGXIAO LI. SECTION 6 IS CONTRIBUTED BY LEI WANG, ZIHAN JIANG, WANLING GAO, AND JIANFENG ZHAN. SECTION 7 IS CONTRIBUTED BY ZIHAN JIANG, XINGWANG XIONG, LEI WANG, WANLING GAO, CHUNXIN LAN, AND JIANFENG ZHAN. SECTION 8 IS CONTRIBUTED BY ZIHAN JIANG, LEI WANG, WANLING GAO, AND JIANFENG ZHAN. SECTION 9 ISCONTRIBUTED BY JIANFENG ZHAN.

BenchCouncil: International Open Benchmarking Council Chinese Academy of Sciences Beijing, China http://www.benchcouncil.org/HPCAI500/index.html

TECHNICAL REPORT NO. BENCHCOUNCIL-HPCAI500-2020-1 JUNE 30, 2020

# HPC AI500: The Methodology, Tools, Roofline Performance Models, and Metrics for Benchmarking HPC AI Systems\*

Zihan Jiang<sup>1,3</sup>, Lei Wang<sup>1,2</sup>, Xingwang Xiong<sup>1,3</sup>, Wanling Gao<sup>1,2</sup>, Chunjie Luo<sup>1,2</sup>, Fei Tang<sup>1,3</sup>, Chuanxin Lan<sup>1</sup>, Hongxiao Li<sup>1,3</sup>, and Jianfeng Zhan<sup>\*1,2,3</sup>

<sup>1</sup>State Key Laboratory of Computer Architecture, Institute of Computing Technology, Chinese Academy of Sciences, {jiangzihan, wanglei\_2011, xingwangxiong, gaowanling, luochunjie, lanchuanxin, tangfei, lihongxiao, zhanjianfeng}@ict.ac.cn <sup>2</sup>BenchCouncil (International Open Benchmarking Council) <sup>3</sup>University of Chinese Academy of Sciences

June 30, 2020

#### 1 Abstract

The recent years witness a trend of applying large-scale distributed deep learning algorithms in both business and scientific computing areas, whose goal is to speed up the training time to achieve a stateof-the-art quality. The HPC community feels a great interest in building the HPC AI systems that are dedicated to running those workloads. The HPC AI benchmarks accelerate the process. Unfortunately, benchmarking HPC AI systems at scale raises serious challenges. None of previous HPC AI benchmarks achieve the goal of being equivalent, relevant, representative, affordable, and repeatable.

This paper presents a comprehensive methodology, tools, Roofline performance models, and innovative metrics for benchmarking, optimizing, and ranking HPC AI systems, which we call HPC AI500 V2.0. We abstract the HPC AI system into nine independent layers, and present explicit benchmarking rules and procedures to assure equivalence of each layer, repeatability, and replicability. On the basis of AIBench–by far the most comprehensive AI benchmarks suite, we present and build two HPC AI benchmarks from both business and scientific computing: Image Classification, and Extreme Weather Analytics, achieving both representativeness and affordability. To ranking the performance and energy-efficiency of HPC AI systems, we propose Valid FLOPS, and Valid FLOPS per watt, which impose a penalty on failing to achieve the target quality. We propose using convolution and GEMM— the two most intensively-used kernel functions of AIBench to measure the upper bound performance of the HPC AI systems, and present HPC AI roofline models for guiding performance optimizations. The evaluations show our methodology, benchmarks, performance models, and metrics can measure, optimize, and rank the HPC AI systems in a scalable, simple, and affordable way. The specification, source code, datasets, and benchmarking data are publicly available from http://www.benchcouncil.org/benchhub/hpc-ai500-benchmark .

# 2 Introduction

The huge success of AlexNet [1] in the ImageNet [2] competition marks the booming success of deep learning (DL) in a wide range of commercial application areas. Many commercial fields, like image recognition, and natural language processing achieve unprecedented accuracy, even outperforming common

<sup>\*</sup>Jianfeng Zhan is the corresponding author.

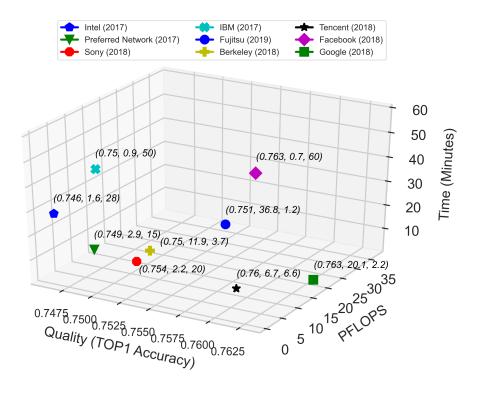

**Figure 1:** ImageNet/ResNet-50 training is one well-known showcase for optimizing HPC AI systems. It reports the performance in terms of a ternary tuple (achieved quality, PFLOPS, time-to-quality–minutes). The past witnesses the systems performance varying wildly from (74.6%, 1.6, 28) to (75.1%, 36.8, 1.2). Table 1 summarizes the utilized optimization approaches. As no equivalent benchmarking rule is stated, we can not objectively derive the performance edge of one system against the others.

human being's capability. Though it is much challenging to obtain high quality labeled scientific data sets, there is an increasing trend in applying DL in scientific computing areas [3–6].

With massive training data available, the recent years witness a trend of applying distributed DL algorithms at scale in both commercial and scientific computing areas. Motivated by these emerging HPC AI workloads, the HPC community feels a great interest in building HPC AI systems to reduce time-to-quality-the training time to achieve a convergent quality. For example, the Summit system [7] is built to tackle huge AI challenges. The benchmark accelerates the process [8,9], as it provides not only design inputs, but also evaluation and optimization metric and methodology [10,11]. However, there are several challenges in benchmarking HPC AI systems.

First, it is nontrivial to prove the equivalence of two AI benchmark implementations on different systems or even the same system with different scales. Equivalence quantifies how equivalent two benchmarks implementations on different systems or the same system with different scales. There are complex interactions among hardware and software systems, which is further aggravated by the AI algorithm complexity. Even for the same AI algorithms, there are huge parameters significantly impacting learning dynamics [9]. ImageNet/ResNet-50 (Image Classification) training is one well-known showcase for optimizing HPC AI systems. Table 1 summarizes the state-of-the-art and state-of-the-practice optimization approaches in ImageNet/ResNet-50 training. Unfortunately, without equivalent benchmarking rules explicitly stated, we can not objectively derive the performance edge of one system against the others from Fig. 1.

The second challenge inherits from the the conflict of two classical benchmarking methodologies with the emphasis of different requirements. On one hand, as no single benchmark or metric can measure the performance of computer systems on all applications [12], being relevant, representative, and diverse is

of paramount importance [10]. On the other hand, TOP500 [13] establishes the de facto super computer benchmark standard in terms of three defining characteristics: scalable, simple, and affordable.

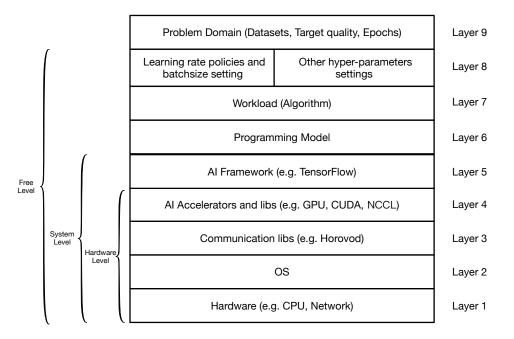

**Figure 2:** The equivalent perspective of HPC AI500 V2.0 Methodology. We abstract the HPC AI system into nine independent layers: put each layer under test while keeping other layers intact. We provide three high levels of benchmarking: hardware, system, and free: put the related layers together under test while keeping other layers intact with only allowed changes stated in the benchmarking rules.

In the AI domain, there are massive AI tasks and models with different performance metrics. For example, by far the most comprehensive and representative AI benchmark suite–AIBench [10, 11, 14, 15] contains seventeen AI tasks. It is not affordable to implement so many massive benchmarks and further perform benchmarking at scale. So what are the criteria for deciding the benchmarks that can fairly and objectively measure the HPC AI systems.

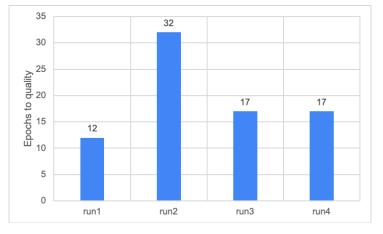

Third, the benchmark mandates being repeatable, while the nature of AI is stochastic, allowing multiple different but equally valid solutions [9]. The uncertainty of HPC AI is manifested by run-to-run variation in terms of epochs-to-quality and the effect of scaling training on time-to-quality [9, 16]. For the first time, Tang et al. [10] quantify the variations of seventeen AI benchmarks of AIBench. They found that the run-to-run variations vary from 0% to 38.46% in terms of the ratio of the standard deviation to the mean of the training epochs to achieve a convergent quality.

None of previous HPC AI benchmarks achieve the goal of being equivalent, relevant, representative, affordable, and repeatable. They either are not representative or even irrelevant to HPC AI workloads in terms of kernel functions [17, 18], or overlook the differences of HPC AI workloads between scientific and business computing [9], or fail to specify fair and equivalent benchmarking rules across different HPC AI systems [9]. Moreover, they fail to propose simple and AI domain-specific metric to score and rank HPC AI systems.

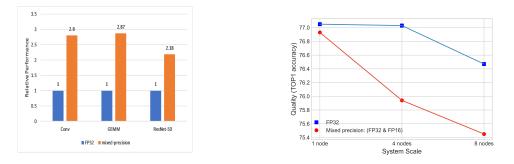

The micro benchmark like HPL-AI [18], which only contains LU decomposition, is affordable to perform a fair comparison of competing systems by isolating hardware and software from statistical optimizations [9]. However, we found it is irrelevant to most of AI workloads in Section 3.2. Moreover, the traditional micro or kernel benchmarking methodology, widely used in the HPC communities, can lead to misleading conclusion, as the mixed precision optimizations indeed improve the FLOPS of a micro benchmark like convolution, while significantly impact time-to-quality of an AI task like image classification as discussed in Section 3.2.

This paper presents HPC AI500 V2.0-a comprhensieve HPC AI benchmarking methodology, tools, performance models, and metrics. As shown in Fig. 2, we abstract the HPC AI system into nine

independent layers. To perform fair benchmarking across different systems or the same system with different scales, we present explicit benchmarking rules to assure equivalence of each layer, repeatability, and replicability of those two benchmarks. We put each layer under test while keeping the other layers intact. Also, We propose three high levels of benchmarking: hardware, system, and free (Fig. 2): put the related layers under test while keeping the other layers intact unless otherwise stated.

On the basis of AIBench , we present two benchmarks: Image Classification with state-of-the-art quality on the ImageNet dataset (business computing), and Extreme Weather Analytics (EWA) with state-of-the-art quality on the EWA dataset (scientific computing) to measure HPC AI systems. These two benchmarks represent two clusters of AI benchmarks–thirteen AI benchmarks from AIBench from perspectives of computing areas (business vs. scientific computing), diversity of model complexity (from 0.03 million to 68.39 million in terms of model parameters ), computational cost (from 0.09 MFLOPs to 157.80 GFLOPs in terms of a single forward computation), and convergence rate (from 6 epochs to 304 epochs). Moreover, our decision also takes into account their repeatablility, and whether these benchmarks have widely-accepted metrics or not.

To rank HPC AI systems, we propose two metrics, named Valid FLOPS, and Valid FLOPS per watt, to emphasise the vital importance of achieving the state-of-the-art quality, and an auxiliary metrics-time-to-quality.

We propose using convolution and GEMM (GEneral Matrix to Matrix Multiplication)-two most intensively-used kernel functions of AIBench to measure the upper bound performance of the HPC AI systems, and present corresponding single-node and distributed-system HPC AI roofline models for guiding performance optimizations.

The evaluations show our benchmarks can fairly measure the HPC AI systems in a scalable, simple, and affordable way. Our Roofline models are helpful to system optimizations. Our metrics can be used to rank HPC AI systems in a simple and visual manner.

# 3 The challenges of HPC AI benchmarking

The challenges of HPC AI benchmarking inherit from the complexity of benchmarking scalable hardware and software systems, which are further exaggerated by the uncertainty of AI algorithms.

#### 3.1 Equivalence

For the same AI algorithms, there are huge parameters significantly impacting learning dynamics [9]. Even for the same system with different scales, the interactions among system size, minibatch size, and learning dynamics have a significant impact on time-to-quality and computation overhead in terms of FLOPS [9, 19, 26]. So for the same AI task, it is non-trivial to prove the equivalence of two benchmark implementations on different systems or even the same system with different scales.

ImageNet/ResNet-50 training is one widely-used showcase for optimizaing HPC AI systems. Fig. 1 shows the systems performance varies wildly: the performance gap in terms of FLOPS is 50x. Accordingly, Table 1 summarizes the state-of-the-art and state-of-the-practice work on ImageNet training at scale. In addition to the system-level optimizations (e.g. more efficient communication typologies), some algorithm-level optimizations involve changing model architectures (e.g. optimizations on batch normalization) or learning rate policies, i.e., LARS [26]. As there are prohibitively complex interactions among hardware systems, software systems, and algorithms, previous work fails to clearly state the equivalent rules of each hardware or software layer for benchmarking HPC AI systems.

#### 3.2 Representative, Affordable, and Relevant

The second challenge inherits from the the conflict of two classical benchmarking methodologies with the emphasis of different requirements.

**Table 1:** The summary of the utilized optimization approaches in ImageNet/ResNet-50 training. The optimization approaches of each system are inconsistent or inequivalent. Please note that only the optimizations items *in italics* are allowed to change in the HPC AI500 benchmarking rules (defined in Section 6).

|                                    |                     | System-le                                                                                                                           | vel                                                      |                                    | Algorithm-level                                             |                                       |                                                             |                                                                       |  |

|------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------------------|-------------------------------------------------------------|---------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------------------|--|

|                                    | parallel<br>Mode    | Communication                                                                                                                       | Precision                                                | Data<br>Staging                    | Learning<br>Rate Policy                                     | Data<br>Argumentation                 | Model<br>Architecture                                       | Others                                                                |  |

| Facebook<br>[19]                   | Data<br>parallelism | Recursive halving<br>and doubling and<br>ring all-reduce.                                                                           | N/A                                                      | N/A                                | Linear scaling<br>and warm<br>up [20].                      | N/A                                   | N/A                                                         | Momentum<br>correction;<br>Data shuffling<br>based on the<br>workers. |  |

| Intel [21]                         | Data<br>parallelism | Intel MLSL [22]                                                                                                                     | N/A                                                      | N/A                                | Linear scaling<br>and warmup;<br>final collapse.            | N/A                                   | N/A                                                         | Collapsed<br>ensembles;<br>Dynamically<br>change<br>weight decay.     |  |

| <b>IBM</b> [23]                    | Data<br>parallelism | Topology aware                                                                                                                      | N/A                                                      | N/A                                | Linear<br>scaling,<br>warmup [20]                           | N/A                                   | N/A                                                         | Momentum<br>correction;<br>Data shuffling<br>based on the<br>workers. |  |

| <b>Berkeley</b><br>[24]            | Data<br>parallelism | Intel MLSL [25]                                                                                                                     | N/A                                                      | N/A                                | Linear scaling<br>and<br>warmup [20];<br>LARS [26].         | N/A                                   | N/A                                                         | N/A                                                                   |  |

| Preferred<br>Net-<br>works<br>[27] | Data<br>parallelism | Ring all-reduce;<br>Communication<br>compression.                                                                                   | N/A                                                      | N/A                                | Linear<br>scaling,<br>RMSprop<br>warmup, and<br>slow-start; | N/A                                   | Batch normal-<br>ization:<br>without<br>moving<br>averages. | N/A                                                                   |  |

| <b>Sony</b> [28]                   | Data<br>parallelism | 2D-Torus<br>all-reduce;<br>Communication<br>compression;<br>Communication<br>tensor fusion.                                         | Mixed<br>precision<br>training:<br>FP16 &<br>FP32        | N/A                                | Linear scaling<br>and<br>warmup [20];<br>LARS [26]          | Adding,<br>scaling,<br>rotations ,etc | Batch normal-<br>ization:<br>without<br>moving<br>averages. | N/A                                                                   |  |

| <b>Tencent</b><br>[29]             | Data<br>parallelism | Hierarchical<br>all-reduce;<br>Communication<br>compression;<br>Communication<br>tensor fusion.                                     | Mixed<br>precision<br>training:<br>FP16 &<br>FP32        | Efficient<br>input<br>pipeline     | Linear scaling<br>and<br>warmup [20];<br>LARS [26]          | N/A                                   | Batch normal-<br>ization:<br>eliminating<br>weight decay.   | N/A                                                                   |  |

| Google<br>[30]                     | Data<br>parallelism | 2D-Mesh<br>all-reduce;                                                                                                              | Mixed<br>precision<br>training:<br>BFLOAT16 [<br>& FP32. | Efficient<br>input<br>31] pipeline | Linear scaling<br>and<br>warmup [20];<br>LARS [26]          | Fused JPEG<br>decode and<br>cropping  | Distributed<br>batch<br>normalization                       | N/A                                                                   |  |

| Fujitsu<br>[32]                    | Data<br>parallelism | Communication<br>tensor fusion;<br>Optimal<br>scheduling by<br>grouping layers;<br>Calculate the<br>norms of layers in<br>parallel. | Mixed<br>precision<br>training:<br>FP16 &<br>FP32.       | N/A                                | Linear scaling<br>and<br>warmup [20];<br>LARS [26]          | N/A                                   | N/A                                                         | Label smooth-<br>ing [33]                                             |  |

On one hand, the SPECCPU [34], PARSEC [35], and TPC benchmarks, like TPC-DS [36] witness the paramount importance [10] of being representative and diverse, as no single benchmark or metric can measure the performance of computer systems on all applications [12].

On the other hand, TOP500 [13] defines three distinctive characteristics of the de facto super computer

benchmark standard: affordable, simple, and scalable. Affordable has two implications: first, the benchmark is easy to port to a new system or architecture; second, the benchmarking cost is affordable for measuring a systems at scale. Simple indicates the number of the metric is not only linear, orthogonal, and monotony [13], but also easily interpretable and understandable. Scalable means the benchmark can be used to measured different scales of system, and the problem size can be scaled up and down.

In the AI domain, there are massive AI tasks and models with different performance metrics. For example, AIBench [10] contains seventeen representative AI tasks, including Image Classification, Object Detection, Learning to Rank, Image Generation, Text-to-Text Translation, Image-to-Text, Image-to-Image Translation, Speech Recognition, Face Embedding, 3D Face Recognition, Recommendation, Video Prediction, Image Compression, 3D Object Reconstruction, Text Summarization, Spatial Transformer, and Neural Architecture Search. For HPC AI benchmarking, it is not affordable to implement so many massive benchmarks and further perform benchmarking at scale.

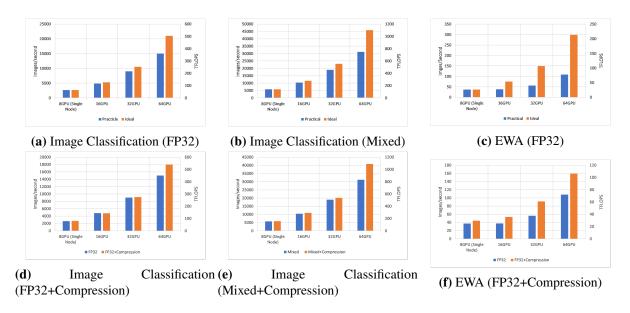

The traditional micro or kernel benchmarking methodology, which is widely in the HPC communities, can lead to misleading conclusion, as the mixed precision optimizations indeed improve the FLOPS of a micro benchmark like convolution, while significantly impact time-to-quality of an AI task like Image Classification. Fig. 4 shows that the mixed precision implementation increases the FLOPS of both micro and component benchmarks, while incurring accuracy drop as the system scale increases.

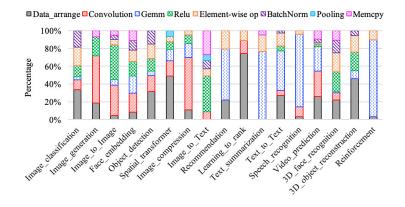

Last but not least, the relevancy [37] of a benchmark indicates that it must measure the peak performance and price/performance of systems when performing typical operations within that problem domain. The micro benchmark like HPL-AI [18], which only contains LU decomposition, is affordable to perform a fair comparison of competing systems by isolating hardware and software from statistical optimizations [9]. However, we found it is irrelevant to most of AI workloads in AIBench. As shown in Fig. 3, the dominated kernel functions are convolution and matrix multiplication.

**Figure 3:** The kernel function breakdown of the 17 representative AI workloads from AIBench [10], indicating the LU factorization is irrelevant.

**Figure 4:** With respect to the FP32 implementation, the mixed precision one speeds up 2x the FLOPS of two micro benchmarks: Conv and GEMM and a component benchmark: ResNet-50 (LEFT), while incurring deteriorated accuracy drop of ResNet-50 when the system scale increases (Right): 0.12% at 1 node while about 1% at 8 nodes.

#### 3.3 Repeatability

Repeatability [38, 39] refers to the variation in repeat measurements of different runs of the same benchmark implementation, by the same team, on the same system under the identical configurations.

Table 2 shows run-to-run variations of 17 benchmarks from AIBench varying from 0% to 38.46%. As shown in Fig. 5, the variation of 3d Face Recognition is high as 38.46%. There are diverse reasons for the uncertainty of different benchmarks. For NAS (network architecture searching), it constructs the network architecture by randomly sampling building blocks (e.g. convolution) from a predefined search space. In addition, the complex design itself, which involves many hyper-parameters, makes AutoML hard to evaluate [40].

| No.       | Component Benchmark        | Variation     | Repeat Times |

|-----------|----------------------------|---------------|--------------|

| DC-AI-C1  | Image Classification       | 1.12%         | 5            |

| DC-AI-C2  | Image Generation           | Not available | N/A          |

| DC-AI-C3  | Text-to-Text Translation   | 9.38%         | 6            |

| DC-AI-C4  | Image-to-Text              | 23.53%        | 5            |

| DC-AI-C5  | Image-to-Image             | Not available | N/A          |

| DC-AI-C6  | Speech Recognition         | 12.08%        | 4            |

| DC-AI-C7  | Face Embedding             | 5.73%         | 8            |

| DC-AI-C8  | 3D Face Recognition        | 38.46%        | 4            |

| DC-AI-C9  | Object Detection           | 0             | 10           |

| DC-AI-C10 | Recommendation             | 9.95%         | 5            |

| DC-AI-C11 | Video Prediction           | 11.83%        | 4            |

| DC-AI-C12 | Image Compression          | 22.49%        | 4            |

| DC-AI-C13 | 3D Object Reconstruction   | 16.07%        | 4            |

| DC-AI-C14 | Text Summarization         | 24.72%        | 5            |

| DC-AI-C15 | Spatial Transformer        | 7.29%         | 4            |

| DC-AI-C16 | Learning to Rank           | 1.90%         | 4            |

| DC-AI-C17 | Neural Architecture Search | 6.15%         | 6            |

| Table 2 | 2: The | run-to-run | variations | of seventeen | AIb | benchmarks c | of AIBench | [10] |

|---------|--------|------------|------------|--------------|-----|--------------|------------|------|

|---------|--------|------------|------------|--------------|-----|--------------|------------|------|

**Figure 5:** The worst unrepeatable benchmark from AIBench is 3D Face Recognition. Its run-to-run variation is high as 38.46%. The variation is defined as the ratio of the standard deviation to the mean of the training epochs to the achieved quality [10].

Without the equivalent benchmarking rules being explicitly stated, ImageNet/ResNet-50 training is not qualified for ranking the performance and energy efficiency of HPC AI systems.

# 4 Benchmarking Methodology

This section presents our methodology to achieve the goal of being equivalent, relevant, representative, affordable, and repeatable.

#### 4.1 Equivalence

To perform fair benchmarking across different systems or the same system with different scale, we propose two approaches to assure the equivalence.

First, as shown in Fig. 2, we abstract the system under test into nine independent layers, and put each layer under test while keeping the other layers intact unless otherwise stated.

Layer 1 is the hardware, including CPUs and networks. Layers 2, and 3 are the related system software, including the operating system (Layer 2), and the communication libraries (Layer 3). Layer 4 is the AI accelerators, i.e., GPU, and libraries, i.e., CUDA and cuDNN. Layer 5 is the AI framework, such as TensorFlow [41] and PyTorch [42]. Layer 6 refers to programming model, including parallel mode (data parallelism or model parallelism), and synchronous or asynchronous training. Layer 7 refers to the workloads used in HPC AI500 V2.0 benchmark. Layer 8 refers to hyper-parameters policies or settings. Layer 9 refers to problem domain, including datasets, target quality, and epochs.

Second, for the sake of simpleness, we propose three high levels of benchmarking and put several related layers together under test.

(1) The hardware level. This high level is for benchmarking HPC AI hardware systems and their related system software (Layers 1, 2, 3, 4). In this context, the other layers should be kept intact unless otherwise stated in the benchmarking rules. The benchmark users should compile the source code of the benchmark implementation, provided by the benchmark committee, on their hardware directly with allowed changes. Luo et al. [43] show that the same model on different frameworks has different accuracy. So in addition to the same data set, and AI model, we mandate that the benchmark implementations also use the same AI framework. The benchmark users can change hardware, OS, compiler settings, communication libraries. For the other layers, the benchmark users can only change parallel modes in Layer 6 or tune learning rate policies and batchsize settings in Layer 8. It is the benchmark committee' duty to assure the equivalence of Layers 6, 7, 8, 9 across different benchmark implementations upon the users' requests.

(2) The system level. Because of the portability cost, some benchmark users may opt for one specific AI framework without the support of the other, so specifying a fixed framework has a limited purpose. So in the system level, we put the hardware system in addition to the AI framework under the test (Layers 1, 2, 3, 4, and 5), which we call the system level. We mandate that the benchmark implementations use the same data set, and AI model. In addition to the changes allowed in the hardware level, the users are allowed to re-implement the algorithms on different or even customized AI framework (Layer 5). The other layers should be kept intact unless otherwise stated in the benchmarking rules.

The benchmark committee or an independent group need double-check the equivalence of Layers 6, 7, 8, 9 between the two benchmark implementations.

(3) The free level. In this high level, the specification of an AI task is stated in a paper-and-pencil manner separating from its specific implementation. That is to say, the same data set, target quality, and training epochs are defined in Layer 9 while the other layers are open for optimizations. The emphasis is advancing the state-of-the-art of software and hardware co-design, so the benchmark users can change any layers from Layer 1 to Layer 8 while keeping Layer 9 intact. Meanwhile, the benchmark users are encouraged to disclose the details.

#### 4.2 Representative vs. Affordable

We investigate and compare the state-of-the-art and state-of-the-practice of AI benchmark suites, including MLPerf [9], AIBench [10], Deep500 [44], HPC AI500 V1.0 [45]. We present the detailed analytics in

Section 9. Fortunately, we found the methodology of AIBench and its subset combines the merits of two methodologies discussed in Section 3.

On one hand, AIBench [10] is by far the most representative and comprehensive AI benchmark suite. It contains seventeen representative AI tasks. These workloads are diverse in terms of model complexity, computational cost, and convergent rate, computation and memory access patterns, hotspot functions, and other micro-architecture characteristics.

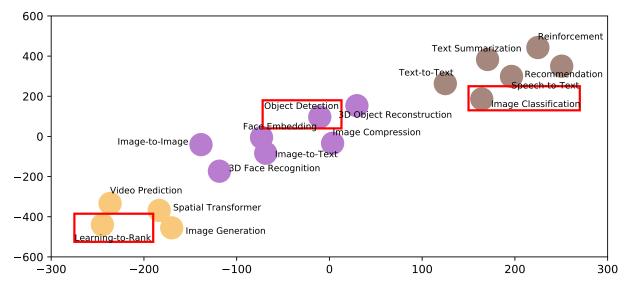

On the other hand, for affordability, AIBench carefully selected a minimum subset from the seventeen AI tasks from perspectives of model complexity, computational cost, convergent rate, run-to-run variation, and having Widely accepted evaluation metrics or not. As shown in Fig. 6, the AIBench subset includes three AI tasks–Image Classification, Object Detection, and Learning to Rank.

**Figure 6:** The three subset of AIBench with respect to the full benchmarks [10]. The clustering is based on the patterns of computation and memory access of seventeen AIBench component benchmarks, which described by five metrics listed in Table 3. For visualization, five dimensional data are downscaled into two-dimension ones by the t-SNE clustering approach [46].

| Metrics            | Meaning                                                                                                            |

|--------------------|--------------------------------------------------------------------------------------------------------------------|

| achieved_occupancy | The ratio of the average active warps per active cycle to the maximum number of warps provided by a multiprocessor |

| ipc efficiency     | The ratio of the executed instructions per cycle to the theoretical number.                                        |

| gld_efficiency     | The ratio of the requested global memory load throughput to the required global memory load throughput             |

| gst_efficiency     | The ratio of the requested global memory store throughput to the required global memory store throughput           |

| dram_utilization   | The utilization level of the device memory relative to the peak utilization                                        |

|  | Table 3: The m | etrics used | by the | t-SNE clust | tering ap | proach | [10]. |  |

|--|----------------|-------------|--------|-------------|-----------|--------|-------|--|

|--|----------------|-------------|--------|-------------|-----------|--------|-------|--|

Tang et al. [10] systematically quantify the run-to-run variation of seventeen AI tasks of AIBench in terms of the standard deviation to the mean of the training epochs to achieve a convergent quality. The variation of image classification, object detection, and learning ranking is 1.12%, 0%, and 1.90%, respectively, and they are the most repeatable benchmarks, which is the other reason for including them into the subset.

So we choose the AIBench subset as the HPC AI500 V2.0 candidate benchmarks for implementing scalable HPC AI benchmark tools.

#### 4.3 Repeatability and Replicability

In line with the experimental sciences discussed in [47], we propose the benchmarking procedures for assuring repeatability and replicability [48]. We adopt the definition similar to that of the Association for Computing Machinery [39]. Different from reproducibility, which requires changes, repeatability and replicability avoid changes [47].

Repeatability (same team): The benchmarking is performed on the same HPC AI system, using the same benchmark implementation under the same configurations, following the same benchmarking procedures, on multiple trials [47].

The team should submit the raw data of all trials, including the average numbers in addition to its variations. The variation is measured in terms of the ratio of the standard deviation to the mean of the numbers of all trials.

To mitigate the influence of stochastic of the AI algorithm, each benchmark should mandate the least valid runs of benchmarking. The number of all trials should be more than the least valid runs of benchmarking.

Replicability (Different team) [39]: The replicability refers to that the other team verifies the benchmarking results on the same HPC AI system, using the same benchmark implementation under the same configurations, following the same benchmarking procedures, on multiple trials.

For replicability, The benchmark committee or an independent group need verify the numbers on the same system, and report the raw data of all trials, including the average numbers in addition to its variation.

# 5 Benchmark Design and Implementation

In this section, we firstly illustrate how to choose the workloads according to our benchmarking methodology (Section 4). Then we present the datasets, AI models, and reference implementations of HPC AI500. Finally, we introduce the metrics.

#### 5.1 How to choose the workloads?

With respect to other AI benchmarks, there are two unique differences of HPC AI benchmarking. First, the challenges of HPC AI benchmarking inherit from the complexity of benchmarking scalable hardware and software systems at scale, i.e., tens of thousands of nodes, significantly different from that of IoT [43] or datacenter [11]. On this point, we need consider the cost of benchmarking at scale. Second, HPC AI domains cover both commercial and high performance scientific computing. Currently, business applications are pervasive. Because of the difficulty of recruiting qualified scientists to label scientific data, the applications in scientific computing lag behind but are promising. In general, the scientific data are often more complex than that of the MINST or ImageNet data: the shape of scientific data can be 2D images or higher-dimension structures with hundreds of channels, while the popular commercial image data like ImageNet often consist of only RGB [45]. So we should include the scientific data in the HPC AI benchmarks.

According to our benchmarking methodology discussed in Section 4, we choose the AIBench subset as the HPC AI500 candidate benchmarks for implementing scalable HPC AI benchmark tools.

#### 5.1.1 Representative and Affordable

As the broad HPC AI applications cover both scientific [5–7,49,50] and commercial field [27–30], we choose the most representative workloads and data sets from these two fields.

**EWA** is one of the pioneering work that uses deep learning algorithm to replace the rules predefined by human expert and achieve excellent results [5]. Most important of all, the goal of EWA is to identify various extreme weather patterns (e.g. tropical depression), which is essentially *object detection*—one of

the three benchmarks of the AIBench subset. In 2018, a deep learning based EWA implementation [7] won the Gordon Bell Prize, which is the first AI application to win this award.

**Image Classification** is widely used in many applications of *commercial fields*, which is a fundamental task in AI research. With the developing of large-scale deep earning, Image Classification has become a well-known showcase optimizing HPC AI systems [27–30], as summarized in Table 1. Image Classification is also one of the three benchmarks of the AIBench Subset.

We exclude Learn to Ranking because it has the lowest computation complexity in terms of FLOPS, which is only 0.08 MFLOPs in terms of a single forward computation. According to [10], Image Classification and Object Detection is more complex than that by one or two orders of magnitude, respectively.

#### 5.1.2 Repeatability

As the stochastic nature of AI, we need to ensure the repeatability by choosing relatively stable workloads in various AI tasks. According to the randomness analytics of AIBench [10], the two most repeatable AI benchmarks are Object Detection and Image Classification, whose variation is 0% and 1.12%, respectively. So they satisfies the property of a good benchmark–being repeatable.

#### 5.1.3 Scaling Characteristics

For comprehensive evaluation, the workloads we choose have distinct characteristics in terms of scaling characteristics. We use scaling ratio to depict the difficulty when scaling a workload from a single node to multiple nodes. As shown in Table 5, the scaling ratio of EWA and Image Classification is 16.85 and 117.76, respectively, reflecting very different scaling characteristics.

#### 5.1.4 Different Levels of Stringent Quality Requirements

When ranking HPC system, we consider not only its performance, but also the achieved quality. Different AI tasks have different levels of stringent quality requirement. Our benchmark decision also consider this factor. In our two benchmarks, EWA has much more stringent quality requirement than that of Image Classification.

#### 5.2 Data sets and AI models

#### 5.2.1 EWA

**Dataset.** The EWA dataset [50] is made up of 26-year climate data. The data of every year is available as one HDF5 file. Each HDF5 file contains two data sets: images and boxes. The images data set has 1460 example images (4 per day, 365 days per year) with 16 channels. Each channel is 768 \* 1152 corresponding to one measurement per 25 square km on earth. The box dataset records the coordinates of the four kinds of extreme weather events in the corresponding images: tropical depression, tropical cyclone, extratropical cyclone and the atmospheric river.

**Model.** Faster-RCNN targets real-time Object Detection [51]. As one of the latest models of an RCNN family [52,53], it deprecates the selective search that has been used in the previous RCNN version. Instead, Faster-RCNN proposes a dedicated convolutional neural network, named region proposal network (RPN), to achieve nearly cost-free region proposals. With such design, Object Detection is much faster. As a result, Faster-RCNN wins the 1st-place entries in ILSVRC'15 (ImageNet Large Scale Visual Recognition Competition).

Quality The target quality is MAP@[IoU = 0.5] = 0.35, which is our best training result. MAP means the average precision, which is a dedicated metric for object detection. The IoU means the intersection over union, used to measure how much our predicted boundary overlaps with the ground truth.

#### 5.2.2 Image Classification

**Dataset.** ImageNet [2] is large visual database designed for use in visual object recognition research. More than 14 million images have been hand-annotated according to the WordNet hierarchy. Both the original images and bounding boxes are provided. The data size is more than 100 GB.

**Model.** ResNet is a milestone in Image Classification [54], marking the ability of AI to identify images beyond humans in a particular domain. The spirit of ResNet is its success in reducing the negative impact of the degradation problem. The degradation problem means in the very deep neural network, the gradient will gradually disappear in the process of back-propagation, leading to poor performance. Therefore, with ResNet, it is possible to build a deeper convolution neural network and archive the higher accuracy. Researchers successfully build a ResNet with 152 layers. This ultra-deep model won all the awards in ILSVRC'15.

**Quality** The target quality is Top1 Accuracy = 0.763, which is the highest accuracy by far in training ImageNet/ResNet50 at scale [30]. The Top-1 accuracy refers to that only the output with the highest probability is the correct answer.

|  | Table 4: | The Summary | of Image D | ata Sets of H | IPC AI500 V2. | 0 Benchmarks |

|--|----------|-------------|------------|---------------|---------------|--------------|

|--|----------|-------------|------------|---------------|---------------|--------------|

| Dataset                          | Channels | Resolution | Size   |

|----------------------------------|----------|------------|--------|

| The extreme weather dataset [50] | 16       | 768*1052   | 558 GB |

| ImageNet dataset [2]             | 3        | 256*256    | 137 GB |

Table 5: The scaling ratio of HPC AI500 v2.0 workloads

| Workloads            | Comm (Parameters/Step) | Comp (GFLOPs/Step) | Comp/Comm<br>(GFLOPs/Parameters) |

|----------------------|------------------------|--------------------|----------------------------------|

| EWA                  | 41 million             | 691                | 16.85                            |

| Image Classification | 25 million             | 2944               | 117.76                           |

# 5.3 Reference Implementation

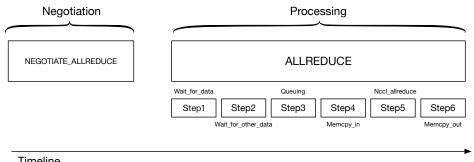

The reference implementation of HPC AI500 V2.0 benchmark is summarized as shown in Table 6. At present, we provide the implementations using TensorFlow [41], which is a popular deep learning framework in the HPC community [55]. For communication, we adopt Horovod [56] instead of the default GRPC protocol in TensorFlow, which is not extendable for large-scale cluster [57] due to the limitation of the master-slave architecture and socket-based communication. Horovod is a library originally designed for scalable distributed deep learning using TensorFlow. It implements *all\_reduce* operations using ring-based algorithms [58] and other high efficient communication algorithms that are widely used in the traditional HPC community.

# 5.4 Metrics and Scoring Rules

# 5.4.1 Valid FLOPS

We propose two metrics, called Valid FLOPS (in short VFLOPS) and Valid FLOPS per watt (in short VFLOPS per watt), to quantify the valid performance and energy efficiency that consider both the system throughput and model quality. The goal of these two metrics is to impose an penalty on failing to achieve a target quality. VFLOPS and VFLOPS per watt is calculated according to the formulas as follows.

$$VFLOPS = FLOPS * penalty\_coefficient$$

(1)

The penalty\_coefficient is used to penalize or award the FLOPS if the achieved quality is lower or greater than the target quality. Its definition is described as follows:

$$penalty\_coefficient = (achieved\_quality/target\_quality)^n$$

(2)

Here, *achieved\_quality* represents the actual model quality achieved in the evaluation. *target\_quality* is the state-of-the-art model quality that has been predefined in our benchmarks 6. The value of n is a positive integer, which is used to define the sensitivity to the model quality. The higher the number of n, the more loss of quality drop. As EWA has much more stringent quality requirement than that of Image Classification. We set n as 10 for EWA and 5 for Image Classification by default.

We propose VFLOPS per watt to evaluate energy efficiency.

| Problem<br>Domains      | Models                | Datasets     | Target Quality          | AI Frameworks  | Comm Lib <sup>1</sup> | AI Acc Lib <sup>2</sup> | Epochs |

|-------------------------|-----------------------|--------------|-------------------------|----------------|-----------------------|-------------------------|--------|

| EWA                     | FasterRCNN [51]       | EWA [50]     | mAP@[IoU=0.5]=0         | .35 TensorFlow | Horovod               | CUDA,<br>cuDNN,<br>NCCL | 50     |

| Image<br>Classification | ResNet50<br>v1.5 [54] | ImageNet [2] | TOP 1<br>Accuracy=0.763 | TensorFlow     | Horovod               | CUDA,<br>cuDNN,<br>NCCL | 90     |

#### Table 6: HPC AI500 V2.0 benchmark suite.

<sup>1</sup> Comm Lib refers to the communication libraries.

<sup>2</sup> AI acc lib refers to AI accelerators libraries.

# 6 Benchmarking Rules and Procedures

For the fairness and equivalence of benchmarking different HPC AI systems, a series of clear and unambiguous benchmarking rules are mandatory.

Our fundamental benchmarking rule is that we put each independent layer (Shown in Fig. 2) under test while keeping the other layers intact.

Furthermore, for the hardware-level and system-level benchmarking presented in Section 4, we give a detailed description from perspectives of each layer. Finally, we introduce the benchmarking procedures.

#### 6.1 The Benchmarking Rules for the Hardware Level

Based on our nine-layer model (Fig. 2), we specify the rules of each layer from top to bottom.

#### 6.1.1 Problem Domain Layer

- The dataset and target quality must be in accordance with the specification of HPC AI500 V2.0 benchmark that we have discussed in Section 5.

- The training epoch number should be the same like the reference implementation to guarantee the equivalent computational cost, namely 90 epochs for ImageNet and 50 epochs for EWA. Note that an epoch is an iteration over the entire data set, while a step refers to one update of the model parameters. The number of epochs is based on our experimental observation, and it should be updated in the future as well as the target qualities.

#### 6.1.2 Hyper-parameters Setting Layer

The rules of hyper-parameters setting layer include three parts, namely batchsize setting, learning rate policies, and other hyper-parameters settings.

**Batchsize Setting** The batchsize of a training step is allowed to change, to fully utilize the computing capability of the system.

**Learning Rate Policies** Previous work shows the increase of batchsize leads to a fall of the model quality [59]. In this context, many learning rate policies are proposed [19, 20, 26, 60]. With state-of-the-art learning rate policies, we can increase the training batch size to fully utilize the hardware's resources while preserving the model quality at the same time. As each learning rate policy has its limitation in terms of the maximum supporting batchsize, our rule allows benchmark users to propose new learning rate policies to fully utilize the hardware's resources. Meanwhile, we provide a default learning rate policy.

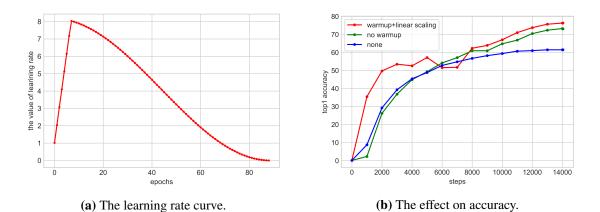

**The default learning rate policy:** The default learning rate policy of HPC AI500 is a linear scaling rule and a warm-up rule. The description is as follows:

- A linear scaling rule: multiply the base learning rate  $\eta$  by *k* when the batch size is multiplied by *k*. The goal of the linear scaling rule is to make SGD updates similar in both distributed and single-worker training [19].

- A warm-up rule: gradually increase the learning rate from a small to a large number until it equals to  $\eta \times k$ . After warmup, the learning rate starts the original learning rate schedule (e.g. cosine decay). The Warm up rule is proposed since using linear scaling rule alone breaks down when the weight of the neural network is changing rapidly in the early training stage [19].

Fig. 7a shows the learning rate changing curve after applying linear scaling and warm-up rules. We also perform a series of experiments to show the effect of this policy on model quality. As shown in Fig. 7b, linear scaling and warm-up rules can improves the top1 accuracy from 61.48% to 76.34% in Image Classification when the batchsize is 8192.

**Figure 7:** The learning rate curve and its effect on accuracy with linear scaling and warm-up rules. The benchmark is Image Classification and the system scale is 64 GPUs. The experiment configuration is consistent with that of Table 9. The batchsize is 8192.

**Other learning rate policies:** Except for the linear scaling and warmup scheme, using state-of-the-art learning rate policies (e.g. LARS [26] and LAMB [60]) are allowed. For new proposed ones, benchmarking users should open source their methods.

**Other Hyper-parameters Setting** Except for batchsize and learning rate policy, other hyper-parameters such as weight decay, momentum must be as the same as the reference implementation.

#### 6.1.3 Workload Layer

The AI algorithms in the workload must be the same as the reference implementation.

#### 6.1.4 Programming Model Layer

- Data parallelism and model parallelism are both allowed as long as the mathematical equivalence is preserved.

- Synchronous Stochastic Gradient Descent (SGD) must be used in training, since asynchronous SGD may a) introduce the randomness, b) destroy the mathematical equivalence, c) decrease the accuracy.

#### 6.1.5 AI Framework Layer

The AI framework must be the same as the reference implementation.

#### 6.1.6 Communication Libraries Layer

In synchronous communication, the workers in the cluster must wait until all the workers have finished, to proceed to next iteration. We allow different communication policies in an synchronous mode.

| Topologies         | Applications                        |  |

|--------------------|-------------------------------------|--|

| Butterfly          | OpenMPI [61]                        |  |

| Double binary tree | NCCL [62]                           |  |

| Ring               | Baidu DeepSpeech [63], Horovod [56] |  |

| Hierarchical ring  | Horovod                             |  |

Table 7: Some common communication typologies of allreduce.

- Based on AllReduce. Table 7 shows the common topology used in AllReduce implementations. The benchmark users are allowed to utilize these existing ones or propose new typologies according to the configuration of the systems. For example, the researchers from Lawrence Berkeley National Laboratory archived Exascale FLOPS by customizing a communication topology of AllReduce on SUMMIT [7].

- Based on MapReduce. The communication topology is determined by the implementation of MapReduce. The distributed training of Spark MLlib, SystemML, and REEF are all based on MapReduce. Users are allowed to implement customized MapReduce on their systems.

- Based on parameter server. It is mandatory that only the synchronous mode is used for the parameter server, while it also supports asynchronous training.

### 6.1.7 The AI Accelerators and Libraries Layer

- Benchmark users can choose the AI accelerator library to achieve the best performance out of the system.

- The single-precision floating point (FP32), half precision (FP16, BFLOAT16 [31]), and quantization (INT8, INT4) are allowed.

### 6.1.8 OS Layer

- Benchmark users can adjust OS configurations (such as CPU-Affinity setting) to achieve the best performance out of the system.

- Benchmark users can choose '-O2' compiler optimization option when compiling the benchmarks and the run time environment software.

#### 6.1.9 Hardware Layer

Benchmark users can adjust hardware configurations (such as hyper-threading setting, memory-prefetching setting) to achieve the best performance out of the system.

### 6.2 The Rules for The System Level

As discussed in Section 4.1, in the system level, we put the hardware system in addition to the framework under test. Therefore, in addition to the rules defined in the hardware level, benchmark users are allowed to reimplement the benchmark using a different or even customized AI framework at the AI framework layer.

# 6.3 The Benchmarking Procedures

#### 6.3.1 Deployment

Benchmark users need to download the source code of the benchmarks from the Benchcouncil Web site.

#### 6.3.2 Measurement

- Timing rules: timing starts when the workload reads the first batch training data and ends when the target epochs is reached.

- Runs: according to the variation of EWA and Image Classification from Table 2, the least number of runs is 5 and 10, respectively, to reduce run-to-run variation. For reporting, we drops the runs with the highest and lowest variations, than calculate the arithmetic mean of the remaining results.

- Benchmarking scores:

1) time-to-quality is the training time to its achieved quality;

2) FLOPS refers to the single-precision floating point operations (or equivalent operations) per second. The equivalent operations of the single-precision floating point operations include but not limited with FP16, BFLOAT16, INT8, and INT4;

3) VFLOPS and VFLOPS per Watt refers to the definitions in Section 5.4.1.

### 6.3.3 Reporting Procedure

The reporting results should include the following parts:

- The description of system under test, including but not limited to:

- 1) detail descriptions of parameters of CPUs and AI accelerators in a single-node;

- 2) detail descriptions of parameters of intra-node connection in a single-node;

- 3) detail descriptions of parameters of OS in a single-node;

- 4) detail descriptions of parameters of run time environment software in a single-node;

- 5) detail descriptions of parameters of inter-node connection in the system;

- 6) detail descriptions of parameters of run time environment software in the system.

- Benchmark configurations, including but not limited to:

- 1) all hyper-parameter setting;

- 2) detail descriptions of communication.

- Benchmarking scores, including time-to-quality, FLOPS, FLOPS per Watt, VFLOPS and VFLOPS per watt in all runs. These metrics should be submitted with the output log of the benchmark.

- The source code, relevant document, and running script should be uploaded to Benchhub, which is the official code repository managed by BenchCouncil.

The BenchCouncil community is responsible for checking the replicability of the reported results and reviewing the code.

#### 6.4 Why Equivalent Benchmarking Rules Matter?

A lot of previous work [27–30] focuses on accelerating Image Classification/ResNet-50 training. These efforts reduce the training time from hours to minutes. In this section, we take Image Classification as an example to explain why equivalent benchmarking rules matter for fair ranking HPC AI systems.

Batch normalization is a common effective method to improve the model generalization [64]. The trainable parameters of batch normalization  $\gamma$  and  $\beta$  are used to restore the representation ability of the network. Jia et al. [29] propose eliminating the weight decay on  $\gamma$  and  $\beta$  of batch normalization layer, which is a significant algorithm innovation in their work. We re-implement this algorithm-level optimization in accordance with [29]. Further, we use the VFLOPS as the metric to quantify the performance gap.

The benchmarking results are shown in Table 8. The accuracy gain and corresponding VFLOPS ratio are reported against the one without removing the weight decay. We find that as the system scale becomes larger, this optimization has a greater impact on the achieved quality. The accuracy gain is 0.45% on the scales of 16 and 32 GPUs, and then jumps to 1.38% on the scale of 64 GPUs, which is a notable improvement. We calculate the VFLOPS ratio according to the formula discussed in Sec 5.4 for each system scale. On the system scale of 64 GPUs, the VFLOPS ratio is high as 1.10, which is essentially the gain contributed solely by the algorithm innovation.

Consider the following case: we perform a comparison between two HPC AI systems using the same benchmark. One benchmark user leverages this algorithm innovation, while the other does not. If we do not exclude this case in the benchmarking rules, the benchmarking results will be unfair. That is the reason why we mandate that the other hyper-parameter settings in Layer 8 must keep intact as shown in Fig. 2.

Someone may question why we allow changing learning rate policies in Layer 8 in our rules as shown in Fig. 2. Just as discussed in Section 6, this is because to fully utilize the hardware resources, the users have to change the learning rate policies.

**Table 8:** The impact of removing the weight decay on batch normalization (BN) layer with different system scales. The benchmark is Image Classification and the accuracy is measured by Top-1 accuracy.

| System Scale | Batchsize | Accuracy Gain | VFLOPS Ratio <sup>1</sup> |

|--------------|-----------|---------------|---------------------------|

| 16 GPUs      | 2048      | +0.45%        | 1.03                      |

| 32 GPUs      | 4096      | +0.45%        | 1.03                      |

| 64 GPUs      | 8192      | +1.38%        | 1.10                      |

<sup>1</sup> The VFLOPS ratio refers to the ratio of the VFLOPS after the optimization against the one without optimization.

# 7 The HPC AI Roofline Performance Model

Given a specific HPC AI system, the theoretical peak performance number can be calculated according to hardware configurations. However, the theoretical peak one is hard to achieve. Hence, we need a performance model to help achieve the upper bound performance of an HPC AI system.

The previous Roofline model [65] is a upper bound performance model based on FLOPS and operation intensity (OI)–the total number of floating point instructions divided by the total byte number of memory accesses. With the aid of a Roofline model, we can decide a workload is memory-bound or compute-bound. Moreover, potential optimization strategies can be recommended according to the different ceilings of the Roofline model. To date, there is no such a performance model available for HPC-AI systems. In this section, we first analyze the distinctive characteristics of an HPC-AI system, and then propose an HPC-AI Roofline Model.

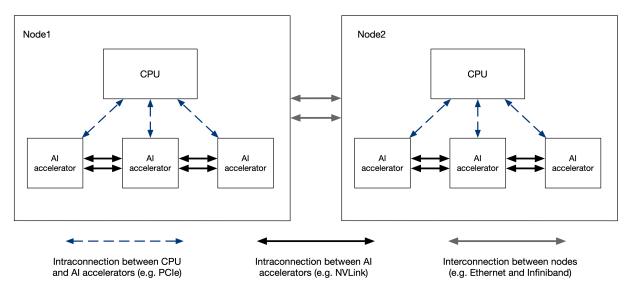

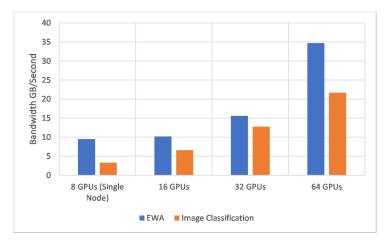

#### 7.1 The Architecture of an HPC AI System

An HPC AI system is a distributed system consisting of multiple nodes, each of which is heterogeneous and equipped with multiple CPUs and AI accelerators, as shown in Fig 8. The CPUs of each node are responsible for scheduling tasks and communicating with other nodes. The AI accelerators are responsible for AI calculations. Each AI accelerator loads or stores data from its memory units through memory channels. And all AI accelerators of each node are connected with a specific high-speed network (e.g. NVLink for GPUs). The distributed nodes are interconnected by a general high-speed network (e.g. high speed Ethernet). Hence, the communications include both inter-node and intra-node ones. Our analytics in Section 8.4 reveals the communication efficiency is one of the dominant factors that impact its performance.

Figure 8: The Architecture of an HPC AI system.

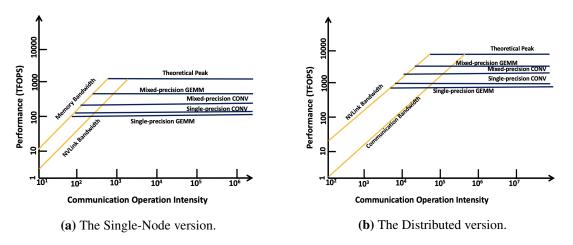

When proposing HPC-AI Roofline models, we consider the distinctive characteristics of HPC AI systems and the huge impact of communication efficiency on the performance of HPC AI systems. Significantly different from the original Roofline model [65], which emphasizes the impact of computation (FLOPS) and memory access (OI) on the overall performance, our HPC-AI Roofline model emphasizes the impact of communication and computation. We propose an innovative metric, named communication operation intensity (in short, COI), to replace OI. COI is defined as the total number of floating point instructions divided by the total byte number of communication.

Considering the different communication modes of inter-node communication (general high speed network) and intra-node communication (specific high speed network), our HPC-AI Roofline model is a combination of a single-node model with a distributed model.

We use FLOPS as the metric to depict the upper bound performance. Unlike the original Roofline model [65] using the double-precision floating point operations per second, we use the single-precision floating point operations or equivalent operations, such as mixed-precision floating point operations per second. This is because double-precision floating point operations are rarely required for deep learning workloads, while single-precision or mixed-precision floating point operations are prevalent.

Intentionally, we do not choose VFLOP as the performance metric. This is because the purpose of the Roofline model is to decide the performance bound of the workload and guide its system-level and hardware-level optimizations. Instead, VFLOP is a composite metric reflecting both performance and accuracy to rank the HPC AI systems.

#### 7.2 The Single-Node HPC-AI Roofline Model

The single-node HPC-AI model is formulated as follows.

$$FLOPS_{Attained} = min(FLOPS_{Peak}, ComBand_{Peak} * COI)$$

(3)

$ComBand_{Peak}$  is the theoretical peak communication bandwidth of a single-node HPC AI system, which is the bandwidth of interconnections among AI accelerators.  $FLOPS_{Peak}$  is the theoretical peak FLOPS of a single-node HPC AI system, which is the aggregate theoretical peak FLOPS of all AI accelerators. The communication operation intensity–COI–is obtained by COI = FLOPs/CT where CT is short for the communication traffic–the total number of communication bytes among AI accelerators. To more accurately reflect the performance bottleneck of a given workload, different ceilings are added to help locate the bottlenecks and provide potential optimization recommendations.

We use CONV (convolution) and GEMM (GEneral Matrix to Matrix Multiplication) to measure the upper bound performance of the system. On one hand, they are two most frequently-appearing kernel functions of the seventeen benchmarks of AIBench; On the other hand, their computing patterns, i.e., their multiplying and adding calculations can be fused, allow them to make more efficient use of accelerators. *FLOPS*<sub>Attained</sub> is the performance that a workload can attain, and the attained performance bound of a given workload under ceilings is formulated as follows.

$$FLOPS_{Attained} = Min(FLOPS_{Ceiling}, ComBand_{Ceiling} * COI)$$

(4)

#### 7.3 The Distributed HPC-AI Roofline Model

For the distributed model, we propose using COI (communication operation intensity) and FLOPS to depict the upper bound performance. The model is formulated as follows.

$$FLOPS_{Attained} = Min(FLOPS_{Peak}, ComBand_{Peak} * COI)$$

(5)

The *ComBand*<sub>Peak</sub> is the theoretical peak communication bandwidth of the distributed system, i.e., the theoretical bandwidth of the high speed Ethernet. *FLOPS*<sub>Peak</sub> is the theoretical peak FLOPS of the distributed system, which is the aggregate theoretical FLOPS of all AI accelerators in the distributed system. The communication operation intensity–*COI* is obtained by COI = FLOPs/CT, where the communication traffic–*CT* is the total byte number of communications among all AI accelerators in the distributed system. To more accurately reflect the performance bottleneck of a given workload, we add several ceilings, and the attained performance bound of a given workload is formulated as follows.

$$FLOPS_{Attained} = Min(FLOPS_{Ceiling}, ComBand_{Ceiling} * COI)$$

(6)

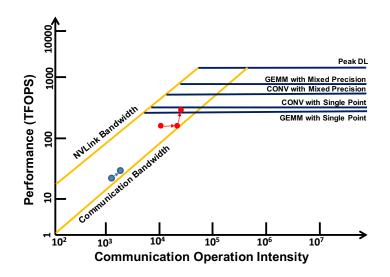

Figure 9: The HPC-AI Roofline Model.

# 7.4 A Case Study of the HPC AI Roofline Models

We perform a case study of our HPC AI Roofline models on an experimental system. The system consists of eight nodes, each of which is equipped with one Intel(R) Xeon(R) Platinum 8268 CPU and eight NVIDIA Tesla V100 GPUs. Each GPU in the same node has 32 GB HBM memory, connected by NVIDIA NVLinka high-speed GPU interconnection that has theoretical peak 300GB/s bi-directional bandwidth. The nodes are connected with an Ethernet networking with a bandwidth of 10 Gb/s. Each node has 1.5 TB of system memory and 8 TB of NVMe SSD disk.

#### 7.4.1 A Case Study of the Single-Node HPC-AI Roofline Model

As shown in Fig. 9a, the y-axis is the performance in terms of floating-point operations per second, while the x-axis is the communication operation intensity—the floating-point operations divided by the total byte number of communication. In Fig. 9a, the peak computation rate forms the 'flat' part, while the communication bandwidth turns into the 'slanted' part. So, if the communication operation intensity is lower, the workload is communication-bound, under the slanted part of the roofline. With the sufficient communication operation intensity, the workload is compute-bound.

We add four computation ceilings: mixed-precision GEMM (the performance of the mixed-precision floating point implementation of GEMM), single-precision GEMM, mixed-precision CONV, and single-precision CONV. Single-precision setting is commonly-used in the AI domain, while mixed-precision is one of the optimization features on some advanced AI accelerators.

The best-case performance of eight GPUs is that the communication and computation totally overlap, and the memory bandwidth becomes the bottlenecks. We add one communication ceiling – memory bandwidth. In Fig. 9a, the theoretical peak number of mixed-precision FLOPS, the mixed-precision GEMM ceiling, the mixed-precision CONV ceiling, the single-precision GEMM ceiling, the single-precision CONV ceiling is 1040 TFLOPS, 636 TFLOPS, 176 TFLOPS, 115 TFLOPS, 112 TFLOPS, respectively. Note that the gap between the theoretical perk number with the actual one is because that the performance of CONV and GEMM is affected by the dimension and sparsity of input data, NCHW format and output channels. Additionally, the convolution kernel also impacts the performance of CONV greatly. The different input size of CONV and GEMM leads to different performance numbers. The NVLink ceiling is the theoretical peak bandwidth of the communications among GPUs–300 GB/S, and the memory bandwidth ceiling is the theoretical peak bandwidth of the memory–1134 GB/S.

### 7.4.2 A Case Study of the Distributed HPC-AI Roofline Model

Our system consists of eight nodes. All the GPUs in the same node are connected by NVIDIA NVLink, and the nodes are connected with an Ethernet networking. In Fig. 9b, the peak computation rate forms the

#### Table 9: Hardware configuration details.

| System Conf                             | igurations       | Single-Node Configurations |                                       |  |  |

|-----------------------------------------|------------------|----------------------------|---------------------------------------|--|--|

| Num of Nodes                            | 8                | СРИ Туре                   | Intel(R) Xeon(R) Platinum<br>8268 CPU |  |  |

| GPUs per Node                           | 8                | Memory                     | 1.5TB, DDR4                           |  |  |

| Total num of GPUs                       | 64               | Disk                       | 8TB, NVxMe SSD                        |  |  |

| Peak Theoretical<br>performance (FP32)  | 960 TFLOPS       | GPU Type                   | Nvidia Tesla V100                     |  |  |

| Peak Theoretical<br>performance (Mixed) | 7680 TFLOPS      | GPU Memory                 | 32GB, HBM                             |  |  |

| Interconnection                         | Ethernet, 10Gb/s | Intraconnection            | NVLink                                |  |  |

'flat' part, while the communication bandwidth (Ethernet networking bandwidth) turns into the 'slanted' part. The theoretical Peak FLOPS of the system is 8320 TFLOPS, and the communication ceiling is 1.2 GB/S.

We add four computation ceilings: mixed-precision GEMM, single-precision GEMM, mixed-precision CONV, and single-precision CONV. Their numbers are 5091, 920, 2376, and 976 TFLOPS, respectively.

The best-case performance of the HPC-AI system is that the communications are within the nodes. So we add one communication ceilings–NVLink bandwidth. The NVLink bandwidth ceiling is 300 GB/S.

# 8 Evaluation

In this section, we introduce the experimental configurations in Section 8.1, present how to measure FLOPs in Section 8.2. Then, we perform an in-depth performance analysis of a single node in Section 8.3 and multiple nodes in Section 8.4, respectively. Finally, we demonstrate how to use our roofline model to guide the optimizations of the HPC AI systems in Section 8.5.

#### 8.1 Experimental Configurations

Our experiments are conducted on an HPC AI system, consisting of eight nodes, each of which is equipped with one Intel(R) Xeon(R) Platinum 8268 CPU and eight NVIDIA Tesla V100 GPUs. Each GPU in the same node has 32GB HBM memory, connected by NVIDIA NVLink–a high-speed GPU interconnection whose theoretical peak bi-directional bandwidth is 300GB/s. The nodes are connected with an Ethernet networking with a bandwidth of 10 Gb/s. Each node has 1.5 TB system memory and 8 TB NVMe SSD disk.

The details of the architecture of each NVIDIA Tesla V100 GPU–NVIDIA Volta architecture are as follows. The NVIDIA Volta architecture is equipped with 640 Tensor Cores to accelerate GEMM and convolution operations. Each Tensor Core performs 64 floating-point fused-multiply-add (FMA) operations per clock, delivering up to 125 TFLOPs of theoretical peak performance. When performing mixed precision training with a Tensor Core, we uses FP16 for calculation and FP32 for accumulation [18].

We use TensorFlow v1.14, compiled with CUDA v10.1 and cuDnn v7.6.2 backend. We use Horovod v0.16.4 for synchronous distributed training, compiled with OpenMPI v3.1.4 and NCCL v2.4.8. NCCL is short for the NVIDIA Collective Communications Library, which is a closed-source library of multi-GPU collective communication primitives that are topology-aware.

#### 8.2 Performance Measurement

The source-code level measurement of FLOPs is difficult for a complex AI model implemented with a complex AI framework. The mainstream frameworks like TensorFlow and PyTorch adopt computational graphs and map them to specific computing engines, e.g., GPU and cuDNN. This process invokes numerous kernels, and each of which contributes to a portion of FLOPs. Hence, we need to figure out the

implementation of each invoked kernel to obtain the FLOPs of an entire AI model. Unfortunately, the source code is not publicly available as the NVIDIA libraries, like CUDA and cuDnn are not open source.

We use NVProf [66]–a performance analysis tool for NVIDIA GPUs–to measure the FLOPs in our experiments. NVProf can be used to collect the profiling data from hardware performance counters. But it has a huge overhead, slowing down the the execution time more than hundreds of times. Thus, profiling the whole training session of a deep learning model is prohibitively costly. The previous work [67,68] has found that each iteration of model training has the same computation logic and the iteration number has little impact on micro-architectural behaviors. So we sample a partial training set and calculate the FLOPs for efficiency. As the image size of the EWA and ImageNet datasets is 13.14k, and 1280k, respectively, so we sample 500 images and 12800 images from the EWA and ImageNet datasets, respectively. The throughput is calculate according to the following equation: *Throughput* =  $N \times R \times C$ . Here N is the number of images processed by each training process per second, R is the total number of ranks (the number of training processes), and C is the FLOPs per image.

| Table 10: The FLOPs per in | image. |

|----------------------------|--------|

|----------------------------|--------|

| Dataset              | Image Sample Size | Total FLOPs    | FLOPs Per Image |

|----------------------|-------------------|----------------|-----------------|

| EWA                  | 500               | 345.66 TFLOPs  | 691 GFLOPs      |

| Image Classification | 12800             | 2877.06 TFLOPs | 23 GFLOPs       |

Table 11: The performance summary of a single node

| Workloads            | Models         | Precision                  | GFLOP<br>(Per Image) | Throughput<br>(Images/s) | Attainable Performance <sup>1</sup><br>(TFLOPS) | Achieved Performance Ratio <sup>2</sup><br>(%) |

|----------------------|----------------|----------------------------|----------------------|--------------------------|-------------------------------------------------|------------------------------------------------|

| Image Classification | ResNet-50 V1.5 | FP32<br>Mixed <sup>3</sup> | 23                   | 2624<br>5734             | 58<br>126                                       | 48<br>105                                      |

| EWA                  | FasterRCNN     | FP32                       | 691                  | 46                       | 31                                              | 26                                             |

<sup>1</sup> The attainable performance refers to the performance obtained in the testing.

<sup>2</sup> The achieved performance ratio refers to the ratio of the attainable performance against the theoretical peak performance (FP32).

<sup>3</sup> Mixed refers to FP32 & FP16 mixed precision.

|                         | Categories          | Convolution | GEMM  | Batch<br>Normalization | Element<br>Wise | Pooling | Memcpy | NCCL<br>Allreduce | Data<br>Arrangement | Overall GPU<br>Utilization (%) |

|-------------------------|---------------------|-------------|-------|------------------------|-----------------|---------|--------|-------------------|---------------------|--------------------------------|

| Image                   | Time (%)            | 35.02       | 25.54 | 13.47                  | 15.51           | 0.73    | 2.62   | 5.63              | *                   | 93.90                          |

| Classification          | IPC                 | 3.17        | 2.14  | 0.91                   | 0.34            | 1.54    | *      | 0.22              | *                   |                                |

| FP32                    | Dram<br>Utilization | 3.34        | 3.74  | 6.06                   | 4.45            | 6.32    | *      | *                 | *                   |                                |

| (                       | Time (%)            | 22.18       | 8.76  | 14.92                  | 12.86           | 1.85    | 7.14   | 6.62              | 15.61               |                                |

| Image<br>Classification | IPC                 | 1.71        | 1.95  | 0.94                   | 0.66            | 1.87    | *      | 0.21              | 1.76                | 90.76                          |

| Mixed                   | Dram<br>Utilization | 4.05        | 3.70  | 5.90                   | 6.98            | 3.40    | *      | *                 | 6.89                |                                |

| ſ                       | Time (%)            | 24.62       | 8.70  | *                      | 11.42           | 0.37    | 14.65  | 35.97             | *                   |                                |

| EWA<br>FP32             | IPC                 | 1.86        | 1.99  | *                      | 0.67            | 1.87    | *      | 0.15              | *                   | 70.05                          |

|                         | Dram<br>Utilization | 1.66        | 2.39  | *                      | 4.45            | 3.81    | *      | 1.00              | *                   | 1                              |

**Figure 10:** The details of single-node performance analytics of Image Classification and EWA. We classify the kernels invoked on the GPU into eight categories and use three metrics to depict their characteristics: the proportion of time, instruction per cycle (IPC) and dram utilization. The GPU utilization during the overall training session is also recorded. An asterisk (\*) is used to indicate the number is negligible, less than 0.001%.

#### 8.3 **Single-node Evaluation**

In this subsection, we first report the execution efficiency on a single node, and then perform communication and computation analytics to recover the factors that impact the performance significantly. We use the HPC AI500 V2.0 benchmarks.

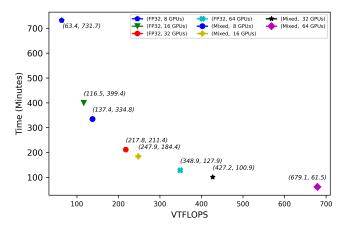

#### Performance Efficiency 8.3.1