### All 2D Heterostructure Tunnel Field Effect Transistors: Impact of Band Alignment and Heterointerface Quality

Keigo Nakamura<sup>†</sup>, Naoka Nagamura<sup>‡,§</sup>, Keiji Ueno<sup>I</sup>, Takashi Taniguchi<sup>‡</sup>, Kenji Watanabe<sup>‡</sup>, and Kosuke Nagashio<sup>†\*</sup>

<sup>†</sup>Department of Materials Engineering, The University of Tokyo, Tokyo 113-8656, Japan <sup>‡</sup>National Institute for Materials Science, Ibaraki 305-0044, Japan, <sup>§</sup>PRESTO, Japan Science and Technology Agency (JST), Saitama, 332-0012, Japan <sup>†</sup>Department of Chemistry, Saitama University, Saitama 338-8570, Japan **E-mail:** nagashio@material.t.u-tokyo.ac.jp

### Abstract

Van der Waals heterostructures are the ideal material platform for tunnel field effect transistors (TFETs) because a band-to-band tunneling (BTBT) dominant current is feasible at room temperature (RT) due to ideal, dangling bond free heterointerfaces. However, achieving subthreshold swing (SS) values lower than  $60 \text{ mVdec}^{-1}$  of the Boltzmann limit is still challenging. In this work, we systematically studied the band alignment and heterointerface quality in *n*-MoS<sub>2</sub> channel heterostructure TFETs. By selecting a *p*<sup>+</sup>-MoS<sub>2</sub> source with a sufficiently high doping level, stable gate modulation to a type III band alignment was achieved regardless of the number of MoS<sub>2</sub> channel layers. For the gate stack formation, it was found that the deposition of Al<sub>2</sub>O<sub>3</sub> as the top gate introduces defect states for the generation current under reverse bias, while the integration of an *h*-BN top gate provides a defect-free, clean interface, resulting in the BTBT dominant current even at RT. All 2D heterostructure TFETs produced by combining the type III *n*-MoS<sub>2</sub>/*p*<sup>+</sup>-MoS<sub>2</sub> heterostructure with the *h*-BN top gate insulator resulted in low SS values at RT.

**KEYWORDS:** All 2D heterostructure devices, Band to band tunneling, Negative differential resistance, Subthreshold swing, type III band alignment

### **INTRODUCTION**

The advanced metal-oxide-semiconductor field-effect transistor (MOSFET) technology now faces the dilemma for the reduction of power consumption because the subsequent reduction of power supply voltage leads to the increase in the leakage currents.<sup>1</sup> This fundamental limitation originates from the thermionic-based transport mechanism in MOSFETs, which prevents the subthreshold swing (SS), that is, steepness of the transfer characteristics in the subthreshold regime, from decreasing to less than 60 mVdec<sup>-1</sup> at room temperature (RT).<sup>2</sup> To overcome this limitation, two major concepts for steep-slope devices with SS values less than 60 mV/dec have been proposed: negative-capacitance (NC) FETs<sup>3-5</sup> and tunnel FETs (TFETs).<sup>6-8</sup> TFETs are more feasible because the device design rule based on the band-to-band tunneling (BTBT), that is, the high-energy tail of the Boltzmann distribution of carriers in the source is cut off by the band gap, is well established,<sup>1,9,10</sup> compared with the unclear physical picture in NC-FET.<sup>11</sup> In principle, however, TFETs suffer from a low drive current, which can be expected from the tunneling process. Recently, "bilayer" TFETs12 have been studied as one of ideal device structures in some systems such as InGaAs/GaAsSb13 and oxide/IV semiconductors,<sup>14</sup> where the effective tunneling area between the source and the channel is extended by the vertical stacking to increase the

tunneling current. In exchange for the enhanced tunnel currents, the increased interface area of the bilayer structure increases the difficulty in controlling the interface quality, resulting in unsatisfactory SS values.

Two-dimensional (2D) materials are highly promising for use in bilayer TFETs with both high drive currents and low SS because the shorter tunneling distance and strong gate controllability can be expected from the van der Waals gap distances and the atomically sharp heterointerfaces that form independent of lattice matching and dangling bonds. Despite intensive research on many 2D TFET systems,15-27 devices with SS values of sub-60 mVdec<sup>-1</sup> over several decades of drain current have rarely been demonstrated,<sup>28</sup> with the exception of devices utilizing ion gating with extremely high gate capacitance, however these types of devices are incapable of being integrated.<sup>8,18,27</sup> There are two main issues to overcome for 2D TFETs. One is the lack of the high doping sources and the other is the difficulty of controlling the interfacial properties.

There are few options for the high doping source materials required in the TFET device design since external doping techniques have not been developed.<sup>29,30</sup> The typical intrinsic high doping crystals like black phosphorus (BP) and SnSe<sub>2</sub> are not tolerant to oxidation and result in the formation of interlayer oxides.<sup>24,31</sup> Although local electrostatic doping in dual gate structures is often applied,<sup>15,24,25,28</sup> the structure of these types of devices becomes complicated and increases the parasitic capacitance unfavorably. Recently, by using a  $p^+$ -WSe<sub>2</sub> source that was doped by charge transfer from a WO<sub>x</sub> surface oxide layer, clear BTBT was successfully demonstrated in a stable *n*- $MoS_2/p^+$ -WSe<sub>2</sub> TFET.<sup>20</sup> Although modulation from a type II (staggered gap) to a type III (broken gap) band alignment by only applying the gate bias was desired, an additional strong drain bias  $(V_D)$  was required to produce the type III band alignment suitable to the TFET operation. This unexpected result suggests that rigorous understanding of the band alignment of 2D/2D interfaces is required. According to the transmission probability calculated for carrier transport through the BTBT barrier,<sup>1,9,10</sup> both high-on and low-off currents are achievable by combining a source with a smaller energy gap ( $E_{\rm G}$ ) and a channel with a larger  $E_{\rm G}$ . Although increasing  $E_{\rm G}$  values with decreasing the number of layers is a characteristic specific to 2D systems, how the band alignment changes as a function of the number of channel layers has not been systematically investigated despite its importance.

For the 2D/2D interfacial properties, the defect-free clean heterointerface<sup>32</sup> is critical for obtaining the BTBT dominant current under reverse bias at the diode. Although the BTBT current has been demonstrated at low temperatures, thermally activated behavior often appears at higher temperatures near RT.<sup>15,19,20,26</sup> That is, the generation current governs the total current, resulting in degradation of the SS at RT. This suggests that interface states exist even for 2D/2D interfaces. In general, high-k top gate oxides have been used in most of 2D TFETs reported thus far to enhance the gate capacitance.<sup>15,20,21,24</sup> However, how the quality of the 2D/2D interface is affected by the deposition of high-k oxides has not been revealed yet. Therefore, comparisons between high-k and h-BN gate insulators should be carried out systematically in the same 2D TFET system,<sup>33</sup> because the use of *h*-BN in TFETs has been quite limited.

In this work, we systematically studied the band alignment in n-MoS<sub>2</sub> channel TFETs with two different sources, the charge transfer type  $p^+$ -WSe<sub>2</sub> and the substitutional type  $p^+$ -MoS<sub>2</sub>. The doping level of  $p^+$ -MoS<sub>2</sub> was found to be higher than that of  $p^+$ -WSe<sub>2</sub>, resulting in stable gate modulation to form the type III band alignment independent of the number of layers. Study of the gate stack revealed that the h-BN gate insulator retains the defect-free clean  $p^+$ -n interface, unlike the deposition of high-k oxide, resulting in the dominant BTBT current even at RT. All 2D heterostructure TFETs produced by combining the

type III n-MoS<sub>2</sub>/p<sup>+</sup>-MoS<sub>2</sub> heterostructure with the h-BN top gate insulator achieved low SS values at RT.

### RESULTS

## Band alignment in *n*-MoS<sub>2</sub>/*p*<sup>+</sup>-WSe<sub>2</sub> heterostructures

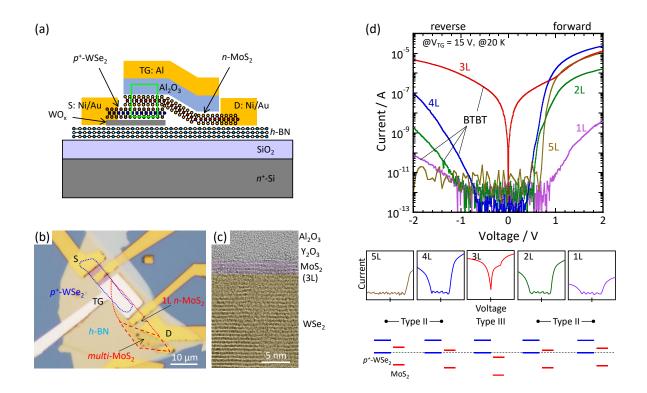

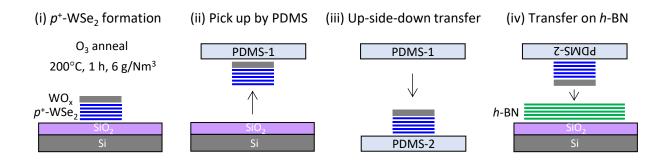

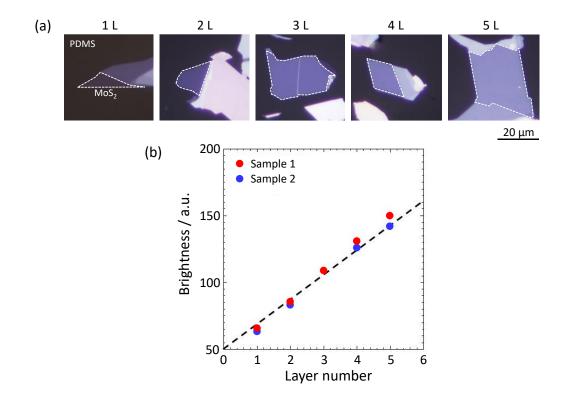

Figure 1 shows a schematic (a) and an optical micrograph (b) of the  $n-MoS_2/p^+-WSe_2$ heterostructure on h-BN with an Al<sub>2</sub>O<sub>3</sub> top gate insulator (30 nm) deposited by atomic layer deposition (ALD).<sup>34,35</sup> The  $p^+$ -WSe<sub>2</sub> FET was demonstrated by charge-transfer doping from the self-limiting WO<sub>x</sub> surface oxide layer, which was formed by ozone treatment.<sup>36,37</sup> This  $p^+$ -WSe<sub>2</sub> was further stabilized as the source crystal in TFETs by being transferred onto the *h*-BN substrate by using a polydimethylsiloxane (PDMS) sheet with an alignment system,<sup>20</sup> since the  $WO_x$  layer was encapsulated by *h*-BN and WSe<sub>2</sub>, as shown in the Supporting information of Figure S1. Typical thicknesses for the *h*-BN substrate and the  $p^+$ -WSe<sub>2</sub> source with the WO<sub>x</sub> layer were  $\sim 50$  nm and  $\sim 40$ nm, respectively. It should be noted that the thin  $p^+$ -WSe<sub>2</sub> (~15 nm) also showed similar results even though thick  $p^+$ -WSe<sub>2</sub> flakes were preferably used because of the easy transfer. For the n-MoS<sub>2</sub> channel, the number of layers was evaluated by measuring the optical contrast of *n*-MoS<sub>2</sub> on PDMS, as shown in the Supporting information of Figure **S2**. The *n*-MoS<sub>2</sub>/ $p^+$ -WSe<sub>2</sub> heterostructure was prepared with the utmost care to the heterointerface quality by the dry PDMS transfer.<sup>38,39</sup> The formation of the clean heterointerface without any oxides is evident in the cross-sectional transmission electron microscopy (TEM) image of Figure 1c, which is one advantage of the stable WSe<sub>2</sub> crystal compared to other unstable, high doping crystals such as BP and SnSe<sub>2</sub>.<sup>24,31</sup>

To determine the band alignment of the n- $MoS_2/p^+-WSe_2$  heterostructures with different numbers of n-MoS<sub>2</sub> channel layers, the diode properties were measured at 20 K at the top-gate voltage ( $V_{TG}$ ) of 15 V, as shown in **Figure 1d**. The forward bias was placed on the positive side ( $V_{\rm D}$  is indeed negative), and vice versa for the reverse bias  $(V_{\rm D} \text{ is positive})$ . It should be noted that the backgate voltage ( $V_{BG}$ ) was not applied in this study since the current was not improved by applying  $V_{\rm BG}$  and single gate structures are more feasible for real applications. Since the thermally excited carriers through the  $p^+$ -n junction can be suppressed at low temperatures, the BTBT current from the valence band of  $p^+$ -WSe<sub>2</sub> to the conduction band of *n*-MoS<sub>2</sub> was clearly observed at the reverse bias side for all cases except for the 5 layer (L) n-MoS<sub>2</sub> channel. Moreover, we have already confirmed that the temperature dependence of the current expected at the source/drain contacts is negligible due to ohmic contact,<sup>20</sup> indicating that the voltage is applied predominantly to the  $p^+$ -njunction. The diode properties firmly reflect the band alignment of the n-MoS<sub>2</sub>/ $p^+$ -WSe<sub>2</sub> heterostructures under sufficiently large  $V_{TG}$ . Interestingly, the layer number dependence is evident, where the band alignment under zero  $V_D$ changes from type II at 5L to type III at 3L and again to type II at 1L, as schematically illustrated at the bottom of **Figure 1d**.

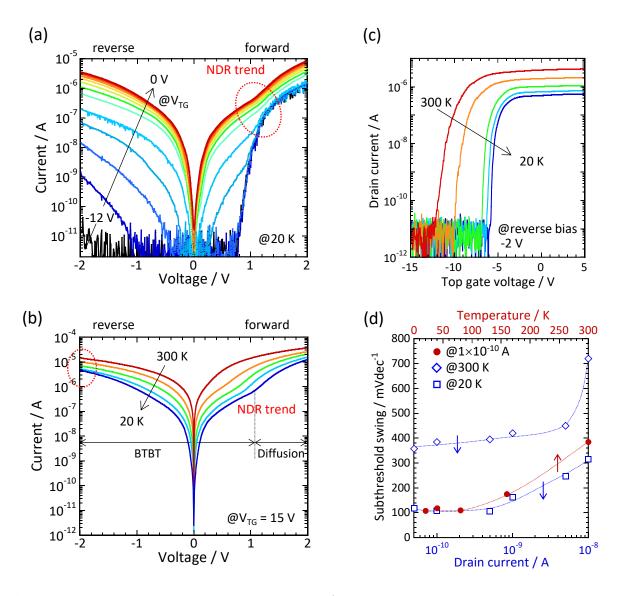

Before considering how the layer number dependence affects the band alignment, let us focus on the 3L n-MoS<sub>2</sub> channel with the type III band alignment, which is suitable for the TFET operation. Figure 2a shows the full set of diode properties at different  $V_{TG}$  at 20 K. For  $V_{TG} = -12$  V, the  $MoS_2$  channel is slightly *n*-type. The diffusion current for the forward bias and the noise level of the saturation current for the reverse bias are present, which clearly shows the rectified behavior. Hence, the band alignment is type II with a large band overlap, which is schematically the same as "5L" shown in **Figure 1d**. For -12 V  $< V_{TG} < -9$  V, the MoS<sub>2</sub> channel is *n*-type. The reverse BTBT currents are enhanced with increasing  $V_{TG}$ . The band alignment under zero  $V_{\rm D}$  is still type II but the band overlap becomes smaller, which is schematically the same as "4L" shown in Figure 1d. Finally, for  $V_{TG} > -8$  V, the MoS<sub>2</sub> channel is highly *n*-type. A negative differential resistance (NDR) trend formed by the transition from the BTBT current to the diffusion current is evident for the forward bias, which indicates that the band alignment is type III. These results clearly indicate that the band alignment of the  $n-MoS_2/p^+-WSe_2$ heterostructure under zero  $V_D$  can be readily changed from type II to type III by only using the  $V_{\rm TG}$ . When the temperature is increased with the constant  $V_{TG} = 15$  V, the NDR trend gradually disappears at ~160 K since thermally excited carriers are generated at the  $p^+$ -n junction, as shown in Figure 2b. The Arrhenius plot of the current at the reverse bias of -2 V in Figure 6e suggests thermally activated behavior at high temperatures and temperature-independent behavior at low temperatures, which also supports the presence of the BTBT current at low temperatures.

**Figure 2c** shows the transfer characteristics of another TFET device at the reverse bias of -2 V at different temperatures. The SS values were estimated as a function of the drain current ( $I_D$ ) in **Figure 2d**. The SS values increase with increasing  $I_D$ , which is consistent with the typical SS behavior of TFETs. As can be expected from the thermally activated behavior of the current, the SS values are constant in the low temperature range and start to increase with increasing temperature. Although the clean 2D/2D interface was achieved, the lowest SS values obtained at RT and 20 K are 358 mVdec<sup>-1</sup> and 106 mVdec<sup>-1</sup>, respectively.

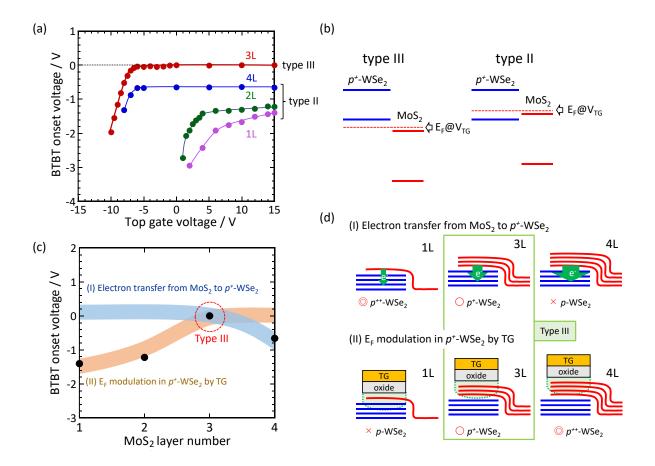

It is necessary to discuss how the dependence of the band alignment on the number of MoS2 layers, which is schematically illustrated at the bottom of Figure 1d. The BTBT onset voltage  $(V_{\text{BTBT}})$  is defined as the voltage at  $10^{-11}$  A in the diode property and is scaled to the band offset between the conduction band minimum (CBM) of MoS<sub>2</sub> and the valance band maximum (VBM) of WSe<sub>2</sub>, as shown in the Supporting information of **Figure S3.** Figure 3a shows the  $V_{\text{BTBT}}$  as a function of  $V_{TG}$  for different numbers of MoS<sub>2</sub> layers in the  $n-MoS_2/p^+-WSe_2$  heterostructure. The 5L MoS<sub>2</sub> channel is excluded from this figure since BTBT was not observed, as shown in Figure 1d. When the  $V_{\text{BTBT}}$  reaches 0 V by applying the  $V_{\text{TG}}$ , the band alignment changes from type III to type II. Interestingly, the  $V_{\text{BTBT}}$  for the 3L MoS<sub>2</sub> channel can only reach 0 V (type III), while the  $V_{\text{BTBT}}$  for different numbers of MoS<sub>2</sub> layers saturates before reaching 0 V even under sufficiently large  $V_{TG}$ (type II). Here, the dependence of  $E_{\rm G}$  on the number of MoS<sub>2</sub> layers may be expected as one of origins for this layer number dependence on the band alignment. According to first-principles calculations,<sup>40</sup> the VBM increases rapidly as the number of layers increases with respect to the vacuum level, while the CBM remains almost constant. Since the band alignment between the CBM for *n*-MoS<sub>2</sub> and the VBM for  $p^+$ -WSe<sub>2</sub> is being considered, the dependence of  $E_{\rm G}$  on the number of MoS<sub>2</sub> layers does not explain the observed band alignment.

Looking back at the saturation behavior of  $V_{\text{BTBT}}$  that suggests that Fermi level ( $E_{\text{F}}$ ) in MoS<sub>2</sub> is sufficiently modulated into the conduction band, it can be considered that the restriction to the type II band alignment is due to WSe<sub>2</sub>, not MoS<sub>2</sub>. That is, the  $E_F$  of WSe<sub>2</sub> is moved into the  $E_G$  from inside of the valence band due to a reduction in *p*-doping, as schematically shown in Figure 3b. In this case, the type III band alignment will never be realized. The reduction of *p*-doping in WSe<sub>2</sub> can originate from two different sources. One is electron transfer from  $MoS_2$  to  $WSe_2$  and the other is that the top gate modulates  $WSe_2$  as well as  $MoS_2$ . The  $V_{BTBT}$  values at  $V_{\rm TG} = 15$  V from Figure 3a are plotted as a function of the number of MoS<sub>2</sub> layers in Figure **3c**, which suggests that the band alignment may be controlled by two different physical origins since the upward convex behavior is not readily explained by a single physical property. When  $p^+$ -WSe<sub>2</sub> is in contact with MoS<sub>2</sub>, electrons are transferred from MoS<sub>2</sub> to WSe<sub>2</sub>, as illustrated in Figure 3d, and the  $E_F$  of WSe<sub>2</sub> will increase uniformly because  $p^+$ -WSe<sub>2</sub> is formed by the transfer of electrons to WO<sub>x</sub>. Because the amount of transferred electrons increases with the number of  $MoS_2$  layers, the  $E_F$  of  $WSe_2$  also changes with the number of MoS<sub>2</sub> layers and the band alignment becomes type II for the 4L and 5L MoS<sub>2</sub> channels, which is indicated by the blue line in Figure 3c. On the other hand, when the number of the  $MoS_2$ layers is reduced from 5L to 1L, WSe<sub>2</sub> is also expected to be modulated by the top gate. Therefore, by applying  $V_{TG}$ , the  $E_F$  of WSe<sub>2</sub> and MoS<sub>2</sub> are both modulated at the same time, which reduces the rate of change of the  $V_{\text{BTBT}}$  for the 1L and 2L MoS<sub>2</sub> channels in Figure 3a. Therefore, the band alignment changes from type III to type II as the number of  $MoS_2$  layers decreases, as shown by the orange line in Figure 3c. Because of this, only the 3L MoS<sub>2</sub> channel appears as type III due to the combination of the two different sources of pdoping reduction for the WSe<sub>2</sub>.

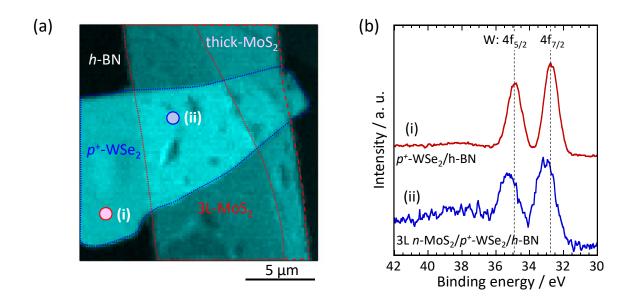

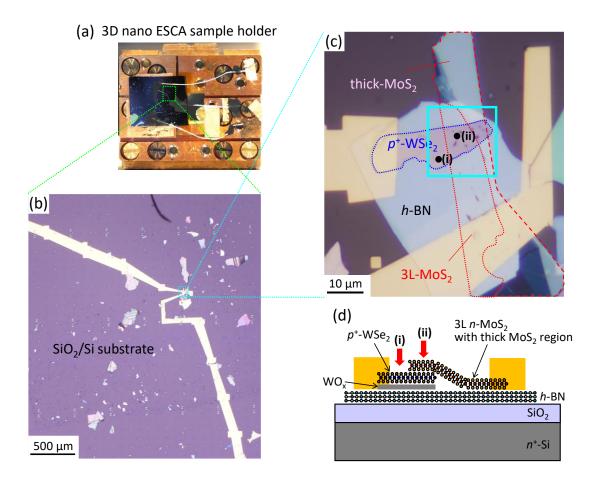

confirming Although experimentally modulation of the  $E_{\rm F}$  of  $p^+$ -WSe<sub>2</sub> by the top gate is difficult, it is possible to prove there is electron transfer from  $MoS_2$  to  $p^+$ -WSe<sub>2</sub>. Here, a core-level photoelectron spectromicroscopic apparatus installed at the synchrotron radiation facility of SPring-8, called "3D nano-ESCA,"41,42 is utilized, with which we can scan a sample with a high lateral spatial resolution of ~70 nm to record photoelectron spectra for quantitative analysis of the chemical states. Figure 4a shows an intensity mapping image for the Mo  $3d_{5/2}$  peak with a spatial resolution of 200 nm for the  $3L-n-MoS_2/p^+-WSe_2$ heterostructure on h-BN specifically prepared for 3D nano-ESCA, as shown in the Supporting information of Figure S4. The position of the heterostructure is clearly identified. Figure 4b shows the pinpoint core-level spectra for the W  $4f_{5/2}$  and  $4f_{7/2}$  peaks recorded at points (i)  $p^+$ -WSe<sub>2</sub>/h-BN and (ii) 3L-n-MoS<sub>2</sub>/p<sup>+</sup>-WSe<sub>2</sub>/h-BN. The W 4f peaks for (ii) where  $p^+$ -WSe<sub>2</sub> is in contact with 3L-n-MoS<sub>2</sub> shifts to higher binding energy than that for point (i) where  $p^+$ -WSe<sub>2</sub> is directly on *h*-BN. When  $p^+$ -WSe<sub>2</sub> is doped with electrons, the  $E_{\rm F}$  of  $p^+$ -WSe<sub>2</sub> increases, resulting in the W 4f peaks having higher binding energy. These results support that *p*-doping reduction is occurring in WSe<sub>2</sub>.

## Realization of stable type III band alignment using a $p^+$ -MoS<sub>2</sub> source

In the TFET transfer characteristics, the on-current is one of important figures of merit. However, the on-current in the type II band alignment is much lower than that for the type III alignment, which can be realized at the current level at the reverse bias of -2 V in **Figure 1d** (also in the Supporting information of **Figure S5**). As discussed in the previous section, the  $E_F$  of the WSe<sub>2</sub> source was modulated by the surrounding, which prevented from controlling the band alignment from type II to type III. The problem for this is that the doping

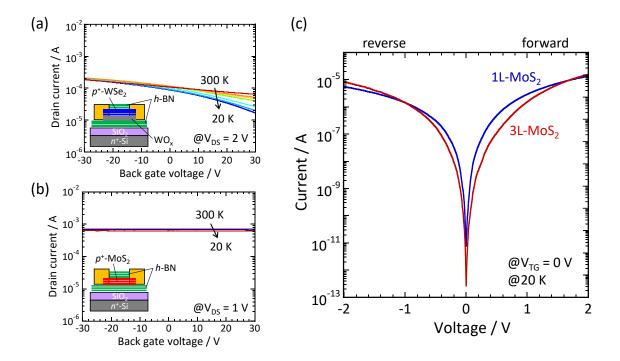

level of  $p^+$ -WSe<sub>2</sub> is not sufficiently high. To mitigate this shortcoming, a niobium (Nb)-doped  $p^+$ -MoS<sub>2</sub> crystal<sup>43,44</sup> was used as an alternative source. Compared to the charge transfer type  $p^+$ -WSe<sub>2</sub>, the Nb-doped  $p^+-MoS_2$ is а thermodynamically stable substitutional type source with a degenerate hole concentration of  $\sim 3 \times 10^{19}$  cm<sup>-3</sup>, which was confirmed by Hall measurement.<sup>43</sup> Figure 5 compares the transfer characteristics of (a)  $p^+$ -WSe<sub>2</sub> and (b)  $p^+$ -MoS<sub>2</sub> FETs at different temperatures. The linear scale is also shown in the Supporting information of Figure S6. No gate dependence was observed for the transfer characteristics of the  $p^+$ -MoS<sub>2</sub> FET for all the measured temperatures compared with the slight change for the  $p^+$ -WSe<sub>2</sub> FET. This indicates that the doping level of  $p^+$ -MoS<sub>2</sub> is higher than  $p^+$ -WSe<sub>2</sub>. The channel thickness dependence of the transfer characteristics of  $p^+$ -MoS<sub>2</sub> is also available in our previous research,33 where it was revealed that the narrow maximum depletion width of ~7 nm is consistent with the degenerate hole concentration. Indeed, when  $p^+$ -MoS<sub>2</sub> was used as the source in the heterostructure TFET with the MoS<sub>2</sub> channel, the diode properties in Figure 5c indicate that the type III band alignment was achieved even for the 1L n-MoS<sub>2</sub> channel as well as the 3L *n*-MoS<sub>2</sub> channel at  $V_{TG} = 0$  V. The successful modulation of the band alignment to type III by only gate modulation supports the above conclusion that the reduction in the *p*-doping of WSe<sub>2</sub> is indeed a limiting factor that restricts the band alignment to type II.

## Demonstration of low SS values for All 2D heterostructure TFETs

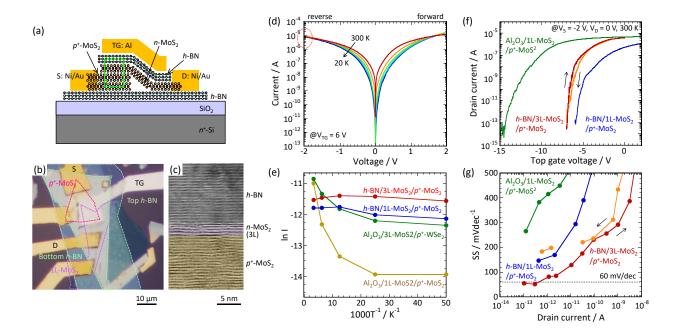

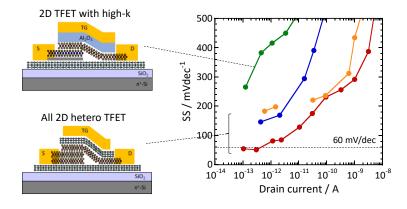

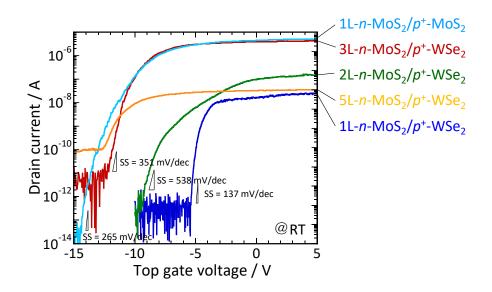

We demonstrated that type III band alignment can be obtained for MoS<sub>2</sub> channels with any number of layers using the  $p^+$ -MoS<sub>2</sub> source. However, the lowest SS values obtained for both the  $p^+$ -MoS<sub>2</sub> source and the  $p^+$ -WSe<sub>2</sub> source were restricted to 137 mVdec<sup>-1</sup>, as shown in the Supporting information of Figure S5. There are three strategies to further reduce the SS values: (i) Recently, we have discovered that the deposition of Al<sub>2</sub>O<sub>3</sub> top gate oxide on the monolayer MoS<sub>2</sub> channel on h-BN substrate increases the interface states density at the "bottom" MoS<sub>2</sub>/h-BN interface as well as the top Al<sub>2</sub>O<sub>3</sub>/MoS<sub>2</sub> interface due to the introduction of strain in the MoS<sub>2</sub> channel.<sup>33</sup> This suggests that the 2D/2D interface in TFET is also degraded by the high-k deposition. Therefore, an h-BN top gate insulator was adopted to benefit from the electrically inert interface in 2D heterostructure TFETs.<sup>32</sup> (ii) The  $p^+$ -MoS<sub>2</sub> source was used instead of the  $p^+$ -WSe<sub>2</sub> source because the  $E_F$  of  $p^+$ -MoS<sub>2</sub> cannot be modulated due to the degenerately high doping of the  $p^+$ -MoS<sub>2</sub>. (iii) According to the transmission probability calculated for carrier

transport through the BTBT barrier,<sup>1,9,10</sup> the  $E_G$  for the channel should be larger than that for the source to keep the off current low but  $E_G$  also should be as small as possible to increase the transmission probability. Therefore, the 1L and 3L MoS<sub>2</sub> channels were compared. Based on these three considerations, all 2D heterostructure TFETs were fabricated to achieve SS values lower than 60 mVdec<sup>-1</sup>.

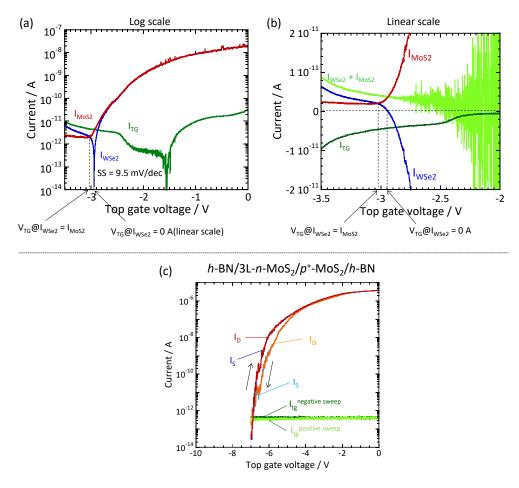

Figure 6 shows a schematic (a) and an optical micrograph (b) of a typical h-BN/n-MoS $_2/p^+$ -MoS<sub>2</sub>/h-BN all 2D heterostructure TFET. The typical thickness for the top gate h-BN insulator and the  $p^+$ -MoS<sub>2</sub> source are ~15 nm and ~30 nm, respectively. The atomically sharp gate stack interfaces are clearly seen in the cross-sectional TEM image of Figure 6c since all of the 2D materials are stable in air. As was expected, the diode properties of the all 2D heterostructure TFET with the 3L-n-MoS<sub>2</sub> channel in Figure 6d shows the type III band alignment at  $V_{TG} = 6$  V. The NDR trend at the forward side is not visible, unlike the case in Figure 2b. This may be explained by the two possibilities. One is large energy gap between VBM for  $p^+$ -MoS<sub>2</sub> and CBM for n-MoS<sub>2</sub> in the type III band alignment because  $E_{\rm F}$  in  $p^+$ -MoS<sub>2</sub> is located deeply in the valence band due to higher doping concentration. The other is the suppression of the diffusion current due to the larger barrier between the CBM for  $p^+$ -MoS<sub>2</sub> and the VBM for the n-MoS<sub>2</sub> channel because the  $E_G$  of bulk MoS<sub>2</sub> (~1.4 eV) is larger than the  $E_G$  of bulk WSe<sub>2</sub> (~1.2 eV). An Arrhenius plot of the current at the reverse bias of -2 V is compared with other heterostructures in Figure 6e. It should be noted that all four heterostructure TFETs exhibit type III alignment. For the *h*-BN top gate band heterostructure devices with the 1L and 3L MoS<sub>2</sub> channels, temperature-independent behavior is evident over the entire temperature range, indicating that BTBT is dominant even at RT and that the source/drain contacts are Ohmic nature. This is quite promising for TFET operation with low SS values at RT. On the other hand, when Al<sub>2</sub>O<sub>3</sub> was used as the top gate insulator, thermally activated behavior at high temperatures was clearly observed regardless of the source crystal. These comparisons indicate that the trap-related generation-recombination current<sup>45</sup> and/or the trapassisted tunneling current<sup>46,47</sup> under reverse bias are drastically suppressed by the successful integration of the electrically inert interface in the 2D heterostructure TFET.

Finally, the transfer characteristics of the 2D heterostructure TFETs at the reverse bias of -2 V at RT are shown in **Figure 6f**. According to our previous studies on the dielectric breakdown of h-BN,<sup>48,49</sup> the vertical dielectric breakdown field is ~1.2 V/nm and the leakage occurs at ~0.5 V/nm.

Therefore, in this study, the  $V_{TG}$  sweep range for the h-BN top gate is determined based on the critical electrical field of ~0.4 V/nm. Compared with the exact control of Al<sub>2</sub>O<sub>3</sub> thickness, the thickness of h-BN cannot be well controlled. Therefore, the  $V_{TG}$  sweep range differs device to device. The estimated SS values are shown as a function of  $I_D$  in Figure 6g. SS values for all 2D heterostructure TFETs are much lower than that for 2D heterostructure TFET with Al<sub>2</sub>O<sub>3</sub> top gate. Moreover, in all 2D heterostructure TFETs, the smaller  $E_{\rm G}$  of the 3L-*n*-MoS<sub>2</sub> channel was preferable, compared with the 1L-n-MoS<sub>2</sub> channel. Here, let us analyze the best device, 3L-*n*-MoS<sub>2</sub>/p<sup>+</sup>-MoS<sub>2</sub> heterostructure, more in detail. The leakage current contributions should be considered carefully since artificially low SS values are often reported, as shown in the Supporting information of Figure S6. It is evident that  $I_{\rm D}$  overlaps with  $I_{\rm S}$ for the 3L-n-MoS<sub>2</sub> channel because there is no gate leakage (Figure S6c), which supports that the SS value is not artificial. However, the hysteresis was detected in the transfer characteristics and SS even for all 2D heterostructure TFET, as shown in Figure 6f and 6g. In general, the existence of hysteresis results in the degraded SS value and never provides the "apparently" better SS value. However, for the actual device applications, SS values in both sweep directions should be low enough for 4-5 decade of the current. By improving the cleanness of the 2D heterointerface, for example, removing the bubbles, further reduction of the hysteresis and the SS value will be possible.

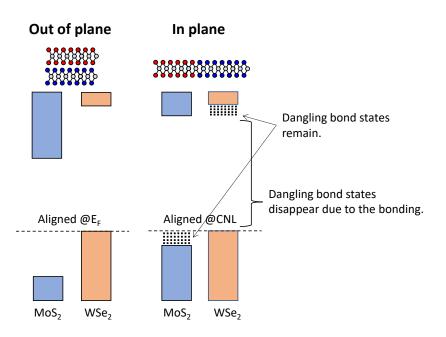

Recently, quite low average SS values over 4 dec of current (SS =  $\sim 22.9 \text{ mVdec}^{-1}$ ) have been reported for "in-plane type" BP/BP heterostructure TFETs,<sup>28</sup> which are different from the "bilayer structure" (out-of-plane) TFETs reported in this study. Density function theory (DFT) calculations<sup>50</sup> suggest that out-of-plane 2D/2D heterostructures are more preferable than in-plane 2D/2D heterostructures in terms of gate controllability because the dangling bond states remain even after the defect free heterointerface is formed for the calculation, as schematically shown in the Supporting information of Figure S7. The fact that such a low SS value was obtained for the in-plane TFETs suggests the lower SS values are possible for out-of-plane TFETs with higher on-currents when the whole heterointerface is more rigorously controlled by ensuring the interface is clean and the lattices match.

### CONCLUSIONS

Band alignment and interfacial quality were critical for achieving SS values lower than 60 mVdec<sup>-1</sup> of the Boltzmann limit. Insufficient doping levels in the source crystal restricted the band alignment to type II, even under sufficient gate bias. This strongly suggests the importance of establishing external doping techniques for the success of future studies. The key finding regarding the quality of the heterointerface is that producing the defect-free clean heterointerface via integration of the h-BN top gate provides the BTBT dominant current even at RT. All 2D heterostructure TFETs produced by combining the type III  $n-MoS_2/p^+-MoS_2$ heterostructure with the *h*-BN top gate insulator resulted in low SS values at RT. Since it has been suggested that out-of-plane 2D/2D heterostructures are more preferable than in-plane 2D/2D heterostructures in terms of gate controllability, further reductions in SS values and higher onpossible when the currents are entire heterointerface is more rigorously controlled.

### **EXPERIMENTAL METHODS**

**Device fabrication.** Natural *n*-MoS<sub>2</sub> and Nb-doped  $p^+$ -MoS<sub>2</sub> bulk crystals were purchased from SPI Supplies and HQ graphene, respectively, whereas WSe<sub>2</sub> and *h*-BN bulk crystals were grown using a physical vapor transport technique without an I<sub>2</sub> transport agent<sup>51</sup> and a temperature-gradient method under a high-pressure and high-temperature atmosphere.<sup>52</sup> The thin 2D layers were prepared from the mechanical exfoliation of the bulk crystals. The  $n-MoS_2/p^+-WSe_2$  heterostructure on the h-BNsubstrate was fabricated using a dry transfer method with PDMS and an alignment system.<sup>38,39</sup> Ni/Au was deposited as the source/drain electrodes after the electrode pattern was formed using electron beam lithography. For the high-k top-gate formation, 1-nm-thick Y<sub>2</sub>O<sub>3</sub> was deposited via thermal evaporation of Y metal in a PBN crucible in an Ar atmosphere with a partial pressure of  $10^{-1}$ Pa to form a buffer layer.<sup>34</sup> Al<sub>2</sub>O<sub>3</sub> oxide layers with thicknesses of 30 nm were deposited via ALD, followed by formation of the Al top-gate electrode.<sup>35</sup> Alternatively, *h*-BN top gate TFETs were also fabricated by the dry transfer method. No additional annealing was performed after fabrication of the heterostructures.

Measurements. Raman spectroscopy and AFM were employed to determine the crystal quality and thickness of the flakes. TEM images were taken at an acceleration voltage of 200 kV using a JEM-ARM200F to confirm the quality of the 2D heterostructure interface. For core-level photoelectron spectromicroscopy measurements, a 3D nano-ESCA installed at the soft X-ray beamline BL07LSU in the synchrotron radiation facility of SPring-8 was used. The photon energy of the incident beam was 1000 eV. All electrical measurements were performed using a Keysight B1500 in a vacuum prober with a cryogenic system.

### SUPPORTING INFORMATION

The up-side-down transfer, optical contrast of MoS<sub>2</sub>, diode property of type II band alignment, 3D nano-ESCA, Transfer characteristics of various heterostructure TFETs, analysis on the leakage current, band alignment of out-of-plane and in-plane heterojunction. The Supporting Information is available free of charge via the Internet at http://pubs.acs.org.

### AUTHOR INFORMATION

### **Corresponding Author**

\*Email: nagashio@material.t.u-tokyo.ac.jp

### Notes

The authors declare no competing financial interests.

### **ACKNOWLEDGEMENTS**

This research was supported by Samco Science and Technology Foundation, The Canon Foundation, the Elemental Strategy Initiative conducted by the MEXT, Grant Number JPMXP0112101001, the A. JSPS Core-to-Core Program, Advanced Research Networks, the JSPS A3 Foresight Program, JSPS KAKENHI Grant Numbers JP20H00354, JP19H00755, 19K21956, 18H03864, 19H02561, and CREST(Grant number: and JPMJCR15F3) and PRESTO (Grant number: JPMJPR17NB) commissioned by the Japan Science and Technology Agency (JST), Japan. The spectral datasets were obtained with the support of the University of Tokyo outstation beamline at SPring-8 (Proposal Numbers: 2018B7580 and 2019A7451).

#### REFERENCES

- (1) Ionescu, A. M.; Riel, H. Tunnel Filed-Effect Transistors as Energy-Efficient Electronics Switches. *Nature* **2011**, *479*, 329-337.

- (2) Sze, S. M. Physics of Semiconductor Devices; 3rd edn. (Wiley interscience, 2006).

- (3) Salahuddin, S.; Datta, S. Use of Negative Capacitance to Provide Voltage Amplification for Low Power Nanoscale Devices. *Nano Lett.* **2008**, *8*, 405-410.

- (4) Kwon, D.; Cheema, S.; Shanker, N.; Chatterjee, K.; Liao, Y.-H.; Tan, A. J.; Hu, C.; Salahuddin, S. Negative Capacitance FET with 1.8-nm-Thick Zr-Doped HfO<sub>2</sub> Oxide. *IEEE Electron Dev. Lett.* 2019, 40, 993-996.

- (5) Kobayashi, M. A Perspective on Steep-Subthreshold Negative-Capacitance Field-Effect Transistor. *Appl. Phys. Express* **2018**, *11*, 110101.

- (6) Chang, L. L.; Esaki, L. Tunnel Triode-a Tunneling Base Transistor. *Appl. Phys. Lett.* **1977**, *31*, 687-689.

- (7) Tomioka, K.; Yoshimura, M.; Fukui, T. Steep-Slope Tunneling Field-Effect Transistors using III-V Nanowire/Si Heterojunction. *Symp. VLSI Technol.* 2012, 47-48.

- (8) Sarkar, D.; Xie, X.; Liu, W.; Cao, W.; Kang, J.; Gong, Y.; Kraemer, S.; Ajayan, P. M.; Banerjee, K. A Subthermionic Tunnel Field-Effect Transistor with an Atomically Thin Channel. *Nature* **2015**, *526*, 91-95.

- (9) Seabaugh, A. C.; Zhang, Q. Low-Voltage Tunnel Transistors for Beyond CMOS Logic. *Proc. IEEE* 2010, 98, 2095-2110.

- (10) Knoch, J.; Mantl, S.; Appenzeller, Impact of the Dimensionality on the Performance of Tunneling FETs: Bulk versus One-Dimensional Device. J. Solid State Electron. 2007, 51, 572-578.

- (11) Cao, W.; Benerjee, K. Is Negative Capacitance FET a Steep-Slope Logic Switch? *Nature commun.* 2020, 11, 196.

- (12) Lattanzio, L.; Dağtekin, N.; De Michielis, L.; Ionescu, A. M. On the Static and Dynamic Behavior of the Germanium Electron-Hole Bilayer Tunnel FET. *IEEE Electron Devices* **2012**, *59*, 2932-2938.

- (13) Yu, T.; Radhakrishna, U.; Hoyt, J. L.; Antoniadis, D. A. Quantifying the Impact of Gate Efficiency on Switching Steepness of Quantum-Well Tunnel-FETs: Experiments, Modeling, and Design Guidelines. *IEEE IEDM Tech. Dig.* 2015, 612-615.

- (14) Kato K.; Jo, K. -W.; Matsui, H.; Tabata, H.; Mori, T.; Morita, Y.; Matsukawa, T.; Takenaka, M.; Takagi, S. *p*-channel TFET Operation of Bilayer Structures with Type-II Heterotunneling Junction of Oxide- and Group-IV Semiconductors. *IEEE Electron Devices* **2020**, *67*, 1880-1886.

- (15) Roy, T.; Tosun, M.; Cao, X.; Fang, H.; Lien, D. -H.; Zhao, P.; Chen, Y. -Z.; Guo, J.; Javey, A. Dual-Gated MoS<sub>2</sub>/WSe<sub>2</sub> van der Waals Tunnel Diodes and Transistors. ACS Nano 2015, 9, 2071-2079.

- (16) Nourbakhsh, A.; Zubair, A.; Dresselhaus, M. S.; Palacios, T. Transport Properties of a MoS<sub>2</sub>/WSe<sub>2</sub> Heterojunction Transistor and its Potential for Application. *Nano Lett.* **2016**, *16*, 1359-1366.

- (17) Li, C.; Yan, X.; Song, X.; Bao, W.; Ding, S.; Zhang, D. W.; Zhou, P. WSe<sub>2</sub>/MoS<sub>2</sub> and MoTe<sub>2</sub>/SnSe<sub>2</sub> van der Waals Heterostructure Transistors with Different Band Alignment. *Nanotechnol.* **2017**, *28*, 415201.

- (18) Liu, X.; Qu, D.; Li, H. -M.; Moon, I.; Ahmed, F.; Kim, C.; Lee, M.; Choi, Y.; Cho, J. H.; Hone, J. C.; Yoo, W. J. Modulation of Quantum Tunneling *via* a Vertical Two-Dimensional Black Phosphorus and Molybdenum Disulfide *p-n* Junction. *ACS Nano* 2017, *11*, 9143-9150.

- (19) Balaji, Y.; Smets, Q.; De La Rosa, C. J. L.; Lu, A. H. A.; Chiappe, D.; Agarwal, T.; Lin, D. H. C.; Huyghebaert, C.; Radu, I.; Mocuta, D.; Groeseneken, G. Tunneling Transistors Based on MoS<sub>2</sub>/MoTe<sub>2</sub> van der Waals Heterostructures. *J. Electron Dev. Soc.* 2018, *6*, 1048-1055.

- (20) He, J.; Fang, N.; Nakamura, K.; Ueno, K.; Taniguchi, T.; Watanabe, K.; Nagashio, K. 2D Tunnel Field Effect Transistors (FETs) with a Stable Charge-Transfer-Type p<sup>+</sup>-WSe<sub>2</sub> Source. *Adv. Electron Mater.* **2018**, *4*, 1800207.

- (21) Guo, Z.; Chen, Y.; Zhang, H.; Wang, J.; Hu, W.; Ding, S.; Zhang, D. W.; Zhou, P.; Bao, W. Independent Band Modulation in 2D van der Waals Heterostructures via a Novel Device Architecture. *Adv. Sci.* 2018, *5*, 1800237.

- (22) Zhang, W.; Kanazawa, T.; Miyamoto, Y. Performance Improvement of a *p*-MoS<sub>2</sub>/HfS<sub>2</sub> van der Waals Heterostructure Tunneling FET by UV-O<sub>3</sub> Treatment. *Appl. Phys. Express* **2019**, *12*, 065005.

- (23) Na, J.; Kim, Y.; Smet, J. H.; Burghard, M.; Kern, K. Gate-tunable tunneling transistor based on a thin black phosphorus-SnSe<sub>2</sub> heterostructure. ACS Appl. Mater. Interfaces 2019, 11, 20973-20978.

- (24) Wu, P.; Ameen, T.; Zhang, H.; Bendersky, L. A.; Ikatikhameneh, H.; Klimeck, G.; Rahman, R.;

Davydov, A. V.; Appenzeller, J. Complementary Black Phosphorus Tunneling Field-Effect Transistors. *ACS Nano* **2019**, *13*, 377-385.

- (25) Balaji, Y.; Smets, Q.; Śzabo, Á.; Mascaro, M.; Lin, D.; Asselberghs, I.; Radu, I.; Luisier, M.; Groeseneken, G. MoS<sub>2</sub>/MoTe<sub>2</sub> Heterostructure Tunnel FETs using Gated Schottky Contacts. *Adv. Func. Mater.* **2020**, *30*, 1905970.

- (26) Lv, Q.; Yan, F.; Mori, N.; Zhu, W.; Hu, C.; Kudrynskyi, Z. R.; Kovalyuk, Z. D.; Patanè, A.; Wang, K. Interlayer Band-to-Band Tunneling and Negative Differential Resistance in van der Waals BP/InSe Field-Effect Transistors. *Adv. Func. Mater.* 2020, *30*, 1910713.

- (27) Jeon, H. B.; Shin, G. H.; Lee, K. J.; Choi, S. -Y. Vertical-Tunneling Field-Effect Transistor Based on WSe<sub>2</sub>-MoS<sub>2</sub> Heterostructure with Ion Gel Dielectric. *Adv. Electronic Mater.* **2020**, 2000091.

- (28) Kim, S.; Meyong, G.; Shin, W.; Lim, H.; Kim, B.; Jin, T.; Chang, S.; Watanabe, K.; Taniguchi, T.; Cho, S. Thickness-Controlled Black Phosphorus Tunnel Field-Effect Transistor for Low-Power Switches. *Nature Nanotechnol.* **2020**, *15*, 203-206.

- (29) Nipane, A.; Karmakar, D.; Kaushik, N.; Karande, S.; Lodha, S. Few-Layer MoS<sub>2</sub> p-Type Devices Enabled by Selective Doping using Low Energy Phosphorus Implantation. ACS Nano 2016, 10, 2128-2137.

- (30) Xu, K.; Zhao, Y.; Lin, Z.; Long, Y.; Wang, Y.; Chan, M.; Chai, Y. Doping of Two-Dimensional MoS<sub>2</sub> by High Energy Ion Implantation. *Semicond. Sci. Technol.* 2017, 32, 124002.

- (31) Fan, S.; Vu, Q. A.; Lee, S.; Phan, T. L.; Han, G.; Kim, Y. -M.; Yu, W. J.; Lee, Y. H. Tunable Negative Differential Resistance in van der Waals Heterostructures at Room Temperature by Tailoring the Interface. ACS Nano 2019, 13, 8193-8201.

- (32) Uwanno, T.; Taniguchi, T.; Watanabe, K.; Nagashio, K. Electrically Inert *h*-BN/Bilayer Graphene Interface in All-Two-Dimensional Heterostructure Field Effect Transistors. ACS Appl. Mater. Interfaces 2018, 10, 2878-28788.

- (33) Fang, N.; Toyoda, S.; Taniguchi, T.; Watanabe, K.; Nagashio, K. Full Energy Spectra of Interface State Densities for *n*- and *p*-Type MoS<sub>2</sub> Field-Effect Transistors. *Adv. Func. Mater.* **2019**, *29*, 1904465.

- (34) Takahashi, N.; Nagashio, K. Buffer Layer Engineering on Graphene via Various Oxidation Methods for Atomic Layer Deposition. *Appl. Phys. Express* **2016**, *9*, 125101.

- (35) Kurabayashi, S.; Nagashio, K. Transport Properties of the Top and Bottom Surfaces in Monolayer MoS<sub>2</sub> Grown by Chemical Vapor Deposition. *Nanoscale* 2017, 9, 13264-13271.

- (36) Yamamoto, M.; Dutta, S.; Aikawa, S.; Nakaharai, S.; Wakabayashi, K.; Fuhrer, M. S.; Ueno, K.; Tsukagoshi, K. Self-Limiting Layer-by-Layer Oxidation of Atomically Thin WSe<sub>2</sub>. *Nano Lett.* **2015**, *15*, 2067-2073.

- (37) Yamamoto, M.; Nakaharai, S.; Ueno, K.; Tsukagoshi, K. Self-Limiting Oxides on WSe<sub>2</sub> as Controlled Surface Acceptors and Low-Resistance Hole Contacts. *Nano lett.* **2016**, *16*, 2720-2727.

- (38) Uwanno, T.; Hattori, Y.; Taniguchi, T.; Watanabe, K.; Nagashio, K. Fully Dry PMMA Transfer of Graphene on *h*-BN using a Heating/Cooling System. 2D *Mater.* 2015, 2, 041002.

- (39) Toyoda, S.; Uwanno, T.; Taniguchi, T.; Watanabe, K.; Nagashio, K. Pinpoint Pick-up and Bubble-Free Assembly of 2D Materials using PDMS/PMMA

Polymers with Lens Shapes. Appl. Phys. Express, 2019, 12, 055008.

- (40) Padilha, J. E.; Peelaers, H.; Janotti, A.; Van de Walle, C. G. Nature and Evolution of the Band-Edge States in MoS<sub>2</sub>: From Monolayer to Bulk. *Phys. Rev. B* 2014, *90*, 205420.

- (41) Horiba, K.; Nakamura, Y.; Nagamura, N.; Toyoda, S.; Kumigashira, H.; Oshima, M.; Amemiya, K.; Senba, Y.; Ohashi, H. Scanning Photoelectron Microscope for Nanoscale Three-Dimensional Spatial-Resolved Electron Spectroscopy for Chemical Analysis. *Rev. Sci. Instrum.* **2011**, *82*, 113701.

- (42) Nagamura, N.; Fukidome, H.; Nagashio, K.; Horiba, K.; Ide, T.; Funakubo, K.; Tashima, K.; Toriumi, A.; Suemitsu, M.; Horn, K.; Oshima, M. Influence of Interface Dipole Layers on the Performance of Graphene Field Effect Transistors. Carbon, 2019, 152, 680-687.

- (43) Dolui, K.; Rungger, I.; Pemmaraju, C. D.; Sanvito, S. Possible Doping Strategies for MoS<sub>2</sub> Monolayers: An ab initio Study. *Phys. Rev. B* **2013**, *88*, 075420.

- (44) Suh, J.; Park, T. E.; Lin, D. Y.; Fu, D.; Park, J.; Jung, H. J.; Chen, Y.; Ko, C.; Jang, C.; Sun, Y.; Sinclair, R.; Chang, J.; Tongay, S.; Wu, J. Doping Against the Native Properties of MoS<sub>2</sub>: Degenerate Hole Doping by Cation Substitution. *Nano Lett.* **2014**, *14*, 6976-6982.

- (45) Gotow, T.; Mitsuhara, M.; Hoshi, T.; Sugiyama, H.; Takenaka, M.; Takagi, S. Performance Enhancement of *p*-GaAs<sub>0.51</sub>Sb<sub>0.49</sub>/In<sub>0.53</sub>Ga<sub>0.47</sub>As Hetero-Junction Vertical Tunneling Field-Effect Transistors with

Abrupt Source Impurity Profile. J. Appl. Phys. 2019, 126, 214502.

- (46) Mori, T.; Morita, Y.; Miyata, N.; Migita, S.; Fukuda, K.; Mizubayashi, W.; Masahara, M.; Yasuda, T.; Ota, H. Study on Tunneling Transport in Si-Based Tunneling Field-Effect Transistors with ON Current Enhancement Utilizing Isoelectronic Trap. *Appl. Phys. Lett.* 2015, *106*, 083501.

- (47) Sajjad, R. N.; Chern, W.; Hoyt, J. L.; Antoniadis, D. A. Trap Assisted Tunneling and Its Effect on Subthreshold Swing of Tunnel FETs. *IEEE Electron Devices* 2016, 63, 4380-4387.

- (48) Hattori, Y.; Watanabe, K.; Taniguchi, T.; Nagashio, K. Layer-by-Layer Dielectric Breakdown of Hexagonal Boron Nitride. ACS nano, 2015, 9, 916-921.

- (49) Hattori, Y.; Taniguchi, T.; Watanabe, K.; and Nagashio, K.; Anisotropic Breakdown Strength of Single Crystal Hexagonal Boron Nitride. ACS appl. mater. interfaces 2016, 8, 27877-27877.

- (50) Guo, Y.; Robertson, J. Band Engineering in Transition Metal Dichalcogenides: Stacked Versus Lateral Heterostructures. *Appl. Phys. Lett.* 2016, 108, 233104.

- (51) Ueno, K. Introduction to the Growth of Bulk Single Crystals of Two-Dimensional Transition-Metal Dichalcogenides. J. Phys. Soc. Jpn. 2015, 84, 121015.

- (52) Watanabe, K.; Taniguchi, T.; Kanda, H. Direct-Bandgap Properties and Evidence for Ultraviolet Lasing of Hexagonal Boron Nitride Single Crystal. *Nature Mater.* 2004, *3*, 404-409.

### FIGURES

**Figure 1** a) Schematic illustration and b) optical micrograph of the n-MoS<sub>2</sub>/p<sup>+</sup>-WSe<sub>2</sub> heterostructure on h-BN with an Al<sub>2</sub>O<sub>3</sub> top gate insulator. c) Cross-sectional TEM image of the Al<sub>2</sub>O<sub>3</sub>/3L-n-MoS<sub>2</sub>/p<sup>+</sup>-WSe<sub>2</sub> heterostructure from the solid rectangular in a). The number of MoS<sub>2</sub> layers is 3. d) Diode properties for the n-MoS<sub>2</sub>/p<sup>+</sup>-WSe<sub>2</sub> heterostructure with different numbers of MoS<sub>2</sub> layers at  $V_{TG} = 15$  V and 20 K. The layer number dependent characteristics are schematically illustrated at the bottom.

**Figure 2** a) Diode properties for the 3L-*n*-MoS<sub>2</sub>/ $p^+$ -WSe<sub>2</sub> heterostructure at different  $V_{TG}$  and 20 K. The voltage step in  $V_{TG}$  is 1 V. b) Temperature dependence of the diode properties for the 3L-*n*-MoS<sub>2</sub>/ $p^+$ -WSe<sub>2</sub> heterostructure at a constant  $V_{TG} = 15$  V (20, 40, 80, 160, and 300 K). c) Transfer characteristics of the TFET at different temperatures under a reverse bias of -2 V. d) SS as a function of  $I_D$  and the temperature.

**Figure 3** a)  $V_{\text{BTBT}}$  as a function of  $V_{\text{TG}}$  for MoS<sub>2</sub> with different numbers of layers the 3L-*n*-MoS<sub>2</sub>/*p*<sup>+</sup>-WSe<sub>2</sub> heterostructure. b) Schematic illustration of the band alignment for type II and type III.  $E_{\text{F}}$  for MoS<sub>2</sub> is fixed in the conduction band. When the  $E_{\text{F}}$  of WSe<sub>2</sub> is in the valence band, the band alignment can be type III. On the other hand, when the  $E_{\text{F}}$  of WSe<sub>2</sub> is in the band gap, it is restricted to type II. c)  $V_{\text{BTBT}}$  as a function of the number of MoS<sub>2</sub> layers. d) Schematic illustration of the two different physical origins for the *p*-doping reduction of WSe<sub>2</sub>.

**Figure 4** a) Photoelectron intensity mapping image for the Mo  $3d_{5/2}$  peak with a spatial resolution of 200 nm for the 3L-*n*-MoS<sub>2</sub>/*p*<sup>+</sup>-WSe<sub>2</sub> heterostructure on *h*-BN. b) Pinpoint corelevel spectra for W  $4f_{5/2}$  and  $4f_{7/2}$  peaks recorded at points (i) and (ii).

**Figure 5** Transfer characteristics for a)  $p^+$ -WSe<sub>2</sub> FET and b)  $p^+$ -MoS<sub>2</sub> FET at different temperatures (20, 40, 80, 160, 200, 250, and 300 K). c) Diode properties for 3L-*n*-MoS<sub>2</sub>/ $p^+$ -MoS<sub>2</sub> and 1L-*n*-MoS<sub>2</sub>/ $p^+$ -MoS<sub>2</sub> heterostructures at  $V_{TG} = 0$  V at 20 K. Both structures are the same as that in **Figure 1a**, except for  $p^+$ -MoS<sub>2</sub>.

**Figure 6** a) Schematic illustration and b) optical micrograph of all 2D heterostructure TFET. c) Cross sectional TEM image of all 2D heterostructure at the solid rectangular in a). The number of MoS<sub>2</sub> layers is 3. d) Diode properties in the 3L-*n*-MoS<sub>2</sub>/*p*<sup>+</sup>-MoS<sub>2</sub> heterostructure at  $V_{TG} = 6$  V and different temperatures (20, 40, 80, 160, and 300 K). e) Arrhenius plot of the current at the reverse bias of -2 V for different heterostructures. f) Transfer characteristics for the three different heterostructure TFETs. Round sweep behavior is shown only for 3L-*n*-MoS<sub>2</sub>/*p*<sup>+</sup>-MoS<sub>2</sub> heterostructure (red & orange). g) SS as a function of *I*<sub>D</sub> for the three different heterostructure TFETs. Round sweep behavior is shown only for 3L-*n*-MoS<sub>2</sub>/*p*<sup>+</sup>-MoS<sub>2</sub> heterostructure (red & orange).

### TOC

### **Supporting information**

# All 2D heterostructure Tunnel Field Effect Transistors: Impact of band alignment and heterointerface quality

Keigo Nakamura<sup>†</sup>, Naoka Nagamura<sup>‡,§</sup>, Keiji Ueno<sup>I</sup>, Takashi Taniguchi<sup>‡</sup>, Kenji Watanabe<sup>‡</sup>, and Kosuke Nagashio<sup>†\*</sup>

<sup>†</sup>Department of Materials Engineering, The University of Tokyo, Tokyo 113-8656, Japan

<sup>‡</sup>National Institute for Materials Science, Ibaraki 305-0044, Japan,

<sup>§</sup>PRESTO, Japan Science and Technology Agency (JST), Saitama, 332-0012, Japan

<sup>I</sup>Department of Chemistry, Saitama University, Saitama 338-8570, Japan **E-mail:** nagashio@material.t.u-tokyo.ac.jp

Figure S1 Schematic drawing for the procedures of (i)~(iv) to stabilize  $p^+$ -WSe<sub>2</sub>.

**Figure S2** (a) Optical images of  $MoS_2$  from monolayer to 5 layers on PDMS. (b) Brightness of  $MoS_2$  on PDMS as a function of layer number. For the brightness calibration, the brightness of PDMS was initially adjusted to be 50 in 256 by changing the optical light intensity. Then, the brightness of  $MoS_2$  on PDMS was measured. The  $MoS_2$  layer number was confirmed by Raman and AFM measurements. These brightness values are plotted for two different samples. Moreover, in case of *h*-BN on PDMS, the brightness for 27-nm *h*-BN is found to be 85. The thickness of *h*-BN is roughly identified before the transfer and measured by AFM after the heterostructure formation.

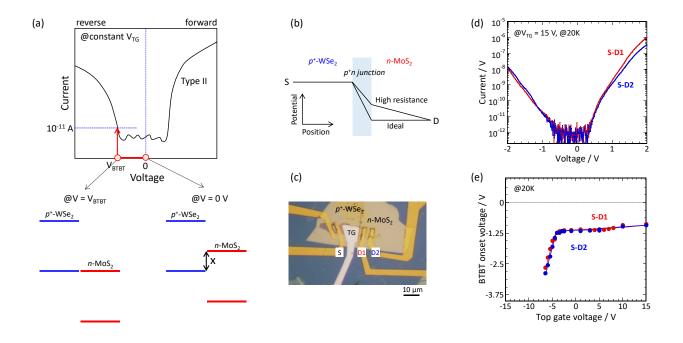

**Figure S3** Schematic illustration of the diode properties of the type II band alignment at the constant  $V_{\text{TG}}$  is shown in (a).  $V_{\text{BTBT}}$  is defined as the voltage at  $10^{-11}$  A. The band alignment @V = 0 V is type II with band overlap. When  $V_{\text{BTBT}}$  is applied, the band alignment becomes type III in which the energy level of the top of the valence band of  $p^+$ -WSe<sub>2</sub> is consistent with that of the conduction band minimum for *n*-MoS<sub>2</sub>. Therefore,  $V_{\text{BTBT}}$  is scaled to the band offset of "x". However, in order that  $V_{\text{BTBT}}$  implies the band offset, all the voltage drop must be consumed only at the  $p^+$ -*n* junction, not at the MoS<sub>2</sub> channel, as shown in (b). Therefore, the  $p^+$ -WSe<sub>2</sub>/4L-*n*-MoS<sub>2</sub> heterostructure with multi terminals were additionally fabricated in (c). Diode properties were measured using different terminals (S-D1 & S-D2) at  $V_{\text{TG}} = 15$  V and 20 K as shown in (d).  $V_{\text{BTBT}}$  is also plotted as a function of  $V_{\text{TG}}$  in (e). It is evident that there is no difference in  $V_{\text{BTBT}}$  between S-D1 and S-D2, supporting that there is no voltage drop in the access region of the *n*-MoS<sub>2</sub> channel. Since the voltage drop at the contact has been neglected due to the Ohmic contact, it can be said that  $V_{\text{BTBT}}$  implies there is band offset.

**Figure S4** 3D-nano ESCA installed at the University of Tokyo outstation beamline BL07LSU in SPring-8 used for chemical analysis. (a) Sample holder for the 3D-nano ESCA measurements, where the Ni/Au electrodes are grounded to the sample holder using Cu wire and carbon paste to prevent charge buildup on the SiO<sub>2</sub>/Si substrate during the ESCA measurements. (b) Low magnification optical image of the device. (c) Magnified optical image of the 3L-*n*-MoS<sub>2</sub>/*p*<sup>+</sup>-WSe<sub>2</sub> heterostructure on *h*-BN with Ni/Au electrodes. (d) Schematic illustration of the heterostructure, showing the measurement points (i) and (ii).

**Figure S5** Transfer characteristics of  $n-MoS_2/p^+-WSe_2$  and  $n-MoS_2/p^+-MoS_2$  TFETs with an ALD-Al<sub>2</sub>O<sub>3</sub> top gate insulator. The minimum SS values are shown.

**Figure S6** (a) Transfer characteristics (log scale) of 1L-n-MoS<sub>2</sub>/ $p^+$ -WSe<sub>2</sub> on the h-BN substrate with the h-BN top gate. The thicknesses of the top h-BN,  $p^+$ -WSe<sub>2</sub>, and bottom h-BN are 7.5 nm, 43 nm, and 30 nm, respectively. (b) Linear scale of (a). (c) (c-1) Comparison of  $I_D$  and  $I_S$  for h-BN/3L-n-MoS<sub>2</sub>/ $p^+$ -MoS<sub>2</sub>/h-BN heterostructure TFET. (c-2) SS values for positive and negative sweeps.

Note: When  $I_{MoS2}$  and  $I_{WSe2}$  are compared in (a), SS = "9.5 mV/dec" in  $I_{WSe2}$  is much smaller than that in I<sub>MoS2</sub>. The origin for this artificially small SS value is discussed here. The linear scale is shown in (b), where  $I_{TG}$  starts to flow at  $V_{TG} = -2$  V =  $V_{WSe2}$  because the h-BN layer is thin. Because of this leakage,  $I_{WSe2}+I_{MoS2}$  does not become zero, instead  $I_{WSe2} + I_{MoS2} = -I_{TG}$ , suggesting the contribution of  $I_{TG}$  in  $I_{WSe2}$ . Here,  $I_{WSe2}$  changes from the negative value to the positive value at  $V_{TG}@I_{WSe2} = 0$  A, which corresponds with the convex downward peak seen in (a). That is, the artificially small SS value for  $I_{WSe2}$  results from the contribution of the leakage current. Unfortunately, this convex downward peak is quite often reported with the artificially small SS values in the previous literatures. To avoid this, for the h-BN/3L-n-MoS<sub>2</sub>/p<sup>+</sup>-MoS<sub>2</sub>/h-BN heterostructure TFET,  $I_D$  must be shown to be consistent with  $I_S$ , as shown in (c). The consistent data between  $I_D$  and  $I_S$  supports low SS value achieved here. In terms of the gate leakage  $I_{TG}$  in (c), if there is no detectable gate current,  $I_{TG}$  generally shows ~10<sup>-13</sup> A in our normal measurement setup (medium power SMU in Keysight B1500). Although this current level is higher than  $I_D$  and Is, this is typical case for no detectable gate leakage current. If there is small but detectable current, MPSMU can detect the range of  $10^{-14}$  A or less, like  $I_{TG}$  in (a). Therefore, the current level of ~ $10^{-10}$ <sup>13</sup> A indicates no gate leakage.

**Figure S7** Schematic comparison of band alignments for out-of-plane and in-plane MoS<sub>2</sub>/WSe<sub>2</sub> junctions.<sup>[1]</sup> In the case of the out-of-plane structure, there is no dangling bond on the basal plane. Therefore, there is no dangling bond states in the interface. On the other hand, in case of in-plane structure, there is dangling bonds at the edge. When two 2D layers are ideally connected to each other, that is, there is no atomic defects at the interface, the dangling bond state remains at the position shown by the arrows. Therefore, out-of-plane heterostructures are preferable in terms of gate controllability.

Ref. [1] Y. Guo, J. Robertson, Appl. Phys. Lett. 2016, 108, 233104.