# **Runtime Enforcement of Programmable Logic Controllers**

RUGGERO LANOTTE, Università degli Studi dell'Insubria, Italy MASSIMO MERRO, Università degli Studi di Verona, Italy ANDREI MUNTEANU, Università degli Studi di Verona, Italy

With the advent of *Industry 4.0*, industrial facilities and critical infrastructures are transforming into an ecosystem of heterogeneous physical and cyber components, such as *programmable logic controllers*, increasingly interconnected and therefore exposed to *cyber-physical attacks*, *i.e.*, security breaches in cyberspace that may adversely affect the physical processes underlying *industrial control systems*.

In this paper, we propose a formal approach based on runtime enforcement to ensure specification compliance in networks of controllers, possibly compromised by colluding malware that may tamper with actuator commands, sensor readings, and inter-controller communications. Our approach relies on an ad-hoc sub-class of Ligatti et al.'s edit automata to enforce controllers represented in Hennessy and Regan's Timed Process Language. We define a synthesis algorithm that, given an alphabet  $\mathcal P$  of observable actions and a timed correctness property e, returns a monitor that enforces the property e during the execution of any (potentially corrupted) controller with alphabet  $\mathcal P$ , and complying with the property e. Our monitors correct and suppress incorrect actions coming from corrupted controllers and emit actions in full autonomy when the controller under scrutiny is not able to do so in a correct manner. Besides classical requirements, such as transparency and soundness, the proposed enforcement enjoys deadlock- and diverge-freedom of monitored controllers, together with scalability when dealing with networks of controllers. Finally, we test the proposed enforcement mechanism on a non-trivial case study, taken from the context of industrial water treatment systems, in which the controllers are injected with different malware with different malicious goals.

CCS Concepts: • Security and privacy → Formal security models; Cyber-physical systems security.

Additional Key Words and Phrases: Runtime enforcement, control systems security, PLC malware

# 1 INTRODUCTION

*Industrial Control Systems* (ICSs) are physical and engineered systems whose operations are monitored, coordinated, controlled, and integrated by a computing and communication core [53]. They represent the backbone of Critical Infrastructures for safety-critical applications such as electric power distribution, nuclear power production, and water supply.

The growing connectivity and integration in *Industry 4.0* has triggered a dramatic increase in the number of *cyber-physical attacks* [31] targeting ICSs, *i.e.*, security breaches in cyberspace that adversely affect the physical processes. Some notorious examples are: (i) the *Stuxnet* worm, which reprogrammed Siemens PLCs of nuclear centrifuges in the nuclear facility of Natanz in Iran [35]; (ii) the *CRASHOVERRIDE* attack on the Ukrainian power grid, otherwise known as Industroyer [58]; (iii) the recent *TRITON/TRISIS* malware that targeted a petrochemical plant in Saudi Arabia [19].

One of the key components of ICSs are *Programmable Logic Controllers*, better known as PLCs. They control mission-critical electrical hardware such as pumps or centrifuges, effectively serving as a bridge between the cyber and the physical worlds. PLCs have an ad-hoc architecture to execute simple repeating processes known as *scan cycles* (IEC 61131-3 [1]). Each scan cycle consists of three phases: (i) reading of sensor measurements of the physical process; (ii) execution of the controller

Authors' addresses: Ruggero Lanotte, Università degli Studi dell'Insubria, Dipartimento di Scienze Umane e dell'Innovazione per il Territorio, via Sant'Abbondio 12, Como, 22100, Italy, ruggero.lanotte@uninsubria.it; Massimo Merro, Università degli Studi di Verona, Dipartimento di Informatica, strada Le Grazie 15, Verona, 37134, Italy, massimo.merro@univr.it; Andrei Munteanu, Università degli Studi di Verona, Dipartimento di Informatica, strada Le Grazie 15, Verona, 37134, Italy, andrei.munteanu@univr.it.

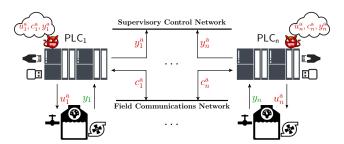

Fig. 1. A network of compromised PLCs:  $y_i$  denote genuine sensor measurements,  $y_i^a$  are corrupted sensor measurements,  $u_i^a$  corrupted actuator commands, and  $c_i^a$  denote corrupted inter-controller communications.

code to compute how the physical process should evolve; (iii) transmission of commands to the actuator devices to govern the physical process as desired.

Due to their sensitive role in controlling industrial processes, successful exploitation of PLCs can have severe consequences on ICSs. In fact, although modern controllers provide security mechanisms to allow only legitimate firmware to be uploaded, the running code can be typically altered by anyone with network or USB access to the controllers (see Figure 1). Published scan data shows how thousands of PLCs are directly accessible from the Internet to improve efficiency [52]. Thus, despite their responsibility, controllers are vulnerable to several kinds of attacks, including PLC-Blaster worm [59], Ladder Logic Bombs [28], and PLC PIN Control attacks [5].

Extra trusted hardware components have been proposed to enhance the security of PLC architectures [45, 46]. For instance, McLaughlin [45] proposed a policy-based enforcement mechanism to mediate the actuator commands transmitted by the PLC to the physical plant. Mohan et al. [46] introduced a different architecture, in which every PLC runs under the scrutiny of a monitor which looks for deviations with respect to safe behaviours. Both architectures have been validated by means of simulation-based techniques. However, as far as we know, formal methodologies have been rarely used to model and formally verify security-oriented architectures for ICSs.

Runtime enforcement [22, 40, 56] is a formal verification/validation technique aiming at correcting possibly-incorrect executions of a system-under-scrutiny (SuS). It employs a kind of monitor [23] that acts as a *proxy* between the SuS and the environment interacting with it. At runtime, the monitor *transforms* any incorrect executions exhibited by the SuS into correct ones by either *replacing*, *suppressing* or *inserting* observable actions on behalf of the system. The effectiveness of the enforcement depends on the achievement of the two following general principles [40, 56]:

- transparency, i.e., the enforcement must not alter correct executions of the SuS;

- soundness, i.e., incorrect executions of the SuS must be prevented.

In this paper, we propose a *formal approach* based on *runtime enforcement* to ensure specification compliance in networks of controllers possibly compromised by *colluding malware* that may tamper with actuator commands, sensor readings, and inter-controller communications. combined with *automatic recovery mechanisms*.

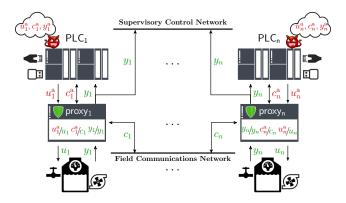

Our *goal* is to enforce potentially corrupted controllers using *secure proxies* based on a subclass of Ligatti et al.'s edit automata [40]. These automata will be *synthesised* from enforceable *timed correctness properties* to form networks of *monitored controllers*, as in Figure 2. The proposed enforcement will enjoy both transparency and soundness together with the following features:

- determinism preservation, i.e., the enforcement should not introduce nondeterminism;

- *deadlock-freedom*, *i.e.*, the enforcement should not introduce deadlocks;

Fig. 2. A network of monitored controllers.

- divergence-freedom, i.e., the enforcement should not introduce divergencies;

- mitigation of incorrect/malicious activities;

- scalability, i.e., the enforcement mechanism should scale to networks of controllers.

Obviously, when a controller is compromised, these objectives can be achieved only with the introduction of a physically independent *secure proxy*, as advocated by McLaughlin and Mohan et al. [45, 46], which does not have any Internet or USB access, and which is connected with the monitored controller via *secure channels*. This may seem like we just moved the problem over to securing the proxy. However, this is not the case because the proxy only needs to enforce a *timed correctness property* of the system, while the controller does the whole job of controlling the physical process relying on potentially dangerous communications via the Internet or the USB ports. Thus, any upgrade of the control system will be made to the controller and not to the secure proxy. Of course, by no means runtime reconfigurations of the secure proxy should be allowed as its enforcing should be based on the physics of the plant itself and not on the controller code.

Contribution. Fist of all, we define the attacker model and the attacker objectives in an enforced ICS architecture such as that depicted in Figure 2. Then, we introduce a formal language to specify controller programs. For this very purpose, we resort to *process calculi*, a successful and widespread formal approach in *concurrency theory* for representing complex systems, such as mobile systems [16] and cyber-physical systems [39], and used in many areas, including verification of security protocols [3, 4] and security analysis of *cyber-physical attacks* [38]. Thus, we define a simple timed process calculus, based on Hennessy and Regan's *Timed Process Language* (TPL) [29], for specifying controllers, finite-state enforcers, and networks of communicating monitored controllers.

Then, we define a simple description language to express *timed correctness properties* that should hold for a (possibly unbounded) number of scan cycles of the monitored controller. This will allow us to abstract over controllers implementations, focusing on general properties which may even be shared by completely different controllers. In this regard, we might resort to one of the several logics existing in the literature for monitoring timed concurrent systems, and in particular cyber-physical systems (see, *e.g.*, [9, 24]). However, the peculiar iterative behaviour of controllers convinced us to adopt the sub-class of *regular expressions* that can be recognised by finite automata whose cycles always contain at least one final state; this is the largest class of regular properties that can be enforced by finite-state Ligatti et at.'s edit automata (see Beauquier et al.'s work [10]). In Section 5, we express a wide class of correctness properties for controllers in terms of (our) regular properties.

After defining a formal language to describe controller properties, we provide a *synthesis function*  $\langle - \rangle^{\mathcal{P}}$  that, given an alphabet  $\mathcal{P}$  of observable actions (sensor readings, actuator commands, and

inter-controller communications) and a deterministic regular property e combining events of  $\mathcal{P}$ , returns an edit automaton  $\langle e \rangle^{\mathcal{P}}$ . The resulting enforcement mechanism will ensure the required features mentioned before: transparency, soundness, determinism preservation, deadlock-freedom, divergence-freedom, mitigation and scalability. Then, we propose a non-trivial case study, taken from the context of industrial water treatment systems, and implemented as follows: (i) the physical plant is simulated in Simulink [44]; (ii) the open source PLCs are implemented in OpenPLC [8] and executed on Raspberry Pi; (iii) the enforcers run on connected FPGAs. In this setting, we test our enforcement mechanism when injecting the PLCs with 5 different malware, with different goals.

Outline. Section 2 describes the attacker model and the attacker objectives. Section 3 gives a formal language for monitored controllers. Section 4 defines the case study. Section 5 provides a language of regular properties to express controller behaviours; it also contains a taxonomy of properties expressible in the language. Section 6 contains the algorithm to synthesise monitors from regular properties, together with the main results. Section 7 discusses the implementation of the case study when exposed to five different attacks. Section 8 is devoted to related work. Section 9 draws conclusions and discusses future work. Technical proofs can be found in the appendix.

# 2 ATTACKER MODEL AND ATTACKER OBJECTIVES

In the following sections, we will propose an enforcement-based architecture for ICSs (as those depicted in Figure 2) to counter attacks complying with the following *attacker model*:

- malware injected in one or more PLCs may forge/drop actuator commands, modify sensor readings coming from the plant, forge/drop inter-controller communications;

- malware injected in different PLCs of the same field communications network may collaborate/communicate with each other to achieve common objectives;

- the attacker runtime behaviour may vary as it may depend on the received sensor signals and the communications with other PLCs;

- malicious alterations of sensor signals at network level, or within the sensor devices, are not allowed (they are out of the scope of this paper);

- scan cycles must be completed within a specific time, called *maximum cycle limit*, which depends on the controlled physical process; if this time limit is violated then the controller stops and throws an exception [59]; we assume that the injected malware never violates the maximum cycle limit because not interested in causing the immediate shutdown of a PLC;

- the enforcers added in the architecture are physically independent *secure proxies* with no Internet or USB access, and connected with the controller via *secure channels*; as a consequence, the measurements transmitted to the *supervisory control network* will not be corrupted;

- runtime reconfigurations of secure proxies are not allowed.

Thus, in general, the attacker objectives can be resumed in alteration/forgery of PLC actuator commands and/or communication messages between PLCs to eventually affect the evolution of the controlled physical processes, and/or transmit fake signals to the supervisory control network.

#### 3 A FORMAL LANGUAGE FOR MONITORED CONTROLLERS

In this section, we introduce the *Timed Calculus of Monitored Controllers*, called TCMC, as an abstract formal language to express networks of controllers integrated with edit automata sitting on the network interface of each controller to monitor/correct their interactions with the rest of the system. Basically, TCMC extends Hennessy and Regan's *Timed Process Language* (TPL) [29] with monitoring edit automata. Like TPL time proceeds in *discrete time slots* separated by tick-actions.

Let us start with some preliminary notation. We use  $s, s_k \in Sens$  to name sensor signals;  $a, a_k \in Act$  to indicate actuator commands;  $c, c_k \in Chn$  for channels;  $c, c_k \in Chn$  for generic names.

Controllers. In our setting, controllers are nondeterministic sequential timed processes evolving through three main phases: sensing of sensor signals, communication with other controllers, and actuation. For convenience, we use five different syntactic categories to distinguish the five main states of a controller:  $\mathbb{C}trl$  for initial states,  $\mathbb{Sleep}$  for sleeping states,  $\mathbb{Sens}$  for sensing states,  $\mathbb{Com}$  for communication states, and  $\mathbb{Act}$  for actuation states. In its initial state, a controller is a recursive process waiting for signal stabilisation in order to start the sensing phase:

$$\begin{array}{cccc} \mathbb{C} \mathrm{tr} \mathbb{I} \ni P & ::= & X \\ \mathbb{S} \mathbb{I} \text{eep} \ni W & ::= & \mathrm{tick}.W & \middle| & S \end{array}$$

The main process describing a controller consists of some *recursive process* defined via equations of the form X = tick.W, with  $W \in \mathbb{Sleep}$ ; here, X is a *process variable* that may occur (free) in W. For convenience, our controllers always have at least one initial timed action tick to ensure *time-guarded recursion*, thus avoiding undesired *zeno behaviours* [30]: the number of untimed actions between two tick-actions is always finite. Then, after a determined sleeping period, when sensor signals get stable, the sensing phase can start.

During the sensing phase, the controller waits for a *finite* number of admissible sensor signals. If none of those signals arrives in the current time slot then the controller will *timeout* moving to the following time slot (we adopt the TPL construct  $\lfloor \cdot \rfloor$  for timeout). The syntax is the following:

$$Sens \ni S ::= \left[\sum_{i \in I} s_i . S_i\right] S \mid C$$

where  $\sum_{i \in I} s_i.S_i$  denotes the standard construct for nondeterministic choice. Once the sensing phase is concluded, the controller starts its calculations that may depend on *communications* with other controllers governing different physical processes. Controllers communicate with each other for mainly two reasons: either to receive notice about the state of other physical sub-processes or to require an actuation on a physical process which is out of their control. As in TPL, we adopt a *channel-based handshake point-to-point* communication paradigm. Note that, in order to avoid starvation, communication is always under timeout. The syntax for the communication phase is:

$$\mathbb{C}_{\text{Omm}} \ni C \quad ::= \quad \left[ \sum_{i \in I} c_i . C_i \right] C \quad \left[ \quad \bar{c} . C \right] C \quad A$$

In the actuation phase a controller eventually transmits a *finite* sequence of commands to actuators, and then, it emits a *fictitious system signal* end to denote the end of the scan cycle. After that, the whole scan cycle can restart. Formally,

$$Act \ni A ::= \overline{a}.A \mid end.X$$

REMARK 1 (SCAN CYCLE DURATION AND MAXIMUM CYCLE LIMIT). The scan cycle of a PLC must be completed within a specific time, called maximum cycle limit, which depends on the controlled physical process; if this time limit is violated the the controller stops and throws an exception [59]. Thus, the signal end must occur well before the maximum cycle limit of the controller. We actually work under the assumption that our controllers successfully complete their scan cycle in less than half of the maximum cycle limit. The reasons for this assumption will be clarified in Remark 4. Please, notice that it is easy to statically derive the maximum duration of a scan cycle expressed in our calculus by simply counting the maximum number of tick-prefixes occurring between two subsequent end-prefixes.

The operational semantics in Table 1 is along the lines of Hennessy and Regan's TPL [29]. In the following, we use the metavariable  $\alpha$  to range over the set of all (observable) controller actions:  $\{s, \overline{a}, \overline{c}, c, \text{tick}, \text{end}\}$ . These actions denote: sensor readings, actuator commands, channel transmissions, channel receptions, passage of time, and end of scan cycles, respectively. Notice that at our level of abstraction we represent only the observable behaviour of PLCs: internal computations are not modelled within PLCs; although, we do have  $\tau$ -actions to express communications between two PLCs, as the reader will notice in Table 2.

$$(Sleep) \xrightarrow{-} \frac{-}{\operatorname{tick}.W} \xrightarrow{\operatorname{tick}} W$$

$$(Rec) \xrightarrow{X} \xrightarrow{\operatorname{tick}} W$$

$$(TimeoutS) \xrightarrow{-} C$$

$$(TimeoutInC) \xrightarrow{-} C$$

$$(TimeoutInC) \xrightarrow{-} C$$

$$(TimeoutOutC) \xrightarrow{-} C$$

$$(TimeoutOutC) \xrightarrow{-} C$$

$$(Vince) \xrightarrow{-} C$$

$$(Vince) \xrightarrow{-} C$$

$$(End) \xrightarrow{-} C$$

$$(Rec) \xrightarrow{X} \xrightarrow{\operatorname{tick}} W$$

$$(TimeoutS) \xrightarrow{-} C$$

$$(TimeoutOutC) \xrightarrow{-} C$$

$$(End) \xrightarrow{-} C$$

Table 1. LTS for controllers.

REMARK 2 (ATTACKER MODEL AND end-SIGNAL). In our abstract representation of PLCs, the end-signal is not really part of the (possibly compromised) PLC program but it is rather a system signal denoting the end of a scan cycle. As a consequence, in accordance with our attacker model, we assume that this fictitious signal cannot be dropped or forged by the attacker.

Monitored controllers. The core of our enforcement relies on (timed) finite-state Ligatti et al.'s edit automata [40], i.e., a particular class of automata specifically designed to allow/suppress/insert actions in a generic system in order to preserve its correct behaviour. The syntax is as follows:

$$\mathbb{E}dit \ni E, F ::= go \mid \sum_{i \in I} \lambda_i.E_i \mid X$$

The special automaton go will admit any action of the monitored system. The edit automaton  $\sum_{i \in I} \lambda_i.\mathsf{E}_i$  enforces an action  $\lambda_i$ , and then continues as  $\mathsf{E}_i$ , for any  $i \in I$ , with I finite. Here, the symbol  $\lambda$  ranges over: (i)  $\alpha$  to allow the action  $\alpha$ , (ii)  $\alpha$  to suppress the action  $\alpha$ , and (iii)  $\alpha_1 < \alpha_2$ , for  $\alpha_1 \neq \alpha_2$ , to insert the action  $\alpha_1$  before the action  $\alpha_2$ . Recursive automata  $\mathsf{X}$  are defined via equations of the form  $\mathsf{X} = \mathsf{E}$ , where the automata variable  $\mathsf{X}$  may occur (free) in  $\mathsf{E}$ .

The operational semantics of our edit automata is given via the following transition rules:

$$(Go) \xrightarrow{\frac{-}{\text{go} \xrightarrow{\alpha} \text{go}}} (Edit) \xrightarrow{j \in I} \xrightarrow{\sum_{i \in I} \lambda_i \cdot E_i} \xrightarrow{\lambda_j} E_j (recE) \xrightarrow{X = E} \xrightarrow{E} \xrightarrow{\lambda} E'$$

Our *monitored controllers*, written  $E \bowtie \{J\}$ , consist of a controller J, for  $J \in \mathbb{Ctrl} \cup \mathbb{Sleep} \cup \mathbb{Sens} \cup \mathbb{Comm} \cup \mathbb{Act}$ , and an edit automaton E enforcing the behaviour of J, according to the following transition rules, presented in the style of [42]:

$$(\text{Allow}) \ \ \frac{\mathsf{E} \xrightarrow{\alpha} \mathsf{E}' \ J \xrightarrow{\alpha} J'}{\mathsf{E} \bowtie \{J\} \xrightarrow{\alpha} \mathsf{E}' \bowtie \{J'\}} \ \ (\text{Suppress}) \ \ \frac{\mathsf{E} \xrightarrow{\neg \alpha} \mathsf{E}' \ J \xrightarrow{\alpha} J'}{\mathsf{E} \bowtie \{J\} \xrightarrow{\tau} \mathsf{E}' \bowtie \{J'\}} \ \ (\text{Insert}) \ \ \frac{\mathsf{E} \xrightarrow{\alpha_1 < \alpha_2} \mathsf{E}' \ J \xrightarrow{\alpha_2} J'}{\mathsf{E} \bowtie \{J\} \xrightarrow{\alpha_1} \mathsf{E}' \bowtie \{J\}}$$

Rule (Allow) is used for allowing observable actions emitted by the controller under scrutiny. By an application of Rule (Suppress), incorrect actions  $\alpha$  emitted by (possibly corrupted) controllers J are suppressed, *i.e.*, converted into (silent)  $\tau$ -actions. Rule (Insert) is used to insert an action  $\alpha_1$  before an action  $\alpha_2$  of the controller. In the following, the metavariable  $\beta$  will range over the same set of actions as  $\alpha$ , together with the *silent action*  $\tau$ .

$$(ParL) \xrightarrow{N_1 \xrightarrow{\alpha} N_1'} N_1 \parallel N_2 \xrightarrow{\alpha} N_1' \parallel N_2 \qquad (ChnSync) \xrightarrow{N_1 \xrightarrow{c} N_1'} N_2 \xrightarrow{\overline{c}} N_2' \xrightarrow{N_1' \parallel N_2} N_2 \parallel N_1 \xrightarrow{\tau} N_1' \parallel N_2' \xrightarrow{r} N_2' \parallel N_1'$$

$$(ParR) \xrightarrow{N_2 \xrightarrow{\alpha} N_2'} N_1 \parallel N_2 \xrightarrow{\alpha} N_1 \parallel N_2' \qquad (TimeSync) \xrightarrow{N_1 \xrightarrow{\text{tick}} N_1' N_2 \xrightarrow{\text{tick}} N_2' N_1 \parallel N_2 \xrightarrow{\tau}} N_1 \parallel N_2 \xrightarrow{\tau} N_1' \parallel N_2'$$

Table 2. LTS for field communications networks of monitored controllers.

Here, we wish to stress that, like Ligatti et al. [40], we are interested in deterministic (and hence implementable) enforcement. With the following technical definitions we extract from enforcer actions  $\lambda$  both: (i) the controller triggering actions, and (ii) the resulting output actions.

DEFINITION 1. Let  $\lambda \in \{\alpha, -\alpha, \alpha_1 < \alpha_2\}$  be an arbitrary action for edit automata, we write  $trigger(\lambda)$  to denote the controller action  $triggering \lambda$ , defined as:  $trigger(\alpha) = \alpha$ ,  $trigger(-\alpha) = \alpha$  and  $trigger(\alpha_1 < \alpha_2) = \alpha_2$ . Similarly, we write  $out(\lambda)$  to denote the output action prescribed by  $\lambda$ , defined as:  $out(\alpha) = \alpha$ ,  $out(-\alpha) = \tau$  and  $out(\alpha_1 < \alpha_2) = \alpha_1$ . Given a trace  $t = \lambda_1 \cdots \lambda_n$ , we write out(t) for the trace  $out(\lambda_1) \cdots out(\lambda_n)$ .

Now, we provide a definition of deterministic enforcer along the lines of Pinisetty at al. [50].

DEFINITION 2 (DETERMINISTIC ENFORCER). A edit automaton  $E \in \mathbb{E}\operatorname{dist}$  is said to be deterministic iff in every term  $\sum_{i\in I}\lambda_i.E_i$  that appears in E there are no  $\lambda_k$  and  $\lambda_j$ , for  $k,j\in I$ ,  $k\neq j$ , such that  $\operatorname{trigger}(\lambda_k) = \operatorname{trigger}(\lambda_j)$  and  $\operatorname{out}(\lambda_k) = \operatorname{out}(\lambda_j)$ .

Finally, we can easily generalise the concept of monitored controller to a *field communications network* of parallel monitored controllers, each one acting on different actuators, and exchanging information via channels. These networks are formally defined via a straightforward grammar:

$$\mathbb{F}\mathbb{N}$$

et  $\ni N ::= \mathbb{E} \bowtie \{J\} \mid N \parallel N$

with the operational semantics defined in Table 2.

Notice that monitored controllers may interact with each other via channel synchronisation (see Rule (ChnSync)). Moreover, via rule (TimeSync) they may evolve in time only when channel synchronisation may not occur (our controllers do not admit zeno behaviours). This ensures *maximal progress* [29], a desirable time property when modelling real-time systems: channel communications will never be postponed.

DEFINITION 3 (EXECUTION TRACES). Given three finite execution traces  $t_c = \alpha_1 \dots \alpha_k$ ,  $t_e = \lambda_1 \dots \lambda_l$ , and  $t_m = \beta_1 \dots \beta_n$ , for controllers, edit automata and monitored controllers, respectively. We write: (i)  $P \xrightarrow{t_c} P'$ , as an abbreviation for  $P = P_0 \xrightarrow{\alpha_1} \dots \xrightarrow{\alpha_k} P_k = P'$ ; (ii)  $E \xrightarrow{t_e} E'$ , as an abbreviation for  $E = E_0 \xrightarrow{\lambda_1} \dots \xrightarrow{\lambda_l} E_l = E'$ ; (iii)  $E \xrightarrow{t_m} E'$ , as an abbreviation for  $E = E_0 \xrightarrow{\lambda_1} \dots \xrightarrow{\lambda_l} E_l = E'$ ; (iii)  $E \xrightarrow{t_m} E'$ , as an abbreviation for  $E = E_0 \xrightarrow{\lambda_1} \dots \xrightarrow{\lambda_l} E_l = E'$ ; (iii)  $E \xrightarrow{t_m} E'$ , as an abbreviation for  $E = E_0 \xrightarrow{\lambda_1} \dots \xrightarrow{\lambda_l} E_l = E'$ ; (iii)  $E \xrightarrow{t_m} E'$

In the rest of the paper we adopt the following notations.

Notation 1. As usual, we write  $\epsilon$  to denote the empty trace. Given a trace t we write |t| to denote the length of t, i.e., the number of actions occurring in t. Given a trace t we write  $\hat{t}$  to denote the trace obtained by removing the  $\tau$ -actions. Given two traces t' and t'', we write  $t' \cdot t''$  for the trace resulting from the concatenation of t' and t''. For  $t = t' \cdot t''$  we say that t' is a prefix of t and t'' is a suffix of t.

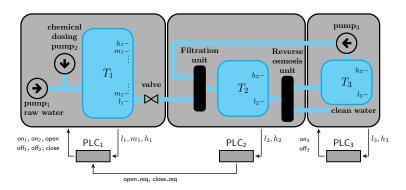

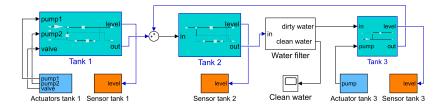

Fig. 3. A simplified Industrial Water Treatment System.

# 4 USE CASE: THE SWAT SYSTEM

In this section, we describe how to specify in TCMC a non-trivial network of PLCs to control (a simplified version of) the *Secure Water Treatment system* (SWaT) [43].

SWaT represents a scaled down version of a real-world industrial water treatment plant. The system consists of 6 stages, each of which deals with a different treatment, including: chemical dosing, filtration, dechlorination, and reverse osmosis. For simplicity, in our use case, depicted in Figure 3, we consider only three stages. In the first stage, raw water is *chemically dosed* and pumped in a tank  $T_1$ , via two pumps  $pump_1$  and  $pump_2$ . A *valve* connects  $T_1$  with a *filtration unit* that releases the treated water in a second tank  $T_2$ . Here, we assume that the flow of the incoming water in  $T_1$  is greater than the outgoing flow passing through the valve. The water in  $T_2$  flows into a *reverse osmosis unit* to reduce inorganic impurities. In the last stage, the water coming from the reverse osmosis unit is either distributed as clean water, if required standards are met, or stored in a backwash tank  $T_3$  and then pumped back, via a pump  $pump_3$ , to the filtration unit. Here, we assume that tank  $T_2$  is large enough to receive the whole content of tank  $T_3$  at any moment.

The SWaT system has been used to provide a dataset containing physical and network data recorded during 11 days of activity [27]. Part of this dataset contains information about the execution of the system in isolation, while a second part records the effects on the system when exposed to different kinds of cyber-physical attacks. Thus, for instance, (i) *drops* of commands to activate  $pump_2$  may affect the quality of the water, as they would affect the correct functioning of the chemical dosing pump; (ii) *injections* of commands to close the valve between  $T_1$  and  $T_2$ , may give rise to an overflow of tank  $T_1$  if this tank is full; (iii) *integrity attacks* on the signals coming from the sensor of the tank  $T_3$  may result in damages of the pump  $pump_3$  if it is activated when  $T_3$  is empty.

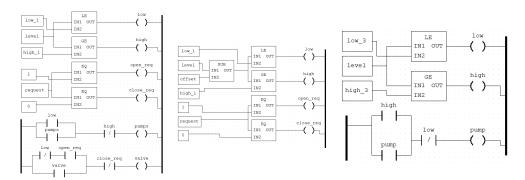

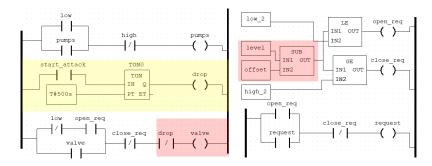

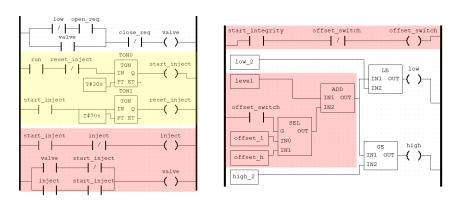

Each tank is controlled by its own PLC. The programs of the three PLCs, expressed in terms of ladder logic, are given in Figure 4. In the following, we give their descriptions in TCMC.

Let us start with the code of the controller  $PLC_1$  managing the tank  $T_1$ . Its definition is given in terms of two equations to deal with the case when the two pumps,  $pump_1$  and  $pump_2$ , are both off and both on, respectively. Intuitively, when the pumps are off, the level of water in  $T_1$  drops until it reaches its low level (event  $l_1$ ); when this happens both pumps are turned on and they remain so

Fig. 4. Ladder logics of the three PLCs controlling the system in Figure 3.

until the tank is refilled, reaching its high level (event  $h_1$ ). Formally,

Thus, for instance, when the pumps are off the PLC<sub>1</sub> waits for one time slot (to get stable sensor signals) and then checks the water level of the tank  $T_1$ , distinguishing between three possible states. If  $T_1$  reaches its low level (signal  $l_1$ ) then the pumps are turned on (commands  $\overline{on_1}$  and  $\overline{on_2}$ ) and the valve is closed (command  $open_req$ ). Otherwise, if the tank  $T_1$  is at some intermediate level between low and high (signal  $m_1$ ) then PLC<sub>1</sub> listens for requests arriving from PLC<sub>2</sub> to open/close the valve. Precisely, if the PLC gets an  $open_req$  request then it opens the valve, letting the water flow from  $T_1$  to  $T_2$ , otherwise, if it gets a  $close_req$  request then it closes the valve; in both cases the pumps remain off. If the level of the tank is high (signal  $h_1$ ) then the requests of water coming from PLC<sub>2</sub> are served as before, but the two pumps are eventually turned off (commands  $off_1$  and  $off_2$ ).

PLC<sub>2</sub> manages the water level of tank  $T_2$ . Its code consists of the two equations to model the filling (state  $\uparrow$ ) and the emptying (state  $\downarrow$ ) of the tank. Formally,

$$\begin{split} P_2^\uparrow &= \operatorname{tick.}(\left\lfloor l_2. \left\lfloor \overline{\operatorname{open\_req}}.\operatorname{end.} P_2^\uparrow \right\rfloor \operatorname{end.} P_2^\uparrow + m_2. \left\lfloor \overline{\operatorname{open\_req}}.\operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow + h_2. \left\lfloor \overline{\operatorname{close\_req}}.\operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow \\ P_2^\downarrow &= \operatorname{tick.}(\left\lfloor l_2. \left\lfloor \overline{\operatorname{open\_req}}.\operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow + m_2. \left\lfloor \overline{\operatorname{close\_req}}.\operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow + h_2. \left\lfloor \overline{\operatorname{close\_req}}.\operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow \right\rfloor \operatorname{end.} P_2^\downarrow \end{split}$$

Here, after one time slot, the level of  $T_2$  is checked. If the level is low (signal  $l_2$ ) then PLC<sub>2</sub> sends a request to PLC<sub>1</sub>, via the channel open\_req, to open the valve that lets the water flow from  $T_1$  to  $T_2$ , and then returns. Otherwise, if the level of tank  $T_2$  is high (signal  $h_2$ ) then PLC<sub>2</sub> asks PLC<sub>1</sub> to close the valve, via the channel close\_req, and then returns. Finally, if the tank  $T_2$  is at some intermediate level between  $l_2$  and  $h_2$  (signal  $m_2$ ) then the valve remains open (respectively, closed) when the tank is refilling (respectively, emptying).

Finally, PLC<sub>3</sub> manages the water level of the backwash tank  $T_3$ . Its code consists of two equations to deal with the case when the pump  $pump_3$  is off and on, respectively. Formally,

$$\begin{array}{lll} P_3^{\mathrm{off}} &=& \mathrm{tick.}(\lfloor l_3.\overline{\mathrm{off_3.end.}}P_3^{\mathrm{off}} &+& m_3.\overline{\mathrm{off_3.end.}}P_3^{\mathrm{off}} &+& h_3.\overline{\mathrm{on_3.end.}}P_3^{\mathrm{on}} \rfloor \big(\mathrm{off_3.end.}P_3^{\mathrm{off}}\big) \\ P_3^{\mathrm{on}} &=& \mathrm{tick.}(\lfloor l_3.\overline{\mathrm{off_3.end.}}P_3^{\mathrm{off}} &+& m_3.\overline{\mathrm{on_3.end.}}P_3^{\mathrm{on}} &+& h_3.\overline{\mathrm{on_3.end.}}P_3^{\mathrm{on}} \big) \big(\mathrm{off_3.end.}P_3^{\mathrm{off}}\big) \\ \end{array}$$

Here, after one time slot, the level of tank  $T_3$  is checked. If the level is low (signal  $l_3$ ) then PLC<sub>3</sub> turns off the pump  $pump_3$  (command  $\overline{\text{off}_3}$ ), and then returns. Otherwise, if the level of  $T_3$  is high (signal  $h_3$ ) then the pump is turned on (command  $\overline{\text{on}_3}$ ) until the whole content of  $T_3$  is pumped back into the filtration unit of  $T_2$ .

Examples of correctness properties and attacks. In a system similar to that described above, one would expect a number of properties capturing the correct functioning of system components. Let us provide a few examples of such correctness properties and some specific attacks that may potentially invalidate these properties.

A first property might say that if  $PLC_1$  receives a request to open the valve between tanks  $T_1$  and  $T_2$  then the same valve will be eventually closed early enough to prevent water overflow in tank  $T_2$ . This property certainly holds when the system is not exposed to any attack. However, a malware injected in  $PLC_1$  might try to undermine this property by tampering either with the actuator dedicated to the valve or with the requests of  $PLC_2$  to open/close the valve. In particular, a malicious request to open the valve might be forged by an attacker injected in  $PLC_2$ . Thus, another desired correctness property might say that whenever the tank  $T_2$  is full then  $PLC_2$  will never ask for incoming water from tank  $T_1$ . Finally, another expected property might say that  $pump_3$  will never work without enough water in tank  $T_3$ . Again, an attacker injected in  $PLC_3$  might try to undermine this property by tampering either with the actuator dedicated to the pump or with the sensor measuring the level of tank  $T_3$ .

In Section 7.3 we will provide formal definitions for patterns template of structured correctness properties that are suitable for enforcing correct behaviours of our PLCs.

#### 5 A FORMAL LANGUAGE FOR CONTROLLER PROPERTIES

In this section, we provide a simple description language to express *correctness properties* that we may wish to enforce at runtime in our controllers. As discussed in the Introduction, we resort to (a sub-class of) *regular properties* as they allow us to express interesting classes of properties referring to one or more scan cycles of a controller. The proposed language distinguishes between two kinds of properties: (i) *global properties*,  $e \in \mathbb{Prop}G$ , to express general controllers' execution traces; (ii) *local properties*,  $p \in \mathbb{Prop}L$ , to express traces confined to a finite number of consecutive scan cycles. The two families of properties are formalised via the following regular grammar:

```

\begin{array}{lll} e \in \mathbb{P} \mathbb{rop} \mathbb{G} & ::= & p^* \mid e_1 \cap e_2 \\ p, q \in \mathbb{P} \mathbb{rop} \mathbb{L} & ::= & \epsilon \mid p_1; p_2 \mid \cup_{i \in I} \pi_i . p_i \mid p_1 \cap p_2 \end{array}

```

where  $\pi_i \in \text{Events} \triangleq \text{Sens} \cup \overline{\text{Act}} \cup \text{Chn}^* \cup \{\text{tick}\} \cup \{\text{end}\}\$ denote *atomic properties*, called *events*, that may occur as prefix of a property. With an abuse of notation, we use the symbol  $\epsilon$  to denote both the *empty property* and the *empty trace*.

The *semantics* of our logic is naturally defined in terms of sets of execution traces which satisfy a given property; its formal definition is given in Table 3.

However, the syntax of our logic is a bit too permissive with respect to our intentions, as it allows us to describe partial scan cycles, *i.e.*, cycles that have not completed. Thus, we restrict ourselves to considering properties which builds on top of local properties associated to *complete scan cycles*, *i.e.*, scan cycles whose last action is an end-action. Formally,

Definition 4. Well-formed properties are defined as follows:

- the local property end. $\epsilon$  is well formed;

- a local property of the form  $p_1$ ;  $p_2$  is well formed if  $p_2$  is well formed;

- a local property of the form  $p_1 \cap p_2$  is well formed if both  $p_1$  and  $p_2$  are well formed;

Table 3. Trace semantics of our regular properties.

- a local property of the form  $\bigcup_{i \in I} \pi_i . p_i$  is well formed if either  $\pi_i . p_i = \text{end.} \epsilon$  or  $p_i$  is well formed, for any  $i \in I$ ;

- a global property p\* is well formed if p is well-formed;

- a global property  $e_1 \cap e_2$  is well-formed if both  $e_1$  and  $e_2$  are well-formed.

In the rest of the paper, we always assume to work with well-formed properties. Moreover, we adopt the following notations and/or abbreviations on properties.

Note that our properties are in general nondeterministic. However, since we are interested in deterministic enforcers, in the following we will focus on deterministic enforcing properties.

Definition 5 (Deterministic properties). A global property  $e \in \mathbb{P}rop\mathbb{G}$  is said to be deterministic if for any sub-term  $\bigcup_{i \in I} \pi_i.p_i$  appearing in e, we have  $\pi_k \neq \pi_h$ , for any  $k, h \in I, k \neq h$ .

# 5.1 Local properties

As already said, local properties describe execution traces which are limited to a finite number of scan cycles. Let us present a number of significant local properties that can be expressed in our language of regular properties. In the following, we assume a fixed maximum number of actions, maxa, that may occur within a single scan cycle of our controllers, *i.e.*, between two subsequent end-actions.

5.1.1 Basic properties. They prescribe conditional, eventual and persistent behaviours.

Conditional. These properties say that when a (pure) untimed event  $\pi$  occurs in the current scan cycle then some property p should be satisfied. More generally, for  $\pi_i \in PUE$ vents and  $p_i \in PTOpL$ , we write Case ( $\bigcup_{i \in I} \{(\pi_i, p_i)\}$ ) to denote the property  $q_k$ , for  $k = \max_i$ , defined as follows:

- $q_k \triangleq \text{end} \cup \bigcup_{i \in I} \pi_i.p_i \cup (PEvents \setminus \bigcup_{i \in I} \{\pi_i\}).q_{k-1}, \text{ for } 0 < k \leq \max$

- $q_0 \triangleq \text{end}$ .

When there is only one triggering event  $\pi \in \mathsf{PUE}$ vents and one associated local property  $p \in \mathsf{PropL}$ , we have a simple conditional property defined as follow:  $\mathsf{Cnd}(\pi, p) \triangleq \mathsf{Case}(\{(\pi, p)\})$ .

Fig. 5. A trace satisfying a persistent conditional property  $PCnd_m(\pi, p)$ .

Conditional properties  $Cnd(\pi, p)$  define a cause-effect relation in which the triggering event  $\pi$  is searched in the current scan cycle; one may think of a more general property  $PCnd_m(\pi, p)$ , in which the cause-effect relation persists for m > 0 consecutive scan cycles, i.e., the search for the triggering event  $\pi$  continues for at most m consecutive scan cycles. Of course, the triggered local property p may span over a finite number of scan cycles (see Figure 5). Formally, we write  $PCnd_m(\pi, p)$ , for  $\pi \in PUEvents$ ,  $p \in \mathbb{P}rop\mathbb{L}$  and m > 0, for the property  $q_{maxa}^m$  defined as follows:

- $\begin{array}{l} \bullet \ q_k^h \triangleq \operatorname{end}.q_{\max a}^{h-1} \cup \pi.p \ \cup \ (\mathsf{PEvents}\backslash \{\pi\}).q_{k-1}^h, \ \text{for} \ 1 < h \leq m \ \text{and} \ 0 < k \leq \max a \\ \bullet \ q_0^h \triangleq \operatorname{end}.q_{\max a}^{h-1}, \ \text{for} \ 1 < h \leq m \\ \bullet \ q_k^1 \triangleq \operatorname{end} \cup \pi.p \ \cup \ (\mathsf{PEvents}\backslash \{\pi\}).q_{k-1}^1, \ \text{for} \ 0 < k \leq \max a \\ \end{array}$

Obviously,  $Cnd(\pi, p) = PCnd_1(\pi, p)$ .

Bounded eventually. In this case, an event  $\pi$  must eventually occur within m scan cycles. Formally, for  $\pi \in PUE$ vents and m > 0, we write  $BE_m(\pi)$  to denote the property  $q_{\max}^m$  defined as follows:

- $\bullet \ q_{\underline{k}}^h \triangleq \text{end.} \\ q_{\max a}^{h-1} \cup \pi. \\ \mathsf{PEvents}^{\leq k-1} \cup (\mathsf{PEvents} \setminus \{\pi\}). \\ q_{k-1}^h, \text{ for } 1 < h \leq m \text{ and } 0 < k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq \max a_k + 1 \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\ q_{\max a_k} + 1 \leq m \text{ and } 0 \leq k \leq m \\$

- $q_0^h \triangleq \operatorname{end}.q_{\max}^{h-1}$ , for  $1 < h \le m$   $q_k^1 \triangleq \pi.\operatorname{PEvents}^{\le k-1} \cup (\operatorname{PEvents} \setminus \{\pi\}).q_{k-1}^1$ , for  $0 < k \le \max$

Bounded persistency. While in BE<sub>m</sub>( $\pi$ ) the event  $\pi$  must eventually occur within m scan cycles, bounded persistency prescribes that an event  $\pi$  must occur in all subsequent m scan cycles. Formally, for  $\pi \in PUE$ vents and m > 0, we write  $BP_m(\pi)$  to denote the property  $q_{\max}^m$  defined as follows:

- $q_k^h \triangleq \pi.\mathsf{PEvents}^{\leq k-1}; q_{\mathsf{maxa}}^{h-1} \cup (\mathsf{PEvents} \setminus \{\pi\}).q_{k-1}^h$ , for  $1 < h \leq m$  and  $0 < k \leq \max$   $q_0^h \triangleq \pi.\mathsf{end}.q_{\mathsf{maxa}}^{h-1}$ , for  $1 < h \leq m$   $q_1^1 \triangleq \pi.\mathsf{PEvents}^{\leq k-1} \cup (\mathsf{PEvents} \setminus \{\pi\}).q_{k-1}^1$ , for  $0 < k \leq \max$

Bounded absence. The negative counterpart of bounded persistency is bounded absence. This property says that an event  $\pi$  must not appear in all subsequent m scan cycles. Formally, for  $\pi \in$ PUEvents and m > 0, we write BA<sub>m</sub>( $\pi$ ) to denote the property  $q_m$  defined as follows:

- $q_h \triangleq (\mathsf{PEvents} \setminus \{\pi\})^{\leq \mathsf{maxa}}; q_{h-1}, \text{ for } 0 < h \leq m$

- $q_0 \triangleq \epsilon$ .

5.1.2 Compound conditional properties. The properties above can be combined together to express more detailed PLC behaviours. Let us see a few examples with the help of the use case of Section 4.

Conditional bounded eventually. According to this property, if a triggering event  $\pi_1$  occurs then a second event  $\pi_2$  must eventually occur between the *m*-th and the *n*-th scan cycle, with  $1 \le m \le n$ . Formally, for  $\pi_1, \pi_2 \in PUE$ vents and  $1 \le m \le n$ , we define  $CBE_{[m,n]}(\pi_1, \pi_2)$  as follows:

$$CBE_{[m,n]}(\pi_1,\pi_2) \triangleq Cnd(\pi_1, (PEvents^{\leq maxa})^{m-1}; BE_{n-m+1}(\pi_2)).$$

Intuitively, if the event  $\pi_1$  occurs then the event  $\pi_2$  must eventually occur between the scan cycles m and n. In case we would wish that  $\pi_2$  should not occur before the m-th scan cycle, then the property would become:  $Cnd(\pi_1, BA_{m-1}(\pi_2); BE_{n-m+1}(\pi_2))$ .

As an example, we might enforce a conditional bounded eventually property in  $PLC_1$  of our use case in Section 4 to prevent water overflow in the tank  $T_2$  due to a misuse of the valve connecting the tanks  $T_1$  and  $T_2$ . Assume that  $z \in \mathbb{N}$  is the time (expressed in scan cycles) required to overflow the tank  $T_2$  when the valve is open and the level of tank  $T_2$  is low. We might consider to enforce a property of the form  $CBE_{[1,w]}(\text{open\_req}, \overline{\text{close}})$ , with w << z, saying that if  $PLC_1$  receives a request to open the valve, then the valve will be eventually closed within at most w scan cycles (including the current one). This will ensure that if a water request coming from  $PLC_2$  is received by  $PLC_1$  then the valve controlling the flaw from  $T_1$  to  $T_2$  will remain open for at most w scan cycles, with w << z, preventing the overflow of  $T_2$ .

Conditional bounded persistency. Another possibility is to combine conditional with bounded persistency to prescribe that if a triggering event  $\pi_1$  occurs then the event  $\pi_2$  must occur in the m-th scan cycle and in all subsequent n-m scan cycles, for  $1 \le m \le n$ . Formally, for  $\pi_1, \pi_2 \in \mathsf{PUE}$  vents and  $1 \le m \le n$ , we write  $\mathsf{CBP}_{[m,n]}(\pi_1, \pi_2)$  to denote the property defined as:

$$CBP_{[m,n]}(\pi_1,\pi_2) \triangleq Cnd(\pi_1, (PEvents^{\leq maxa})^{m-1}; BP_{n-m+1}(\pi_2)).$$

As an example, we might enforce a conditional bounded persistency property in PLC<sub>3</sub> of our use case in Section 4 to prevent damages of  $pump_3$  due to lack of water in tank  $T_3$ . Assume that  $z \in \mathbb{N}$  is the minimum time (in terms of scan cycles) required to fill  $T_3$ , *i.e.*, to pass from level  $I_3$  to level  $I_3$ , when  $pump_3$  is off. We might consider to enforce a property of the form  $CBP_{[I,z]}(I_3, \overline{off_3})$ , to prescribe that if the tank reaches its low level (event  $I_3$ ) then  $pump_3$  must remain off (event  $\overline{off_3}$ ) for  $I_3$  consecutive scan cycles. This will ensure enough water in tank  $I_3$  to prevent damages on  $I_3$ .

Notice that all previous properties have a single triggering event  $\pi_1$ ; in order to deal with multiple triggering events it is enough to replace the conditional operator with the case construct.

Conditional bounded absence (also called Absence timed [24]). Finally, we might consider to combine conditional with bounded absence to formalise a property saying that if a triggering event  $\pi_1$  occurs then another event  $\pi_2$  must not occur in the m-th scan cycle and in all subsequent n-m scan cycles, with  $1 \le m \le n$ . Formally, for  $\pi_1, \pi_2 \in PUE$ vents and  $1 \le m \le n$ , we write  $CBA_{\lceil m,n \rceil}(\pi_1,\pi_2)$  to denote the property defined as follows:

$$CBA_{\lceil m,n \rceil}(\pi_1,\pi_2) \triangleq Cnd(\pi_1, (\mathsf{PEvents}^{\leq \mathsf{maxa}})^{m-1}; BA_{n-m+1}(\pi_2)).$$

Intuitively, if the triggering event  $\pi_1$  occurs then the event  $\pi_2$  must not occur in the time interval between the m-th and the n-th scan cycle.

As an example, we might enforce a conditional bounded absence property in  $PLC_2$  of our use case in Section 4 to prevent water overflow in the tank  $T_2$  due to a misuse of the valve connecting the tanks  $T_1$  and  $T_2$ . Assume that  $z \in \mathbb{N}$  is the time (expressed in scan cycles) required to empty the tank  $T_2$  when the valve is closed and the tank  $T_2$  reaches its high level  $h_2$ . Then, we might consider to enforce a property of the form  $CBA_{[1,w]}(h_2,\overline{open\_req})$ , for w < z, to prescribe that if the tank reaches its high level (event  $h_2$ ) then  $PLC_2$  may not send a requests to open the valve (event  $\overline{open\_req}$ ) for the subsequent w scan cycles. This ensures us that when  $T_2$  reaches its high level then it will not ask for incoming water for at least w scan cycles, so preventing tank overflow.

5.1.3 Compound persistent conditional properties. Now, we formalise in our language of regular properties a number of correctness properties used by Frehse et al. for the verification of hybrid systems [24]. More precisely, we formalise bounded versions of their properties.

Fig. 6. A trace satisfying a minimum duration property  $MinD(\pi_1, \pi_2, m, n)$ , for m = n = 3.

Bounded minimum duration. When a triggering event  $\pi_1$  occurs, if a second event  $\pi_2$  occurs within m scan cycles then this event must appear in at least all subsequent n scan cycles (see Figure 6). Formally, we can express this property as follows:

$$MinD(\pi_1, \pi_2, m, n) \triangleq Cnd(\pi_1, PCnd_m(\pi_2, BP_n(\pi_2))).$$

Note that the property MinD( $\pi_1$ ,  $\pi_2$ , m, n) is satisfied each time CBP[m,m+n]( $\pi_1$ ,  $\pi_2$ ) is. The vice versa does not hold as in  $CBP_{[m,m+n]}(\pi_1,\pi_2)$  the event  $\pi_2$  is required to occur in the whole time interval [m, m+n], while, according to MinD $(\pi_1, \pi_2, m, n)$ , the event  $\pi_2$  might not occur at all.

Bounded maximum duration. When an event  $\pi_1$  occurs, if a second event  $\pi_2$  occurs within m scan cycles then the same event  $\pi_2$  may occur in at most all subsequent n scan cycles. Formally, we can represent this property as follows:

$$\operatorname{MaxD}(\pi_1, \pi_2, m, n) \triangleq \operatorname{Cnd}(\pi_1, \operatorname{PCnd}_m(\pi_2, (\operatorname{PEvents}^{\leq \max})^n; \operatorname{BA}_1(\pi_2))).$$

The property  $MaxD(\pi_1, \pi_2, m, n)$  is satisfied each time the property  $CBP_{[m,m+n]}(\pi_1, \pi_2)$ ;  $BA_I(\pi_2)$  is. Again, the vice versa does not hold.

Bounded response. When an event  $\pi_1$  occurs, if a second event  $\pi_2$  occurs within m scan cycles then a third event  $\pi_3$  appears within n scan cycles. Formally, we can express this property as follows:

$$BR(\pi_1, \pi_2, \pi_3, m, n) \triangleq Cnd(\pi_1, PCnd_m(\pi_2, BE_n(\pi_3))).$$

Bounded invariance. Whenever an event  $\pi_1$  occurs, if  $\pi_2$  occurs within m scan cycles then  $\pi_3$  will persistently occur for at least n scan cycles. Formally, we can express this property as follows:

$$BI(\pi_1, \pi_2, \pi_3, m, n) \triangleq Cnd(\pi_1, PCnd_m(\pi_2, BP_n(\pi_3))).$$

- Bounded mutual exclusion. A different class of properties prescribes the possible occurrence of events  $\pi_i \in P$ Events, for  $i \in I$ , in mutual exclusion within m consecutive scan cycles. Formally, for  $\pi_i \in PUE$ vents,  $i \in I$  and  $m \ge 1$ , we write  $BME_m(\bigcup_{i \in I} \{\pi_i\})$ , for the property  $q_{\max}^m$  defined as:

- $\bullet \ q_k^h \triangleq \text{end.} q_{\max}^{h-1} \ \cup \ \bigcup_{i \in I} \pi_i. (\bigcap_{j \in I \setminus \{i\}} \text{BA}_h(\pi_j)) \ \cup \ (\mathsf{PEvents} \setminus \bigcup_{i \in I} \{\pi_i\}). q_{k-1}^h, \text{for } 1 < h \leq m \text{ and } 1 <$  $0 < k \le \max$

- $q_0^h \triangleq \operatorname{end}.q_{\max}^{h-1}$ , for  $1 < h \le m$   $q_k^1 \triangleq \operatorname{end} \cup \bigcup_{i \in I} \pi_i.(\bigcap_{j \in I \setminus \{i\}} \operatorname{BA}_I(\pi_j)) \cup (\operatorname{PEvents} \setminus \bigcup_{i \in I} \{\pi_i\}).q_{k-1}^1$ , for  $0 < k \le \max$

- $q_0^1 \triangleq \epsilon$ .

As an example, we might enforce a bounded mutual exclusion property in the PLC<sub>1</sub> of our use case of Section 4 to prevent chattering of the valve, i.e., rapid opening and closing which may cause mechanical failures on the long run. In particular, we might consider to enforce a property of the form BME<sub>3</sub>({\overline{\text{open}}, \overline{\text{close}}}) saying that within 3 consecutive scan cycles the opening and the closing of the valve (events open and close, respectively) may only occur in mutual exclusion.

In Table 4, we summarise all local properties represented and discussed in this section.

| Case:                            | if $\pi_i$ occurs then $p_i$ should be satisfied, for $i \in I$                          |

|----------------------------------|------------------------------------------------------------------------------------------|

|                                  |                                                                                          |

| Persistent conditional:          | for $m$ scan cycles, if $\pi$ occurs then $p$ should be satisfied                        |

| Bounded eventually:              | event $\pi$ must eventually occur within $m$ scan cycles                                 |

| Bounded persistency:             | event $\pi$ must occur in all subsequent $m$ scan cycles                                 |

| Bounded absence:                 | even $\pi$ must not occur in all subsequent $m$ scan cycles                              |

| Conditional bounded eventually:  | if $\pi_1$ occurs then $\pi_2$ must eventually occur in the scan cycles $[m, n]$         |

| Conditional bounded persistency: | if $\pi_1$ occurs then $\pi_2$ must occur in all scan cycles of $[m, n]$                 |

| Conditional bounded absence:     | if $\pi_1$ occurs then $\pi_2$ must not occur in all scan cycles of $[m, n]$             |

| (Bounded) Minimum duration:      | when $\pi_1$ , if $\pi_2$ in $[1, m]$ then $\pi_2$ persists for at least $n$ scan cycles |

| (Bounded) Maximum duration:      | when $\pi_1$ , if $\pi_2$ in $[1, m]$ then $\pi_2$ persists for at most $n$ scan cycles  |

| Bounded response:                | when $\pi_1$ , if $\pi_2$ in $[1, m]$ them $\pi_3$ appears within $n$ scan cycles        |

| Bounded invariance:              | when $\pi_1$ , if $\pi_2$ in $[1, m]$ then $\pi_3$ persists for at least $n$ scan cycles |

| Bounded mutual exclusion         | events $\pi_i$ may only occur in mutual exclusion within $n$ scan cycles                 |

Table 4. Overview of local properties.

Fig. 7. A trace satisfying the just mentioned property for some m, n = m + 4 and d = 4.

#### 5.2 Global properties

As expected, the previously described local properties become global ones by applying the Kleeneoperator \*. Once in this form, we can put these properties in conjunction between them. Here, we show two global properties, the first one is built top of conditional bounded persistency properties and the second one is built on top of a conditional bounded eventually property.

As a first example, we might consider a global property saying that whenever an event  $\pi$  occurs then all events  $\pi_i$ , for  $i \in I$ , must occur in the m-th scan cycle and in all subsequent n-m scan cycles, for  $1 \le m \le n$ . Formally, for  $\pi$ ,  $\pi_i \in \mathsf{PUEvents}$ ,  $i \in I$ , and  $1 \le m \le n$ :  $\bigcap_{i \in I} (\mathsf{CBP}_{[m,n]}(\pi,\pi_i))^*$ .

We might enforce this kind of property in PLC<sub>1</sub> of our use case of Section 4. Assume  $z \in \mathbb{N}$  being the time (expressed in scan cycles) required to overflow the tank  $T_1$  when the level of the tank  $T_1$  is low and both pumps are on and the valve is closed. Then, the property would be  $(CBP_{[I,w]}(I_I,\overline{on_1}))^* \cap (CBP_{[I,w]}(I_I,\overline{on_2}))^*$ , with w < z, saying that if the tank  $T_1$  reaches its low level (event  $I_1$ ) then both  $pump_1$  and  $pump_2$  must be on (events  $\overline{on_1}$  and  $\overline{on_2}$ ) in all subsequent w scan cycles, starting from the current one.

As a second example, we might consider a more involved global property relying on conditional bounded eventually, persistent conditional, and bounded persistency. Basically, the property says that whenever an event  $\pi_1$  occurs then a second event  $\pi_2$  must eventually occur between the m-th scan cycle and the n-th scan cycle, with  $1 \le m \le n$ ; moreover, it must occur for d consecutive scan cycles, for  $1 \le d$  (see Figure 7). Formally, the property is the following:

$$\left(\mathrm{CBE}_{[m,n]}(\pi_1,\pi_2)\right)^* \cap \left(\mathrm{Cnd}(\pi_1,\mathrm{PCnd}_n(\pi_2,\mathrm{PEvents}^{\leq \max};\mathrm{BP}_{d-1}(\pi_2)))\right)^*$$

for  $\pi_1, \pi_2 \in \mathsf{PUE}$ vents, with  $1 \le m \le n$  and  $d \ge 1$ . Intuitively, the property  $(\mathsf{CBE}_{[m,n]}(\pi_1, \pi_2))^*$  requires that when  $\pi_1$  occurs the event  $\pi_2$  must eventually occur between the m-th scan cycle and the n-th scan cycle. The remaining part of the property says if the event  $\pi_2$  occurs within the n-th scan cycle (recall that  $m \le n$ ) then it must persist for d scan cycles.

In this manner, we might strengthen the conditional bounded eventually property given in Section 5.1 for PLC<sub>1</sub> of our use case to prevent water overflow in the tank  $T_2$ . Let  $z \in \mathbb{N}$  be the time (expressed in scan cycles) required to overflow the tank  $T_2$  when the valve is open and the level of tank  $T_2$  is low. The property is the following:

$$(CBE_{[1,w]}(open\_req, \overline{close}))^* \cap (Cnd(open\_req, PCnd_w(\overline{close}, PEvents^{\leq maxa}; BP_{d-1}(\overline{close}))))^*$$

where w << z, and  $d \in \mathbb{N}$  is the time (expressed in scan cycles) required to release in  $T_3$  the (maximum) quantity of water that the tank  $T_2$  may accumulate in w scan cycles. The first part of the property says that if  $PLC_1$  receives a request to open the valve (event open\_req) then the valve must be eventually closed (event  $\overline{close}$  must eventually occur) within at most w scan cycles. The remaining part of the property says that when  $PLC_1$  receives a request to open the valve (event open\_req), if the valve gets closed (event  $\overline{close}$ ) within the w-th scan cycle, then it must remain closed for the d consecutive scan cycles. Here, d depends both on the maximum level of water reachable in  $T_2$  in w scan cycles and on the physical law governing the water flow from  $T_2$  to  $T_3$ .

#### 6 MONITOR SYNTHESIS

In this section, we provide an algorithm to synthesise monitors from regular properties whose events are contained in (the set of events associated to) a fixed set  $\mathcal{P}$  of observable controller actions. More precisely, given a global property  $e \in \mathbb{Prop}\mathbb{G}$  the algorithm returns an edit automaton  $\{e\}^{\mathcal{P}} \in \mathbb{E} \text{dif}$  that is capable to enforce the property e during the execution of a generic controller whose possible actions are confined to those in  $\mathcal{P}$ . The synthesis algorithm is defined in Table 5 by induction on the structure of the global/local property given in input; as we distinguish global properties from local ones, we define our algorithm in two steps.

Remark 3. We recall that, according to the operational semantics defined in Table 1, all controller actions  $\alpha$  are observable and they basically coincide with the set Events used to build up the enforcing properties defined in Section 5. As a consequence, we will synthesise enforcing monitors that may observe any action of the controller under scrutiny and may act consequently.

The monitor  $\langle p^* \rangle^{\mathcal{P}}$  associated to a global property  $p^*$  is an edit automaton defined via the recursive equation  $X = \langle p \rangle_X^{\mathcal{P}}$ , to recursively enforce the local property p. The monitor  $\langle e_1 \cap e_2 \rangle^{\mathcal{P}}$  is given by the *cross product* between the edit automata  $\langle e_1 \rangle^{\mathcal{P}}$  and  $\langle e_2 \rangle^{\mathcal{P}}$ , to accept only traces that satisfy both  $e_1$  and  $e_2$ ; the definition of the cross product between two edit automata recalls that for finite state automata, and it is reported in the appendix in Table 6. The monitor  $\langle p_1 \cap p_2 \rangle_X^{\mathcal{P}}$  is given by the cross product between the edit automata  $\langle p_1 \rangle_X^{\mathcal{P}}$  and  $\langle p_2 \rangle_X^{\mathcal{P}}$ . The monitor  $\langle p_1 \cap p_2 \rangle_X^{\mathcal{P}}$  is given by the automaton  $\langle p_1 \rangle_Z^{\mathcal{P}}$ , where  $Z = \langle p_2 \rangle_X^{\mathcal{P}}$ ; basically Z ties the final states of the automaton enforcing  $p_1$  with the initial state of the automaton enforcing  $p_2$  (e.g.,  $\langle e; p_2 \rangle_X^{\mathcal{P}} = \langle e \rangle_Z^{\mathcal{P}} = Z$ , for  $Z = \langle p_2 \rangle_X^{\mathcal{P}}$ ). The monitor associated to a union property  $\cup_{i \in I} \pi_i.p_i$  does the following: (i) *allows* all actions associated to the events  $\pi_i$ , (ii) *inserts* an action associated to some admissible event  $\pi_i$  only when the controller wishes to prematurely complete the scan cycle, i.e., it emits an end-action, and (iii) *suppresses* any other action except for tick- and end-actions.

Thus, the *mitigation* of the enforcement is actually implemented in the monitors synthesised from union properties. In practise, when the controller under scrutiny complies with the property enforced by the monitor, the two components, monitor and controller, evolve in a tethered fashion (by applying rule (Allow)), moving through related correct states. However, if the controller gets somehow corrupted (for instance, due to the presence of a malware) then the two components will get misaligned reaching unrelated states. In this case, the enforcer mitigates the attack by suppressing the remaining actions emitted by the controller (by applying rule (Suppress)) until the

```

\langle \mid p^* \mid \rangle^{\mathcal{P}} \quad \triangleq \quad \mathsf{X}, \text{ for } \mathsf{X} = \langle \mid p \mid \rangle_{\mathsf{X}}^{\mathcal{P}}

\langle \mid e_1 \cap e_2 \mid \rangle^{\mathcal{P}} \quad \triangleq \quad \mathsf{Prod}_{\mathsf{X}}^{\mathcal{P}}(\langle \mid e_1 \mid \rangle^{\mathcal{P}}, \langle \mid e_2 \mid \rangle^{\mathcal{P}}), \; \mathsf{X} \text{ fresh}

\langle \mid \epsilon \mid \rangle_{\mathsf{X}}^{\mathcal{P}} \quad \triangleq \quad \mathsf{X}

\langle \mid p_1 \cap p_2 \mid \rangle_{\mathsf{X}}^{\mathcal{P}} \quad \triangleq \quad \mathsf{Prod}_{\mathsf{X}}^{\mathcal{P}}(\langle \mid p_1 \mid \rangle_{\mathsf{X}}^{\mathcal{P}}, \langle \mid p_2 \mid \rangle_{\mathsf{X}}^{\mathcal{P}})

\langle \mid p_1 : p_2 \mid \rangle_{\mathsf{X}}^{\mathcal{P}} \quad \triangleq \quad \langle \mid p_1 \mid \rangle_{\mathsf{X}}^{\mathcal{P}}, \; \mathsf{for } \mathsf{Z} = \langle \mid p_2 \mid \rangle_{\mathsf{X}}^{\mathcal{P}}, \; \mathsf{Z} \text{ fresh}

\langle \mid \bigcup_{i \in I} \pi_i . p_i \mid \rangle_{\mathsf{X}}^{\mathcal{P}} \quad \triangleq \quad \mathsf{Z}, \; \mathsf{for}

\mathsf{Z} = \begin{cases} \sum_{i \in I} \pi_i . \langle \mid p_i \mid \rangle_{\mathsf{X}}^{\mathcal{P}} + \sum_{i \in I} \pi_i < \mathsf{end.} \langle \mid p_i \mid \rangle_{\mathsf{X}}^{\mathcal{P}} + \sum_{\alpha \in Q} -\alpha . \mathsf{Z}, \; \mathsf{if } \mathsf{end} \notin \cup_{i \in I} \pi_i \\ \sum_{i \in I} \pi_i . \langle \mid p_i \mid \rangle_{\mathsf{X}}^{\mathcal{P}} + \sum_{\alpha \in Q} -\alpha . \mathsf{Z}, \; \mathsf{otherwise} \end{cases}

\mathsf{where } \mathcal{Q} = \mathcal{P} \setminus (\cup_{i \in I} \pi_i \cup \{\mathsf{tick,end}\})

```

Table 5. Monitor synthesis from properties in PropG and PropL.

controller reaches the end of the scan cycle, signalled by the emission of the end-action<sup>1</sup>. After that, if monitor and controller are not aligned the monitor will command the insertion of a safe trace, without any involvement of the controller, via one or more applications of the rule (Insert). Safe traces inserted in full autonomy by our enforcers always terminate with an end. Thus, when both the controller and the monitor will be aligned, at the end of the scan cycle, they will synchronise on the action end, via an application of the rule (Allow), and from then on they may continue in a tethered fashion.

Remark 4. Note that even whe the controller is completely unreliable and the monitor inserts an entire safe trace, the assumption made in Remark 1 ensures us that the enforced scan cycle always ends well before a violation of the maximum cycle limit.

Now, we calculate the complexity of the synthesis algorithm based on the number of occurrences of the operator  $\cap$  in e and the dimension of e,  $\dim(e)$ , i.e, the number of all operators occurring in e. Intuitively, the size of a property is given by the number of operators occurring in it.

Definition 6. Let  $\dim(): \mathbb{P}rop\mathbb{G} \cup \mathbb{P}rop\mathbb{L} \to \mathbb{N}$  be a property-size function defined as:

```

\begin{array}{llll} \dim(p^*) & \triangleq & \dim(p)+1 & \dim(e_1\cap e_2) & \triangleq & \dim(e_1)+\dim(e_2)+1 \\ \dim(\epsilon) & \triangleq & 1 & \dim(p_1;p_2) & \triangleq & \dim(p_1)+\dim(p_2)+1 \\ \dim(p_1\cap p_2) & \triangleq & \dim(p_1)+\dim(p_2)+1 & \dim(\bigcup_{i\in I}\alpha_i.p_i) & \triangleq & \mid I\mid +\sum_{i\in I}\dim(p_i). \end{array}

```

PROPOSITION 1 (COMPLEXITY). Let  $e \in \mathbb{Prop}\mathbb{G}$  be a global property and  $\mathcal{P}$  be a set of actions such that  $events(e) \subseteq \mathcal{P}$ . The complexity of the algorithm to synthesise  $\{|e|\}^{\mathcal{P}}$  is  $O(|\mathcal{P}| \cdot m^{k+1})$ , with  $m = \dim(e)$  and k being the number of occurrences of the operator  $\cap$  in e.

In the following, we prove that the enforcement induced by our synthesised monitors enjoys the properties stated in the Introduction: *determinism preservation*, *transparency*, *soundness*, *deadlock-freedom*, *divergence-freedom*, and *scalability*. In this section, with a small abuse of notation, given a set of observable actions  $\mathcal{P}$ , we will use  $\mathcal{P}$  to denote also the set of the corresponding events.

Given a deterministic global property e, our synthesis algorithm returns a deterministic enforcer (according to Definition 2), i.e., an enforcer that can be effectively implemented. Formally,

Proposition 2 (Deterministic preservation). Given a deterministic global property  $e \in \mathbb{P}ropG$  over a set of events  $\mathcal{P}$ . The edit automaton  $\{e\}^{\mathcal{P}}$  is deterministic.

As said in Section2, a malware that aims to take control of the plant has no interest in delaying the scan cycle and risking the violation of the maximum cycle limit whose consequence would be the immediate shutdown of the controller [59].

Let us move to *transparency*. Intuitively, the enforcement induced by a deterministic property  $e \in \mathbb{P} rop \mathbb{G}$  should preserve any execution trace satisfying e itself (Definition 2 at pag. 5 of [40]).

THEOREM 1 (TRANSPARENCY). Let  $e \in \mathbb{P} \mathbb{r} \oplus \mathbb{P} \mathbb{G}$  be a deterministic global property,  $\mathcal{P}$  be a set of observable actions such that events  $(e) \subseteq \mathcal{P}$ , and  $P \in \mathbb{C} \mathbb{t} \mathbb{r} \mathbb{I}$  be a controller. Let  $t = \alpha_1 \cdots \alpha_n$  be a trace of the controller P with  $t \in [e]$ . Then, (1) t is a trace of the edit automaton  $(e)^{\mathcal{P}}$ , and (2) there is no trace  $t' = \alpha_1 \cdots \alpha_k \cdot \lambda$  for  $(e)^{\mathcal{P}}$  such that  $0 \le k < n$  and  $\lambda \in (-\alpha_{k+1}, \alpha < \alpha_{k+1})$ , for some  $\alpha$ .

Basically, conclusion (1) says that all execution trace t (of a controller P) satisfying the enforcing property e are *allowed* by the associated enforcer  $\{e\}^{\mathcal{P}}$ , while conclusion (2) says that allowing the trace t is the only possible option in the enforcement (this follows by the determinism of e).

Another important property of our enforcement is *soundness* [40]. Intuitively, a controller under the scrutiny of a monitor  $\langle e \rangle^{\mathcal{P}}$  should only yield execution traces which satisfy the enforced property e, *i.e.*, execution traces which are consistent with its semantics [e] (up to  $\tau$ -actions).

THEOREM 2 (SOUNDNESS). Let  $e \in \mathbb{P}_{\mathbb{T}\mathbb{O}\mathbb{D}}\mathbb{G}$  be a global property,  $\mathcal{P}$  be a set of observable actions such that  $events(e) \subseteq \mathcal{P}$ , and  $P \in \mathbb{C}tr\mathbb{I}$  be a controller. If t is a trace of the monitored controller  $\{e\}^{\mathcal{P}} \mapsto \{P\}$  then  $\hat{t}$  is a prefix of some trace in [e] (see Notation 1 for the definition of the trace  $\hat{t}$ ).

Here, it is important to stress that in general soundness does not ensure deadlock-freedom of the monitored controller. That is, it may be possible that the enforcement of some property e causes a deadlock of the controller P under scrutiny. In particular, this may happen in our controllers only when the initial sleeping phase does not match the enforcing property (e.g., P = tick.c.end.P and  $e = (c.end)^*$ ). Intuitively, a local property will be called a k-sleeping property if it allows k initial time instants of sleep. Formally,

DEFINITION 7. For  $k \in \mathbb{N}^+$ , we say that  $p \in \mathbb{P} \mathbb{T} \oplus \mathbb{D} \mathbb{L}$  is a k-sleeping local property, only if  $\llbracket p \rrbracket = \{t \mid t = t_1 \cdot ... \cdot t_n, \text{ for } n > 0, \text{ s.t. } t_i = \operatorname{tick}^k \cdot t_i' \cdot \operatorname{end}, \operatorname{end} \notin t_i', \text{ and } 1 \leq i \leq n\}$ . We say that  $p^*$  is a k-sleeping global property only if p is, and  $e = e_1 \cap e_2$  is k-sleeping only if both  $e_1, e_2$  are k-sleeping.

The enforcement of k-sleeping properties does not introduce deadlocks in k-sleeping controllers. This is because our synthesised monitors suppress all incorrect actions of the controller under scrutiny, driving it to the end of its scan cycle. Then, the controller remains in stand-by while the monitor yields a safe sequence of actions to mimic a safe completion of the current scan cycle.

Theorem 3 (Deadlock-freedom). Let  $e \in \mathbb{P}ropG$  be a k-sleeping global property, and P be a set of observable actions such that events  $(e) \subseteq P$ . Let  $P \in \mathbb{C}tr\mathbb{I}$  be a controller of the form  $P = tick^k.S$  whose set of observable actions is contained in P. Then,  $\langle e \rangle^P \bowtie \{P\}$  does not deadlock.

Another important property of our enforcement mechanism is *divergence-freedom*. In practice, the enforcement does not introduce divergence: monitored controllers will always be able to complete their scan cycles by executing a finite number of actions. This is because we limit our enforcement to well-formed properties (Definition 4) which always terminates with an  $_{\text{end}}$  event. In particular, the well-formedness of local properties ensures us that in a global property of the form  $p^*$  the number of events within two subsequent  $_{\text{end}}$  events is always finite.

Theorem 4 (Divergence-freedom). Let  $e \in \mathbb{Prop}\mathbb{G}$  be a global property,  $\mathcal{P}$  be a set of observable actions such that events  $(e) \subseteq \mathcal{P}$ , and  $P \in \mathbb{Ctrl}$  be a controller. Then, there exists a  $k \in \mathbb{N}^+$  such that whenever  $(e)^{\mathcal{P}} \bowtie \{P\} \xrightarrow{t} \mathsf{E} \bowtie \{J\}$ , if  $\mathsf{E} \bowtie \{J\} \xrightarrow{t'} \mathsf{E}' \bowtie \{J'\}$ , with  $|t'| \geq k$ , then  $\mathsf{end} \in t'$ .

Notice that all properties seen up to now scale to *field communications networks* of controllers. This means that they are preserved when the controller under scrutiny is running in parallel with other controllers in the same field communications network. As an example, by an application

Fig. 8. Some physical components of our implementation.

of Theorems 1 and 2, we show how both transparency and soundness scale to field networks. A similar result applies to the remaining properties.

COROLLARY 1 (SCALABILITY TO NETWORKS OF PLCs). Let  $e \in \mathbb{P}_{\mathbb{T}\mathbb{O}\mathbb{D}}\mathbb{G}$  be a global property and  $\mathcal{P}$  be a set of observable actions, such that events  $(e) \subseteq \mathcal{P}$ . Let  $P \in \mathbb{C}\mathfrak{tr}\mathbb{I}$  be a controller and  $N \in \mathbb{F}\mathbb{N}$  be a field network. If  $(\langle e \rangle^{\mathcal{P}} \bowtie \{P\}) \parallel N \xrightarrow{t} (\mathsf{E} \bowtie \{J\}) \parallel N'$ , for some t, E, J and N', then

- whenever  $P \xrightarrow{t'} J$ , with  $t' = \alpha_1 \cdots \alpha_n \in [e]$ , the trace t' is a trace of  $\langle e \rangle^{\mathcal{P}}$  and there is no trace  $t'' = \alpha_1 \cdots \alpha_k \cdot \lambda$  of  $\langle e \rangle^{\mathcal{P}}$  such that  $0 \leq k < n$  and  $\lambda \in \{-\alpha_{k+1}, \alpha < \alpha_{k+1}\}$ , for some  $\alpha$ ;

- whenever  $\langle e \rangle^{\mathcal{P}} \bowtie \{P\} \xrightarrow{t'} \mathsf{E} \bowtie \{J\}$  the trace  $\widehat{t'}$  is a prefix of some trace in  $[\![e]\!]$ .

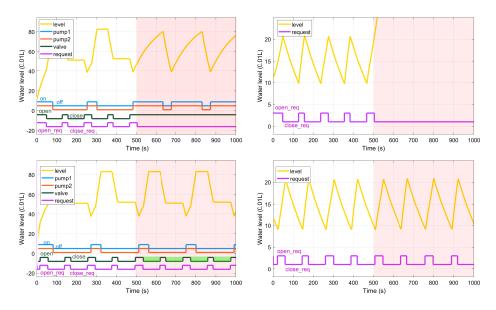

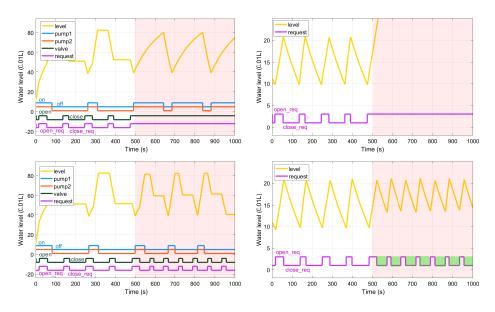

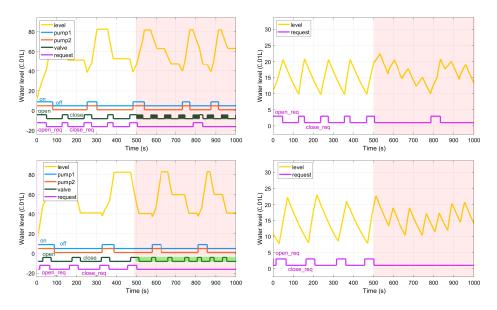

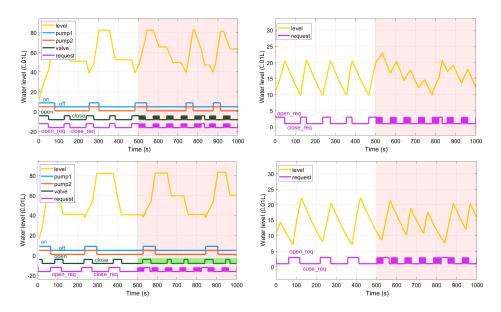

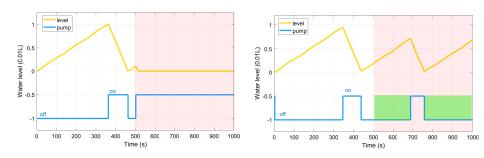

# 7 OUR ENFORCEMENT MECHANISM AT WORK

In this section, we propose an implementation of our enforcement mechanism in which monitors, running on *field-programmable gate arrays* (FPGAs) [61], enforce *open source PLCs* [8], running on Raspberry Pi devices [25], and governing a physical plant simulated in *Simulink* [44]. The section has the following structure. In Section 7.1, we argue why FPGAs are good candidates for implementing *secure proxies*. In Section 7.2, we describe how we implemented the whole enforcement architecture for the use case of Section 4. In Section 7.3, we test our implementation injecting the enforced PLCs with five different malware aiming at causing three different physical perturbations: tank overflow, valve damage, and pump damage. The attacks have been chosen to cover as much as possible the attacker model of Section 2. In particular, they include: a drop of the actuator commands of the valve, an integrity attack on the water-level sensors, a forgery of the actuator commands of the valve, a forgery of the message requests to open/close the valve, and a forgery of the actuator commands of the pumps. Section 7.4 discusses the performance of our implementation.

## 7.1 FPGAs as secure proxies for ICSs

Field-programmable gate arrays (FPGAs) are semiconductor devices that can be programmed to run specific applications. An FPGA consists of (configurational) logic blocks, routing channels and I/O blocks. The logic blocks can be configured to perform complex combinational functions and are further made up of transistor pairs, logic gates, lookup tables and multiplexers. The applications are written using hardware description languages, such as Verilog [60]. Thus, in order to execute an application on the FPGA, its Verilog code is converted into a sequence of bits, called *bitstream*, that is loaded into the FPGA.

FPGA are assumed to be secure when the adversary does not have physical access to the device, *i.e.*, the bitstream cannot be compromised [32]. Recent FPGAs support remote updates of the bitstream by relying on authentication mechanisms to prevent unauthorised uploads of malicious logic [32].

Fig. 9. An implementation in Simulink of the plant of the SWaT system.