# ETICA: Efficient Two-Level I/O Caching Architecture for Virtualized Platforms

Saba Ahmadian, Reza Salkhordeh, Onur Mutlu, Hossein Asadi

**Abstract**—In recent years, increased I/O demand of *Virtual Machines* (VMs) in large-scale data centers and cloud computing has encouraged system architects to design high-performance storage systems. One common approach to improving performance is to employ fast storage devices such as *Solid-State Drives* (SSDs) as an I/O caching layer for slower storage devices. SSDs provide high performance, especially on random requests, but they also have limited endurance: they support *only* a limited number of write operations and can therefore *wear out* relatively fast due to write operations. In addition to the write requests generated by the applications, each read miss in the SSD cache is served at the cost of imposing a write operation to the SSD (to copy the data block into the cache), resulting in an even larger number of writes into the SSD. Previous I/O caching schemes on virtualized platforms *only* partially mitigate the endurance limitations of SSD-based I/O caches; they mainly focus on assigning efficient cache write policies and cache space to the VMs. Moreover, existing cache space allocation schemes have inefficiencies: they *do not* take into account the impact of cache write policy in reuse distance calculation of the running workloads and hence, reserve cache blocks for accesses that would *not* be served by cache.

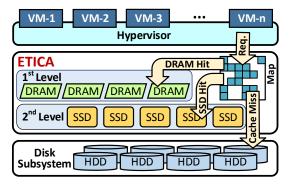

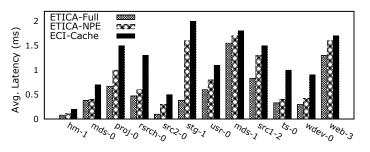

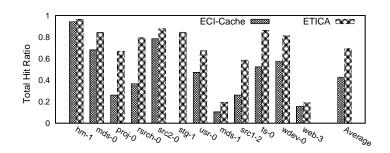

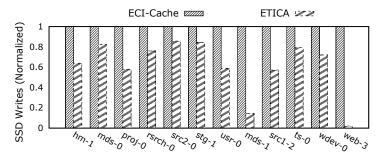

In this paper, we propose an *Efficient Two-Level I/O Caching Architecture* (ETICA) for virtualized platforms that can significantly improve I/O latency, endurance, and cost (in terms of cache size) while preserving the reliability of write-pending data blocks. As opposed to previous *one-level I/O* caching schemes in virtualized platforms, our proposed architecture 1) provides *two* levels of cache by employing both *Dynamic Random-Access Memory* (DRAM) and SSD in the I/O caching layer of virtualized platforms and 2) effectively partitions the cache space between running VMs to achieve maximum performance and minimum cache size. To manage the two-level cache, unlike the previous reuse distance calculation schemes such as *Useful Reuse Distance* (URD), which only consider the request type and neglect the impact of *cache write policy*, we propose a new metric, *Policy Optimized reuse Distance* (POD). The key idea of POD is to effectively calculate the reuse distance and estimate the amount of two-level DRAM+SSD cache space to allocate by considering both 1) the request type and 2) the cache write policy. Doing so results in enhanced performance and reduced cache size due to the allocation of cache blocks only for the requests that would be served by the I/O cache. ETICA maintains the reliability of write-pending data blocks and improves performance by 1) assigning an effective and fixed write policy at each level of the I/O cache hierarchy and 2) employing effective promotion and evicition methods between cache levels. Our extensive experiments conducted with a real implementation of the proposed two-level storage caching architecture show that ETICA provides 45% higher performance, compared to the state-of-the-art caching schemes in virtualized platforms, while improving both cache size and SSD endurance by 51.7% and 33.8%, respectively.

# 1 INTRODUCTION

Virtualized platforms are widely used in large scale data centers to provide significantly improved availability and flexibility. In such platforms, multiple *Virtual Machines* (VMs) provide different services on shared hardware. VM management and resource partitioning between VMs are performed by the hypervisor, which plays a major role in the virtualized platforms and aims to maximize performance and system utilization. The key advantages of virtualized platforms that are continuously evolving in computing industry are: 1) high flexibility due to the ability to run multiple VMs with different *Operating Systems* (OS), 2) high resource utilization, 3) resource isolation between different VMs, and 4) allocation of dynamically adjustable resources to the VMs [1].

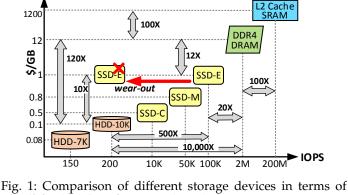

The growing popularity of I/O intensive applications in data centers, such as *Online Transaction Processing* (OLTP), banking, data analysis, and other big data workloads, greatly increases the demand for high-performance storage subsystems. Existing storage systems still mainly consist of high-capacity and low-performance *Hard Disk Drives* (HDDs) with the goal of storing very large amounts of data at low cost. Such storage systems have become the performance bottle-neck in large-scale data centers due to the growing performance gap between HDDs and processing elements in enterprise servers (as depicted by *I/O Operations Per Second* (IOPS) performance in Fig. 1).

To alleviate the performance shortcomings of such HDDbased storage systems, enterprise manufacturers, such as Dell EMC, HP, and NetApp [3], [4], [5], and various research works on emerging storage architectures, such as [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [21], [22], [23], propose *I/O caching* schemes that accelerate the response

Fig. 1: Comparison of different storage devices in terms of cost (\$/GB) and performance (IOPS). SSD-C: Consumer SSD, SSD-M: Midrange SSD, SSD-E: Enterprise SSD, DDR4 DRAM: Double Data Rate 4<sup>th</sup> generation, HDD-7K: HDD with 7K *Revolutions Per Minute* (RPM), HDD-10K: HDD with 10K RPM [2].

time of I/O requests. High-performance storage devices such as *Dynamic Random Access Memories* (DRAMs) and *Solid-State Drives* (SSDs) can be employed in the I/O caching layer to alleviate the low performance of HDDs. As depicted in Fig. 1, DRAM provides the highest performance among many types of storage/memory devices [24] and thus seems to be the best candidate to employ in the I/O caching layer. However, DRAM is expensive, and using *volatile* DRAM as a cache comes with reliability hurdles for write requests. A DRAM-based I/O cache requires additional battery backups to correctly maintain the data buffered in DRAM to survive power outages and system failures. Compared to DRAM, enterprise SSDs have about 12X lower cost and offer 20X less performance but they provide 500X higher performance than HDDs. In contrast to DRAM, SSDs are non-volatile and typically do not suffer from data loss due to power outages, but they support only a limited number of reliable writes [25], [26], [27], [28], [29], [30]. Thus, the main shortcoming of SSDs is their endurance limitation where both performance and reliability are significantly degraded when the number of committed writes exceeds the endurance limit (i.e., when the SSD wears out, as shown in Fig. 1). In addition, frequent replacement of such expensive SSDs imposes significant cost and reliability issues<sup>1</sup> in storage systems. Recent studies, such as [6], [7], [8], [9], [10], [11], [12], [13], [14], [15], [16], [17], [18], [19], [20], [32], propose I/O caching schemes based on SSDs. Among such studies, only few are applicable to virtualized platforms [6], [9], [10], [11], [32]. Such I/O caching schemes aim to either only improve performance without considering the endurance of the SSD [7], [10], [11], [12], [13], [14], [32] or attempt to improve performance with minimum overhead on SSD endurance [6], [8], [9]. In addition, such studies suffer from two main shortcomings: 1) their performance improvement is limited by the high SSD latency (relative to DRAM) and 2) their endurance-preserving techniques lead to performance degradation.

Another approach to improving the performance of storage systems is to use hybrid techniques that take advantage of both DRAM and SSDs in the I/O caching layer. Multiple industrial approaches (e.g., the Dell EMC FAST cache [3] and ZFS L2ARC cache [33], [34], [35], [36]) and academic studies [37], [38], [39], [40], [41], [42], [43], [44], [45], [46], [47], [48], [49], [50], [51], [52], [53] employ two levels of I/O caching using both DRAM and emerging Non-Volatile Memo*ries* (NVMs)/SSDs in their storage architectures. Such caching schemes, however, suffer from several important shortcomings: 1) They cannot provide cache space partitioning across VMs, which results in poor performance and high cost in virtualized platforms. 2) Buffered data in DRAM cache is at risk of loss due to sudden power outage; additional battery backups add significant cost overhead to the caching scheme. 3) The employed mechanisms for detecting hot data blocks are not accurate since they do not consider any workload characteristics, such as reuse distance of the accesses. 4) Past works do not provide write policy management at DRAM or SSD levels and most schemes configure both cache levels to use the Write Back (WB)<sup>2</sup> policy. 5) Such schemes only focus on detecting and promoting *hot* data blocks to the cache while there is no specified method to detect and evict cold data blocks (i.e., least recently accessed data blocks) from cache.

Most recent cache space partitioning schemes in virtualized platforms employ reuse distance analysis to estimate each VM's cache size, but they neglect key parameters such as *request type* and *cache write policy* [6], [11]. The state-of-the-art scheme, ECI-Cache [6], proposes *Useful Reuse Distance* (URD) and considers the *request type* in reuse distance calculation. However, it neglects the impact of *cache write policy* on the reuse distance calculation, and, as a result, it over-estimates the cache sizes for caches with write policies other than WB and *Write Through* (WT). ECI-Cache estimates the cache sizes of the VMs based on the URD metric and assigns a cache write policy on a per-VM basis. As such, it results in improved SSD endurance and performance-per-cost. The URD metric is optimized for caches with WB and WT policies. It *overestimates* the cache size for caches with other write policies (e.g., *Read Only* (RO)). If we use the URD metric in a cache with the RO policy, cache blocks would be allocated for *write* requests that would not be buffered in the RO cache, and thus the allocated blocks remain *unused*.

In this paper, we first propose a new metric, called *Policy Optimized reuse Distance* (POD), which considers the impact of the *cache write policy* in addition to *request type* in reuse distance calculation. POD, unlike URD, does *not* reserve cache blocks for accesses that would not be supplied by the cache and, hence, allocates much smaller cache space for a VM, compared to URD, while preserving the VM's performance. Second, we propose the *Efficient <u>Two-Level I/O</u> <u>Caching Architecture</u> (ETICA) for virtualized platforms. ETICA employs <i>two levels* of cache, with DRAM at the first and SSD at the second level. Using the POD metric, the proposed architecture effectively partitions the space of both levels of cache between VMs and improves both performance and endurance.

In our proposal, we first assign an effective and fixed write policy to each cache level that provides high reliability and high endurance in DRAM and SSD levels, respectively. Second, using the POD metric, we partition the cache space by assigning an efficient cache size to each VM, which maximizes performance-per-cost. Third, we propose promotion and eviction methods to effectively transfer *popular* (i.e., *hot*) and unpopular (i.e., cold) data blocks between the two cache levels. Unlike previous I/O caching schemes, our proposed two-level cache does not evict popular data blocks from the cache until they become unpopular. Via online monitoring of I/O characteristics of the running workload, we extract several metrics such as 1) frequency, 2) type, and 3) POD of accesses in the running VMs. The extracted information is used to 1) estimate an efficient cache size for each VM and 2) detect popular and unpopular data blocks. To summarize, our proposed two-level I/O caching scheme aims to: 1) enhance both read and write performance, 2) overcome the reliability issues of the volatile DRAM cache, 3) improve the lifetime of the SSD cache, and 4) reduce the overall cost of the two-level cache (in terms of cache size allocated to each VM).

We implement our proposed two-level I/O caching mechanism on a real virtualized system including: 1) per-VM cache size estimation, 2) write policy assignment, 3) popular/unpopular data block detection, and 4) promotion/eviction mechanisms. We evaluate ETICA with more than 10 VMs running real application workloads from SNIA [54], [55]. Our experimental results show that the proposed architecture provides 45% lower I/O latency while also improving effective cache size and SSD endurance by 51.7% and 33.8%, respectively, compared to the best state-of-the-art caching scheme in virtualized platforms.

We make the following contributions.

- We propose a novel *two-level I/O cache* for virtualized platforms, using DRAM and SSD, that resolves reliability, endurance, and performance issues *without* any additional high-cost peripherals such as battery backups or internal disks.

- We propose a new metric, *Policy Optimized reuse Distance* (POD), which refines the concept of useful reuse distance calculation based on *cache write policy*. This metric does *not* allocate cache space for accesses that would not be served by the cache. Thus, it assigns a smaller cache space to each VM, resulting in lower cost.

- We propose a mechanism to assign efficient write policies for different cache levels to balance endurance and reliability of the I/O cache. Our mechanism enables read

<sup>1.</sup> Due to the degraded mode of *Redundant Array of Independent Disks* (RAID) [31] during the rebuild process in SSDs.

<sup>2.</sup> In a WB cache, the data block is written into the cache but the corresponding location in the hard disk is updated only when the data block is evicted from the cache, or at specific time intervals.

requests to be supplied from DRAM and write requests to be supplied from the SSD.

- Via online characterization of I/O requests, our technique effectively determines *popular* and *unpopular* data blocks. Our proposed promotion and eviction methods buffer and hold data blocks in the cache while they remain *popular*.

- We implement the proposed two-level I/O cache in a real system and evaluate the performance and endurance of our scheme by performing extensive experiments with more than 10 VMs running real application workloads on an open-source hypervisor, QEMU [56].

- We find ETICA to provide higher performance, higher efficiency, and higher endurance than the state-of-the art I/O caching schemes for virtualized platforms [6].

## 2 RELATED WORK

In this section, we first describe and analyze the previous I/O caching architectures in virtualized platforms. Second, we analyze the existing I/O cache architectures in two groups: 1) single level and 2) multi level, which are mainly employed in *non-virtualized* platforms.

## 2.1 I/O Caching in Virtualized Platforms

S-CAVE [10], vCacheShare [9], Centaur [11], and ECI-Cache [6] are the most state-of-the-art hypervisor-based I/O caching schemes in virtualized platforms. Such schemes employ a *single level* of SSD cache and mainly focus on dynamic and efficient cache space partitioning between running VMs. S-CAVE [10] uses the *Working Set Size* (WSS) of the VMs for cache space estimation. To preserve the reliability of write requests, the write policy of the SSD cache is set to *Write Through* (WT). Such cache size estimation (based on WSS) is deprecated and fails to accurately estimate the cache space needed for workloads with sequential access patterns [6].

vCacheShare [9] estimates the cache size of the VMs based on locality and reuse intensity (i.e., workloads' burstiness). vCacheShare considers both reliability and endurance by applying *Write Around* (WA) or *Read Only* (RO) write policies which direct the write requests to the disk subsystem and *only* improve the performance of read accesses via caching. The cache size estimation scheme used in vCacheShare is applicable to CPU caches, but its assumptions (e.g., reuse intensity) *cannot* be applied in I/O caches [11]. vCacheShare does *not* improve the performance of write requests.

Centaur [11] assigns cache space to the running VMs based on reuse distance analysis, which is an effective approach to cache size estimation. The write policy of the SSD cache is simply set to *Write Back* (WB). Such a cache size estimation scheme does not consider either the *request type* or the *cache write policy*, which leads to over-estimation of the cache sizes, negatively impacting cost. In addition, by using the WB policy, Centaur negatively affects both storage reliability and the endurance of the SSD cache.

ECI-Cache [6] is the latest state-of-the-art I/O caching scheme for virtualized platforms, which overcomes the shortcomings of previous schemes. It proposes the *Useful Reuse Distance* (URD) metric, which considers *request type* in cache size estimation and reduces the allocated cache space while preserving performance, enabling lower cost. ECI-Cache dynamically assigns either the WB or the RO policies for each VM and thus provides higher performance and endurance for the SSD cache. There are four issues with ECI-Cache, which we aim to overcome with our new design. **First**, ECI-Cache dynamically assigns RO and WB policies on the VM's cache, while URD-based cache size estimation does *not* consider the *cache write policy* and only works for WB and WT caches. URD reserves cache blocks for the accesses that would *not* be served by the cache due to different cache write policies, and therefore, it *over-estimates* the size of the caches using other policies, such as RO. For instance, in an RO cache, URD reserves cache blocks for write accesses that would *not* be buffered in the cache. **Second**, ECI-Cache is only a *one-level* (i.e., SSD-only) I/O cache where the performance improvement is limited by the performance of the SSD. **Third**, ECI-Cache updates the cache content on each cache miss and therefore imposes a large number of unnecessary writes into the SSD cache. **Fourth**, ECI-Cache's cache update scheme is supposed to promote any missed data blocks into the cache. Such scheme may evict a *hot* data block to promote a data block without any future references into the cache, resulting in performance degradation.

To summarize, existing hypervisor-based I/O caching architectures suffer from three major shortcomings: 1) they employ only an SSD in the caching layer, and thus their performance improvement is limited by the performance of the SSD (which is much lower than that of DRAM), 2) they fail in cache size estimation under different workloads and different cache write policies, and 3) they fail in balancing performance and endurance.

#### 2.2 I/O Caching in Non-Virtualized Platforms

#### 2.2.1 Single Level I/O Caches

A relatively high-performance memory device, such as DRAM or SSD is employed in the caching layer to close the performance gap between the processing units and the storage subsystem (which is mainly composed of lowperformance HDDs) [7], [8], [12], [14], [18], [19], [57]. Such I/O caching schemes improve the performance of I/O requests by providing efficient cache space allocation and configuration. However, they neglect other key parameters such as storage reliability and endurance of the SSDs. Argon [57] aims to efficiently partition the DRAM cache space between different services to maximize the cache hit ratio. Janus [12] allocates SSD space based on the ratio of read accesses of the workload and aims to improve the performance of read requests. Hystor [7] employs an SSD cache to improve the performance of read and write accesses and aims to identify and buffer the data blocks, which helps in improving the hit ratio. ReCA [8] characterizes the workloads of running applications and provides a per-application cache configuration. This scheme aims to improve both performance and endurance by assigning different cache policies to different applications, but it cannot minimize the number of SSD writes (mainly the writes due to read misses) because it uses a single SSD in the caching layer. ReCA is able to reconfigure 1) cache line size, 2) write policy, and 3) eviction policy. This scheme allocates cache space globally and neglects the cache management in case of running multiple workloads (i.e., services). Such scheme cannot be applied in virtualized platforms, where multiple VMs are running on the system. Since this approach only employs SSDs in the caching layer, the performance improvement is limited by the highest performance of the SSDs. SHARDS [58] presents a hashed approximate reuse distance sampling scheme to be used in cache size estimation. This scheme improves the performance of reuse distance calculation without considering requests type and cache write policy in reuse distance calculation.

#### 2.2.2 Multi Level I/O Caches

Such schemes employ both SSD and DRAM in the I/O caching layer.<sup>3</sup> uCache [37] provides a simple two-level I/O cache design by employing DRAM and SSD. In this scheme, data blocks are kept in DRAM until they are evicted, and after eviction they are moved to the SSD. uCache improves the process of demoting data blocks from DRAM to SSD by aggregating a large number of small writes and, hence, improves the endurance of the SSD. However, write-pending data blocks are kept in the *volatile* DRAM cache, which results in data loss in case of power failure. Molar [38] presents a simulator-based hybrid I/O cache without any improvement in eviction/promotion methods. This scheme consists of DRAM, SSD, and HDD tiers and migrates data blocks between them. Molar aims to predict the future accesses and decides which data block should be evicted from DRAM based on this prediction. This scheme does not employ any cache write policy management on different tiers and hence cannot preserve 1) the reliability of buffered data blocks in the volatile DRAM cache, and 2) the endurance of the SSD cache.

In [22], DRAM, Write Optimized SSD (WO-SSD), and Read Optimized SSD (RO-SSD) are used in the caching layer. Write requests are buffered in both DRAM and WO-SSD, read misses are promoted to DRAM, and evictions from DRAM are directed into the RO-SSD. The main shortcomings of this architecture are: 1) Write requests are directed to both DRAM and WO-SSD, hence, they experience the write latency of the SSD. Using DRAM to buffer the write accesses has *no* impact on the performance of writes and only helps to improve the latency of future reads that may hit in DRAM (i.e., RAW accesses). The limited DRAM space and small ratio of RAW accesses lead to very small performance improvement by this architecture. 2) This architecture prevents buffering write accesses in the RO-SSD (to preserve the lifetime of RO-SSD), but on the other hand, evictions from the DRAM and promotions of read misses are performed on RO-SSD which impose extra writes and have a negative impact on the limited lifetime of RO-SSDs. 3) This method is a *global* cache which cannot assign efficient cache space for the running services, and hence, is not applicable in virtualized platforms.

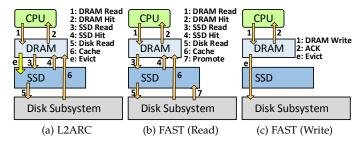

Zettabyte File System (ZFS) Level 2 Adaptive Replacement Cache (L2ARC) [33], [34], [35], [36] is a file system level cache, which improves upon Adaptive Replacement Cache (ARC) [69] by employing an SSD between DRAM and HDD (i.e., disk subsystem), thereby reducing the latency of read misses. L2ARC works in a simple First In First Out (FIFO) mode and only improves the performance of read requests. As shown in Fig. 2a<sup>4</sup>, read requests may be supplied from DRAM or SSD (i.e., hit), and read misses are supplied from the disk subsystem and promoted into DRAM. L2ARC predicts tobe-evicted data blocks from DRAM and pushes them to the SSD (before they have to be evicted). The major shortcomings of L2ARC are: 1) it lacks an efficient promotion/eviction method: only a simple FIFO manages the contents of the SSD, 2) it could waste the SSD space by pushing data blocks from DRAM to SSD before their eviction, 3) by keeping evicted

4. L2ARC does *not* buffer write requests in the SSD and, hence, we do not provide the flow of write accesses in Fig. 2.

blocks in the SSD, L2ARC mainly improves the performance of *Read After Read* (RAR) accesses with a reuse distance larger than the DRAM size (i.e., non-popular blocks), which has a relatively small impact on overall performance.

Dell EMC Fully Automated Storage Tiering (FAST) cache [3] is an enterprise approach that employs a two-level I/O cache in storage products. This scheme sets the write policy of the DRAM cache (called SP<sup>5</sup> cache) to Write Back (WB) to accelerate the performance of write requests and uses battery backups to maintain reliability in the presence of power and system failures. The write policy of the SSD cache is also set to WB. Fig. 2b and Fig. 2c show how FAST handles read and write requests. It employs a very simplistic method to identify hot data blocks where a block with more than three accesses in a recent time interval is identified as hot. Hot blocks are promoted to the SSD cache. There is no specified rule for evicting data blocks from cache. Thus, FAST may evict hot data blocks early from the cache (due to promoting new data blocks), which affects both performance and endurance of the SSD. In this case, promotion of the evicted hot data block again imposes additional write operations on the SSD.

Fig. 2: Architecture of two-level I/O caches employed in enterprise storage systems.

Table 1 summarizes the previously discussed architectures. Among all previous proposals, uCache [37], L2ARC [33], [34], [35], [36], and FAST [3] as two-level caching schemes and ECI-Cache [6] as a hypervisor-based I/O caching scheme are close to our proposal. However, the previous two-level caching schemes neglect cache write policy assignment on different cache levels and hence, fail to provide storage reliability and high endurance for the SSD cache. L2ARC works in the file system level and only improves read performance without considering the endurance of the SSDs. L2ARC fails in detecting popular blocks and does not provide efficient eviction/promotion methods where the cache is managed in a simple FIFO mode. FAST cache keeps write pending data blocks in volatile DRAM cache and employs additional battery backups to provide reliability and hence imposes additional cost. However, such scheme cannot guarantee the reliability of write pending data blocks. In addition, FAST cache employs a simple method to recognize hot data blocks which fails in different types of workloads. uCache keeps both read and write data blocks in DRAM. Thus, a power failure leads to data loss. On the other hand, the DRAM cache becomes polluted due to caching all requests in such small space. In addition, uCache does not consider the popularity of data blocks in the proposed caching scheme. ECI-Cache dynamically assigns different write policies on different VMs caches but does not take into account the impact of cache write policy on cache size estimation and hence, overestimates cache sizes for the VMs that use write policies other than WB. ECI-Cache imposes additional write operations to the

<sup>3.</sup> Many recent works examine DRAM cache design [59], [60], [61], [62], [63], [64], [65] for hybrid main memory systems, e.g., those combining DRAM and *Phase Change Memory* (PCM) [59], [66], [67] or *Spin-Transfer Torque Magnetic Random-Access Memory* (STT-MRAM) [68]. Our work is significantly different, since none of these recent works 1) are applicable to I/O caching in virtualized storage systems (as they focus on main memory), 2) develop the new reuse distance metric we introduce and evaluate. As such, our work is orthogonal to such hybrid main memory system designs, and the reuse distance metric we introduce can be useful within the hybrid main memory system context – an avenue we leave for future work.

<sup>5.</sup> SP: Storage Processor

SSD cache by updating the cache on each miss operation. In addition, it is one level: it employs only an SSD, no DRAM. Buffering both read and write requests in the SSD reduces the SSD endurance.

TABLE 1: Summary of previous architectures (WSS: Working Set Size, RI: Reuse Intensity, TRD: Traditional Reuse Distance, URD: Useful Reuse Distance, and POD: Policy Optimized reuse Distance).

| Architecture                      | Industrial | Virtualized | Cache Space<br>Partitioning | Multi Level     | Write Policy<br>Management | Endurance<br>Improvement | Reliability<br>Improvement |

|-----------------------------------|------------|-------------|-----------------------------|-----------------|----------------------------|--------------------------|----------------------------|

| S-CAVE [10]                       | ×          | ~           | WSS                         | (SSD)           | ×                          | ×                        | ~                          |

| vCS [9]                           | ×          | ~           | RI                          | (SSD)           | ×                          | ~                        | ~                          |

| Centaur [11]                      | ×          | ~           | TRD                         | (SSD)           | ×                          | ×                        | ×                          |

| ECI-Cache [6]                     | ×          | ~           | URD                         | (SSD)           | ~                          | ~                        | ×                          |

| Argon [57]                        | ×          | ×           | Acc.<br>Based               | (DRAM)          | ×                          | -                        | ×                          |

| Janus [12]                        | ×          | ×           | Read<br>Acc.<br>Based       | ¥<br>(SSD)      | ×                          | ×                        | ×                          |

| Hystor [7]                        | ×          | ×           | Global                      | (SSD)           | ×                          | ×                        | ×                          |

| ReCA [8]                          | ×          | ×           | Global                      | (SSD)           | ~                          | ~                        | ×                          |

| [22]                              | ×          | ×           | Global                      | (DRAM+SSD)      | ×                          | 1                        | ×                          |

| uCache [37]                       | ×          | ×           | Global                      | (DRAM+SSD)      | ×                          | ×                        | ×                          |

| L2ARC<br>[33], [34]<br>[35], [36] | ~          | ×           | Global                      | ✔<br>(DRAM+SSD) | ×                          | ×                        | ×                          |

| FAST [3]                          | ~          | ×           | Global                      | (DRAM+SSD)      | ×                          | ~                        | ×                          |

| ETICA<br>(Proposed)               | ×          | ~           | POD                         | (DRAM+SSD)      | ~                          | ~                        | ~                          |

## **3 MOTIVATION AND ILLUSTRATIVE EXAMPLE**

I/O caches are employed to enhance the performance of storage systems. High-locality data blocks are kept in the cache to serve future requests to them faster and hence reduce the response time significantly. Currently, enterprise storage systems employ high-performance SSDs in the I/O caching layer. SSDs provide more than 500X the performance provided by HDDs (in terms of IOPS for random requests) but SSDs wear out fast due to write operations. Depending on the cache *write policy*, both read and write requests from the application layer may impose write operations on the SSD. Four different write policies can be used on the cache. We elaborate on how 1) requests are supplied by the cache, and 2) performance, reliability, and endurance are affected by different write policies:

• Write Back (WB) (with write allocate and no read through<sup>6</sup>) buffers write requests in the I/O cache and writes them back to the storage subsystem when the dirty blocks are evicted. Read requests are also buffered in a WB cache. Each miss from the cache imposes an additional write operation into the cache to store the read block. The WB policy reduces write accesses to the disk subsystem and thus improves both read and write performance. WB policy may lose the write-pending data before they can be written back to the storage subsystem, on power failure. In addition, an SSD

6. A read through cache buffers read misses in the cache, and hence, serves further read accesses to that address.

WB cache wears out fast due to the large number of write operations induced on the cache.

- *Write Through* (WT) (with write allocate and no read through) buffers write requests in the I/O cache and at the same time also commits them to the storage subsystem. In addition to writes, WT cache buffers also read requests. WT does *not* improve write performance and only helps read performance. WT policy preserves the reliability of writes since it does *not* buffer any write-pending data (i.e., dirty blocks). WT policy has the same negative impact on the endurance of the SSD as the WB policy.

- *Write Only* (WO) (with write allocate and read through) handles the write requests in a similar way to the WB policy. Read requests are *not* buffered in the WO cache. Hence, this policy improves the performance of only write and *Read After Write* (RAW) operations. WO does not incur additional write operations due to read misses in the cache and, therefore, significantly improves the endurance of an SSD cache.

- *Read Only* (RO) (with no read through) buffers *only* read requests and directs writes to the storage subsystem. RO improves only read performance and preserves the reliability of write requests. RO has a positive impact on SSD cache endurance because it does not expose the I/O write requests to the cache.

We conduct comprehensive experiments to examine the impact of these write policies on the performance and endurance of the SSD cache (in terms of number of write operations on the SSD). The results of these experiments motivate us in selecting the optimized cache policies to provide higher performance, endurance, and reliability in our proposed I/O caching architecture. In these experiments, we study the use of an SSD as a caching layer for the HDD-based storage subsystem with three types of write policies: 1) WB, 2) RO, and 3) WBWO (i.e., WB and WO). WT cache compared to WB (as described earlier) provides similar performance for read accesses and degraded performance for write accesses (due to simultaneous writes in both SSD and HDD devices). Hence, we do not report WT cache performance in our evaluations.

To do so, we perform experiments on a real system. The experimental setup and the running workloads are reported in Table 2. We use an open-source EnhanceIO cache module [70] to implement our I/O caching scheme. The system is warmed up for 30 minutes and then we run the workload for one hour.

TABLE 2: Setup of the motivational experiments.

| Hardware           |                              |                                                                                     |                                       |             |         |              |  |  |  |  |  |  |  |

|--------------------|------------------------------|-------------------------------------------------------------------------------------|---------------------------------------|-------------|---------|--------------|--|--|--|--|--|--|--|

| HDD                |                              | 6x 4TB SAS 7.2K Seagate HDD in R5 (5+1) configuration<br>Disk Partition size: 200GB |                                       |             |         |              |  |  |  |  |  |  |  |

| SSD                | 4x 2TB Sa<br>Disk Part       | 4x 2TB Samsung 863a SSD in R10 (2+2) configuration<br>Disk Partition size: 50GB     |                                       |             |         |              |  |  |  |  |  |  |  |

| DRAM               | 128GB Sa                     | 128GB Samsung DDR4                                                                  |                                       |             |         |              |  |  |  |  |  |  |  |

| CPU                | 32xIntel(I                   | 32xIntel(R) Xeon (R) 2.1GHz CPU core                                                |                                       |             |         |              |  |  |  |  |  |  |  |

| Software           |                              |                                                                                     |                                       |             |         |              |  |  |  |  |  |  |  |

| OS                 | CentOS 7                     | CentOS 7 (kernel version: 3.10.327)                                                 |                                       |             |         |              |  |  |  |  |  |  |  |

| Workloads          |                              |                                                                                     |                                       |             |         |              |  |  |  |  |  |  |  |

| FIO [71]<br>RandRW | Req.<br>Size                 | Req.<br>Type                                                                        | Access<br>Pattern                     | IO<br>Depth | Threads | IO<br>Engine |  |  |  |  |  |  |  |

| KanuKw             | 8KB                          | Read/Write<br>(Read: 70%)                                                           | Random<br>(distribution:<br>zipf:1.1) | 16 16       |         | Libaio       |  |  |  |  |  |  |  |

| FileBench          | Dee                          | Des                                                                                 | Access                                |             |         |              |  |  |  |  |  |  |  |

| [72]               | Req.<br>Size                 | Req.<br>Type                                                                        | Pattern                               | Th          | reads   | WSS          |  |  |  |  |  |  |  |

| Web<br>Server      | 64KB Read/Write Random 100 6 |                                                                                     |                                       |             |         |              |  |  |  |  |  |  |  |

| Video<br>Server    | 256KB                        | Read                                                                                | Sequential                            |             | 120GB   |              |  |  |  |  |  |  |  |

| Varmail            | 64KB                         | Read/Write                                                                          | Random                                |             | 16      | 62GB         |  |  |  |  |  |  |  |

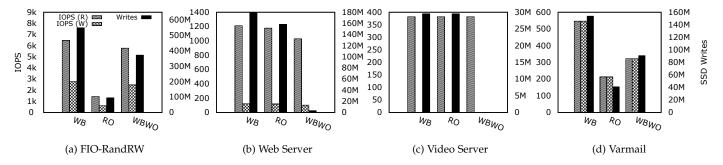

Fig. 3 shows the results of the experiments, in terms of both performance (measured as *Input/Output Operations Per Second* (IOPS)) and endurance (measured in terms of committed write operations on the SSD). We make four major observations:

Fig. 3: Effect of the cache write policy on the performance of workloads and endurance of the SSD cache (WB: Write Back, RO: Read Only, WBWO: Write Back and Write Only, and IOPS: Input/Output Operations Per Second).

- 1) In the FIO-RandRW workload, WB achieves the highest performance. But, WB also imposes the highest number of write operations on the SSD compared to other policies. As shown in Fig. 3a, by using WBWO cache, performance decreases by 10.7% while the number of write operations on the SSD also decreases by 32%. The RO cache provides about 78% lower performance compared to the WB cache while it decreases the SSD writes by 82%. This is because the FIO-RandRW workload mainly includes Read After Write (RAW) operations (70% read operations), where buffering the write requests in the cache (as in the WB and WBWO policies) significantly improves both read and write performance. WBWO policy does not cache read misses and hence decreases the number of SSD writes by 32% with only 10% performance degradation, compared to the WB cache. On the other hand, RO does not help the performance of RAW operations and, therefore, cannot provide good performance. In addition, RO does not cache I/O write requests and hence, provides no performance improvement for them.

- 2) In the Web Server workload, the WB policy achieves the highest performance while also having the highest number of write operations on the SSD. The difference in performance provided by the three policies is very low: Fig. 3b shows that the WB cache achieves about 15% higher performance compared to WBWO by imposing 98% more writes on the SSD. Compared to RO, WB only marginally improves performance (by 2.7%) at the cost of imposing 11.3% more writes on the SSD. This is because the Web Server workload mainly includes random cold reads (i.e., the first read access to an address) with low locality of reference, and keeping such data blocks in the SSD cache does not help in improving read performance. The WB and WO caches keep read miss data blocks in the SSD cache and impose about 178M and 158M writes on the SSDs, respectively, while WBWO, compared to WB, does not cache read misses and achieves almost similar read performance (about 15% lower) with a significantly smaller number of writes on the SSDs (about 98% lower).

- 3) In the Video Server workload, all three polices achieve the same read and write performance with considerable difference in the number of SSD writes. As shown in Fig. 3c, WB, RO, and WBWO achieve 382 IOPS in read and 0 IOPS in write requests (the running workload includes *only* read requests). WB and RO impose about 29M writes on the SSD cache while WBWO does *not* perform any write operations on the SSD cache. This is because the Video Server includes sequential read requests without any locality of reference. Thus, WB and RO perform a large number of unnecessary writes (due to read misses)

into the SSD cache without any performance gain. WBWO imposes no writes to the SSD cache and achieves the same performance as WB and RO. Note that for such a sequential read workload, all requests are supplied from the HDD and the cache hit ratio is equal to 0.

In the Varmail workload, WB has the highest performance 4) and SSD writes. Both WBWO and RO reduce performance and SSD writes over WB. This is because the RO and WBWO caches fail in serving RAW and RAR accesses, respectively. Fig. 3d shows that both read and write performance of WB are about 41% more than WBWO while WBWO imposes about 40% fewer writes on the SSD. Compared to RO, WB achieves 61% higher performance by imposing 73% more writes into the SSD. The reason is that Varmail includes an equal number of random read and write requests. WBWO does not cache read misses and hence cannot help the RAR requests, but it reduces the number of writes on the SSD. RO does not buffer write requests and thus RAW requests, but it reduces the number of writes on the SSD.

Our main experimental conclusions are:

- In most of the workloads, WB cache achieves the highest performance for read and write requests, however it also imposes the highest number of writes on the SSD. Hence, WB does *not* balance performance and endurance.

- 2) In workloads with a large number of cold reads (such as Web Server and Video Server), WBWO has almost the same performance as WB while it imposes a much smaller number of writes on the SSD cache.

- 3) In workloads with a large number of read requests (such as FIO-RandRW), WBWO cannot provide as good read or write performance as WB, but it results in a smaller number of SSD writes.

- 4) RO cache can be employed in read-intensive workloads with a large number of re-references to greatly extend the SSD lifetime with negligible performance impact compared to WB.

- 5) In workloads such as Video Server and Web Server, cache read misses impose a large number of write operations on the SSD, affecting both endurance and performance.

# 4 ETICA ARCHITECTURE

In this section, we present the architecture of our proposed two-level I/O cache, ETICA. ETICA has four major characteristics. It: 1) employs both DRAM and SSD in the caching layer of virtualized platforms, 2) assigns effective cache write policies to the two levels of cache, 3) effectively detects the popular data blocks and aims to evict only unpopular blocks from the cache, and 4) allocates efficient cache space for the VMs using the *Policy Optimized reuse Distance* (POD) metric. Fig. 4 provides an overview of the proposed two-level cache for virtualized platforms. The I/O cache employs two levels including DRAM in the first and the SSDs in the second level. The information about the content of cache levels is kept in a table called *Map*. The hypervisor receives the I/O requests of the VMs, and routes them to the storage subsystem. The two-level cache resides on the path of requests to the disk subsystem. The cache searches the destination address of the requests in *Map* and finds out whether the corresponding data is located in the 1<sup>st</sup> level (i.e., DRAM hit) or the 2<sup>nd</sup> level (i.e., SSD hit). If neither is the case, the request is supplied by the disk subsystem (i.e., cache miss).<sup>7</sup>

Fig. 4: Architecture of ETICA.

We aim to take advantage of the different merits of both the DRAM technology and SSDs while minimizing the negative characteristics of each. DRAM provides high performance but comes with 1) reliability issues (due to volatility) and 2) high cost. SSDs preserve reliability (due to non-volatility) and have 20X lower cost than DRAM, but they have 1) lower performance and 2) limited endurance (i.e., write cycles). As shown in Fig. 4, DRAM in the first level of the proposed cache mainly improves performance (and endurance) while the SSD in the second level avoids the performance spikes due to the large performance gap between DRAM and the disk subsystem and provides reliability. In Section 4.1, we describe how we assign different write policies at different levels of cache to address the shortcomings and exploit the advantages of each technology. In Section 4.2, we propose popular/unpopular block detection and our promotion/eviction schemes to manage the two-level cache even more efficiently. In Section 4.3, we describe how ETICA estimates efficient cache sizes for different VMs.

#### 4.1 Write Policy Management

We use DRAM in the first level of our I/O cache architecture to enable high performance. Using such a volatile storage technology increases the risk of data loss under different types of failures, such as power failures. We use SSDs in the second level of our I/O cache architecture. SSDs mainly suffer from endurance, i.e., they can support only a limited number of reliable writes. This section shows how we 1) preserve storage reliability in the presence of DRAM and 2) enhance SSD endurance in our proposed two-level I/O cache by applying effective write policies on both levels. Previously, in Section 3, we described the different types of cache write policies and their impact on performance, reliability, and endurance. To address the storage reliability issue with using DRAM, we assign the RO policy to the first level of cache (i.e., the DRAM level). In this case, *no* write requests are served (i.e., supplied) by DRAM and hence, there is no write-pending request (i.e., dirty block) in DRAM. Write requests are directed immediately to the non-volatile second level (i.e., the SSD level), which is able to protect the write-pending data in case of power outage (it is important to note that in our scheme, we use SSDs in the RAID10 configuration [73], which tolerates the failure of up to two SSDs). In this scheme, the DRAM level is responsible for buffering and serving only read requests. Buffering only read requests in DRAM guarantees that any data block in the DRAM level has a copy in another level

in DRAM has no negative reliability impact. To address the endurance issue of the SSDs, we assign the WBWO policy to the second level (i.e., the SSD level). Recall that in Section 3, we observed the significant negative impact of buffering read misses on the endurance of the SSD cache. The WBWO policy buffers only write requests in the cache and does *not* buffer read requests. Buffering only write requests in the SSDs effectively improves the endurance of the SSDs by reducing the number of unnecessary write operations on the SSDs (that would otherwise be needed to buffer read requests). Using WBWO at the SSD level does not degrade performance because read requests are buffered and served at the DRAM level.

(i.e., the SSD level or the disk subsystem). Thus, losing data

In summary, the key advantages of our heterogeneous write policy assignment for two different cache levels are:

- We preserve the reliability of write requests by bypassing DRAM and buffering them only in SSDs (in RAID10 configuration).

- 2) We improve the endurance of the SSDs by buffering only write requests while read misses (which would impose a large number of write operations on the SSDs) are only cached in the DRAM level.

- 3) The DRAM level improves the performance of read requests while the SSD level improves the performance of write requests, compared to HDDs. The read misses from DRAM that happen to be supplied by the SSDs (due to RAW requests) also experience the higher performance of SSDs versus the disk subsystem.

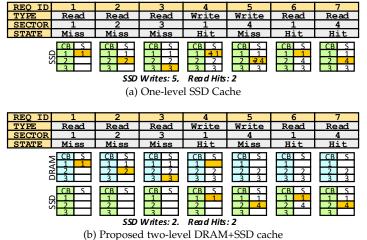

We now provide an example and show how the proposed write policy assignment approach in our two-level cache 1) improves the endurance of SSDs, 2) preserves the reliability of I/O requests, and 3) keeps performance intact. In the example of Fig. 5, we compare a one-level WB SSD cache (Fig. 5a) with our two-level cache where the write policy of the DRAM and SSD levels are RO and WBWO, respectively (Fig. 5b). Each cache level has a capacity of 3 data pages. Note that in this example, no cache size estimation algorithm is employed.

When one-level SSD caching is used, as shown in Fig. 5a,  $Req_1$  reads the data of sector 1 and buffers the corresponding data block into the cache (due to read miss) by imposing one write operation on the SSD. Similarly,  $Req_2$  and  $Req_3$  are read misses that are buffered in the cache and each one imposes an additional write on the SSD.  $Req_4$  overwrites the data content of the cache (sector 1 in cache block 1) and  $Req_5$  writes the contents of sector 4 into the cache (in cache block 2).  $Req_6$  hits in the cache and reads sector 1 from cache block 1, which was previously written by  $Req_4$ . Similarly,  $Req_7$  reads data from cache as it is a read hit. We observe that, in the one-level WB SSD cache, the sample workload imposes 5 write operations to the SSD and obtains 2 read hits.

Fig. 5b shows how the two-level cache design of ETICA (with RO DRAM and WBWO SSD levels) supplies the I/O requests with a much smaller number of write operations on

<sup>7.</sup> Each cache level works based on set-associative mapping scheme where each set size is 512 blocks (the set size is configurable to other sizes, but to have a fair comparison, in our experiments the associativity configuration in ETICA is done the same as ECI-Cache).

Fig. 5: Comparison of a) one-level and b) the proposed twolevel cache in terms of endurance, reliability, and performance (CB: Cache Block and S: Sector).

the SSD. In the two-level cache,  $Req_1$ ,  $Req_2$ , and  $Req_3$  buffer data blocks into the DRAM level (due to read misses) without imposing any write operations on the SSD.  $Req_4$  overwrites the cache content (sector 1): the write request is served by the SSD and the existing data block in DRAM is marked as invalid.  $Req_5$  is a write request that bypasses DRAM and writes data directly into the SSD. Finally, Req<sub>6</sub> and Req<sub>7</sub> are read requests that hit in the cache and read the data blocks from the SSD level. Unlike the one-level SSD cache, our twolevel cache design imposes only 2 write operations on the SSD (60% fewer than one-level) while providing the same hit ratio as one-level does. In summary, compared to the one-level SSD cache, our two-level DRAM+SSD cache with intelligent cache write policy assignment reduces the number of write operations on the SSD while preserving the reliability of write requests and achieving similar performance.<sup>8</sup>

#### 4.2 Promotion/Eviction Optimization

In this section, we propose another approach for improving both endurance and performance in our two-level I/O cache, in which we mainly focus on improving performance (in terms of hit ratio) with the minimum number of write operations into the SSD. The proposed approach is mainly adopted from pull mode caches (i.e., non-datapath caches), where the content of the SSD cache is not updated during handling of miss accesses (as opposed to push mode caches or datapath caches) [74]. Updating cache blocks on each cache miss (as push mode caches such as LRU<sup>9</sup> and LFU<sup>10</sup> caches do) leads to promoting new blocks to the cache which could easily be less popular than the evicted ones. Instead, periodically, we detect unpopular data blocks and evict them from the SSD and promote *popular* ones. Thus, we minimize the probability of evicting *popular* blocks from the cache, thereby avoiding performance (due to cache miss) and endurance (due to promoting new data blocks into the cache) overheads associated with the churn caused by the pollution due to unpopular blocks. To do so, we first detect popular and unpopular data blocks and then decide when to promote and evict them to/from the SSD level.

10. Least Frequently Used

We aim to detect *popular* and *unpopular* data blocks via online characterization of the running workload on the VMs. To this end, in specific time intervals (which are determined based on the number of requests, e.g., after observing N I/O requests), we analyze the characteristics of the running workloads based on the collected information such as 1) request type, 2) number of accesses, and 3) POD of data blocks. In Section 4.2.1, we describe how we detect *popular* and *unpopular* data blocks.

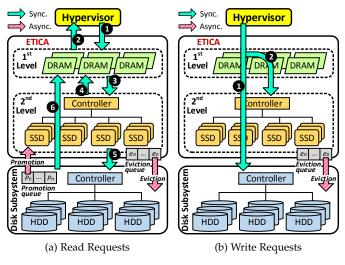

Fig. 6 shows the flow of I/O requests in our proposed twolevel I/O cache for both read and write accesses. As shown in this figure, we employ two queues in our scheme: 1) promotion queue in the disk subsystem level and 2) eviction queue in the SSD cache level. The data blocks in the disk subsystem that are recognized as *popular* are pushed into the promotion queue while the *unpopular* ones in the SSD cache are inserted into the eviction queue. Periodically, we evict the blocks in the eviction queue from the SSD cache to the disk subsystem and promote the blocks in the promotion queue into the SSD cache (only when there is free space in SSD). This approach greatly increases the likelihood that 1) data blocks are evicted from the SSD when they become unpopular, 2) only popular data blocks are buffered in the SSD cache, and 3) we do not replace a data block in the SSD cache with a less popular one. Hence, the proposal improves both performance and SSD endurance.

Fig. 6: Examples showing how ETICA handles requests.

We now elaborate on how our proposed promotion and eviction approach in our two-level I/O cache handles the I/O requests. Fig. 6a and Fig. 6b provide the detailed flow of read and write requests, respectively.

4.2.0.1 Read: As shown in Fig. 6a, the read request is first received in the DRAM level (1). If the corresponding data block is found in the DRAM cache (i.e., DRAM hit), the request is served via the DRAM level (2). Otherwise, the request is sent to the SSD in the second level (3). In the case of an SSD hit, we first promote the data block to the DRAM level (4) and then serve the request. Otherwise, in case of an SSD miss (5) we read the data from the disk subsystem and promote it directly to the DRAM level *without* buffering in the SSD level (6). Recall that the write policy management scheme presented in Section 4.1 sets the policy of the SSD level to WBWO, where no read miss is buffered in the SSD. However, any data block that is detected as *popular* in the disk subsystem (listed in the promotion queue) is promoted to the SSD level to accelerate future accesses. Furthermore,

<sup>8.</sup> Performance of our scheme would be higher when requests hit in the DRAM level.

<sup>9.</sup> Least Recently Used

*unpopular* data blocks in the SSD are evicted through the eviction queue.

4.2.0.2 Write: Fig. 6b shows how we handle write requests in the proposed two-level I/O cache. Write requests (in case of both hit or miss) bypass the DRAM (since the write policy of the first level is set to RO). In case of an SSD miss (1), the data block is directly written to the disk subsystem. Otherwise, in the case of an SSD hit where the corresponding data block is located in the second level (as a *popular* block), the data block update in any level (SSD and disk subsystem), we invalidate the corresponding data block in upper level (DRAM and SSD, respectively). The operation of the eviction queue in handling writes is the same as that of the eviction queue in handling read requests.

To summarize, the proposed eviction/promotion scheme provides the following key benefits:

- 1) Performance improvement by keeping *popular* data blocks in the SSD cache as long as possible.

- SSD endurance improvement (reduced number of SSD cache updates) by periodically promoting *only* popular data blocks into the SSD cache.

#### 4.2.1 Popular and Unpopular Block Detection

In this section, we provide our approach to detecting *popular* and *unpopular* data blocks. Our proposal decides the popularity of data blocks based on two key parameters: 1) POD and 2) frequency of accesses. Hence, we consider both *spatial* and *temporal* locality. We update the *popularity*( $B_i$ ) parameter for each access to the *i*<sup>th</sup> data block  $B_i$  and push the data block into the eviction or promotion queues based on its relative popularity. The least popular 5% of the blocks in the SSD (i.e., the *unpopular ones*) are put into the eviction queue. Similarly, the most popular 5% of the data blocks in disk subsystem (i.e., HDD) are pushed into the promotion queue. Eq. 1 shows how we calculate *popularity*( $B_i$ ):

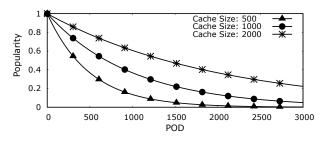

$$popularity(B_i) = \sum_{t=1}^{numAcc} e^{-\frac{POD(i,t)}{cacheSize}}$$

(1)

Where POD(i, t) is the POD of  $B_i$  in the  $t^{th}$  access to that data block,<sup>11</sup> numAcc is the number of accesses to  $B_i$ , and cacheSize is the allocated cache size to the VM. Popularity of each data block is updated periodically in specified time intervals. To keep the popularity information of each data block, a space of 8B is required per data page (4KB). The memory overhead is less than 0.15% (e.g., we need an 8MB space to store the popularity of one million data blocks. This information is kept in SSD). Since popularity is computed asynchronously, its computation does not cause any overhead to the servicing of I/O requests. Fig. 7 shows the impact of POD on the popularity of each access for different cache sizes. It can be seen that calculating  $popularity(B_i)$  based on Eq. 1 provides the following key ideas:

- 1) A larger POD leads to smaller *popularity*. Note that when the POD of a block is close to the cache size, the frequency of access to that block is low. Thus, that block likely has no significant impact on the total cache hit ratio.

- 2) When the POD of a block is larger than the cache size, and since this block will be missed from cache, we set low *popularity* to that block according to Eq. 1. On the other hand, we set high *popularity* for a block with a POD smaller than the cache size.

3) The frequency of the accesses is considered in the popularity calculation. In Eq. 1, we estimate the total popularity of a single block based on all accesses to that block.

Fig. 7: Popularity as a function of POD and cache size.

The proposed popularity detection scheme is scalable, which is compatible with the removal or addition of VMs into the system. When we add a new VM to the system (or when an existing VM comes online), based on the I/O accesses of that VM, ETICA first assigns efficient cache space in both DRAM and SSD levels and then estimates the popularity of that VM's accesses (we calculate popularity of each VM's accesses independently from other VMs). In contrast, when a VM is removed from the system (or when it goes offline), we reclaim the allocated cache space and thus the popularity detection process for this VM is also stopped. Furthermore, since in specific intervals, ETICA recalculates the cache size of the VMs, in case of extending or shrinking the total SSD and DRAM cache spaces, ETICA is able to reconfigure the newly allocated cache sizes to the VMs based on new SSD and DRAM sizes.

#### 4.3 Cache Size Estimation

In this section, we propose our two-level cache size estimation approach that aims to 1) maximize the overall performance of the co-running VMs and 2) minimizes the overall cost (in terms of allocated cache size). We effectively partition the space of both levels (DRAM and SSD) between VMs based on their demand. In Section 4.3.1, we propose the metric of *Policy Optimized reuse Distance* (POD) and demonstrate how the proposed metric effectively reduces the allocated cache size to the workloads (compared to the previous state-of-theart scheme, URD) by considering both 1) *request type* and 2) *cache write policy* in the reuse distance calculation, and thereby resulting in reduced cost. Then in Section 4.3.2 we show how ETICA assigns efficient cache size for the VMs to achieve the most efficient performance per cost.

#### 4.3.1 Policy Optimized reuse Distance (POD)

Traditional Reuse Distance (TRD) [58], [75], [76], [77], [78], [79], [80], [81], [82], [83], [84], [85] calculates the distance of the requests only based on the address and access order of the requests. Useful Reuse Distance (URD) [6] improves upon TRD by considering request type in reuse distance calculation: it considers only the distance of Read After Read (RAR) and Read After Write (RAW) accesses, enabling a smaller cache with the same or with better performance [6]. However, existing schemes that are employed in cache size estimation neglect the impact of *cache write policy* on reuse distance calculation. In this section, we first provide examples to show the effect of the cache write policy on reuse distance calculation of the workloads. Then, we propose a novel metric, *Policy Optimized reuse* Distance (POD), which allocates much smaller cache space compared to TRD and URD while preserving performance (in terms of hit ratio). The POD metric considers both request

<sup>11.</sup> In Section 4.3.1 we elaborate how to calculate POD.

*type* and *cache write policy* in reuse distance calculation, and hence, does *not* reserve cache blocks for the requests which would *not* be served by the cache (i.e., read accesses in a WBWO and write accesses in a RO cache, respectively). We provide sample workloads and elaborate on how URD (which considers only the request type without considering the cache write policy) and POD (which considers *both* request type and the cache write policy) estimate cache size for caches that use 1) WBWO and 2) RO write policies.

Fig. 8 compares the cache size estimation provided by URD and POD in a WBWO cache. For the given sample workload in Fig. 8a, URD detects the maximum reuse distance between  $Req_1$  and  $Req_6$  (due to their RAR accesses to the same sector, i.e., sector 1). Hence, the maximum URD is equal to 4, and 5 blocks of cache are allocated to the workload. Fig. 8a shows that the workload uses only two blocks of the allocated cache space for write requests (write accesses to sector 4 and sector 5 by  $Req_4$  and  $Req_5$ , respectively). Since data blocks of read misses are not buffered in a WBWO cache, three blocks of allocated cache remain unused while they are reserved for this workload. At the end of the workload, Req<sub>7</sub> reads the buffered data block from the cache: it is a read hit due to the RAW operation. We observe that a cache with WBWO policy helps only the write and RAW<sup>12</sup> requests without providing any performance improvement for read and RAR (i.e., Read After Cold<sup>13</sup> Read) accesses.

The POD metric considers both request type (similar to URD) and cache write policy in reuse distance and cache size estimation. Fig. 8b shows how POD estimates cache size for the sample workload. POD estimates the maximum reuse distance based on  $Req_4$  and  $Req_7$  due to their RAW access to sector 4. In this case, the POD of the workload is equal to 1. Crucially, note that the read access of  $Req_6$  is *not* considered in POD calculation in the WBWO cache. This is because such a request would *not* be served by the cache. Therefore, only two blocks of cache are allocated to the workload.  $Req_4$  and  $Req_5$ commit write requests into the cache (due to their accesses to sectors 4 and 5) and  $Req_7$  (to sector 4) is supplied from the cache. In summary, for the given sample workload, we observe that in a WBWO cache URD allocates 5 blocks while POD allocates only 2 blocks of cache and achieves the same I/O performance (for both read and write requests) as URD.

| RE  | Q   | TYP | SEC |   | e |  | s | REQ | TYP | SEC              | Ca | che | s |   |   |

|-----|-----|-----|-----|---|---|--|---|-----|-----|------------------|----|-----|---|---|---|

| ┢   | 1   | R   | 1   |   |   |  |   |     | м   | 1                | R  | 1   |   |   | м |

|     | 2   | R   | 2   |   |   |  |   |     | м   | 2                | R  | 2   |   |   | м |

| Q   | 3   | R   | 3   |   |   |  |   |     | м   | 3                | R  | 3   |   |   | м |

| URD | 4   | W   | 4   | 4 |   |  |   |     | н   | ₽4               | W  | 4   | 4 |   | н |

|     | 5   | W   | 5   | 4 | 5 |  |   |     | н   | 85               | W  | 5   | 4 | 5 | н |

| Ь   | 6   | R   | 1   | 4 | 5 |  |   |     | м   | <mark>6</mark> 6 | R  | 1   | 4 | 5 | м |

|     | 7   | R   | 4   | 4 | 5 |  |   |     | н   | <del>ا ک</del>   | R  | 4   | 4 | 5 | н |

|     | (a) |     |     |   |   |  |   |     |     |                  |    | (b) |   |   |   |

Fig. 8: Comparison of cache size allocation in a WBWO cache (a) without and (b) with considering cache write policy (REQ: Request, TYP: Type, SEC: Sector, W: Write, R: Read, S: State, H: Hit, M: Miss).

Fig. 9 shows how URD and POD work in a RO cache, by comparing the cache allocation and I/O performance of these two schemes. For the given sample workload in Fig. 9a, URD detects the maximum reuse distance for the RAW access by  $Req_1$  and  $Req_7$  to sector 1 of the disk. In this case, the URD of the workload is equal to 4 and hence, five blocks of cache are allocated to the workload (note that read access of  $Req_6$  to sector 3 is duplicated with  $Req_3$  and both of them are supplied by the same cache block). Fig. 9a shows that the write accesses of the workload  $(Req_1, Req_4, and Req_5)$ are bypassed from the cache and are supplied by the disk subsystem. Only the *read misses* ( $Req_2$  and  $Req_3$ ) are buffered in cache and RAR accesses such as  $Req_6$  are served while RAW accesses such as *Req*<sup>7</sup> cannot be served by the RO cache. Only three blocks of allocated cache are actually used and the remaining two blocks are unused but they are reserved by the workload. This is because the RO cache only buffers reads and serves RAR accesses. In this case, reserving cache blocks for write accesses (as URD does) has no performance benefit while imposing additional cost (because it allocates larger cache space with unused cache blocks).

In Fig. 9b, we show how POD considers the cache write policy in reuse distance calculation and results in 1) a much smaller cache space allocation compared to URD and 2) the same I/O performance as URD. In the RO cache, POD detects the maximum reuse distance of the workload for the RAR accesses to sector 3 by  $Req_3$  and  $Req_6$ . Since no write request can be supplied by RO cache, write requests are not considered in the POD calculation of such a cache. Hence, POD is equal to 0 ( $Req_4$  and  $Req_5$  are not considered since write accesses have no impact on the RO cache operation) and only one block of cache is allocated to the workload. As shown in Fig. 9b, write accesses  $(Req_1, Req_4, and Req_5)$  are not served by the cache. A read miss by  $Req_2$  promotes the data block of sector 2 into the cache. Then,  $Req_3$  updates the cache by promoting the data block of sector 3 (note that in this workload there is no future read access to sector 2 and POD enables updating the data block by  $Req_3$ ).  $Req_6$  hits in the cache and finally, Req<sub>7</sub> promotes sector 1 into the cache. We observe that in an RO cache, POD calculates the maximum reuse distance based on RAR operations. Compared to URD, POD assigns a much smaller cache space to the workload (only 1 block versus 5 blocks) while achieving exactly the same cache hit ratio.

| F | ΈQ         | TYI | SEC |   | lach | e |   | s | REQ | TYP        | SEC | Cache | S |   |

|---|------------|-----|-----|---|------|---|---|---|-----|------------|-----|-------|---|---|

| 1 | <b>;</b> { | LW  | 1   |   |      |   | М | 1 | W   | 1          |     | М     |   |   |

|   | 2          | 2 R | 2   | 2 |      |   |   |   | М   | 2          | R   | 2     | 2 | м |

|   |            | B R | 3   | 2 | 3    |   |   |   | м   | 3 ←        | R   | 3     | 3 | м |

|   | Ę          | W   | 4   | 2 | 3    |   |   |   | м   | <b>4</b>   | W   | 4     | 3 | м |

|   | 5          | 5 W | 5   | 2 | 3    |   |   |   | м   | <b>0</b> 5 | W   | 5     | 3 | м |

|   | e          | 5 R | 3   | 2 | 3    |   |   |   | н   | 46         | R   | 3     | 3 | н |

|   | <b>}</b>   | R   | 1   | 2 | 3    | 1 |   |   | м   | 7          | R   | 1     | 1 | м |

|   | (a)        |     |     |   |      |   |   |   |     |            |     | (b)   |   |   |

Fig. 9: Comparison of cache size allocation in RO cache (a) without and (b) with considering cache write policy (REQ: Request, TYP: Type, SEC: Sector, W: Write, R: Read, S: State, H: Hit, and M: Miss).

To summarize, the key ideas behind POD are as follows:

- 1) POD considers both 1) *request type* and 2) the specific *cache write policy* in the reuse distance calculation.

- 2) In a WBWO cache, the reuse distance calculation of POD is based only on the *maximum* distance of RAW accesses (also including RARAWs). This is because no RAR (i.e., Read After *Cold* Read) request is supplied by a WBWO cache (since the cache does *not* buffer read misses). Hence,

<sup>12.</sup> Note that WBWO cache supplies *only* RAR accesses where the first read was RAW (i.e., RARAW). We also consider such accesses as RAW and calculate POD for the *maximum* distance of such accesses.

<sup>13.</sup> The first accesses to an address.

POD does *not* reserve cache blocks for read miss requests (note that the read hits are due to RAW accesses where the read cache block is previously buffered by a write request). Thus, POD always estimates a smaller cache size compared to URD, while achieving the *same* hit ratio and I/O performance (for both read and write operations in a WBWO cache).

- 3) In an RO cache, POD considers the *maximum* distance of only RAR accesses in reuse distance calculation. Since the cache does *not* buffer write requests, no cache block is reserved for write operations by POD. In this case, POD results in a smaller cache size than URD, while providing the same hit ratio and I/O performance.

- 4) In a WB cache, URD and POD work similarly. Both RAR and RAW accesses are supplied by the WB cache. In this case, both URD and POD estimate the cache size based on the *maximum* distance of either RAR and RAW accesses.

#### 4.3.2 Allocating Efficient Cache Size for VMs

We now elaborate on how we allocate an efficient cache size (in both DRAM and SSD levels) for each running VM. ETICA estimates and assigns cache sizes to the VMs by using the POD metric. ETICA aims to achieve the maximum performance (in terms of hit ratio) with the minimum cost (in terms of cache size) as opposed to previous architectures which mainly aim to optimize performance with the maximum available cache sizes [6], [11]. The steps of cache size assignment by ETICA are as follows:

- 1) Periodically, ETICA calculates the POD of the running VMs for both the RO and WBWO policies used in the DRAM and SSD levels, respectively. Recall from Section 4.3.1 that POD does *not* reserve cache blocks for writes in RO and reads in WBWO caches and hence estimates different cache sizes for different write polices.

- 2) Based on the calculated POD, we estimate two efficient cache sizes for the VM in both the DRAM and the SSD levels. Eq. 2 shows how we calculate the cache sizes:

$$Cache_{DRAM} = POD_{DRAM} \times blockSize_{DRAM}$$

$$Cache_{SSD} = POD_{SSD} \times blockSize_{SSD}$$

(2)

Where  $POD_{DRAM}$  and  $POD_{SSD}$  are the calculated POD metrics of the running VM in DRAM and SSD levels and  $blockSize_{DRAM}$  and  $blockSize_{SSD}$  are the cache block size in DRAM and SSD, respectively.

- 3) We check whether the total estimated cache sizes for all VMs fit in the available physical DRAM and SSD space.

- 4) If the sum of estimated cache sizes exceeds the existing physical DRAM or SSD space, we reduce the estimated size of each VM to maximize the *Performance-Per-Cost* (PPC) factor in Eq. 3.

$$PPC = \sum_{i=1}^{numVMs} \frac{H(VM_i, c_i)}{c_i}$$

(3)

Where numVMs is the number of running VMs and  $H(VM_i, c_i)$  is the hit ratio achieved by  $VM_i$  by allocating it a cache size equal to  $c_i$ .

Since the running VMs are weighted identically, we aim to maximize the aggregate *PPC* as proposed in Eq. 3. Assigning cache sizes based on Eq. 3 guarantees the maximum overall performance with minimum cost. To do so, ETICA provides POD-based *Miss Ratio Curves* (MRCs) for each running VM and finds the set of  $\{c_0, ..., c_{N-1}\}$  which provides the maximum *PPC*.

## **5** EXPERIMENTAL RESULTS

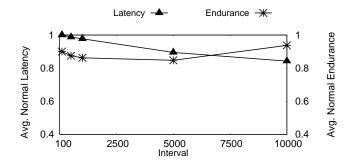

In this section, we evaluate the effectiveness of our proposed two-level I/O caching scheme, ETICA, in terms of cache size, performance, and endurance.

## 5.1 Experimental Setup

We conduct comprehensive experiments on a real system including a 4U rack mount SuperMicro server with 1) 6x Seagate 4TB SAS 7.2K HDDs in RAID5 (5+1) configuration at the disk subsystem level, 2) 4x Samsung 2TB 863a SATA SSDs configured as RAID10 (2+2) at the SSD cache level, 3) 128GB Samsung DDR4 DRAM where 100GB is used at the DRAM cache level, 4) LSI9361i PCIe RAID controller to apply the RAID configuration, 5) 32x Intel(R) Xeon (R) 2.1GHz CPU cores, and 6) a SuperMicro X10i motherboard. We integrated ETICA with QEMU as the open-source hypervisor running on the CentOS7 operating system (kernel version: 3.10.327.36.3).<sup>14</sup> We implement POD by modifying the source code of PARDA [76].

We run VMs with the CentOS and Ubuntu operating systems on the hypervisor. Each VM is configured with 1) 50GB disk space, 2) 1GB memory, and 3) two virtual CPUs. ETICA estimates and allocates the I/O cache size for each VM based on the I/O patterns of workloads running on the VMs. We run MSR traces from SNIA [54], [55] in the device layer, including more than ten real application workloads with different I/O characteristics, such as hm\_1 (hardware monitoring), mds\_0 (media server), mds\_1, src2\_0 (source control), src1\_2, stg\_1 (web staging), ts\_0 (terminal server), wdev\_0 (test web server), web\_3 (web/SQL server), rsrch\_0 (research projects), usr\_0 (user home directories), and proj\_0 (project directories). To show the effectiveness of ETICA, we compare it with the latest state-of-the-art I/O caching scheme in virtualized platforms, ECI-Cache [6]. To do so, we implemented this scheme in our real testing platform and evaluated it with the same experiments. The evaluation of ECI-Cache and ETICA are performed via the default configuration of the device layer with enabled *request merge* option for a 128-entry device queue size and disabled buffer cache.<sup>15</sup>

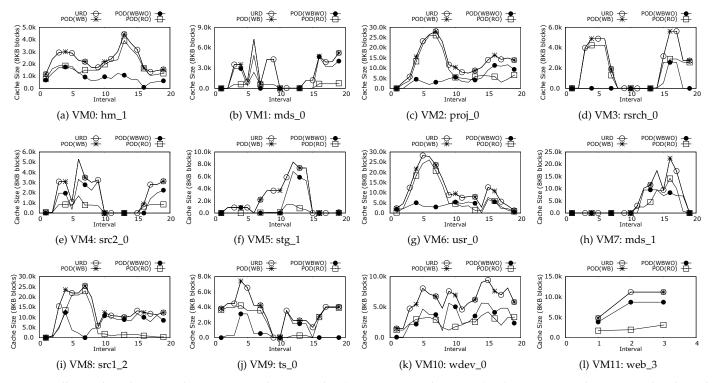

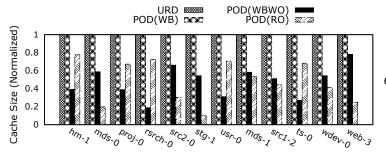

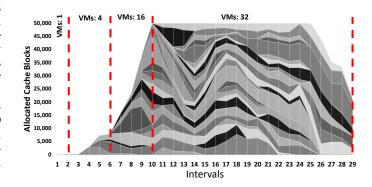

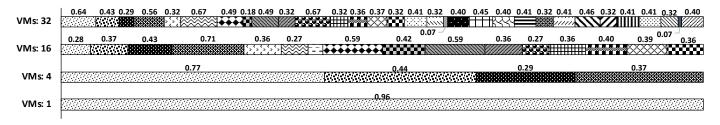

#### 5.2 Cache Size Improvement

In this section, we empirically show that ETICA reduces the allocated cache space to each VM. Our experiments show how ETICA estimates a smaller cache size compared to the previous state-of-the-art cache space partitioning scheme, ECI-Cache, while preserving the performance (i.e., latency) of the running VMs (Section 5.3). ETICA employs the POD metric in cache size estimation, which effectively allocates smaller cache sizes to the VMs by taking into account both request *type* and *cache write policy* (as we showed in Section 4.3.1). The state-of-the-art scheme, ECI-Cache, works based on URD; we have shown that this metric ignores the impact of cache write policy and only considers the request type in reuse distance estimation and thus overestimates the cache size of the VMs with RO and WBWO policies (see Section 4.3.1). We run 12 VMs with different types of workloads on the hypervisor and measure the cache size estimation of ETICA and ECI-Cache. To do so, we set different cache write policies to the VMs: 1) WB, 2) WBWO, and 3) RO. We estimate the cache size of the VMs in predefined intervals (after observing 10,000 I/O

<sup>14.</sup> We disable the buffer cache and set the configuration of the block layer to the default mode with *merge* option enabled with a 128-entry device queue size.

<sup>15.</sup> Note that ETICA and ECI-Cache has no management on the buffer cache and they only perform in the device layer.

requests) by POD and URD which are used by ETICA and ECI-Cache, respectively.