## LEVERAGING GPU BATCHING FOR SCALABLE NONLINEAR PROGRAMMING THROUGH MASSIVE LAGRANGIAN DECOMPOSITION\*

## YOUNGDAE KIM<sup>†</sup>, FRANÇOIS PACAUD<sup>†</sup>, KIBAEK KIM<sup>†</sup>, AND MIHAI ANITESCU<sup>†</sup>

**Abstract.** We present the implementation of a trust-region Newton algorithm EXATRON for bound-constrained nonlinear programming problems, fully running on multiple GPUs. Without data transfers between CPU and GPU, our implementation has achieved the elimination of a major performance bottleneck under a memory-bound situation, particularly when solving many small problems in batch. We discuss the design principles and implementation details for our kernel function and core operations. Different design choices are justified by numerical experiments. By using the application of distributed control of alternating current optimal power flow, where a large problem is decomposed into many smaller nonlinear programs using a Lagrangian approach, we demonstrate computational performance of EXATRON on the Summit supercomputer at Oak Ridge National Laboratory. Our numerical results show the linear scaling with respect to the batch size and the number of GPUs and more than 35 times speedup on 6 GPUs than on 40 CPUs available on a single node.

Key words. GPU optimization solver, second-order optimization method, decomposition

AMS subject classifications. 65K05, 90C06, 90C30, 90-04, 90-08

1. Introduction. Batch nonlinear programming refers to computing solutions of a batch of nonlinear programming problems that can be solved in parallel. The need for batch programming stems from distributed computing, which has been widely used to tackle large-scale optimization problems by the decomposition of the large problem into many smaller subproblems. In this case, the subproblems are solved in parallel at each iteration of the algorithm. Examples of distributed computing algorithms include Lagrangian-based decomposition algorithms, for example the alternating direction method of multipliers (ADMM) [6], and value function iteration of dynamic programming [7]. Structures amenable to such decomposition are embedded in many applications in the literature including network optimization (e.g., communication networks [31], electric grids [25], and water networks [35]), as well as stochastic optimization [19, 18] and multi-period optimization [17]. In these cases, the solution time highly depends on the time to solve each batch.

While graphics processing units (GPUs) have shown great success in accelerating the computation time of some batch operations, such as mini-batch training in machine learning and batched factorization [1, 14, 20] in linear algebra, little attention has been given to accelerating batched nonlinear programming using GPUs. Many studies have focused on solving a single medium to large optimization problem and leveraged GPUs to improve the computation time of the linear algebra only. For example, GPUs have been used to accelerate the solution of linear systems arising in convex optimization algorithms [30, 36, 37] and the KKT system of an augmented

<sup>\*</sup>Submitted to the editors DATE.

**Funding:** This research was supported by the Exascale Computing Project (17-SC-20-SC), a collaborative effort of the U.S. Department of Energy Office of Science and the National Nuclear Security Administration. The material was based in part on work supported by the U.S. Department of Energy, Office of Science, under contract DE-AC02-06CH11357. This research used resources of the Oak Ridge Leadership Computing Facility at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-000R22725.

<sup>&</sup>lt;sup>†</sup>Mathematics and Computer Science Division, Argonne National Laboratory, Lemont, IL (young-dae@anl.gov, fpacaud@anl.gov, kimk@anl.gov, anitescu@mcs.anl.gov).

Lagrangian of nonlinear programming [9]. In [12], the authors have implemented some number of components of the L-BFGS-B algorithm<sup>1</sup> on GPUs, however, the algorithm does not work fully on GPUs.

All the aforementioned work takes a hybrid approach; some part requires execution on CPUs and involves data transfers between CPUs and GPUs. Limited success in terms of outperforming CPUs has been observed on selected problems with these approaches. This situation is partly due to lack of a fast large-scale sparse symmetric indefinite linear system solver<sup>2</sup> for GPUs, expensive data transfer cost, and the sequential nature of many optimization algorithms prohibiting full utilization of the parallel computation capability of GPUs. Such a linear solver is required because the system of equations (the KKT matrix) to be solved at each iteration of optimization algorithms is large, sparse, symmetric, and indefinite. In order to find a descent direction in this case, many optimization algorithms, such as Ipopt [43], perform inertia control which requires computation of the number of positive, negative, and zero eigenvalues. Recent experimental results [41] of Ipopt using a GPU-based linear solver SPRAL [11, 15] show limited success on dense problems only. In sparse cases, Ipopt with a GPU-based solver showed much slower performance than when it used CPU-based linear solvers.

In this paper we focus on batch nolninear programming using GPUs, where we have a large number (e.g., tens of thousands) of problems in the batch. In this case, we employ a massive number of threads on GPUs to their full capacity to solve as many problems as possible in parallel so that we can maximize the throughput. Although individual solve of a problem might be still slower than CPUs, a vast number of parallel computations is expected to outperform CPUs in the case of a batched solve, even CPUs with multiple cores as demonstrated in section 6.

Special attention should be given to the kernel design and its implementation according to the problem size. When the size of problems in a batch is small, the algorithm becomes memory bound, therefore, data transfers between CPU and GPU could cause a significant cost. Reducing such transfers is a key to accelerating computation time. Also, due to the scarcity of available resources on the GPU hardware, kernel design should take into account factors leading to maximizing the throughput of the computation. We discuss these factors and present our kernel design scheme in section 4.

As a GPU solver for the individual solve of a problem in a batch, we implement a novel GPU-accelerated algorithm for bound-constrained nonlinear nonconvex optimization problems of the form:

(1.1) minimize

$$f(x)$$

subject to  $l \le x \le u$ ,

where  $x \in \mathbf{R}^d$  is the optimization variable and  $l, u \in \mathbf{R}^d \cup \{-\infty, \infty\}^d$  are respectively lower and upper bounds (allowing negative and positive infinite values). Bound constraints hold componentwise, and the objective function  $f : \mathbf{R}^d \to \mathbf{R}$  is a generic nonlinear nonconvex function. Bound-constrained problems play an important role as a building block to solve problems with more general constraints such as h(x) = 0, where h is a linear or a nonlinear function.<sup>3</sup> This is achieved by reformulating the

<sup>&</sup>lt;sup>1</sup>This is a variant of the limited-memory Broyden–Fletcher–Goldfarb–Shanno (L-BFGS) for boxconstrained nonlinear optimization [45].

$<sup>^2 \</sup>rm Currently,$  Nvidia's cuSOLVER [29] library supports only a dense version of symmetric indefinite linear solver.

<sup>&</sup>lt;sup>3</sup>General inequality constraints can be formulated as equality constraints by introducing slack variables, for example,  $g(x) \le 0 \Leftrightarrow g(x) + s = 0, s \ge 0$ .

given problem into a bound-constrained form by taking an augmented Lagrangian  $L_{\rho}(x;\lambda,\rho) := f(x) + \lambda^T h(x) + \frac{\rho}{2} ||h(x)||^2$  and minimizing it with respect to x, that is,  $\min_{l \leq x \leq u} L_{\rho}(x;\lambda,\rho)$ . A sequence  $\{x^k\}$  is generated with each  $x^k$  corresponding to an approximate solution of the augmented Lagrangian problem, and under suitable assumptions [10, 26] the sequence converges to a solution of the original problem with an appropriate updating scheme for  $(\lambda^k, \rho^k)$ .

We demonstrate the computational performance of our algorithm by solving many nonlinear programming problems of (1.1) by leveraging GPU batching. We highlight that our numerical experiment cannot be performed by any existing solver. The solution of such nonlinear programming problems is required for the Lagrangianbased decomposition methods. For example, in our computational experiment, the decomposition of electric grid network results in 34,704 nonlinear programming subproblems that need to be solved multiple times in the decomposition method. Our GPU-accelerated algorithm will be used to solve the nonlinear subproblems on multiple GPUs available on the Summit supercomputer at Oak Ridge National Laboratory. In addition, we implement the algorithm in Julia for the following reasons: portability, performance, and productivity. The portability is about removing the complicated process of setting compilation flags and linking proper libraries for each platform. A great productivity can also be achieved by Julia's high-level operations (vs. low-level operations in C) while showing as fast performance as CUDA without requiring users to optimize the code [4].

Our batch nonlinear programming solver is extremely important in the new optimization algorithm paradigm that solves a large-scale optimization by various decomposition methods (e.g., [34, 44, 40]). In particular, our solver enables the scalable solution of large-scale nonlinear constrained optimization problem solely on GPUs. Recent advances on ADMM algorithms [39] enable us to have convergence guarantees even with nonconvex problems. This implies that for any given large-scale optimization problem we can decompose it into smaller subproblems via ADMM to the extent that will work well with our batch nonlinear programming solver on GPUs. Since other ADMM routines, such as consensus variable and multiplier updates, in general have a closed-form solution, they can be efficiently implemented on GPUs as well. Therefore, the entire ADMM algorithm can be implemented on GPUs. In subsection 6.1, we present such an ADMM example.

The contributions of this work can be summarized as follows:

- We develop the first bound-constrained nonlinear optimization solver, implemented fully on GPU without data transfer to or from CPU.

- The optimization solver, as well as the ADMM used for our experiment, has been implemented in Julia, which is portable to supercomputers such as Summit at Oak Ridge National Laboratory.

- We have investigated and profiled multiple GPU-centric design decisions, which we report in detail in section 4. Using the optimal choices for each algorithmic unit has allowed us to obtain a superior overall performance.

- By applying our approach to a distributed control of large-scale electric grid operations, we demonstrate that the solution time is significantly reduced by a factor of 9–35 on 6 GPUs (vs. 40 CPU cores) on Summit.

- We demonstrated the multi-GPU implementation by using direct GPU-GPU communication.

2. Background on GPU architecture. This section presents background on the GPU architecture with a focus mainly on the concepts and terminologies relevant

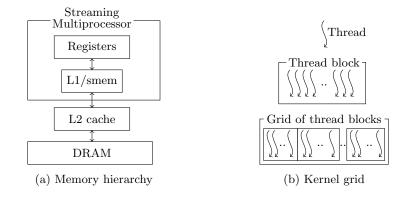

Fig. 1: Memory hierarchy and kernel grid of GPUs.

to understanding this paper. Note that the concepts described here are generic but use the terminologies for Nvidia's CUDA programming model [27, 28], which was used for numerical experiments of this work. For other architectures and programming models, we refer to [2, 16].

For GPU memory architectures, each device has its own memory hardware that is separate from the host (CPU) memory. Therefore, data transfers are needed when we want to copy data from the host to the device and vice versa. Similar to the CPU memory system, the GPU memory is hierarchical, based on data access speed, as illustrated in Figure 1(a). Basically, the higher the units are in the hierarchy, the faster they are for read and write operations. Registers are the fastest for read and write, L1 cache and shared memory are the next, and so on. We note that the L1 cache and shared memory (smem) share the same memory unit, and that we can determine how much space we allocate for each of them.

State-of-the-art GPU programming models (such as Nvidia CUDA, OpenCL, and oneAPI) implement the execution model based on single instruction, multiple threads (SIMT) that executes single instruction on multiple threads in lockstep. A kernel function is a small program that is used to execute instructions on GPUs. Once the kernel function is launched, the execution environment creates a grid of thread blocks, each of which consists of the same number of threads, as depicted in Figure 1(b).

Each GPU architecture consists of multiple streaming multiprocessors (SMs), each of which contains scheduler and cores for computation and registers and L1 cache/shared memory for storage. In particular, a SM schedules the execution of the instruction into warps, each of which typically consists of a set of 32 threads. The L1 cache and shared memory are shared by all the threads inside the same thread block to help them communicate with each other, whereas registers are allocated for each thread. Since these computational and storage resources on each SM are scarce, the number of thread blocks that can run in parallel on each SM is restricted depending on how many resources each thread block requires.

**3.** Overview of the ExaTron algorithm. In this section we describe a variant of the trust-region Newton algorithm TRON for bound-constrained, nonlinear non-convex optimization problems [23]. Our algorithmic variant EXATRON implements the complete Cholesky factorization for preconditioning, as opposed to the incomplete

Algorithm 3.1 EXATRON's algorithm [23]

**Require:**  $x^0, [l, u], \delta > 0$ , and functions to evaluate  $f, \nabla f$ , and  $\nabla^2 f$ .

**Ensure:**  $x^*$  a solution to (1.1).

- 1: Set  $k \leftarrow 0$  and check convergence at  $x^k$ .

- 2: while not converged do

- 3:

- Evaluate  $f(x^k)$ ,  $\nabla f(x^k)$ , and  $\nabla^2 f(x^k)$ . Compute a Cauchy point:  $x_c^k \leftarrow P_{[l,u]}[x^k \alpha_k \nabla f(x^k)]$ . 4:

- Identify a subspace  $\mathcal{F}$  to optimize:  $\mathcal{F} \leftarrow \{i : l_i < (x_c^k)_i < u_i\}$ 5:

- Optimize over the subspace using a preconditioned conjugate gradient method 6: with  $A = \nabla^2 f(x^k)_{\mathcal{F},\mathcal{F}}$ :

- Compute a preconditioner L such that  $A + \alpha I = LL^T$  for some  $\alpha > 0$ . 7:

- Solve  $\hat{A}s = \hat{b}$  satisfying  $||s|| \leq \delta$  using the conjugate gradient method where 8:  $\hat{A} = L^{-1}AL^{-T}$  and  $\hat{b} = L^{-1}\nabla f(x^k)_{\mathcal{F}}$ .

- Set  $w \leftarrow L^T \backslash s$ . 9:

- Perform a projected line search:  $x^{k+1} \leftarrow P_{[l,u]}[x^k + \beta_k w].$ 10:

- Set  $k \leftarrow k+1$  and check convergence at  $x^k$ . 11:

- 12: end while

- 13: return  $x^* \leftarrow x^k$ .

factorization in the original algorithm [23], which is further discussed in subsection 4.3. Moreover, we present the core operations relevant to its implementation on GPUs.

Algorithm 3.1 summarizes the algorithmic steps of EXATRON. It is an iterative Newton-based algorithm that requires evaluating the values of the objective function, its gradient, and Hessian at the current point at each iteration (in line 3). These values are used to formulate a second-order Taylor approximation of the given model at the current point  $x^k$ ,  $f(x) \approx \tilde{f}(x) := f(x_k) + \nabla f(x_k)(x - x_k) + \frac{1}{2}(x - x_k)^T \nabla^2 f(x_k)(x - x_k)$ . EXATRON then computes a Newton direction for the approximation  $\tilde{f}$  (or a descent direction following a negative curvature in the nonconvex case) within the trustregion, expecting that we may be able to reduce the actual objective function value by moving along that direction. These steps correspond to Line 3 through Line 10 of Algorithm 3.1.

EXATRON computes a Newton direction by the following four steps: (i) Cauchy point computation (Line 4); (ii) identification of a subspace to optimize (Line 5); (iii) subspace optimization using a conjugate gradient step (Line 6); and (iv) projected line search (Line 10). The Cauchy point computation step performs the gradient projection to find a point with a sufficient reduction for the approximation f in Line 4. The sufficient reduction of a Cauchy point is a key property to guarantee the global convergence of the procedure. Starting from the Cauchy point, we identify a subset of the variables to optimize further, which has been shown in [26, 23, 22] to result in a faster convergence rate (superlinear or even quadratic). The subset corresponds to the variables with their values being strictly within their bounds, denoted by  $\mathcal{F}$ in Line 5. We then optimize the variables in the subset by using the trust-region based conjugate gradient method [38]. This involves the computation of a preconditioner L [22] to accelerate the convergence of the conjugate gradient step. Convergence of the conjugate gradient step is reached when one of the following three conditions is satisfied: (i)  $|\mathcal{F}|$  number of CG iterations has been taken; (ii) the current CG direction reaches the trust-region radius; and (iii) a negative curvature is detected. We note that condition (iii) allows us to move along a descent direction even if  $\nabla^2 f(x^k)$  is

Linear algebra routines Other routines  $\texttt{axpy()}: y \leftarrow y + \alpha x \ (8,10)$ breakpt(): (4,10)  $b_i \leftarrow \begin{cases} (u_i - x_i)/w_i, w_i > 0\\ (l_i - x_i)/w_i, w_i < 0 \end{cases}$  $ccf(): A + \alpha I = LL^T$  (7)  $\texttt{copy()}: y \leftarrow x \ (4,8,10)$ dot():  $\sum_{i=1}^{n} x_i y_i$  (4,8,10) ccfs():  $A \leftarrow A + \alpha I$  (7) gpstep(): (4,10) gemv():  $y \leftarrow \alpha A x + \beta y$  (4,8,10)  $s^{k} \leftarrow P_{[l,u]}(x^{k} + \alpha_{k}w^{k}) - x^{k}$ trqsol(): (8)  $nrm2(): ||x||_2$  (4.8) scal():  $x \leftarrow \alpha x$  (4,8) trtrs():  $x \leftarrow A \setminus x$  or  $A^T \setminus x$  (8,9)  $\sigma$  satisfies  $||x^k + \sigma w^k||_2 = \delta$

Fig. 2: Core operations

not positive definite [38]. Using the direction w computed in Line 9, we perform a projected line search to find the next point with a sufficient reduction, as depicted in Line 10. The projected line search allows a rapid change of active sets, which further accelerates the convergence. Interested readers are referred to [23] for more details.

Figure 2 describes the core operations to implement Algorithm 3.1, with a mapping showing where those operations are used in it. The numbers in parentheses at the end of each operation correspond to the line numbers of Algorithm 3.1. EXATRON implements its entire algorithm on GPUs in a way that does not require data transfers between CPUs and GPUs, provided that evaluation functions are implemented on GPUs. This removes latency issues incurred by such data transfers and enables us to achieve a much faster performance than on CPUs as described in section 6.

4. Kernel design principles. This section discuss the six kernel design principles and optimization techniques that are considered for the efficient implementation of Algorithm 3.1 on GPU. The design choices made in this section are specific for a nonlinear programming problem with 32 variables or less, considering the computational experiment in section 6. Note, however, that for problems with a larger number of variables, we discuss alternative choices of each design principle.

**4.1. Single kernel vs multiple kernels.** Our choice of the kernel design in Ex-ATRON is to use a single kernel function in order to maximize the algorithm throughput. The throughput can be maximized by promptly reassigning the resources on SMs to thread blocks used for the optimization problems. Moreover, with this design choice, a batch run can be easily implemented by launching the kernel with a grid of thread blocks, whose size is equal to the number of problems in the batch. Assigning a specific thread block to each problem is logical, because the thread blocks are independently used and scheduled in the single-kernel design. However, a potential caveat of this single-kernel approach is that a large number of live registers are required for a thread block, as the registers may need to save many states in different device functions during the kernel execution.

Alternatively, multiple kernels may be employed as an alternative design choice in order to avoid the high register usage issue. However, the multi-kernel design would involve frequent memory operations to copy the current algorithm state information from one kernel to the other, exacerbating memory-bound situations. Moreover, the implementation becomes more complicated with multiple kernel functions, because we need to track down each problem's state outside of the kernel function. If the

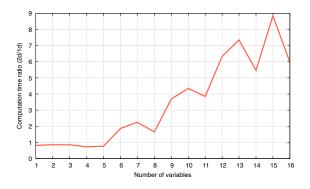

Fig. 3: Computation time ratio between the 1-dimensional and 2-dimensional thread configurations over a batch solve of 10,000 nonlinear nonconvex problems.

same kernel function was used for different problems by employing multiple thread blocks, the throughput would be significantly degraded due to the potential wait time for reassigning problems to the kernel function.

**4.2. Thread configuration.** EXATRON uses the single warp 1-dimensional thread configuration. Each thread block consists of a single warp of 32 threads with an 1-dimensional thread configuration. These threads naturally enable parallel operations on a vector of size up to 32. Since most of our operations are matrix-vector and vector-vector operations (described later in this section), such a 1-dimensional scheme fits well with our needs.

Since we perform factorization of a matrix of size  $n \times n$  in Algorithm 3.1, one might think that a 2-dimensional  $n \times n$  thread configuration may be more efficient, with each thread in charge of each element of a matrix. This configuration may be effective when we read or write the entire matrix: one line of code will do the work, such as  $B[tx, ty] \leftarrow A[tx, ty]$ , where tx and ty are thread IDs in x- and y-coordinate, respectively.

However, the number of threads required for the 2-dimensional  $n \times n$  configuration is proportional to the square of the number of variables, limiting the throughput of EXATRON on each multiprocessor significantly. As discussed in [1], for n = 16 we already need 256 threads for each thread block in this case. On the Nvidia's Volta architecture [27], this implies that we can have at most 8 active thread blocks on each multiprocessor, since a maximum of 2,048 threads is allowed per multiprocessor. Since a maximum of 32 thread blocks is allowed on each multiprocessor, the maximum throughput can be reduced by a factor of 4 with this configuration.

Another issue with the 2-dimensional  $n \times n$  configuration is that instruction efficiency is expected to be much lower than the single warp 1-dimensional configuration. Among the core operations of EXATRON (Figure 2), factorization and triangular solves are the most expensive. However, they factorize or solve a single column of size at most n at a time, which makes the remaining threads idle. Moreover, the synchronization burden increases because a thread-level synchronization should be performed to synchronize between warps instead of a lighter warp-level synchronization.

In Figure 3, we plot the computation time ratio between the 1-dimensional and 2dimensional thread configurations obtained from running EXATRON for a batch solve of 10,000 nonlinear nonconvex problems.<sup>4</sup> When a single warp was used in both cases for  $n \leq 5$ , the 2-dimensional configuration showed slightly faster computation time than did the 1-dimensional configuration. For  $n \geq 6$ , however, its computation time deteriorated sharply when it started to use more than a single warp; and it showed up to 9 times slower performance than the 1-dimensional configuration. A similar result was obtained in [1] for Cholesky, LU, and QR factorizations under the same two different thread configurations.

**4.3. Cholesky factorization.** We use the Cholesky factorization to compute a preconditioner L for a dense Hessian matrix  $A = \nabla^2 f(x)$ .<sup>5</sup> If A is positive definite, the Cholesky factorization will give us a lower triangular factor L such that  $A = LL^T$ . In this case,  $\hat{A} = L^{-1}AL^{-T}$  becomes an identity matrix, and we can find a solution to  $\hat{A}s = \hat{b}$  in just one conjugate gradient iteration.<sup>6</sup> If A is not positive definite, L is computed for a diagonally perturbed matrix  $(A + \alpha I)$  for some  $\alpha > 0$ . Such a preconditioner is expected to have eigenvalues of  $\hat{A}$  clustered so that we can find a solution in a few conjugate gradient iterations [22, 23, 26].

In contrast to the existing method [23], which implements an incomplete Cholesky factorization with sparse linear algebra, EXATRON implements a complete Cholesky factorization with dense linear algebra. The incomplete Cholesky factorization stores only a subset of the new nonzero entries generated during factorization because of storage limitation with sparse linear algebra. This may result in a less accurate preconditioner. In contrast, the complete Cholesky factorization stores all of the newly generated nonzero entries. Since we are dealing with small sparse Hessian matrices, storing them in a dense matrix does not induce any memory limitations on GPUs. Dense linear algebra computations combined with GPU's SIMT capability may be as competitive as sparse linear algebra in this case as well. By storing all the newly generated nonzero entries, we will have a more accurate preconditioner than that of the incomplete Cholesky factorization, which could potentially leads to fewer conjugate gradient iterations.

By taking advantage of a small matrix, we store its entire elements in shared memory during factorization for efficient read/write operations on GPUs. In this case, we do not have to employ a blocking algorithm that stores a block of elements at a time and factorizes it for efficient data reuse. All the elements are already available in shared memory, and read/write operations on shared memory are much faster than on global memory. Therefore, we implement an unblocked version of Cholesky factorization; we factorize one column at a time without employing level 3 BLAS operations. A similar design choice was made in [1] for a batch of Cholesky factorizations of small matrices of size  $n \leq 32$ .

To further optimize the implementation, we have experimented with two representative Cholesky factorization algorithms [14, 20]: left-looking factorization and right-looking factorization. The left-looking factorization applies all the previous updates just before a column is factorized, called lazy update, whereas the right-looking

<sup>&</sup>lt;sup>4</sup>We modified the hs45 problem from [13] to experiment with different numbers of variables. The problem is a bound-constrained nonlinear nonconvex problem with objective function  $f(x) = 120 - \prod_{i=1}^{n} x_i$  and bounds  $x_i \leq i$  for i = 1, ..., n. Hence, the optimal solution is  $x_i^* = i$ . In each batch, we generated the same 10,000 instances.

<sup>&</sup>lt;sup>5</sup>There are other methods to compute a preconditioner, such as LU factorization. However, Cholesky factorization exploits the symmetricity of the Hessian matrix, enabling two times faster computation time than LU factorization.

<sup>&</sup>lt;sup>6</sup>We note that because of the numerical limitation of finite precision of floating-point numbers we determine s is a solution to  $\hat{A}s = \hat{b}$  if  $||\hat{A}s - \hat{b}|| \leq \epsilon$  for some small error tolerance  $\epsilon > 0$ .

factorization immediately applies the updates to the trailing submatrix right after a column is factorized. A theoretical analysis in [14] shows that the left-looking algorithm has a smaller number of read/write operations than that of the right-looking algorithm, thus making it more efficient under memory-bound situations.

Table 1 shows the average computation time of the left-looking and right-looking batched Cholesky factorizations over 10,000 randomly generated matrices for  $1 \leq n \leq 32$ . As expected from the analysis, the left-looking algorithm showed a faster performance than that of the right-looking algorithm. Hence, EXATRON uses by default the left-looking Cholesky factorization algorithm to compute a preconditioner.

Table 1: Average computation time of the left- and right-looking Cholesky factorizations.

| Factorization | Time $(ms)$ |

|---------------|-------------|

| Left-looking  | 0.362       |

| Right-looking | 0.437       |

**4.4. Triangular solves.** In the conjugate gradient step, we need to perform matrix-vector multiplications between a preconditioned matrix  $\hat{A} = L^{-1}AL^{-T}$  and a vector p. This involves two triangular solves: 1)  $L^T z = p$  (backward substitution); and 2)  $Lq = \tilde{z}$  (forward substitution), where  $\tilde{z} = Az$ .

Triangular solves are inherently memory bound because they have to sequentially access one column at a time with a simple arithmetic applied to each element of it. Moreover, the number of elements to access is diminishing as we move forward or backward in both forward and backward substitutions. Hence, at most n threads are needed. In this case, we apply data parallelism as described in subsection 5.2, updating each element of a column in parallel.

Implementing the forward substitution is straightforward; however, the backward substitution involves the transpose of L, requiring a row-wise memory access with as many strides as the size of the matrix. Although we store the elements of L in shared memory, this memory access pattern could cause bank conflicts. For example, when n = 8 and the shared memory has 32 banks, a 2-way bank conflict will occur: elements in the same row with column indices differing by 4 will be stored in the same bank as they are accessed at the same time by different threads.

To avoid bank conflicts, we store the elements for both L and  $L^T$  in the same matrix. Since L is a lower triangular matrix stored in a dense matrix format, we could use its upper triangular part to store the elements of  $L^T$ . This would involve additional write operations for the subspace optimization step of Algorithm 3.1. But since the backward substitution is applied multiple times during the conjugate gradient iterations and we could avoid bank conflicts, we may obtain performance gain offsetting the cost of additional writes. A similar approach was applied in [14].

In Table 2 we present the average computation time of explicit and implicit backward substitutions over 10,000 randomly generated matrices. By explicit, we mean we save the transpose of L in its upper triangular part explicitly, whereas we perform row-wise access in the case of implicit. The results demonstrate that saving the transpose  $L^{\top}$  explicitly yields a faster computation time.

4.5. Shared-memory management. In many parts of EXATRON, memory space is needed to share data between device functions and to store and reuse in-

Table 2: Average computation time of explicit and implicit triangular solve

| Backward substitution | Time (ms) |

|-----------------------|-----------|

| Explicit              | 0.875     |

| Implicit              | 1.408     |

termediate computation results. The current iterate  $x^k$  is used by all components of EXATRON together with its lower and upper bounds. A preconditioner matrix is referred to in multiple places of EXATRON. We also need some number of vectors to store a Cauchy point and perform the conjugate gradient step.

One advantage of EXATRON's algorithm is that it does not require dynamic memory allocation during its procedure. Therefore, we can predetermine the memory space needed for its computation for a given problem size n. For efficient data access and reuse, we use shared memory for such memory space.

Table 3 presents the effect of shared memory on the computation time of EXA-TRON over the batch of 10,000 nonlinear nonconvex problems used in subsection 4.2. With shared memory, EXATRON's computation performance was about twice faster.<sup>7</sup>

Table 3: Average computation time with/without using shared memory

| Data share       | Time (ms) |

|------------------|-----------|

| Shared memory    | 9.536     |

| No shared memory | 16.293    |

Currently, the memory space allocated in shared memory for each thread block is proportional to the square of the problem size,  $O(n^2)$ . Since 96 KB of shared memory are available on recent GPU architectures, for small n our shared-memory requirement is not a limiting factor for achieving high occupancy. For medium or larger size n > 32, however, it could become a limiting factor, and a different implementation may be needed to achieve higher occupancy in that case.

4.6. Register file management. EXATRON's kernel invokes multiple device functions, and some of them are called in a nested way. This could increase the number of live registers significantly by accumulating the function calls in the nested call graph. When we compile EXATRON, the output of "ptxas -v" shows that our kernel function uses more than 100 registers. If we add another kernel on top of it (such as a kernel implementing an augmented Lagrangian algorithm), the number of registers could increase even more.

The use of a large number of registers potentially hinders achieving high occupancy. On the Volta architecture, the number of registers allowed per multiprocessor is 65,536. Assuming that each thread is using about 100 registers, the limit on the number of active thread blocks becomes  $20.^{8}$  Therefore, the theoretical occupancy we could achieve is at most 31%.

<sup>&</sup>lt;sup>7</sup>As noted on page 17 of [27], the Volta architecture significantly improved L1 data cache performance, leading to much lower latency and higher bandwidth. When we do not use shared memory, frequently used data are cached in the L1 data cache.

<sup>&</sup>lt;sup>8</sup>The number was obtained from floor(65536/(32 \* 100), 4) = 20 where we round down the result of the division to the multiple of 4, 4 being the warp allocation granularity.

To achieve higher occupancy, we need to reduce the number of registers down to where it stops improving performance. In general, there is a trade-off in restricting the number of registers. It may incur register spills to local memory, potentially slowing performance on data access. On the other hand, it could increase occupancy so that larger number of thread blocks could be executed simultaneously. We control the number of registers to use by specifying explicitly the compile option maxregs.

5. Other Implementation Details. We describe other implementation details to optimize the efficiency of the core operations on GPU. The implementation details considered in this section are independent to the problem size.

5.1. Register shuffling and warp-level synchronization. In some parts of EXATRON, we need to compute an aggregation over a vector, such as a sum or a maximum of the vector elements, and broadcast the result back to threads. For example, a two-norm or a maximum-norm of a vector needs to be computed to check the violation of a trust region,  $||x||_2 \leq \delta$ , or the convergence of the algorithm (measured by the maximum element of the projected gradient vector  $||\nabla_{[l,u]}f(x)||_{\infty} \leq \epsilon$ ). Once we compute such a value, we need to broadcast it back to threads so that each thread can proceed to the next step.

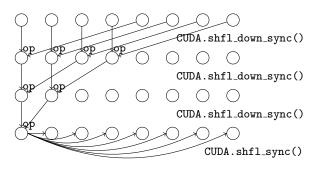

Fig. 4: Sharing values between threads in the same warp via register shuffling. op is a binary operator such as + or max.

For an efficient utilization of threads and a lightweight synchronization, we implement this type of aggregation using a register shuffling and a warp-level synchronization. The register shuffling refers to shared register values between threads in the same warp-through shuffling. For example, in order to compute  $||x||_2 = \sqrt{\sum_{i=1}^n x_i^2}$ , each thread *i* for  $i \in \{1, \ldots, n\}$  computes  $x_i^2$  first, and the values are summed up by using a register shuffling as shown in Figure 4 for n = 8. The aggregated value is stored in the first thread, and we broadcast it back to all threads in the same warp using the register shuffling again. Similarly, computing a maximum is performed by replacing the + operator with max. Register shuffling routines include a warp-level synchronization such as CUDA.sync\_warp(), which is lighter than a thread-level synchronization CUDA.sync\_threads(). Also, the use of registers avoids the use of more expensive shared memory. All of these make it efficient to compute an aggregation and share data between threads in the same warp.

**5.2. Data-level parallelism.** Data-level parallelism (DLP) refers to applying the same instruction to multiple data in parallel. Arithmetic operations such as axpy(), copy(), and scal() can benefit from DLP by affecting one thread per element

in a vector, replacing the use of a loop by a single line of code. For example, axpy() computes  $y \leftarrow y + ax$ , where x and y are vectors of the same size and a is a scalar. Without the use of DLP, we have to loop around each element of those two vectors like for i=1:n y[i] = y[i] + a\*x[i], where only a single thread works at a time. With DLP, this can be implemented as y[tid] = y[tid] + a\*x[tid], where tid is a thread ID less than or equal to n, utilizing n threads simultaneously. In a similar way, EXATRON makes use of DLP for other arithmetic operations whenever applicable.

**5.3.** Instruction-level parallelism. Within a thread, instruction-level parallelism (ILP) refers to the simultaneous execution of multiple instructions in a sequence of them that can be executed in any order. This depends on the compiler's capability to detect such independent instructions.

An example of ILP in EXATRON can occur when we form a submatrix in step ii of the procedure. We extract and copy the rows and the columns of a Hessian matrix A corresponding to the free variables. This is implemented by assigning each thread to each free variable index—applying DLP—and having it copy the rows of A corresponding to that column. There are multiple rows to copy for each thread, and these copy instructions are independent of each other, making them a target to apply ILP: for thread j taking care of the jth free column, it copies elements A[i, j]for  $i \in R(j)$ , with R(j) being the set of row indices to copy for column j, and these copy instructions can be executed in any order.

6. Computational Results. In this section we demonstrate the performance of EXATRON using a distributed control application from the power system literature. In subsection 6.1 we briefly introduce an alternating current optimal power flow (ACOPF) and its distributed-computation method based on an alternating direction method of multipliers (ADMM). Subsections 6.2 and 6.3 describe the performance of EXATRON over single and multiple GPUs, respectively. We compare the performance of the GPU implementation of EXATRON with a CPU implementation in subsection 6.4.

The implementation of EXATRON is written in Julia, and the code is available at https://github.com/exanauts/ExaTron.jl. All experiments were performed on a compute node of the Summit supercomputer at Oak Ridge National Laboratory using Julia 1.6.0 [5] and CUDA.jl 2.6.1 [4]. Note, however, that our implementation is not limited to a single node. Each compute node of the Summit supercomputer has 2 sockets of POWER9 processors having 22 physical cores each, 512 GB of DRAM, and 6 NVIDIA Tesla V100 GPUs evenly distributed to each socket [21]. We note that the MPI communication between GPUs was implemented using a CUDA-aware MPI with the asynchronous send/receive routines. For CPUs, we used the scatter/gather routines. Our different use of the MPI routines is mainly because we found scatter/gather routines between GPUs were much slower than the asynchronous send/receive. We re-emphasize that EXATRON does not require transferring data between the CPU and GPU.

**6.1. Distributed control of ACOPF.** In electrical engineering, the optimal power flow problem [42] focuses on computing the optimal dispatch of active and reactive powers among a set of generators, while satisfying physical constraints such as voltage/generator limits, power balance, and transmission line limits. The power network is modeled as a undirected graph: generators are located on certain buses of the network. The active and reactive powers produced by the generators flow between buses via the transmission lines, so as to satisfy demand at each bus. The problem

corresponds to the ACOPF problem when the power flow is modeled by using alternating current. In that case, there exists an exact formulation that encapsulates the actual physical constraints, such as Ohm's and Kirchhoff's current laws. Computing an exact and efficient solution to the ACOPF problem has a practical application, since a small percentage increase in market efficiency leads to billions of dollars of cost savings per year [8] for transmission operators.

Four representative variants of the ACOPF formulations exist: polar, rectangular, extended rectangular, and current-voltage formulations. Although their forms are different, they are equivalent between each other. In the following, we present the extended rectangular formulation using the notation in [24]:

|        | $ \min_{\substack{p_{gi}, q_{gi}, p_{ij}, q_{ij}, \\ p_{ji}, q_{ji}, w_i, w_i^R, w_{ij}^I}} \sum_{(g,i) \in \mathcal{G}} f_{gi}(p_{gi}) $ |                                            |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|        | subject to                                                                                                                                |                                            |

| (6.1a) | $\underline{p}_{gi} \le p_{gi} \le \bar{p}_{gi},$                                                                                         | $(g,i)\in \mathcal{G}$                     |

| (6.1b) | $\underline{q}_{gi} \le q_{gi} \le \bar{q}_{gi},$                                                                                         | $(g,i)\in \mathcal{G}$                     |

| (6.1c) | $\sqrt{p_{ij}^2 + q_{ij}^2} \le \bar{s}_{ij},$                                                                                            | $(i,j) \in \mathcal{L} \cup \mathcal{L}_t$ |

| (6.1d) | $(w_{ij}^R)^2 + (w_{ij}^I)^2 = w_i w_j,$                                                                                                  | $(i,j)\in\mathcal{L}$                      |

| (6.1e) | $\underline{v}_i^2 \le w_i \le \overline{v}_i^2,$                                                                                         | $i\in \mathcal{B}$                         |

| (6.1f) | $\tan(\underline{\theta}_{ij}^{\Delta})w_{ij}^{R} \le w_{ij}^{I} \le \tan(\bar{\theta}_{ij}^{\Delta})w_{ij}^{R},$                         | $(i,j)\in\mathcal{L}$                      |

| (6.1g) | $\sum_{(q,i)\in\mathcal{G}} p_{gi} - p_i^d = \sum_{j\in\mathcal{B}_i} p_{ij} + g_i^{sh} w_i,$                                             | $i\in\mathcal{B}$                          |

| (6.1h) | $\sum_{(g,i)\in\mathcal{G}} q_{gi} - q_i^d = \sum_{j\in\mathcal{B}_i} q_{ij} - b_i^{sh} w_i,$                                             | $i\in \mathcal{B}$                         |

| (6.1i) | $p_{ij} = g_{ij}^c w_i - g_{ij} w_{ij}^R + b_{ij} w_{ij}^I,$                                                                              | $(i,j)\in\mathcal{L}$                      |

| (6.1j) | $q_{ij} = b_{ij}^c w_i - b_{ij} w_{ij}^R - g_{ij} w_{ij}^I,$                                                                              | $(i,j)\in\mathcal{L}$                      |

| (6.1k) | $p_{ji} = g_{ji}^c w_j - g_{ji} w_{ij}^R - b_{ji} w_{ij}^I,$                                                                              | $(i,j) \in \mathcal{L}$                    |

(6.11)

$$q_{ji} = b_{ii}^c w_j - b_{ji} w_{ij}^R + g_{ji} w_{ij}^I, \qquad (i, j) \in \mathcal{L},$$

where  $\mathcal{G}, \mathcal{L}$ , and  $\mathcal{B}$  denote the set of generators, branches, and buses in the network, respectively. We use  $(g, i) \in \mathcal{G}$  to represent that generator g is connected to bus i. For a branch  $(i, j) \in \mathcal{L}, i$  is the "from" bus and j is the "to" bus in  $(j, i) \in \mathcal{L}_t$ . Formulation (6.1) is a *nonlinear nonconvex* optimization problem, which is known to be computationally challenging; even verifying local optimality can be an NPhard problem [32]. Hence, convergence is in general achieved at a point satisfying only second-order necessary optimality conditions [26], and we are not interested in proving global optimality.

In order to efficiently solve large-scale ACOPFs, Mhanna et al. [24] introduce a distributed control approach, where the problem is decomposed into components—generators, branches, and buses —by duplicating the variables linking different components. Then, the problem is solved by optimizing each component separately using an ADMM algorithm. One subproblem is associated with each component, resulting in a total number of subproblems equal to  $(|\mathcal{G}| + |\mathcal{L}| + |\mathcal{B}|)$ . At each ADMM iteration, the algorithm starts by solving the generator and branch subproblems in

parallel. Then, the bus subproblems are solved concurrently. Once all the subproblems are solved, the algorithm updates its Lagrange multipliers and moves to the next iteration.

One advantage of the algorithm introduced in [24] is that both the generator and the bus subproblems have a closed-form solution, so we do not have to employ a nonlinear optimization solver for them. However, the solutions of branch subproblems require to solve nonlinear nonconvex problems, each of which is formulated as (6.2) for branch  $(i, j) \in \mathcal{L}$ :

$$\begin{split} \underset{v_{i},v_{j},\theta_{i},\theta_{j}}{\text{minimize}} & \sum_{(l,m)\in\{(i,j)\cup(j,i)\}} \left( \lambda_{p_{lm}}(p_{lm}-\tilde{p}_{lm}) + \lambda_{q_{lm}}(q_{lm}-\tilde{q}_{lm}) + \frac{\rho_{p_{lm}}}{2}(p_{lm}-\tilde{p}_{lm})^{2} + \frac{\rho_{q_{lm}}}{2}(q_{lm}-\tilde{q}_{lm})^{2} \right) \\ & + \sum_{l\in\{i,j\}} \left( \lambda_{w_{l}}(v_{l}^{2}-\tilde{w}_{l}) + \lambda_{\theta_{l}}(\theta_{l}-\tilde{\theta}_{l}) + \frac{\rho_{w_{l}}}{2}(v_{l}^{2}-\tilde{w}_{l})^{2} + \frac{\rho_{\theta_{l}}}{2}(\theta_{l}-\tilde{\theta}_{l})^{2} \right) \end{split}$$

subject to

- (6.2a)  $\underline{v}_i \le v_i \le \overline{v}_i$

- (6.2b)  $\underline{v}_j \le v_j \le \overline{v}_j$

- (6.2c)  $-2\pi \le \theta_i, \theta_i \le 2\pi,$

where the definition of  $p_{ij}, q_{ij}, p_{ji}$ , and  $q_{ji}$  follows from (6.1i)–(6.1l) by plugging-in  $w_i = v_i^2, w_j = v_j^2, w_{ij}^R = v_i v_j \cos(\theta_i - \theta_j)$ , and  $w_{ij}^I = v_i v_j \sin(\theta_i - \theta_j)$ . Note that the objective of (6.2) is nonconvex.

| Table 4: | Data | statistics |

|----------|------|------------|

|----------|------|------------|

| Data        | # Generators | # Branches | # Buses    |

|-------------|--------------|------------|------------|

| 2868rte     | 600          | 3,808      | 2868       |

| 6515rte     | 1,389        | 9,037      | 6515       |

| 9241pegase  | $1,\!445$    | 16,049     | 9,241      |

| 13659pegase | 4,092        | 20,467     | $13,\!659$ |

| 19402 goc   | 971          | 34,704     | 19,402     |

We have implemented the ADMM algorithm fully on GPUs without data transfer to the CPU, and we use EXATRON to solve the branch subproblems at each ADMM iteration. The ADMM algorithm has also been written in Julia. We have experimented with our implementation in five large-scale examples from the MATPOWER [46] and PGLIB benchmark [3], where the first four of them were also used in the literature to test ADMM algorithm [24, 40]. Table 4 presents the data statistics of our test examples. We note that up to 34K nonlinear nonconvex problems are solved by EXATRON at each ADMM iteration.

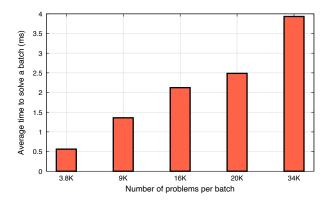

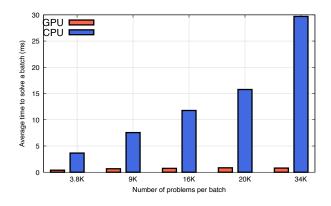

**6.2.** Performance on a single GPU. Figure 5 depicts the average solution time of EXATRON for different sizes of batches of branch subproblems listed in Table 4.

Fig. 5: Performance of EXATRON on a single GPU

The time on the y-axis is the average computation time in milliseconds taken by EXATRON to solve each batch within an ADMM iteration.

As illustrated in the figure, the performance of EXATRON generally scales linearly with respect to the batch size. This is expected since EXATRON solves the subproblems inside a batch in parallel, meaning that increasing the batch size would linearly increase its computation time as well. Moreover, all the subproblems share the same formulation (6.2), differing only by the parameter values.

We note that there are two main factors contributing to the computation time of a batch: (i) the number of subproblems per batch (i.e., batch size) and (ii) the average time for EXATRON to solve each subproblem in a batch. The latter is related to the level of difficulty of the subproblems in a batch. Although two batches are of the same size, one batch can show more computation time than the other if the subproblems in that batch are more difficult to solve than those in the other. In our case, the difficulty of batches was not significantly different from each other so EXATRON showed a linear scaling over them. However, this is not always the case, as demonstrated in subsection 6.3, where we present a load imbalance on multiple GPUs that was caused by different level of difficulties among batches.

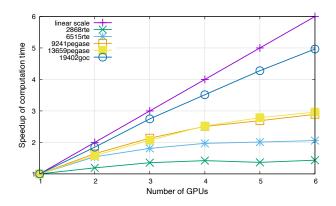

Fig. 6: Performance of EXATRON on multiple GPUs

**6.3.** Performance on multiple GPUs. We can achieve greater speedups of EXATRON by employing multiple GPUs. The GPU-aware message passing interface (MPI) with Nvidia's GPUDirect supports direct GPU-GPU communication by allowing GPUs to directly send or receive data from and to the device memories, without staging through host memory. We employ such a GPU-aware MPI to communicate between GPUs that are connected via NVLink on Summit. We note that the MPI communication can become more expensive when we start to use more than 3 GPUs, since this involves cross-socket communications. This degradation of communication time will be observed in the experiments later in this section.

Figure 6 shows the speedup of EXATRON when we parallelize the computation across different GPUs (up to the 6 GPUs available on a node in the Summit supercomputer). Branch problems are evenly dispatched among 6 MPI processes in the order of branch indices, and the speedup is computed based on the timing of the root process. At each ADMM iteration, the root process distributes variable values over multiple GPUs, solves its own batch, and gathers variable values back from other GPUs. Therefore, the timing of the root process represents the synchronous time for all the MPI processes to finish their own solves, and communicate their solutions back to the root process.

As expected, we obtained a larger speedup as we increase the number of GPUs. In the case of 19402goc, it shows almost a perfect linear scaling: we obtained 5 times faster computation time when we used 6 GPUs. In general, a larger speedup is achieved for larger test instances, because the speedup is related to the maximum number, say N, of subproblems that a single GPU can solve in parallel. Therefore, the size of a batch divided by N will determine the upper bound on the number of GPUs that we can benefit from employing them. This explains why the speedup is saturated for smaller batches, for example 2868rte and 6515rte. We also note that the slope of the changes of the speedup was slightly decreased when we used more than 3 GPUs. We think this is because of the increased communication cost for cross-socket communications.

In addition to the size of a batch, another factor contributing to the speedup is the load balance among GPUs. As we briefly discussed in subsection 6.2, the level of difficulty of problems affect the computation time of a batch. Although each GPU is assigned to a batch of the same size, the speedup may be degraded if the computational load is imbalanced in terms of the level of difficulty between GPUs. In our case, the level of difficulty of a batch is measured by its solution time on a GPU. Since the root process operates synchronously, some GPU may finish its computation much earlier than others, making it idle until all the other GPUs finish their work.

We quantify this load imbalance of our data using the metrics described in [33, 18] and present their values in Table 5. The percent imbalance of a problem instance p—where p is divided into batches on GPUs in our case—at iteration k is defined as

(6.3)

$$v_{pk} := \left(\frac{t_{pk}^{\max}}{\bar{t}_{pk}} - 1\right) \times 100\%,$$

where  $t_{pk}^{\max}$  and  $\bar{t}_{pk}$  are the maximum and mean computation times of a batch among GPUs at iteration k. We define  $\bar{\nu}_p = \max_k \nu_{pk}$ ,  $\underline{\nu}_p = \min_k \nu_{pk}$ , and  $\nu_p^m := \operatorname{mean}_k \nu_{pk}$ . Hence, a smaller  $\nu_p^m$  implies that the load is balanced better than the case with a larger  $\nu_p^m$ .

Table 5 clearly shows that the workload of 19402goc among GPUs is much better balanced than the others, providing another insight into its superior speedup. We note that the load balance of 13659pegase is worse than that of 9241pegase. This explains why 13659pegase shows a very small increase of the speedup compared to 9241pegase, although its size is about 25% larger than that of 9241pegase.

Table 5: Load imbalance metric values

| Data $(p)$  | $\overline{ u}_p$ | $\underline{\nu}_p$ | $\nu_p^m$ |

|-------------|-------------------|---------------------|-----------|

| 2868rte     | 481.58%           | 2.85%               | 46.76%    |

| 6515rte     | 480.88%           | 0.54%               | 37.02%    |

| 9241pegase  | 475.48%           | 1.40%               | 32.79%    |

| 13659pegase | 469.64%           | 5.98%               | 45.76%    |

| 19402goc    | 469.79%           | 2.14%               | 9.04%     |

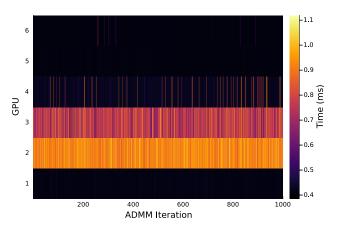

Fig. 7: Load imbalance among GPUs for 13659pegase

Figure 7 presents a verification of the load imbalance of 13659pegase problem. It depicts a heatmap where we sample 1,000 ADMM iterations for visibility and the value corresponds to the computation time in milliseconds of a batch that is assigned to each GPU. As we observe in the figure, the computation time of the second and the third GPU was almost twice more than the others throughout the iterations. An asynchronous solve combined with a load balancing scheme is our future research topic to alleviate this load imbalance issue.

**6.4.** Performance comparison: CPU vs GPU. We next compare the performance of EXATRON between a parallel CPU implementation and the GPU implementation. This experiment was run on a single Summit node with 6 GPUs and 40 CPUs. For the CPU run, we use the MPI library to implement the parallel communication between the CPU processes. Similar to the experiments for multiple GPUs in subsection 6.3, we measured the timing of the root process for CPUs that includes the cost for synchronizing distributed solves over the 40 cores.

Since EXATRON can operate in either CPU or GPU mode, the same EXATRON package was used to test the CPU implementation. We note that both modes implement the same algorithm described in Algorithm Algorithm 3.1, hence the sequence of calling their functions is identical. The only differences are in the implementation

Fig. 8: Performance comparison: 40 CPUs vs 6 GPUs on a single Summit node

of such functions—especially functions listed in Figure 2—where we follow our kernel design principles described in section 4 for the GPU implementation.

In Figure 8, the computation time of the CPU implementation shows a linear increase of with respect to the batch size. However, the average computation time increases faster than that of the GPU implementation: the computation time of EX-ATRON on 6 GPUs is about 9–35 times faster than the CPU implementation using 40 cores. Most of the speedup relates to the GPU's massive parallel computation capability.

7. Conclusion. Large-scale nonlinear programming can be tackled through Lagrangian decomposition. Such decomposition results in a batch of nonlinear programming problems to solve at each iteration of its algorithm. We have developed EXATRON for efficient batched nonlinear programming using GPUs. It implements a trust-region Newton algorithm for bound constrained nonlinear programming problems and works fully on GPUs without data transfers between CPU and GPU. This removes expensive data transfer cost which could be significant especially when the size of problems in the batch is small. We presented our design principles and implementation details for our kernel function for efficient utilization of GPUs. Experimental results over large-scale ACOPF problems decomposed into components through ADMM algorithm provided linear scaling of computation speed of EXATRON with respect to the batch size and the number of GPUs. On a single Summit node, the algorithm running on GPUs achieved more than 35 times speedup than on CPUs.

We conclude this paper by discussing several directions of future work. First of all, we plan to apply the ADMM algorithm with our GPU batch solver for solving multi-period multi-scenario optimal power flow problem. We found that only minor modifications are required to extend the current ADMM algorithm for solving the problem, while requiring more computing resources (i.e., multiple nodes and GPUs). Moreover, as we introduce more GPUs, a better design for MPI communication will be required. In particular, we have already observed that the computational load can be significantly imbalanced over multiple processes. Advanced asynchronous algorithms (e.g., [18]) will be required to alleviate the load imbalance.

REFERENCES

- A. ABDELFATTAH, A. HAIDAR, S. TOMOV, AND J. DONGARRA, <u>Batched one-sided factorizations</u> of tiny matrices using GPUs: challenges and countermeasures, J. Comput. Sci., 26 (2018), pp. 226–236, https://doi.org/10.1016/j.jocs.2018.01.005, https://doi.org/10.1016/j.jocs.2018.01.005.

- [2] AMD, ROCm Documentation, 2021, https://rocmdocs.amd.com/en/latest/index.html.

- [3] S. BABAEINEJADSAROOKOLAEE, A. BIRCHFIELD, R. D. CHRISTIE, C. COFFRIN, C. DE-MARCO, R. DIAO, M. FERRIS, S. FLISCOUNAKIS, S. GREENE, R. HUANG, ET AL., <u>The</u> <u>power grid library for benchmarking ac optimal power flow algorithms</u>, arXiv preprint arXiv:1908.02788, (2019).

- [4] T. BESARD, C. FOKET, AND B. DE SUTTER, <u>Effective extensible programming: unleashing Julia</u> on GPUs, IEEE Trans. Parallel Distrib. Syst., 30 (2019), pp. 827–841, https://doi.org/10. <u>1109/TPDS.2018.2872064</u>, https://doi.org/10.1109/TPDS.2018.2872064.

- [5] J. BEZANSON, A. EDELMAN, S. KARPINSKI, AND V. B. SHAH, Julia: a fresh approach to numerical computing, SIAM Rev., 59 (2017), pp. 65–98, https://doi.org/10.1137/ 141000671, https://doi.org/10.1137/141000671.

- [6] S. BOYD, N. PARIK, E. CHU, B. PELEATO, AND J. ECKSTEIN, <u>Distributed optimization and statistical learning via the alternating direction method of multipliers</u>, Foundations and Trends<sup>®</sup> in Machine Learning, 3 (2011), pp. 1–122, https://doi.org/10.1561/2200000016, https://doi.org/10.1561/2200000016.

- [7] Y. CAI, K. L. JUDD, G. THAIN, AND S. J. WRIGHT, <u>Solving dynamic programming problems</u> on a computational grid, Comput. Econ., 45 (2015), pp. 261–284, https://doi.org/10.1007/ s10614-014-9419-x, https://doi.org/10.1007/s10614-014-9419-x.

- [8] M. B. CAIN, R. P. O'NEILL, AND A. CASTILLO, <u>History of optimal power flow and formulations</u>, tech. report, Federal Energy Regulatory Commission, Dec. 2012, https://www.ferc.gov/ sites/default/files/2020-04/acopf-1-history-formulation-testing.pdf.

- [9] Y. CAO, A. SETH, AND C. D. LAIRD, <u>An augmented Lagrangian interior-point approach for large-scale NLP problems on graphics processing units</u>, Computers & Chemical Engineering, 85 (2016), pp. 76–83, https://doi.org/10.1016/j.compchemeng.2015.10.010, https://doi.org/10.1016/j.compchemeng.2015.10.010.

- [10] A. R. CONN, N. I. M. GOULD, AND P. L. TOINT, <u>A globally convergent augmented Lagrangian algorithm for optimization with general constraints and simple bounds, SIAM J. Numer. Anal., 28 (1991), pp. 545–572, https://doi.org/10.1137/0728030, https://doi.org/10.1137/0728030.</u>

- I. DUFF, J. HOGG, AND F. LOPEZ, <u>A new sparse ldl<sup>t</sup> solver using a posteriori threshold pivoting</u>, SIAM J. Sci. Comput., 42 (2020), pp. C23–C42, https://doi.org/10.1137/18M1225963, https://doi.org/10.1137/18M1225963.

- [12] Y. FEI, G. RONG, B. WANG, AND W. WANG, Parallel L-BFGS-B algorithm on GPU, Computers & Graphics, 40 (2014), pp. 1–9.

- [13] N. I. M. GOULD, D. ORBAN, AND P. L. TOINT, CUTEr and SifDec: a constrained and unconstrained testing environment, revisited, ACM Transactions on Mathematical Software, 29 (2003), pp. 373–394, https://doi.org/10.1145/962437.962439, https://doi.org/10. 1145/962437.962439.

- [14] A. HAIDAR, A. ABDELFATTAH, M. ZOUNON, S. TOMOV, AND J. DONGARRA, <u>A guide for achieving</u> high performance with very small matrices on GPU: a case study of batched <u>LU</u> and <u>Cholesky factorizations</u>, IEEE Trans. Parallel Distrib. Syst., 29 (2018), pp. 973–984, https: //doi.org/10.1109/TPDS.2017.2783929, https://doi.org/10.1109/TPDS.2017.2783929.

- [15] J. D. HOGG, E. OVTCHINNIKOV, AND J. A. SCOTT, <u>A sparse symmetric indefinite direct solver</u> for <u>GPU architectures</u>, ACM Trans. Math. Software, 42 (2016), https://doi.org/10.1145/ 2756548, https://doi.org/10.1145/2756548.

- [16] INTEL, Intel oneAPI Programming Guide, 2021, https://software.intel.com/content/www/us/ en/develop/documentation/oneapi-programming-guide/top.html.

- [17] K. KIM, A. BOTTERUD, AND F. QIU, Temporal decomposition for improved unit commitment in power system production cost modeling, IEEE Transactions on Power Systems, 33 (2018), pp. 5276–5287, http://ieeexplore.ieee.org/document/8316946/.

- [18] K. KIM, C. G. PETRA, AND V. M. ZAVALA, <u>An asynchronous bundle-trust-region method for dual decomposition of stochastic mixed-integer programming</u>, SIAM Journal on Optimization, 29 (2019), pp. 318–342, <u>https://doi.org/10.1137/17M1148189</u>.

- [19] K. KIM AND V. M. ZAVALA, Algorithmic innovations and software for the dual decomposition method applied to stochastic mixed-integer programs, Mathematical Programming Computation, 10 (2018), pp. 225–266.

- [20] J. KURZAK, H. ANZT, M. GATES, AND J. DONGARRA, Implementation and tuning of batched Cholesky factorization and solve for NVIDIA GPUs, IEEE Trans. Parallel Distrib. Syst.,

27 (2016), pp. 2036–2048, https://doi.org/10.1109/TPDS.2015.2481890, https://doi.org/10.1109/TPDS.2015.2481890.

- [21] O. R. N. LABORATORY, <u>Summit User Guide</u>, 2021, https://docs.olcf.ornl.gov/systems/summituser\_guide.html.

- [22] C.-J. LIN AND J. J. MORÉ, Incomplete Cholesky factorizations with limited memory, SIAM J. Sci. Comput., 21 (1999), pp. 24–45, https://doi.org/10.1137/S1064827597327334, https: //doi.org/10.1137/S1064827597327334.

- [23] C.-J. LIN AND J. J. MORÉ, <u>Newton's method for large bound-constrained optimization</u> problems, SIAM J. Optim., 9 (1999), pp. 1100–1127, https://doi.org/10.1137/ S1052623498345075, https://doi.org/10.1137/S1052623498345075.

- [24] S. MHANNA, G. VERBIČ, AND A. C. CHAPMAN, <u>Adaptive ADMM for distributed AC optimal power flow</u>, IEEE Trans. Power Syst., 34 (2019), pp. 2025–2035, https://doi.org/10.1109/ TPWRS.2018.2886344, https://doi.org/10.1109/TPWRS.2018.2886344.

- [25] D. K. MOLZAHN, F. DÖRFLER, H. SANDBERG, S. H. LOW, S. CHAKRABARTI, R. BALDICK, AND J. LAVAEI, A survey of distributed optimization and control algorithms for electric power systems, IEEE Transactions on Smart Grid, 8 (2017), pp. 2941–2962.

- [26] J. NOCEDAL AND S. J. WRIGHT, <u>Numerical optimization</u>, Springer-Verlag, New York, NY, 2nd. ed., 2006.

- [27] NVIDIA, <u>NVIDIA Tesla V100 GPU architecture</u>, Aug. 2017, https://images.nvidia.com/ content/volta-architecture/pdf/volta-architecture-whitepaper.pdf.

- [28] NVIDIA, <u>CUDA C++ Programming Guide</u>, 2021, https://docs.nvidia.com/cuda/ cuda-c-programming-guide/index.html.

- [29] NVIDIA, cusolver: the api reference guide for cusolver, a gpu accelerated library for decompositions and linear system solutions for both dense and sparse matrices., 2021, https://docs.nvidia.com/cuda/cusolver/index.html.

- [30] B. O'DONOGHUE, E. CHU, N. PARIKH, AND S. BOYD, <u>Conic optimization via operator splitting</u> and homogeneous self-dual embedding, Journal of Optimization Theory and Applications, 169 (2016), pp. 1042–1068.

- [31] D. P. PALOMAR AND M. CHIANG, <u>A tutorial on decomposition methods for network utility</u> <u>maximization</u>, IEEE Journal on Selected Areas in Communications, 24 (2006), pp. 1439– 1451.

- [32] P. M. PARDALOS AND G. SCHNITGER, <u>Checking local optimality in constrained quadratic</u> programming is NP-hard, Oper. Res. Lett., 7 (1988), pp. 33–35, https://doi.org/10.1016/ 0167-6377(88)90049-1, https://doi.org/10.1016/0167-6377(88)90049-1.

- [33] O. PEARCE, T. GAMBLIN, B. R. DE SUPINSKI, M. SCHULZ, AND N. M. AMATO, <u>Quantifying</u> the effectiveness of load balance algorithms, in Proceedings of the 26th ACM International Conference on Supercomputing, ICS '12, New York, NY, USA, 2012, Association for Computing Machinery, p. 185–194, https://doi.org/10.1145/2304576.2304601, https://doi.org/10.1145/2304576.2304601.

- [34] M. RYU AND K. KIM, <u>A privacy-preserving distributed control of optimal power flow</u>, arXiv preprint arXiv:2102.02276, (2021).

- [35] A. K. SAMPATHIRAO, P. SOPASAKIS, A. BEMPORAD, AND P. P. PATRINOS, <u>GPU-accelerated</u> stochastic predictive control of drinking water networks, IEEE Transactions on Control Systems Technology, 26 (2017), pp. 551–562.

- [36] M. SCHUBIGER, G. BANJAC, AND J. LYGEROS, <u>GPU acceleration of ADMM for large-scale quadratic programming</u>, Journal of Parallel and Distributed Computing, 144 (2020), pp. 55–67.

- [37] E. SMITH, J. GONDZIO, AND J. HALL, <u>Gpu acceleration of the matrix-free interior point</u> <u>method</u>, in Parallel Processing and Applied Mathematics, R. Wyrzykowski, J. Dongarra, <u>K. Karczewski</u>, and J. Waśniewski, eds., Berlin, Heidelberg, 2012, Springer Berlin Heidelberg, pp. 681–689, https://doi.org/10.1007/978-3-642-31464-3\_69, https://doi.org/10. 1007/978-3-642-31464-3\_69.

- [38] T. STEIHAUG, The conjugate gradient method and trust regions in large scale optimization, SIAM J. Numer. Anal., 20 (1983), pp. 626–637, https://doi.org/10.1137/0720042, https: //doi.org/10.1137/0720042.

- [39] K. SUN AND X. A. SUN, A two-level distributed algorithm for nonconvex constrained optimization, tech. report, Georgia Institute of Technology, Atlanta, GA, Aug. 2020, https://arxiv.org/abs/1902.07654.

- [40] K. SUN AND X. A. SUN, <u>A two-level ADMM algorithm for AC OPF with convergence guarantees</u>, tech. report, Georgia Institute of Technology, Atlanta, GA, Jan. 2021, <u>https://arxiv.org/ abs/2008.12139</u>.

- [41] B. TASSEFF, C. COFFRIN, A. WÄCHTER, AND C. LAIRD, Exploring benefits of linear solver

parallelism on modern nonlinear optimization applications, tech. report, Loa Alamos National Laboratory, Los Alamos, NM, Sept. 2019, https://arxiv.org/abs/1909.08104.

- [42] A. J. WOOD, B. F. WOLLENBERG, AND G. B. SHEBLÉ, Power generation, operation, and control, John Wiley and Sons, Hoboken, New Jersey, 3rd. ed., 2013.

- [43] A. WÄCHTER AND L. T. BIEGLER, On the implementation of an interior-point filter line-search algorithm for large-scale nonlinear programming, Math. Program, 106 (2006), pp. 25–57, https://doi.org/10.1007/s10107-004-0559-y, https://doi.org/10.1007/s10107-004-0559-y.

- [44] W. ZHANG, K. KIM, AND V. M. ZAVALA, On the tightness and scalability of the lagrangian dual bound for the alternating current optimal power flow problem, arXiv preprint arXiv:2104.03788, (2021).

- [45] C. ZHU, R. H. BYRD, P. LU, AND J. NOCEDAL, <u>Algorithm 778: L-BFGS-B: Fortran subroutines</u> for large-scale bound-constrained optimization, ACM Transactions on Mathematical Software (TOMS), 23 (1997), pp. 550–560.

- [46] R. D. ZIMMERMAN, C. E. MURILLO-SÁNCHEZ, AND R. J. THOMAS, <u>MATPOWER: steady-state</u> operations, planning, and analysis tools for power systems research and education, IEEE Trans. Power Syst., 26 (2011), pp. 12—19, https://doi.org/10.1109/TPWRS.2010.2051168, https://doi.org/10.1109/TPWRS.2010.2051168.

The submitted manuscript has been created by UChicago Argonne, LLC, Operator of Argonne National Laboratory ("Argonne"). Argonne, a U.S. Department of Energy Office of Science laboratory, is operated under Contract No. DE-AC02-06CH11357. The U.S. Government retains for itself, and others acting on its behalf, a paid-up nonexclusive, irrevocable worldwide license in said article to reproduce, prepare derivative works, distribute copies to the public, and perform publicly and display publicly, by or on behalf of the Government. The Department of Energy will provide public access to these results of federally sponsored research in accordance with the DOE Public Access Plan (http://energy.gov/downloads/doepublic-access-plan).