# arXiv:2110.14108v2 [quant-ph] 28 Oct 2021

# Scale, Quality, and Speed: three key attributes to measure the performance of near-term quantum computers

Andrew Wack, Hanhee Paik, Ali Javadi-Abhari, Petar Jurcevic, Ismael Faro, Jay M. Gambetta, and Blake R. Johnson

IBM Quantum, IBM T. J. Watson Research Center, Yorktown Heights, NY 10598

(Dated: January 15, 2022)

Defining the right metrics to properly represent the performance of a quantum computer is critical to both users and developers of a computing system. In this white paper, we identify three key attributes for quantum computing performance: quality, speed, and scale. Quality and scale are measured by quantum volume and number of qubits, respectively. Using an update to the quantum volume experiments, we propose a speed benchmark that allows the measurement of Circuit Layer Operations Per Second (CLOPS) and identify how both classical and quantum components play a role in improving performance. We prescribe a procedure for measuring CLOPS and use it to characterize the performance of some IBM Quantum systems.

### I. INTRODUCTION

As we build and deploy increasingly capable quantum computers, it is important to develop benchmarks that track the performance of typical user workloads. Such benchmarks not only aid in identification of the optimal quantum computing system for a particular application, but these metrics also guide performance improvements for system developers. With the ultimate goal of achieving quantum advantage — where a user can run a quantum program to find a solution faster, cheaper, or more accurately than classical computing alone — it is important to make progress along the critical factors that drive quantum computing systems toward advantage on meaningful applications. As we enter the era where quantum applications also use substantial classical processing alongside quantum resources, we must be careful to include quantum-classical interactions in the defined benchmarks. Otherwise, our metrics will not be representative of real applications.

Quantum computing performance is defined by the amount of useful work accomplished by a quantum computer per unit of time. In a quantum computer, the information processing is actualized by quantum circuits containing instructions to manipulate quantum data. Unlike classical computer systems, where instructions are executed directly by a CPU, the Quantum Processing Unit (QPU), which is the combination of the control electronics and quantum memory, is supported by a classical runtime system for converting the circuits into a form consumable by the QPU and then retrieving results for further processing. Performance on actual applications depends on the performance of the complete system, and as such any performance metric must holistically consider all of the components.

In this white paper, we propose that the performance of a quantum computer is governed by three key factors: scale, quality, and speed. *Scale*, or the number of qubits, determines the size of problem that can be encoded and solved. *Quality* determines the size of quantum circuit that can be faithfully executed. And *speed* is related to the number of primitive circuits that the quantum computing system can execute per unit of time. We introduce a benchmark for measuring speed in section III C. Before diving into the metrics, we first revisit some foundational definitions for clarity.

### **II. DEFINITIONS**

### A. Quantum Circuits and Programs

A quantum circuit is a computational routine consisting of an ordered sequence of quantum operations including gates, measurements, and resets on quantum data (qubits) and concurrent real-time classical computation [1, 2]. Data flows between the quantum operations and the real-time classical compute so that the classical compute can incorporate measurement results and the quantum operations may be conditioned upon or parameterized by data from the real-time classical compute. Here *real-time* means within the coherence time of the qubits. We exclude from the quantum circuit definition *near-time* computations occurring on time scales longer than the coherence of the quantum computation. Extended quantum circuits may be completely described by the OpenQASM 3 language [2].

A quantum program expresses a larger concept of a task or algorithm that executes or samples from multiple quantum circuits within the context of a larger classical computer program. Variational algorithms are examples of quantum programs that execute circuits within a classical optimization loop. For these workloads, system performance increases substantially with a runtime architecture that hosts the classical computation in a *near-time* context with low-latency access to quantum hardware. Quantum-classical interactions occur via the classical program requesting execution of one or more quantum circuits. The communication time for these requests plays a large role in system performance, thus we deem it essential to capture this time in defining a speed metric.

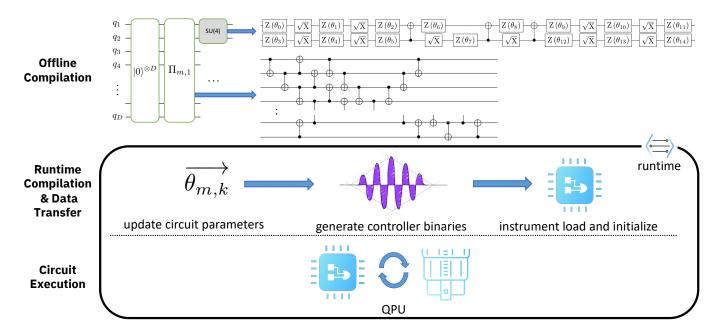

FIG. 1. Runtime architecture and phases of compilation. The circuit pattern of a Quantum Volume benchmark is shown, as well as its offline compilation. Circuit parameters in the Circuit Layer Operations per Second benchmark are updated during runtime, making the metric heavily dependent on the runtime architecture and runtime compilation.

## B. Compiling quantum programs: offline & runtime compilation

A key part of executing quantum programs is the compilation of quantum circuits that arise from them. Figure 1 shows our envisioned phases of compilation and how they interact with the runtime. Many quantum programs, such as variational ones, give rise to quantum circuits whose outlines are known, but whose parameters are runtime-dependent.

In the Quantum Volume benchmark [3] the circuit patterns are composed of layers of qubit permutation and random 2-qubit unitaries. These can be compiled and optimized to a great degree offline. Permutations capture data motion, a key requirement of large-scale quantum computing. These may be compiled to SWAP networks, CNOT networks, teleportation, shuttling instructions, etc. Random unitaries capture average circuits and how they may explore the Hilbert space. These may be compiled using a variety of methods to the target gate set [4]. The quality of the circuits will be dictated to a great extent by how well this compiler performs.

The benchmark proposed here provisions some parameters that will only be available during runtime (e.g. those that depend on previous runs). The runtime compiler is thus responsible for binding such parameters, generating new binaries, and feeding them to the control electronics of the QPU. Repeated interactions between quantum-classical compute make this critical for speed, which is what the benchmark aims to capture. We have thus designed the benchmark so as to separate these phases, and measure speed as it pertains to the interactive use of the QPU. Of course the separation is not exact: knowing the parameters or latest calibration data can help the compiler improve the circuits even more, through approximation, noise adaptivity, etc. [3, 5]. If this information is used, then it will be included in the benchmark measurement as well.

### **III. PERFORMANCE METRICS**

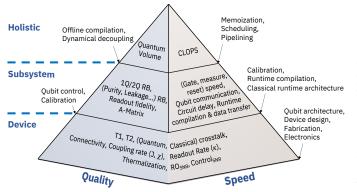

In this section we describe the three metrics in more detail. Before we begin, it is worth emphasizing that many design choices are made in building a quantum computer, all of which can affect the quality, speed, and scale. A useful way of thinking about this is a benchmarking pyramid [6], where different levels of complexity are captured at different tiers. Device level parameters provide more complexity, but do not give an accurate picture of the overall performance. Holistic benchmarks capture the many different ways that system parameters can interact and influence the overall performance, at the cost of less specificity. In Figure 2, we enhance this picture by including another face to the pyramid: speed. This figure shows some of the "ingredients" that influence quality and speed, which we capture holistically using Quantum Volume and Circuit Layer Operations Per Second metrics.

FIG. 2. Benchmarking pyramid showing how quality and speed can be benchmarked. Higher-level benchmarks capture more complexity but less specificity. There may be tradeoffs between the two faces of the pyramid.

### A. Number of qubits

The number of qubits determines the amount of information that can be encoded in a quantum computer for computation, which caps the size of solvable problems. For example, in chemistry simulations, the number of qubits sets the size of the basis set that represents each electron wavefunction in a molecule and therefore the size of the molecules that can be simulated. Since fault-tolerant computation requires very large number of qubits, scale is a key metric in the development of quantum computers. Number of qubits can also be used as a resource to improve the other two metrics of quality and speed. For example, auxiliary qubits can often be used to reduce the depth of circuits and increase their fidelity [7]. Extra qubits can also be used in multiprogramming of QPUs to increase their circuit processing speed [8].

For most quantum computing platforms, increasing the number of qubits — the scalability — relies heavily on the available materials and fabrication technologies developed from the semiconducting industry. Superconducting, semiconducting, ion traps and photonics qubit platforms all leverage 3D integration technology and multi-layer fabrication process from CMOS packaging for scalable on-chip wiring solutions, building traps and building photonic waveguides. While all quantum hardware platforms have challenges in scaling, superconducting qubits are making fast progress to scale beyond 100 qubits.

The challenge lies rather in developing key technologies that make scaling possible while maintaining quantum coherence on the processor. Technology development for quantum hardware takes a significant amount of investment and time in hard tech, and this is the reason we must continue investing and developing technologies for quantum computing hardware.

### B. Quantum volume

Quantum volume (QV) [3] indicates how faithfully a quantum circuit can be implemented in a quantum computing system. We define a QV layer as one layer of permutation among qubits and one layer of pair-wise random SU(4) 2-qubit unitary gates, as shown in Fig. 3. The QV is defined by the *width* or number of QV layers of the largest random square circuit (with width equal to the number of layers) that a quantum processor can successfully run. Note that when a QV circuit is compiled to the native gate set of a particular QPU, the circuit depth of the compiled circuit will typically be much larger than the number of QV layers as the abstract permutations and SU(4) unitaries may be each decomposed into multiple native gates. QV measurement starts with executing a square circuit of width N, and then compares the measurement results from the heavy output states (the states with probabilities higher than median of probabilities of all output states) with the ideal results from simulation. The largest N-qubit, square circuit that can run successfully to produce more than 2/3 of heavy outputs, determines the quantum volume on a quantum computing system, given by  $2^N$ .

Quantum volume is sensitive to coherence, gate fidelity, and measurement fidelity which are hardware properties of a quantum processor. Quantum volume is also influenced by connectivity and compilers which can make circuits efficient to minimize the effect of decoherence [4]. Quantum volume is a holistic metric because it cannot be improved by just improving one aspect of the system, but rather requires all parts of the system to be improved in a synergistic manner. Quantum volume has been adopted widely by research and industry, and has been reported for several ion trap and superconducting quantum computers.

### C. Circuit Layer Operations per Second Benchmark

Circuit Layer Operations per Second (CLOPS) is a measure correlated with how many OV circuits a OPU can execute per unit of time. That simple statement hides a wealth of choice about the possible circuit families and the execution context. Here, we pursue a holistic speed benchmark of a *typical* application. In order to faithfully model real-world use, we deem it essential to capture interaction time with the run-time environment that invokes the circuits. This attempts to avoid a pitfall seen in some synthetic benchmarks that characterize classical systems by their instruction clock rate without considering the effects of data transfers between CPU, cache and main memory. With more fragile quantum data we don't have the luxury to persist quantum data across multiple invocations, so data transfer plays an even more prominent role. To capture this element, we suggest to measure multiple executions of parameterized

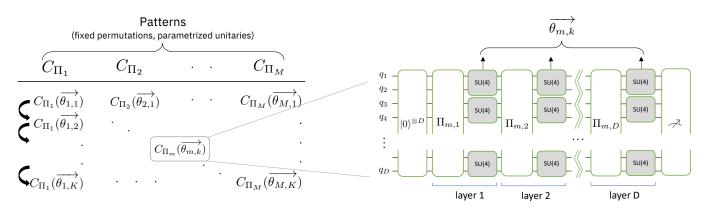

FIG. 3. Matrix of circuits used for CLOPS benchmark There are M = 100 independent templates of QV circuits, with D layers of SU(4)s, where each SU(4) in the circuit is fully parameterized. The parameters for each circuit are updated K = 10 times. The parameters  $\theta_{m,k}$  depend on the output from circuit using parameters  $\theta_{m,k-1}$

circuits where the choice of parameters is deferred until run time. This mimics the scenario found in algorithms such as the variational quantum eigensolver (VQE) or quantum kernel alignment, where the ability of a quantum system to efficiently handle parameterized circuits is key to performance of these algorithms.

Measuring execution speed of *typical* applications requires either a corpus of representative circuits or a choice of circuit family that somehow captures an "average" circuit. While acknowledging the difficulty in the latter, we argue that QV circuits are at least representative of random circuits while simultaneously allowing for a rigorous notion of quality. This last point ensures that the benchmarked circuits operate in a regime where the QPU is producing meaningful results. A natural extension of the metric proposed here would consider speed for a variety of other circuit families [9].

We formally define CLOPS as the number QV layers executed per second using a set of parameterized QV circuits, where each QV circuit has  $D = \log_2 \text{QV}$  layers. Circuit execution time includes updating parameters to the circuit, submitting the job to the QPU, executing on the QPU and sending results back to be processed. CLOPS is then calculated as the total number of QV layers executed divided by the total execution time.

The CLOPS benchmark consists of 100 parameterized template circuits (denoted  $C_{\Pi_m}$  for  $0 \le m < 100$ ) of the same type as the model circuits used when measuring the quantum volume of the system except that each of the SU(4) random unitaries are left fully parameterized. In other words, we choose and fix the random permutation layers in 100 QV circuits while leaving the SU(4)s on adjacent qubit pairs parameterized. Each circuit template  $C_{\Pi_m}$  will be executed 10 times with 10 choices of random parameters ( $\overrightarrow{\theta_{m,k}}, 0 \le m < 100, 0 \le k < 10$ ). These parameters are applied to the circuit template to generate the final circuit that is then run on the system without any further parameter updates. Each of these instantiated circuits are denoted as  $C_{\Pi_m}(\overrightarrow{\theta_{m,k}})$ . See figure **3**. Each of these circuits is executed with 100 shots, which is an attempt to balance the benchmark between just measuring setup time for execution against the number of shots typically required to estimate an observable with reasonable variance from the output. The benchmark procedure is as follows:

- 1. The 100 parameterized circuits,  $C_{\Pi_m}$ , are generated and may be compiled to a parameterized circuit in the target machine's native gate set

- 2. Time is started

- 3. The parameters for the initial circuits  $\overrightarrow{\theta_{m,0}}$  are generated using a suitable pseudo-random number generator (PRNG), and used to run circuits  $C_{\Pi_m}(\overrightarrow{\theta_{m,0}})$

- 4. For  $C_{\Pi_m}(\overrightarrow{\theta_{m,k}})$  where k > 0 the output of  $C_{\Pi_m}(\overrightarrow{\theta_{m,k-1}})$  is used to seed the PRNG to generate parameters  $\overrightarrow{\theta_{m,k}}$ . Thus circuit  $C_{\Pi_m}(\overrightarrow{\theta_{m,k}})$  may not run until  $C_{\Pi_m}(\overrightarrow{\theta_{m,k-1}})$  has completed and returned its results.

- 5. Circuits are executed using 100 shots and the same qubits, gate length, inter-circuit delays, etc. that were used when establishing the QV of the device

- 6. Outside of the constraints listed in item 4 and 5, circuits may be executed in any order or combination that makes the best use of the system resources while not changing the QV quality.

- 7. When all circuits have been run and results received, time is stopped.

| Device        | Qubits | QV | Layers | Shots | CLOPS |

|---------------|--------|----|--------|-------|-------|

| ibmq_bogota   | 5      | 32 | 5      | 100   | 1419  |

| ibmq_toronto  | 27     | 32 | 5      | 100   | 951   |

| ibmq_brooklyn | 65     | 32 | 5      | 100   | 753   |

CLOPS can then be calculated as:

$$\frac{M \times K \times S \times D}{\text{time\_taken}}$$

where:

M = number of templates = 100 K = number of parameter updates = 10 S = number of shots = 100 D = number of QV layers = log<sub>2</sub> QV

The CLOPS benchmark is designed to allow the system to leverage all of the quantum resources on a device to run a collection of circuits as fast as possible, as well as stress all parts of the execution pipeline. This includes data transfer of circuits and results, run-time compilation (lowering basis-gate level circuits to control electronics instructions), latencies in loading control electronics, initialization of control electronics, gate times, measurement times, reset time of qubits, delays between circuits, processing results as well as parameterized updates. The generation of random parameters from a seed constructed from the shots of the previous execution simulates the parameter updates in iterative quantum algorithms.

Including all of these parameters in the benchmark ensures that all aspects of the system are included to generate a meaningful comparison between systems. Physical qubit architectures may effect the repetition time, gate times, reset times, and measurement times and can vary significantly across technologies. For example, the repetition rate and the gate rate of superconducting qubits [1] can be orders of magnitude faster than the ones of ion trap qubits [10] which significantly impacts the CLOPS. Similarly, software components such as run-time compilation, orchestration of the control electronics, etc. are all aspects that are necessary in current architectures to run already "compiled" programs for the QPU and have considerable impact on overall performance. Finally the CLOPS is also impacted by how efficiently circuits can be delivered to the system for execution and results returned to the user-space application.

### IV. MEASUREMENT OF PERFORMANCE METRICS OF IBM QUANTUM COMPUTING SYSTEMS

We have run the CLOPS benchmark on several of our systems. We chose systems that had the same quantum volume, but varied in size to highlight the current differences in their performance. The results are shown in figure 4. The systems range in size from 5 to 65 qubits, each with quantum volume 32. By choosing machines with the same QV, the characteristics of the benchmark were the same for each machine (e.g. size of circuits, typical gate depth in the native gate set, etc). Additional each of these machines have the same *rep\_delay* (delay between shots) of 250 microseconds. Despite all of these similarities, we see differences in performance, with the largest machine performing the slowest, at a CLOPS of 753 layers per second, compared to 1419 for the 5 qubit device. Given the similarities we might expect that the numbers to be nearly identical, but the benchmark reveals real world differences in performance that the user experiences.

To better understand those differences, we have broken down the time to execute the benchmark on each device into five areas:

- 1. Time actually spent running the circuit on the device: *circuit execution*

- 2. Delay time between each shot of each circuit on the device: *circuit delay*

- 3. Time spent on preparing the circuits to actually run on device (parameter upddates, run-time compilation, waveform generation) as well as data transfers (circuit submission to the backend, instrument initialization, instrument load, return of results to user) : run-time compilation and data transfer

The time breakdowns for each device are shown in figure 5. This breakdown highlights the need for a holistic benchmark of speed as we can see from the time to execute the circuits themselves, the machine that would appear to be fastest, *ibmq\_brooklyn* is in fact the slowest. This is because other factors dominate, *circuit delay* being one order of magnitude larger than gate time, and most notably *run-time compilation and data transfer* which two orders of magnitude larger, limiting the overall utilization. This shows the clear value of the benchmark to allow us to find the real barriers to improved speed.

The first of these large consumers, *circuit delay*, represents the idle time between circuits on the device, and we can see that this is the same for all of the benchmarked systems, which is expected as the default delay is the same on all systems and we ran the same number of circuits and shots. While today this does not dominate the benchmark, as we drive down the *run-time compilation*

|               |       | Time breakdown |         |                        |  |  |

|---------------|-------|----------------|---------|------------------------|--|--|

|               | Total | Circuit        | Circuit | Run-time compilation & |  |  |

| Device        | time  | execution      | delay   | data transfer          |  |  |

| ibmq_bogota   | 352.2 | 2.5            | 25.0    | 324.7                  |  |  |

| ibmq_toronto  | 525.7 | 2.4            | 25.0    | 498.4                  |  |  |

| ibmq_brooklyn | 663.6 | 2.0            | 25.0    | 636.6                  |  |  |

FIG. 5. CLOPS time breakdown All times are in seconds

and data transfer it will have a considerable effect on the CLOPS. Also for applications that require larger shot counts, this factor becomes more dominant as the rest of the overheads do not scale with shot count. Because of these factors, reducing this delay time is a constant area of research, and as quantum devices improve we expect that this delay time can be dramatically shortened.

The second area, run-time compilation and data transfer, shows effects of increasing time with machine size. This happens for several reasons. The first is that the larger machines require larger complexes of control electronics to send signals to the device, and this requires more time to initialize and load. As we move forward, changes in our software stack will improve these characteristics, reducing initialization effort as well as amount of data needed to be loaded. The second piece is the time to compile the circuits into the instructions needed for the control electronics. As we move to OpenQASM3, we are building a new high performance compiler to do this final lowering step, which we expect to have a large impact on performance. Similarly, support for parameterized updates throughout the stack will help reduce

- A. D. Córcoles, M. Takita, K. Inoue, S. Lekuch, Z. K. Minev, J. M. Chow, and J. M. Gambetta, Phys. Rev. Lett. **127**, 100501 (2021).

- [2] A. W. Cross, A. Javadi-Abhari, T. Alexander, N. de Beaudrap, L. S. Bishop, S. Heidel, C. A. Ryan, J. Smolin, J. M. Gambetta, and B. R. Johnson, "Openqasm 3: A broader and deeper quantum assembly language," (2021), arXiv:2104.14722 [quant-ph].

- [3] A. W. Cross, L. S. Bishop, S. Sheldon, P. D. Nation, and J. M. Gambetta, Phys. Rev. A 100, 032328 (2019).

- [4] P. Jurcevic, A. Javadi-Abhari, L. S. Bishop, I. Lauer, D. F. Bogorin, M. Brink, L. Capelluto, O. Günlük, T. Itoko, N. Kanazawa, A. Kandala, G. A. Keefe, K. Krsulich, W. Landers, E. P. Lewandowski, D. T. McClure, G. Nannicini, A. Narasgond, H. M. Nayfeh, E. Pritchett, M. B. Rothwell, S. Srinivasan, N. Sundaresan, C. Wang, K. X. Wei, C. J. Wood, J.-B. Yau, E. J. Zhang, O. E. Dial, J. M. Chow, and J. M. Gambetta, "Demonstration of quantum volume 64 on a superconducting quantum computing system," (2020), arXiv:2008.08571 [quant-ph].

[5] P. Murali, D. C. McKay, M. Martonosi, and A. Javadi-

- [5] P. Murali, D. C. McKay, M. Martonosi, and A. Javadi-Abhari, in Proceedings of the Twenty-Fifth International Conference on Architectural Support for Programming Languages and Operating Systems (2020) pp. 1001–1016.

- [6] D. McKay and S. Merkel, Private communication (2021).

the run-time compilation requirements as well as reducing amount of data that needs to be moved.

### V. SUMMARY

Performance benchmarks have always been difficult to properly engineer for classical computer systems, and quantum systems add both result quality and interaction with classical systems into the equation. We have shown that low level, single dimension benchmarks do not properly express the performance that user's see from the system. Instead it is necessary to create holistic benchmarks that capture all of the components that will translate to performance on real world applications but not be overly cumbersome to execute. We have defined a CLOPS benchmark that captures many of the necessary aspects for running user applications with good performance, and provided examples of using the benchmark to find current bottlenecks in the system.

- [7] P. Høyer and R. Špalek, Theory of computing 1, 81 (2005).

- [8] P. Das, S. S. Tannu, P. J. Nair, and M. Qureshi, in Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture (2019) pp. 291–303.

- [9] T. Lubinski, S. Johri, P. Varosy, J. Coleman, L. Zhao, J. Necaise, C. H. Baldwin, K. Mayer, and T. Proctor, "Application-oriented performance benchmarks for quantum computing," (2021), arXiv:2110.03137 [quant-ph].

- [10] J. M. Pino, J. M. Dreiling, C. Figgatt, J. P. Gaebler, S. A. Moses, M. S. Allman, C. H. Baldwin, M. Foss-Feig, D. Hayes, K. Mayer, C. Ryan-Anderson, and B. Neyenhuis, Nature **592**, 209 (2021).

### VI. APPENDIX: DEPTH-1 CIRCUIT PERFORMANCE

While the QV layers provide a means to compare across different quantum computer architectures, it is also useful to explore the speed of particular systems relative to their own basis gate set. We can do this with some simple additional instrumentation on the CLOPS benchmark. This provides a means to extrapolate from the CLOPS results to how it might affect other algorithms when run on the same system. We first define how to measure circuit depth in this context and then show some results for our systems.

### A. Circuit depth

Circuit depth is an important parameter in performance metrics. With current quantum computing systems, depth plays a key role in result quality. For speed metrics we need a consistent way to count operations performed by the QPU.

There are several considerations we need to take when calculating depth. First, there may be gates used that the machine cannot natively execute. For those gates we assume that they are decomposed into the native gate set of the machine before depth is calculated. Second, unlike classical systems, operations in algorithms on qubits are assumed to operate with full parallelism. We can think of each of the gates as occupying boxes on parallel timelines for each qubit in the circuit. Single qubit gates are boxes that span a single unit of time and act only on a single qubit. Two qubit gates result in a box that spans a single unit of time but encompasses two qubits. Since two qubit gates need to operate synchronously on both qubits, the box acts as a implicit barrier and we cannot place the box in the time sequence until both qubits are ready to execute the gate. Once we have all boxes placed, we can then look for the longest sequence of boxes across all of the qubits to determine the depth of the circuit.

Formally, the following rules are then used to calculate the depth d for each qubit in the circuit

• depth of a 1 qubit gate of non-zero duration from

the native gate set is 1

- depth of a measurement is 1

- depth of reset is 1

- depth of a 2 qubit gate from the native gate set is 1 and is preceded by an implicit barrier on the same 2 qubits and the barrier rule applies

- depth of a barrier is 0, but synchronizes the depth across all applied qubits to the current max depth of those qubits at the barrier

The depth d for circuit C with qubits  $Q_0 \ldots Q_n$  is then :

$$d(C) = max[d(Q_0), d(Q_1), \dots, d(Q_n)]$$

$$(1)$$

where  $Q_0...Q_n$  are all of the qubits in the circuit

The above definitions allows us to define a useful concept of "depth-1 circuits" as a primitive circuit. A depth-1 circuit is any circuit that can be executed across a set of qubits in a single unit of time from the depth definition above. This allows us to talk about any circuit of depth d as an ordered sequence of d depth-1 circuits, and the performance of a quantum computing system in terms of its speed of execution of these depth-1 circuits.

### B. Measurement of depth-1 circuit performance

Figure 6 Updates the CLOPS table to include the depth-1 circuits per second executed. We instrumented the CLOPS code so that when the benchmark was run, the average depth of each of the random 100 circuit templates is reported. All machines reported the same depth value at around 99, a reflection that each used a similar qubit topology to run the benchmark, a straight line of 5 qubits. From this depth value, knowing the number of circuits and shots run as well as the total time we can calculate the depth-1 circuits per second. Because all of these values are the same for these machines, this results in a linear scaling from the CLOPS values to the depth-1 circuits per second values.

|               |        | Attri |        |       |       |                            |

|---------------|--------|-------|--------|-------|-------|----------------------------|

| Device        | Qubits | QV    | Layers | Shots | CLOPS | depth-1 circ<br>per second |

| ibmq_bogota   | 5      | 32    | 5      | 100   | 1419  | 28355                      |

| ibmq_toronto  | 27     | 32    | 5      | 100   | 951   | 18837                      |

| ibmq_brooklyn | 65     | 32    | 5      | 100   | 753   | 15041                      |

$\ensuremath{\operatorname{FIG.}}$  6. CLOPS results with depth-1 circuits per second