# A RISC-V Simulator and Benchmark Suite for Designing and Evaluating Vector Architectures

CRISTÓBAL RAMÍREZ, Polytechnic University of Catalonia and Barcelona Supercomputing Center CÉSAR A. HERNÁNDEZ, National Polytechnic Institute of México and Barcelona Supercomputing Center OSCAR PALOMAR and OSMAN UNSAL, Barcelona Supercomputing Center MARCO A. RAMÍREZ, National Polytechnic Institute of México ADRIÁN CRISTAL, Polytechnic University of Catalonia and Barcelona Supercomputing Center

Vector architectures lack tools for research. Consider the gem5 simulator, which is possibly the leading platform for computer-system architecture research. Unfortunately, gem5 does not have an available distribution that includes a flexible and customizable vector architecture model. In consequence, researchers have to develop their own simulation platform to test their ideas, which consume much research time. However, once the base simulator platform is developed, another question is the following: Which applications should be tested to perform the experiments? The lack of Vectorized Benchmark Suites is another limitation. To face these problems, this work presents a set of tools for designing and evaluating vector architectures. First, the gem5 simulator was extended to support the execution of RISC-V Vector instructions by adding a parameterizable Vector Architecture model for designers to evaluate different approaches according to the target they pursue. Second, a novel Vectorized Benchmark Suite is presented: a collection composed of seven dataparallel applications from different domains that can be classified according to the modules that are stressed in the vector architecture. Finally, a study of the Vectorized Benchmark Suite executing on the gem5-based Vector Architecture model is highlighted. This suite is the first in its category that covers the different possible usage scenarios that may occur within different vector architecture designs such as embedded systems, mainly focused on short vectors, or High-Performance-Computing (HPC), usually designed for large vectors.

## $\label{eq:ccs} \mbox{CCS Concepts:} \bullet \mbox{Computing methodologies} \rightarrow \mbox{Simulation tools}; \bullet \mbox{Computer systems organization} \rightarrow \mbox{Single instruction, multiple data};$

Additional Key Words and Phrases: High-performance computer architecture, vector architectures, gem5, benchmarking, vectorization

Authors' addresses: C. Ramírez, C. A. Hernández, O. Palomar, O. Unsal, and A. Cristal, Barcelona Supercomputing Center, Carrer de Jordi Girona, 29,31, Barcelona, Spain, 08034; emails: {cristobal.ramirez, cesar.hernandez, oscar.palomar, osman.unsal, adrian.cristal}@bsc.es; M. A. Ramírez, Computer Research Center, National Polytechnic Institute of México, Av. Juan de Dios Bátiz s/n, Nueva industrial Vallejo, Gustavo A. Madero, Mexico City, Mexico, 07738; email: mars@cic.ipn.mx.

This work is licensed under a Creative Commons Attribution International 4.0 License.

© 2020 Copyright held by the owner/author(s). 1544-3566/2020/11-ART38 https://doi.org/10.1145/3422667

New article, not an extension of a conference paper.

This work is partially supported by CONACyT Mexico under Grant No. 472106 and the DRAC project, which is co-financed by the European Union Regional Development Fund within the framework of the ERDF Operational Program of Catalonia 2014-2020 with a grant of 50% of total cost eligible.

## **ACM Reference format:**

Cristóbal Ramírez, César Alejandro Hernández, Oscar Palomar, Osman Unsal, Marco Antonio Ramírez, and Adrián Cristal. 2020. A RISC-V Simulator and Benchmark Suite for Designing and Evaluating Vector Architectures. *ACM Trans. Archit. Code Optim.* 17, 4, Article 38 (November 2020), 30 pages. https://doi.org/10.1145/3422667

## **1 INTRODUCTION**

During the past four decades, the evolution of supercomputing has been very progressive. In 1997, the fastest computer in the world, the ASCI Red featuring Intel processors, had a top performance of 1.06 TeraFLOPS, while in 2020, a single Intel processor tops 1 TeraFLOPS. In fact, Exascale computing has become the new milestone for supercomputing. In the most basic sense, Exascale (1,018 floating-point operations per second) will provide the capability to perform more realistic simulation about the processes involved in precision medicine, regional climate, the unseen physics in materials discovery and design, the fundamental forces of the universe, and much more. However, to arrive at Exascale levels, architectural innovations, technology breakthroughs, and hardware and software coordination are needed. In this sense, different nations have increased their investments in HPC projects such as the European Processor Initiative (EPI) [1] in Europe, the Exascale Computing Project (ECP) in the US [2], the Post-K project in Japan [3], and the National Key R&D project in China [4], competing in what today is called "The race to Exascale."

Parallelism at multiple levels is now the driving force of computer designs where energy is one of the primary constraints. One effective way to achieve high performance and efficiency is the exploitation of data-level parallelism (DLP). In this sense, parallel architectures can deliver good performance at a lower cost. One category of parallel hardware organization is termed Single Instruction Multiple Data (SIMD) [5]. Two variants of SIMD are multimedia extensions and vector architectures [6]. Multimedia extensions allow executing a set of predefined operations over vector registers of a fixed length. In contrast, in a Vector Architecture, there is no single preferred vector length, just the Maximum Vector Length (MVL) is defined, and the application can use any vector length that does not exceed the maximum. Nowadays, most commodity CPUs implement architectures that feature SIMD instructions. Common examples for Multimedia extensions include Intel x86's MMX, SSE, AVX, AVX2 and AVX-512 [7], MIPS's MSA [8], ARM's NEON [9]; for vector architectures, the well-known vector extensions for NEC [10] and CRAY, and the new vector extensions ARM's SVE [11] and RISC-V V extension [12], which are considered part of "*the reemergence of vectors*."

Exascale systems will be strongly constrained by energy efficiency. In that sense, SIMD processing plays an important role in the development of the new Exascale systems. SIMD instruction set architectures (ISAs) are very expressive, enabling a good representation of high-level HPC algorithm semantics to be carried into the microarchitecture. Also, SIMD is potentially more energyefficient, since a single instruction can launch many data operations. Finally, and perhaps the biggest advantage of SIMD from the software perspective, is the ease-of-programmability, since the programmer continues thinking sequentially, and SIMD is close to the already familiar Single Instruction Single Data (SISD) category.

In that sense, RISC-V [13] ISA is opening new opportunities for academia and industry with the incorporation of the new vector extension. In fact, this vector extension has arrived just at the most convenient moment where the quest for extreme energy efficiency hardware has renewed interest in vector architectures. It has not been long, since RISC-V announced the first stable release of the RISC-V vector extension, and there are already several open and commercial-based products. Some examples are Ara [14] from ETH Zurich and Xuantie-910 [15] from the Chinese company

Alibaba, to name a couple. Also, in the HPC projects mentioned above, clear research examples on vector architectures can be seen. In the case of the EPI project, a design based on the new RISC-V vector extension was proposed as one of the essential points to develop power-efficient and high-throughput accelerators. In the case of the Post-K project, breaking news puts Japan at the top in the TOP500 [16] list released in June 2020. Fujitsu put into operation parts of the Fugaku supercomputer originally scheduled to start operating in 2021. Fugaku is built with the Fujitsu A64FX microprocessor based on the ARM 8.2-A architecture. This architecture adopts the Scalable Vector Extension (SVE) as an efficient way to achieve Exascale computing. Since there is no single solution to arrive at Exascale, novel ideas on vector architectures must be explored.

## 1.1 Tools for research on Vector Architectures

One of the most-used platforms for computer-system architecture research encompassing systemlevel architecture as well as processor microarchitecture is gem5 [17], which can be used to test those novel ideas on vector architectures. For Multimedia extensions, gem5 has support for the Intel's MMX and SSE (64-bit and 128-bit extensions), which are implemented as part of the core microarchitecture. However, the support for the more current extensions such as AVX2 and AVX-512 is missing. On the vector architecture side, there is full support for the ARM SVE, where the MVL allowed by the architecture is 2,048-bit (32 elements each 64-bit). However, despite the relevance of vector architectures, gem5 does not have a public distribution, which includes a vector architecture model that evaluates different implementations including short (around 512-bit), medium (around 4,096-bit), and large (16,384-bit or more) vectors combined with a flexible and customizable model that fits with the research requirements. In consequence, researchers have to limit their explorations to the MVL allowed by the current models, which decreases the possible scenarios that could allow a flexible and customizable model without MVL limitation; either, researchers have to develop their own environment to test their ideas, which is very time-consuming. In this sense, the incorporation of the new RISC-V vector extension will offer to the computer architecture community maximum freedom in the research and development of new acceleration technologies where the MVL can be chosen by the architect instead of being restricted by the architecture.

On the benchmark suites side, as novel architecture designs have appeared, the need for new benchmark suites arises. There are several suites to measure single-core performance over dataparallel applications such as Parboil [18] and Polybench [19]. Also, there are several suites focused on parallel computing on general-purpose CPU architectures such as PARSEC [20] and HPC Challenge Benchmark Suite [21], as well as others for heterogeneous computing such as Rodinia [22] and Polybench/GPU [19], covering MPI, OpenMP, OpenCL, and CUDA programming models, while SIMD Suites are very limited, such as ParVec [23]. It is well-known that many applications can benefit from vector execution achieving higher performance, higher energy efficiency, and greater resource utilization. However, the effectiveness of the hardware depends not only on the design but also on the compiler's ability to vectorize the code to be executed. As reported in Reference [6], there is a tremendous variation in how different compilers perform in vectorizing programs. Supporting auto-vectorizing large codes is currently too limiting. Relying on good performance typically relies on the programmer's effort; for example, rewriting to obtain wellstructured control flow or vectorizing the code using intrinsics. This effort is one of the principal reasons for not having many vectorized benchmark suites. Despite this, suites to evaluate the different modules that compose a Vector Architecture have received little attention from previous work on benchmark development.

The contribution of this article is to present a simulator and benchmark framework, which enables researchers to test novel ideas on vector architectures. Our gem5-based simulator baseline model corresponds to a decoupled vector architecture, and different vector micro-architecture

implementations can be evaluated, since the number of physical vector registers, MVL, number of queue entries, issue scheme, number of lanes, the latency of the functional units, latency and topology of the lanes interconnection, and number of memory ports are customizable. To help evaluate these architectures, a novel Vectorized Benchmark Suite was developed that covers the different possible scenarios that may occur within different vector architecture designs that can operate from short MVL to large MVL, taking into account the different modules that can be evaluated in a vector architecture such as the lanes, the interconnection between lanes, and the memory management.

This article is organized as follows: In Section 2, the background and some academic and industrial efforts on vector architectures is given. In Section 3, a detailed description of our vector architecture model implemented on gem5 is shown. Then, the RISC-V Vectorized Benchmark Suite is presented in Section 4, describing how the vectorized versions were implemented and showing the degree of vectorization achieved. Once both tools are detailed in Section 5, a study of the scalability for each application executed on different configurations of the gem5-based vector architecture model is highlighted. Section 6 focuses on the related work. Finally, Section 7 summarizes the key points of this work and gives some examples of next-generation ideas.

## 2 BACKGROUND

This section presents some important concepts of vector architectures, which are needed to better understand the Vector Architecture model presented in Section 3. Also, some important academic and industrial efforts on vector architectures are shown.

## 2.1 Vector Architectures

An elegant interpretation of SIMD is called a Vector Architecture, which has been closely identified with supercomputers designed by Seymour Cray. A key element of these architectures is that arithmetic/logic and load/store instructions operate on sets of vectors instead of individual data items. Moreover, instead of having, for example, 32 Arithmetic Logic Units (ALU) to perform 32 operations simultaneously, vector architectures typically pipeline the ALU to obtain a good performance at a lower cost. One of the main features of vector architectures is the Vector Register File (VRF), where each vector register can hold a large number of elements, and the maximum number of elements are represented by the MVL parameter, which can vary depending on the hardware implementation [6].

Vector architectures that include multiple parallel pipelines, also known as lanes, can produce two or more results per clock cycle. Adding multiple vector processing lanes is a popular technique that leads to an advantage in performance and scalability, as shown by Asanovíc [24]. In a multilane vector architecture, one lane operates with a register subset of the overall VRF and a data path subset of the overall vector functional units data paths, where all the lanes work fully synchronized [25]. Furthermore, multi-lane vector architectures need extra hardware to control the synchronization between lanes and also a lane-interconnection network to allow data movement between all the lanes.

Vector architectures have been traditionally applied to the supercomputing domain (Cray, NEC, IBM) in the 1970s up to the 1990s. The Cray-1 [26] introduced in 1976, was a register-based machine and the first supercomputer to successfully implement the vector processor design where arithmetic instructions operate on vector registers while separate vector load and store instructions move data between memory and vector registers. In the early '80s, Japanese manufacturers (NEC, Fujitsu, and Hitachi) entered the vector supercomputer market, introducing lines of parallel vector computers [27]. In the early '90s, there was a radical change in the computer industry. The introduction of faster microprocessors substantially changed the supercomputing market mainly

because the FLOPS/\$ is substantially lower for commodity-based supercomputers, although vector supercomputers could achieve higher FLOPS. Thus, the idea of building parallel machines based on many out-of-order microprocessors offered an attractive alternative instead of vector supercomputers [27].

In the late 1990s, there were many academic research proposals on vector architectures. Espasa [28] proposed using decoupling techniques in a vector processor by splitting the instruction stream into three different streams through a set of queues: scalar computation instructions, vector computation instructions, and memory accessing instructions (both vector and scalar), and showed that the performance of vector programs could be significantly improved. In a second study, Espasa [29] demonstrated that dynamic scheduling commonly applied to the superscalar processors such as register renaming and out-of-order execution could also be applied to the vector processors and obtain significant advantages. Applying dynamic scheduling, they reported a speedup of 1.24-1.72x for realistic memory latencies. Those academic ideas were studied by the processor manufacturers to conceive new designs. A clear example is the Cray X1 [30] launched in 2003, which is a distributed shared memory multiprocessor with a vector ISA (NV-1), capable of scaling to thousands of processors. The design features a VRF that holds 32 physical registers with an MVL of 64 elements where each element is 64-bit. The Cray X1 was the first to implement a decoupled vector micro-architecture. Decoupling between the vector memory unit and the vector execution unit facilitates the dynamic tolerance of memory latency. Moreover, decoupling between the vector and scalar execution units allows scalar execution to run ahead. The next Cray design launched in 2007 was called BlackWidow [31]. Like its predecessor, BlackWidow implements decoupling from the scalar core and improves scalar-vector synchronization primitives with a new vector ISA (NV-2). A large VRF was implemented that has 32 physical registers with an MVL of 128 elements each 64-bit wide. The design was organized as an eight-lane configuration, where each lane is associated with 16 elements of every vector register.

One modern example of a vector architecture is the SX-Aurora TSUBASA [10, 32], launched in 2018. SX-Aurora TSUBASA features eight vector cores in a single chip with a frequency of 1.6 GHz. Each vector core includes a scalar processor that provides the basic functionality as a processor (Fetch, decode, exception handling, etc.) and a decoupled Vector Processing Unit (VPU). The VPU includes renaming with 256 physical registers and Out-of-Order scheduling. The MVL is 256 elements each 64-bit wide, and it has 32 Vector Lanes with each lane featuring four pipelines (FMA0, FMA1, ALU0/FMA2, and ALU1/Store), executing up to three arithmetic operations plus one memory operation in parallel.

## 3 GEM5–VECTOR ARCHITECTURE MODEL

The gem5 simulator has been extended to model a decoupled vector architecture. The customization provided by the parameter-based model allows the designer to obtain a vector engine design capable of achieving a tradeoff between performance, energy efficiency, and area. In that sense, it is possible to simulate a design that fits with the researcher requirements. For example, a vector engine designed for HPC, by setting a design for large vectors (256 64-bit elements), composed of a renaming unit capable of supporting 64 physical registers, a vector arithmetic and a memory queue with 16 entries; these features can be set up to work with, say, eight lanes. In contrast, the vector engine can also be targeted for the embedded market segment by setting a design for short vectors (8 64-bit elements), reducing the number of available physical registers, and with only one-lane configuration. The main goal of this work is to obtain the more flexible and customizable vector engine for researchers; in that sense, several decisions were taken into account.

**Create a model based on RISC-V.** The adoption of RISC-V is a key factor for having the maximum freedom both in research and development of the new technologies, without the limitation from hardware and software ecosystems. Furthermore, the new V extension includes a key feature that is unbounded MVL size, which, in combination with a flexible and customizable model, could lead to set designs that support very long vectors.

Decoupled vector engine. A decoupled design provides several advantages. First, decoupling between the vector memory unit and the vector execution unit facilitates the dynamic tolerance of memory latency. Second, decoupling between the vector and scalar execution units allows scalar execution to run ahead. Implementing a vector engine as a pipeline tightly coupled to an aggressive out-of-order superscalar core is a typical implementation. In fact, most commodity CPUs that feature SIMD instructions work in this way. However, these designs are optimized for short vectors such as Intel's AVX-512, where the VRF size is around 2 KB (32 vector registers each 512-bit wide), and the area overhead added to the superscalar core is acceptable, without limiting the maximum frequency of the superscalar core. The case for vector engines designed for long vectors is a different story. In this case, the VRF size is around 64 KB (32 vector registers each 16,384-bit wide) or more when implementing renaming, which could lead to a big area overhead and could limit the maximum frequency of the superscalar core. Contemporary vector architectures are implemented as decoupled engines running around 1.5 GHz (e.g., Cray BlackWidow runs at 1.3 GHz, and SX-Aurora TSUBASA runs at 1.6 GHz), mainly limited by the big structures needed to hold long vectors. In contrast, superscalar cores run at higher frequencies. Furthermore, by having a decoupled design, it is possible to study different possibilities to get energy-efficient architectures. Examples include clock gating, turning off the clock of inactive modules to save energy and dynamic power; or applying dynamic voltage-frequency scaling when there are periods of low activity where there is no need to operate at the highest clock frequency and voltage.

## 3.1 Scalar Core

Different fully parameterizable CPU models are provided by gem5, such as the in-order CPU and the out-of-order CPU, which allows micro-architectural simulations. In this work, extra support to the in-order CPU pipeline was added to recognize the vector instructions and perform different tasks before sending these instructions to the vector engine. The core runs concurrently with the vector engine, so most of the scalar operations are amortized underneath vector execution. The scalar core is responsible for fetching and decoding the vector instructions and carrying it through the pipeline. Most of the vector instructions are treated as a *nop* operations in the scalar core. Furthermore, if the vector instruction has a scalar operand as a source, it must read the scoreboard to check if the source operand is ready. Then, the vector instructions continue to the next stages until they reach the commit stage, where they are sent to the vector engine. With this, the vector instruction execution will not be interrupted by any possible control hazard, such as a miss branch prediction generated by older scalar instructions.

One of the current limitations is that RISC-V is supported only in Syscall Emulation mode, which implies that interrupts, exceptions, and fault handlers are trapped and managed by the host without running a handler routine to manage the event. More detailed information about current limitations is given in Section 3.2.6. Having said the above, once the vector instruction is sent to the vector engine, it can be retired from the scalar pipeline, since any exception generated by a vector instruction, such as a page fault caused by a memory request, is trapped and managed by gem5.

## 3.2 Vector Engine

Once the vector instructions arrive at the vector engine, they are first renamed to remove the false dependencies, increasing the amount of instruction-level parallelism (ILP) that can be exploited. Then, two operations are performed in parallel. The first is to assign one entry in the reorder buffer, and the second is to allocate the instruction in a temporal queue depending on the

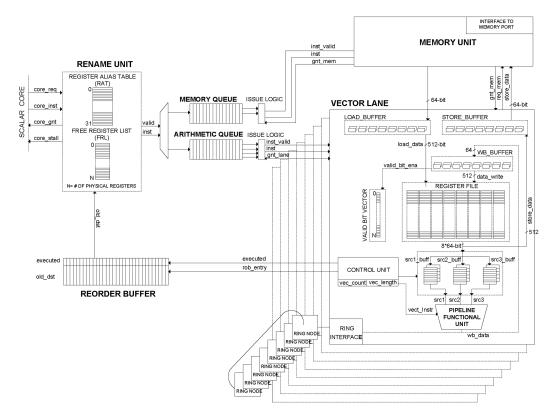

Fig. 1. gem5 Vector architecture model.

instruction type (arithmetic or memory). Once assigned in the corresponding queue, the instruction waits until it fulfills the requirements to be issued; its operands become ready, and the corresponding execution unit is available (the memory unit or the vector lane). Then, when the instruction completes execution, the commit is made by retiring the instruction and freeing up the hardware resources consumed. Our decoupled architecture design has some other unique features for efficiency. For example, as explained in Section 3.2.3, the vector lane architecture was carefully tuned to minimize pipeline bubbles due to structural hazards. The following subsections present a more detailed description of the components of the vector architecture model.

Figure 1 shows the general view of the vector engine model. Some specific configurations are also included to explain the interaction between the internal modules. The model presented corresponds to a multi-lane vector engine. By setting eight lanes, only one memory port could be enough to feed all the lanes, taking into account that the cache line size is set to 512-bit (8 elements each 64-bit), and with every cache line request it is possible to send one element to each lane in an interleaved fashion. The MVL is set to 16,384-bits (256 elements each 64-bit). The VRF line size is set to 512-bits. Also, a ring topology for lane interconnection is chosen.

3.2.1 Vector Renaming. As part of the dynamic scheduling implemented in the design register renaming is performed. The goal of the renaming is to remove false dependencies by changing the names of the source logical registers to its corresponding physical register that was mapped previously. Additionally, the logical destination register is renamed to a new physical register. This is performed by reading a structure termed as the Free Register List (FRL), which contains all the

available physical registers. This mapping is stored in another structure termed as the Register Alias Table (RAT), where the logical destination operates as the write address. At the same time, the logical sources and destination registers read the RAT to obtain the corresponding physical source registers and the physical destination register that was mapped by a previous instruction, also known as *old-destination*. Then, these structures are coupled with a dependency check logic to analyze the instruction and solve any write-after-write dependencies. The physical registers in-flight (*old-destinations*) that are no longer used are appended to the free register list at commit time. Detailed information about the commit process can be found in Section 3.2.2. Finally, the number of physical registers can be set by the designer.

3.2.2 *Reorder Buffer.* The implemented vector architecture model permits choosing the issue scheme, which can be in-order or out-of-order; for that reason, a structure to preserve the program order is needed. A Reorder Buffer (ROB) is a structure that allows instructions to be committed in-order. Also, it holds important information about the instruction that can be useful during and at the end of its execution, such as the program counter, the physical *old-destination*, and a bit field termed as *executed*. The *executed* bit allows to know if the instruction has been completed or not. The number of ROB entries can be set by the designer.

When a new instruction arrives at the ROB, it is allocated in the next available entry signaled by the tail pointer (write pointer). At the same time, the address of the assigned entry is sent together with the instruction to the corresponding queue. In that way, the instructions know their locations in the ROB, and they can write to it when it is needed.

When an instruction finalizes its execution, the *executed* bit field associated with the corresponding ROB entry is set. It means that the instruction is ready to be committed. However, since the commit is performed in-order, the instruction must wait its turn to start this process. The head pointer defines the turn (read pointer). When the instruction pointed by the head pointer has the *executed* bit set, it means that it can commit. If this is the case, the physical *old-destination* is written back to the FRL structure, to be assigned later to a new instruction. Also, the head pointer advances to the next entry to evaluate a new instruction in the next cycles.

3.2.3 Vector Issue Queues. As mentioned before, the design of the vector engine corresponds to a decoupled vector architecture, meaning that memory instructions and arithmetic instructions are buffered in different queues (Arithmetic Queue and Memory Queue) until fulfilling all the requirements to be issued. In this scheme, it is allowed to execute independent memory instructions ahead of arithmetic instructions and vice versa. This stage is called Issue, and it is in charge of dispatching instructions to the vector lanes or to the vector memory unit.

The issue stage is composed of two fundamental modules that are termed as Instruction Queue and the Issue Logic. The scheduling can be configured to use an in-order or out-of-order issue scheme. In addition, the number of entries in the issue queues also can be configured.

The instructions are issued as soon as they fulfill the requirements. First, the source operands must be ready; this is done by reading a structure called *Valid-bit* (more detailed information about the *Valid-bit* structure can be found in Section 3.2.4). Second, the hardware resources needed for execution must be available. An important restriction is that the vector lanes only support the execution of one arithmetic instruction at a time. This means that for certain arithmetic instruction, all source operands can be ready. However, the issue queue must wait until the previous instruction finishes its execution. Note that it is possible to execute memory operations at the same time.

In the special case of the memory queue, if an out-of-order issue scheme is selected, a dynamic memory disambiguation logic is enabled to check for possible memory hazards between load and stores held in the queue. Once the instruction arrives at the memory queue, the disambiguation process sets a bit called *memory hazard*. First, the load is disambiguated against all the stores in

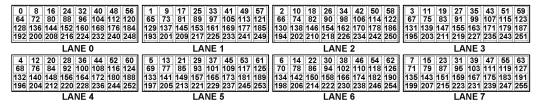

Fig. 2. VRF elements distribution for a MV=256 elements and eight-lane configuration.

the queues. In this case, for every memory reference (load/store), there is a Vector Base Address (VBA), a Vector Length (VL), a Vector Stride (VS), and Standard Element Width (SEW) in bytes. The memory range accessed by a vector reference is defined as a set of memory locations located between VBA and VBA+(VL\*VS\*SEW) -1. Then, there is a memory hazard between a vector load and vector store if their corresponding memory ranges overlap at least one byte. Scatters/gathers operations (more detailed information about gather/scatter instructions can be found in Section 3.2.5) represent a special case where characterizing by a memory range implies more complex implementations. Then, these operations are executed in order.

3.2.4 Vector Lanes. Figure 1 shows a simplified picture of the internal modules that comprise one vector lane. The vector engine can be configured with the required number of lanes. A key aspect is the VRF. In gem5, this is modeled as a simple memory, and it is possible to choose the number of read/write ports. However, the designer should take into account that in a hardware implementation, the number of ports would be highly constrained mainly in a large register file. This is because adding additional ports to an SRAM memory could lead to an increase in area and also could limit the maximum operating frequency or require more than one cycle to read/write in the VRF.

One important source of overhead is the *start-up time*, which is the latency in clock cycles until the pipeline is full [6]. The start-up time is principally determined by the pipeline latency of the vector functional unit. Moreover, the number of read ports in the VRF also can influence the *start-up time*. For example, in a vector engine designed for low power, a one read/write port SRAM memory can be used. In that sense, when a vector multiply-add operation arrives at the lane, in a first cycle, it can read the source1, in a second cycle, it can read the source2, and finally, in the third cycle, it can read the source3. All these read operations take three cycles, which are added to the start-up time. On the contrary, if a VRF with three read ports and one write port is chosen, the read of the three operands can be made in only one cycle. It is a design decision that can be taken according to the final target. For large vectors where it takes several cycles to execute an arithmetic operation, paying three cycles could be negligible. For a short vector where the full vector can be computed in less than a dozen cycles, paying three cycles in every instruction could lead to a serious loss of performance.

When multiple lanes are enabled, each lane operates with a register subset of the overall VRF. The elements of a vector register are interleaved across all the lanes. Figure 2 shows a detailed example using the same configuration presented in Figure 1 (eight-lane configuration with an MVL of 256 elements). Lane 0 is the owner of element 0, lane 1 is the owner of element 1, lane 2 is the owner of element 2, and so on.

The designer can specify the VRF line size (512-bit in the example shown in Figure 1). Then, every read operation to the register file will return a VRF line size; for that reason, it is necessary to perform operands buffering to store the elements read and to keep a constant stream of data to the functional unit, avoiding bubbles in the pipeline.

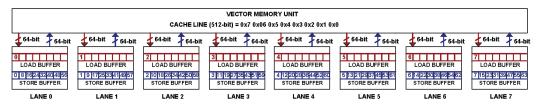

Fig. 3. Vector load/store buffer behavior.

As soon as the first result is computed, it is sent to a structure called *Write-back Buffer* (WB). This structure holds the resultant data (one 64-bit element per cycle) from the functional units. Once the WB buffer gets the total elements corresponding to one VRF line (512-bit in the example shown in Figure 1), the data can be written back in the VRF.

Each lane has a 64-bit bus to communicate with the Vector Memory Unit. When a load operation is performed, the Vector Memory Unit receives a complete cache line (512-bit in the example shown in Figure 1) and sends it in parallel to each lane (one 64-bit element). The Load Buffer (LB) is the structure in charge of collecting data from the Vector Memory Unit. Once the LB completes one VRF line (eight 64-bit elements), it proceeds to write back to the VRF. Figure 3 shows a more detailed example with the same configuration presented in Figure 1. In the vector memory unit side there is a cache line with eight 64-bit elements. Those elements are sent in interleaved fashion to each lane, meaning that Lane 0 is the owner of element 0, lane 1 is the owner of element 1, lane 2 is the owner of element 2, and so on. On the contrary, store operations read a complete line (512-bit) from the VRF and store it in the Store Buffer. This operation is performed at the same time in all lanes. Then, the store buffer sends one 64-bit element to the Vector Memory Unit each cycle.

When an instruction completes execution, the corresponding physical destination must be marked as ready to issue new instructions that were waiting for it. This is done in a structure called *Valid-Bit*, which for every physical register, one bit is added to the structure. For example, for a vector engine with 64 physical registers, a 64-bit Valid bit structure is implemented.

3.2.5 Vector Memory Unit (VMU). VMU receives instructions (load/store) from the memory queue, and it cannot accept a new instruction until it finishes its current work. This module is in charge of managing the requests to memory. The VMU supports unit-stride, strided, and indexed (gather/scatter) addressing modes. Vector unit-stride operations access elements stored contiguously in memory, starting from the effective base address. Vector strided operations access the first memory element at the effective base address and then access subsequent elements at address increments given by the byte offset specified by a scalar source. Vector-indexed operations add the contents of each element of the vector offset operand specified by the second vector source operand to the effective base address to give the effective address of each element.

Once it receives the memory instruction, as well as the memory address, the VL, and the stride (1 for unit-stride access), the VMU generates all the requested addresses and puts them in a FIFO. Then, the requests to memory are sent in-order in a pipeline fashion. However, the memory system can answer in a different order (hit under miss support). Additionally, it is possible to set the number of Miss Status and Handling Registers (MSHRs), which for a large vector implementation could be a relevant factor to consider. The MSHRs implement a queue that holds the list of outstanding memory requests. Each memory request is assigned to an MSHR object that represents a particular block of memory that has to be read or written to complete the command. When the memory request is sent, a unique order number is assigned to each read/write request as they appear on the slave port.

The memory port can be connected directly to any level of the memory hierarchy, unlike the Vector Lane where the timing is defined by the vector engine model. Once a request to the memory system is sent, the timing is managed by the gem5 memory model. There are several configurations that can be used; for example, it is possible to connect the vector memory port directly to the L1-Data cache. In another configuration, it may be possible to bypass the first level cache. It is normal that these kinds of architectures with large vector lengths are connected directly to L2 cache, since a vector memory instruction can amortize long memory latency over many elements with a small performance degradation [33].

3.2.6 Lane Interconnection. The vector extension can be configured with different numbers of lanes, where the lanes work fully synchronized. However, there is a class of instructions that involves communication between different vector lanes, basically for moving and addressing data such as vector *slides, vector reductions*, and vector *register gather* instructions. The *slide* instructions move elements up and down a vector register. The vector *reduction* instruction takes a vector register group of elements and performs a reduction using some binary operator to produce a scalar result that is written in the element 0 of a vector register. The *vector register gather* instruction reads elements from a first source vector register group at locations given by a second source vector register group and writes it in a destination vector register.

Therefore, an interconnection network is necessary to support this class of instructions. Two different interconnection networks (crossbar and ring network) are modeled. In the example shown in Figure 1, the vector lanes include a ring node (router) to communicate with the neighboring node. This interconnection could limit the performance for those applications that make intensive use of the lane interconnection, but it is cheap in terms of area. On the contrary, the crossbar interconnection could achieve an excellent performance, but it implies a considerable increase in area.

3.2.7 *Capabilities and Limitations.* Two different simulation modes are provided by gem5, Full System (FS) mode, and Syscall Emulation (SE) mode. The first provides the ability to simulate a full system. It can boot an operating system, handle interrupts, exceptions, and fault handlers. The second, the SE mode, focuses on the CPU and memory system and does not emulate the entire system. Syscalls are emulated, typically by calling the host OS. The gem5 RISC-V implementation still does not have the support to run in FS mode. Consequently, the vector architecture model is available only to run in SE mode.

Regarding the RISC-V vector extension, three versions (0.7, 0.8, 0.9) have been released so far. However, between the three different versions, the changes are small. For sure, there will be more updates before the specification is frozen as an official release, and it is believed that point is close. In that sense, this work has started to add vector extension support to gem5. However, the full specification is not implemented, leaving as future work the implementation of atomic operations, permutation operations, register grouping, and exception handling for the full system mode.

3.2.8 *Early Access.* Progress is being made on integrating the Vector Architecture model on the official gem5 repository [34]. It is possible to get an early access by cloning [35], a fork of the official gem5 repository that includes the Vector Architecture model. Note that this is a temporary repository only for early access, which will be removed as soon as the full code is hosted in the official gem5 repository.

## 4 RISC-V VECTORIZED BENCHMARK SUITE

The RISC-V Vectorized Benchmark Suite is a collection composed of seven data-parallel applications from different domains. The suite focuses on benchmarking vector micro-architectures;

| Application     | Application Domain | Algoritdmical Model  | DLP Pattern | Benchmark Suite |

|-----------------|--------------------|----------------------|-------------|-----------------|

| Blackscholes    | Financial Analysis | Dense Linear Algebra | Regular     | PARSEC/PARVEC   |

| Canneal         | Engineering        | Unstructured Grids   | Irregular   | PARSEC/PARVEC   |

| Jacobi-2D       | Engineering        | Dense Linear Algebra | Regular     | PolyBench       |

| Particle Filter | Medical Imaging    | Structured Grids     | Mix         | Rodinia         |

| Pathfinder      | Grid Traversal     | Dynamic Programming  | Regular     | Rodinia         |

| Streamcluster   | Data Mining        | Dense Linear Algebra | Mix         | PARSEC/PARVEC   |

| Swaptions       | Financial Analysis | MapReduce            | Regular     | PARSEC/PARVEC   |

Table 1. Vectorized Benchmark Suite Applications

nevertheless, it can be used as well for Multimedia microarchitectures. Applications are Vector Length Agnostic; therefore, applications can be tested using short, medium, and large VLs. The current implementation is targeting RISC-V Architectures. It can be easily ported to any SIMD ISA, thanks to a wrapper library, which is developed to map vector intrinsics and math functions to the target architecture. A study was performed of different benchmarks to select the final applications for our suite, taking into account the following criteria:

*Applications from different domains.* Although the vector architectures have been traditionally applied to the supercomputing domain, this suite does not try to explore a single application domain, as was done by several benchmark suites.

*Applications with different data-level parallelism patterns.* Having different data-level parallelism patterns helps to test different real-world scenarios. While some vector architectures can take advantage of regular data-level parallelism patterns found in the application, these architectures could poorly execute another application that presents irregular data-level parallelism pattern. This property is interesting, enabling us to expose the weaknesses of some proposals/designs.

Applications that cover most of the Vector ISA. Finding an application, which uses almost all the vector ISA operations, is difficult. This is covered by selecting applications with different instruction uses. For example, applications were considered in which most of the instructions are memory operations or applications that are compute-bound, where arithmetic operations consume most of the execution time. Furthermore, vector ISAs typically feature a certain set of unique instructions such as slide or mask operations that are not found in scalar ISAs.

The RISC-V Vectorized Benchmark Suite is available to the computer architecture community to evaluate vector architecture designs. It is openly and temporarily available at *GitHub* [36]. Like the gem5 model, the suite will be hosted in the gem5 resources repository [37].

## 4.1 Vectorized Applications

Table 1 presents general information about the seven applications selected for the Vectorized Benchmark Suite. These applications can be categorized as having regular DLP, irregular DLP, or a mix of both. In the case of a mix there is, on the one hand, well-structured data accesses with regular and well-known address streams, including well-structured control flow corresponding to a regular DLP; and, on the other hand, less-structured data accesses with dynamic and difficult-to-predict address streams, and less-structured control flow representing irregular DLP [38].

Table 2 presents more detailed information for every application, such as the supported VL and the memory access pattern. It also indicates which applications stress the different vector microarchitecture modules such as the lane functional units or lane interconnection network. The final

|                 |                 |              |              | Jacobi-      | Particle     |              | Stream       |              |

|-----------------|-----------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| Application     |                 | Blackscholes | Canneal      | 2D           | Filter       | Pathfinder   | cluster      | Swaptions    |

| Vector Length   | Short           | $\checkmark$ |

|                 | Medium          | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

|                 | Large           | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| Memory Unit     | Unit-stride     | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

|                 | Indexed         |              | $\checkmark$ |              |              |              | $\checkmark$ |              |

| Vector Lane     | Arithmetic      | $\checkmark$ |

|                 | Mask            | $\checkmark$ |              |              | ~            |              | ~            | ~            |

| Interconnection | Slides          |              |              | $\checkmark$ |              | $\checkmark$ |              |              |

| Network         | Reductions      |              | $\checkmark$ |              |              |              | $\checkmark$ | $\checkmark$ |

| Intensive Comm  | with the Scalar | core         | $\checkmark$ |              | $\checkmark$ |              | $\checkmark$ |              |

Table 2. Vectorized Benchmark Suite Applications

row shows if the application has intense communication with the scalar core, featuring a tight mixture of scalar and vector operations and accesses.

It is important to mention that several efforts are being made from the community to include the support for the new vector standard to the compiler. However, the current support is at an initial stage, limiting use to assembly code or intrinsics at best. In that sense, at this point, it is not possible to use auto-vectorization to obtain a different set of instructions. Having said that, all the applications (C and C++ programs) were extended by adding the RISC-V vectorized version. The implementations make use of intrinsics, meaning that the compiler will substitute the intrinsic by a sequence of predefined vector instructions. In that sense, the vector compiler only takes the decision to insert spill code (vector load/store) when the number of vector registers is not sufficient, and vector move instructions when a vector register is used as an argument in a function. Also, the code was written in a Vector Length Agnostic fashion, meaning that the same binary can be executed in different Vector Engine configurations with any modification. It is important to point out that a detailed description of the original applications is omitted; however, the suite in which the applications were taken from is specified. For all the applications, four input sets are available: small, medium, large and native, which are specified in the README file of the repository [36]. All results discussed in this document were performed using the large input set. The following subsections describe how the vectorized versions were implemented. Furthermore, the degree of the vectorization achieved and how it could lead to obtain some initial insights about expected performance is discussed.

*4.1.1 Blackscholes.* This application represents the wide field of analytic PDE solvers in general and their application in computational finance in particular. This application was taken from PARSEC, and a detailed description can be found in Reference [20].

Table 3 presents some statistics of the Blackscholes application for both the scalar and the vectorized implementations. The analysis for the Vectorized code takes into account three different MVL configurations: short-vectors (MVL=8 elements each 64-bit wide), medium-vectors (MVL=64 elements each 64-bit wide), and large-vectors (MVL=256 elements each 64-bit wide). *Total Instructions* represents the number of executed instructions (*Scalar Instructions* + *Total Vector Instructions*). *Scalar Instructions* represents only the instruction executed by the scalar core. *Total Vector* Instructions represents the instructions executed by the vector engine (*Vector Memory Instructions* + *Vector Arithmetic Instructions*). *Vector Operations* represents the number of operations performed by the

|                                | Scalar Code   | Vectorized Code |                 |                  |

|--------------------------------|---------------|-----------------|-----------------|------------------|

|                                |               | MVL=8 elements  | MVL=64 elements | MVL=256 elements |

|                                |               | each 64-bit     | each 64-bit     | each 64-bit      |

| Total Instructions             | 4,316,765,131 | 727,119,128     | 342,504,727     | 298,856,749      |

| Scalar Instructions            | 4,316,765,131 | 484,635,928     | 312,194,327     | 291,279,149      |

| Vector Memory Instructions     |               | 22,118,400      | 2,764,800       | 691,200          |

| Vector Arithmetic Instructions |               | 220,364,800     | 27,545,600      | 6,886,400        |

| Total Vector Instructions      |               | 242,483,200     | 30,310,400      | 7,577,600        |

| Vector Operations              |               | 1,939,865,600   | 1,939,865,600   | 1,939,865,600    |

| % of Vectorization             |               | 80%             | 86%             | 87%              |

| Average VL                     |               | 8               | 64              | 256              |

Table 3. Instruction-level Characterization of Blackscholes Application

vector instructions, while scalar instructions perform only one operation per instruction, vector instructions perform VL operations per vector instruction. % *of vectorization* is defined as the ratio of *Vector Operations* over the total number of operations (*Scalar Instructions + Vector Operations*). Thus, all previous data plus the *Average VL* give us an idea if most of the hardware resources will be used through the program execution. The same table structure is used for all applications in this study.

Blackscholes is a regular DLP application where there are no dependencies between each price computation. The runtime profile of the scalar code shows that around 12% of the total runtime is spent in the initialization phase, which is not vectorizable. This task executes 573,256,509 scalar instructions, which are not taken into account in the results presented in Table 3 to present the % *Vectorization* only of the region of interest (ROI). Around 85% of the runtime is used to compute the *BlkSchlsEqEuroNoDiv* and *CNDF functions*, which corresponds to the ROI. In this code section basic floating-point operations are computed, including *fadd*, *fsub*, *fmul*, *fdiv*, *fsqrt*, as well as logarithmic and exponential functions. The vectorization of these functions was straightforward, since it presents a very regular DLP. Furthermore, logarithmic and exponential functions where also vectorized, since most of the time is spent computing these functions.

The total number of instructions drops considerably for the vectorized versions, not only because one vector instruction represents many scalar operations of the same type. For example, a *vadd.v* instruction for a configuration of VL = 256 elements represents 256 scalar add instructions, but also it removes many control instructions needed to execute the desired number of operations. All the scalar instructions needed to write the "*for*" loop, or the data movement from/to memory produced by the limited number of physical scalar registers are removed. As the VL increases, the percentage of vectorization increases because of the ratio resulting from the number of vector operations, which remains equal, over the number of the total operations (scalar operations + vector operations), which decreases as a result of the reduction of the number scalar instructions, as shown in Table 3.

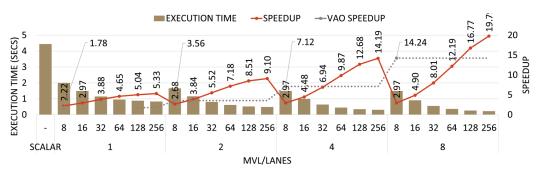

From previous data, it is possible to get an initial insight about the expected performance when executing the program in the vector architecture model. For example, obtaining the ratio between the number of the *Total instructions* of the serial version divided by the total number of operations (*Vector Operations* + *Scalar Instructions*) obtains a Vector-Accelerator-Only (VAO) speedup of 1.78x. Several factors can influence reducing or increasing this speedup. The execution of the remaining scalar instructions can be amortized underneath vector execution or the use of parallel lanes. Increasing the number of lanes would be expected to obtain a linear speedup increase, since it is

a high DLP application. However, based on the fact that the number of *Vector Operations* are the same for all versions, and omitting the use of parallel lanes, is the VAO speedup of 1.78x going to be the same no matter the MVL configuration? The answer is no! One important difference between the scalar and the vector execution with one lane is that the execution of the vector operations can be pipelined, because all vector operations of one vector instruction are independent. So benefits from vectorization are two-fold: reduction in the total number of operations and faster execution of vector operations, thanks to pipelining. Then, as the MVL is increased, it is possible to hide the latency of individual operations. Then, as an initial conclusion, it can be said that for larger MVLs, it is possible to achieve higher speedups than 1.78x. As the number of lanes is increased, obtaining a linear speedup increase would be expected especially for larger MVL configurations where the % of *Vectorization* is higher.

4.1.2 *Canneal.* The Canneal application is focused on minimizing the routing cost of a chip design using cache-aware simulated annealing (SA). SA is a metaheuristic to approximate global optimization in a large search space for an optimization problem. This application is representative of engineering workloads and features fine-grained parallelism with lock-free synchronization and pseudo-random worst-case memory access pattern. This application was taken from PARSEC, and a detailed description can be found in Reference [20].

The candidate function to vectorize is *swap\_cost*, which consumes most of the execution time. This is potentially a very vectorizable function, because it is composed of a couple of "for" loops in which three basic operations are performed: subtraction, absolute value, and addition. However, the data needed to perform these operations are the locations (coordinate x and y) of each input and output of the picked nodes; but these locations are not contiguous data in memory. The consequence is the need to use vector indexed load instructions, which are very costly operations. Furthermore, to use the vector indexed load operations, it is necessary to create the vector of pointers to each input/output element to have access to the pointer of the current element location. Creating it in every iteration is not good for the performance. Therefore, the class netlist\_elem was expanded with a new array of pointers called *fan\_locs* that stores the pointers to all inputs and outputs of each element; it is created in the initialization phase. Once the new array of pointers is added to the original code, the function *swap\_cost* can be vectorized easily by first loading the fan\_locs arrays of the picked nodes and then taking those loaded addresses to perform a couple of load indexed operations. Computing the routing cost is vectorized by using vector arithmetic and reduction instructions, sending the final result to the core to compute the final routing cost, and deciding if it should be swapped or not.

In this particular case, six configurations are presented in Table 4, since this application features some special case that will be discussed. Note that the initialization phase is not considered in the results presented in Table 4, to know the % Vectorization only of the region of interest. In Section 5.2, the impact in execution time caused by the addition of the *fan\_locs* array in the initialization phase is shown.

There are three relevant observations about this application. First, there is no considerable reduction in the number of Scalar Instructions and Total Vector Instructions. This happens because the inputs and outputs for each node vary from 0 up to 22 connections for the large input set. Then, the largest requested VL in this application is 22 elements each, representing a short-vector application. From MVL=8 to MVL=32, there are slight variations in the number of Scalar Instructions and Total Vector Instructions, while from MVL=32 up to MVL=256, it remains constant. From MVL=8 to MVL=32 the variation in Total Vector Instructions is visible, since the "for" loops in the function *swap\_cost* iterates 1, 2, 3, or up to 4 times, depending on the number of inputs and outputs for the picked node. This makes it possible to execute more Vector Instructions and, therefore,

|                                | Scalar Code   | Vectorized Code |                  |                  |

|--------------------------------|---------------|-----------------|------------------|------------------|

|                                |               | MVL=8 elements  | MVL=16 elements  | MVL=32 elements  |

|                                |               | each 64-bit     | each 64-bit      | each 64-bit      |

| Total Instructions             | 5,239,983,271 | 3,722,402,159   | 3,490,359,558    | 3,488,680,211    |

| Scalar Instructions            | 5,239,983,271 | 3,368,424,160   | 3,218,719,265    | 3,217,635,854    |

| Vector Memory Instructions     |               | 59,887,894      | 37,432,156       | 37,269,628       |

| Vector Arithmetic Instructions |               | 294,090,105     | 234,208,137      | 233,774,729      |

| Total Vector Instructions      |               | 353,977,999     | 271,640,293      | 271,044,357      |

| Vector Operations              |               | 2,450,191,462   | 3,102,641,472    | 4,078,370,559    |

| % of Vectorization             |               | 42%             | 49%              | 56%              |

| Average VL                     |               | 6.92            | 11.42            | 15.05            |

|                                |               | MVL=64 elements | MVL=128 elements | MVL=256 elements |

|                                |               | each 64-bit     | each 64-bit      | each 64-bit      |

| Total Instructions             |               | 3,488,680,211   | 3,488,680,211    | 3,488,680,211    |

| Scalar Instructions            |               | 3,217,635,854   | 3,217,635,854    | 3,217,635,854    |

| Vector Memory Instructions     |               | 37,269,628      | 37,269,628       | 37,269,628       |

| Vector Arithmetic Instructions |               | 233,774,729     | 233,774,729      | 233,774,729      |

| Total Vector Instructions      |               | 271,044,357     | 271,044,357      | 271,044,357      |

| Vector Operations              |               | 6,030,736,943   | 9,926,999,575    | 17,727,994,975   |

| % of Vectorization             |               | 65%             | 76%              | 85%              |

| Average VL                     |               | 22.25           | 36.63            | 65.41            |

| Table 4. | Instruction-level | Characterization of | Canneal Application |

|----------|-------------------|---------------------|---------------------|

|----------|-------------------|---------------------|---------------------|

more Scalar Instructions, since to iterate several times causes the execution of more scalar instructions such as control instructions. For MVLs equal or larger than 32 elements, the number of Total Vector Instructions is the same. Since the larger requested VL is 22, hardware implementations with MVL=32 or bigger can operate on all the input and outputs for the current element in only one iteration.

Second, the increase in the number of Vector Operations as the MVL is increased is substantial. Why does this occur? When analyzing the assembly code generated by the compiler, it is noted that there are two main factors that cause such an increase in the number of Vector Operations. First, there is code generated by the compiler when the number of vector registers is not sufficient. Then, additional vector load/store statements must be inserted to storing some registers in memory and restoring from memory to the original vector register when it finalizes. These extra statements are referred as spill code. The compiler knows nothing about the available MVL. In that sense, the compiler makes use of vector load/store instructions with the VL size equal to zero, which means to use the MVL that is supported by the micro-architecture. Then, the Vector Operations count increases as the MVL is increased. Second, every time that the function *swap\_cost* is called, as part of the input arguments, there are three vector registers, which are a mask register and two vector registers holding the coordinates (x and y) for each node. The compiler creates vector move instructions to move those input arguments to specific registers, which can be used inside the vectorized function. This vector move instructions uses the MVL allowed by the hardware, meaning that the full vector is copied into a new one, no matter that only a small part of the vector register will be used, causing the increase in the number of Vector Operations.

Third, the % of Vectorization increases notably for large MVL configuration. This increase does not reflect what happens. It would be expected that the % of Vectorization increases as the MVL is

increased because of the reduction of *Scalar Instructions*, while the number of vector operations remains constant. However, the number of *Vector Operations* also increases because of the different reasons explained above. Such an increase directly impacts the value of the % of *Vectorization*, since it is calculated as the ratio between the *Vector Operations over the Scalar Instructions* + *Vector Operations*. For that reason, this increase in the % of *Vectorization* does not provide a real improvement by vectorizing the application.

From previous data, it is possible to get an initial insight about the expected performance. In this case, it obtained a VAO speedup of 0.90x for the MVL=8. Unlike the Blackscholes application, Canneal presents intensive communication with the scalar core. When vector computation for every couple of picked nodes is finalized, the result is sent to the scalar core to evaluate if the nodes should be swapped or not. Then, it can be expected that many of the remaining scalar instructions cannot be amortized underneath vector execution. Contrary to Blackscholes, as the MVL is increased, a speedup decrease is expected, since the number of *Vector Operations* increases notably.

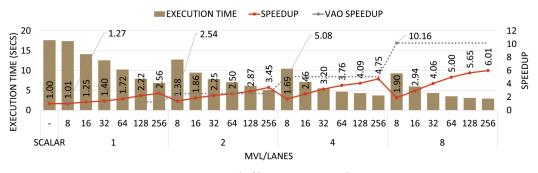

4.1.3 Jacobi-2D. Jacobi-2D is an iterative algorithm for determining the solutions of a diagonally dominant system of linear equations. This solver is often used in computational science as part of scientific and engineering applications. This application was taken from PolyBench, and a detailed description can be found in Reference [19].

The Jacobi solver is a very interesting application, because it can be vectorized by using vector arithmetic operations, vector memory instructions, and vector element manipulation instructions. In that sense, not only the Lanes and the Vector Memory Unit are evaluated, but also the interconnection between the lanes. These vector element manipulation instructions are *vslide1up.v* and *vslide1down.v*, which move elements one position up and down a vector register. It is possible to load a fraction of one row and operate on it by applying vslide1up.v to obtain the left neighboring nodes and *vslide1down.v* to obtain the right neighboring nodes. Once the left and right neighboring nodes are aligned and top and bottom neighboring nodes are loaded, it is possible to operate on them in parallel.

One interesting observation is the slight variation in the number of *Vector Operations*. This happens because a nested "for" loop is implemented to go through the matrix to compute one complete iteration. Outside the "for" loop, a vector instruction is defined, which sets a constant. This instruction is executed only once per iteration, and for the large input set, 4,000 iterations are defined, meaning that this instruction is executed 4,000 times. For MVL=8 elements, means that in one iteration, this instruction is going to execute 8 *Vector Operations* (32,000 *Vector Operations* after finalizing all the iterations). On the contrary, for MVL=256 elements, means that in each iteration, this instruction is going to execute 256 *Vector Operations* (1,024,000 *Vector Operations* after finalizing all the iterations). Then, if those values are subtracted from the total *Vector Operations* in the corresponding configuration, this will result in the same number of *Vector Operations* for all the cases.

As an initial insight based on the data presented in Table 5, it is possible to obtain a VAO speedup of 1.09x. Additionally, for larger MVLs it is possible to achieve higher speedups. As increasing the number of lanes obtains a linear speedup, an increase would be expected, especially for larger MVL configurations where the % of Vectorization is higher.

4.1.4 Particle Filter. The Particle Filter (PF) application is a statistical estimator of the location of a target object given noisy measurements of the state. In image analysis, the PF is utilized widely in applications such as facial recognition. This particular implementation is optimized for tracking cells, particularly leukocytes (white blood cells). This application was taken from Rodinia, and a detailed description can be found in Reference [22]. This application uses special operations with

|                                | Scalar Code   | Vectorized Code |                 |                  |

|--------------------------------|---------------|-----------------|-----------------|------------------|

|                                |               | MVL=8 elements  | MVL=64 elements | MVL=256 elements |

|                                |               | each 64-bit     | each 64-bit     | each 64-bit      |

| Total Instructions             | 4,797,698,032 | 1,665,765,868   | 328,373,875     | 185,081,872      |

| Scalar Instructions            | 4,797,698,032 | 1,275,617,868   | 279,601,875     | 172,885,872      |

| Vector Memory Instructions     |               | 65,280,000      | 8,160,000       | 2,040,000        |

| Vector Arithmetic Instructions |               | 259,894,400     | 32,489,600      | 8,124,800        |

| Vector Elem Manipulation Inst  |               | 64,973,600      | 8,122,400       | 2,031,200        |

| Total Vector Instructions      |               | 390,148,000     | 48,772,000      | 12,196,000       |

| Vector Operations              |               | 3,121,184,000   | 3,121,408,000   | 3,122,176,000    |

| % of Vectorization             |               | 71%             | 92%             | 95%              |

| Average VL                     |               | 8               | 64              | 256              |

Table 5. Instruction-level Characterization of Jacobi-2D Application

masks, which send resultant data to the scalar core and were not used in previous applications. These vector instructions are *vfirst.m*, which finds the lowest-numbered active element of the source mask vector that has its least-significant bit set and writes that element's index to a scalar register; and *vpopc.m*, which counts the number of mask elements of the active elements of the vector source mask register that have their least-significant bit set and writes the result to a scalar register. Also, this application uses complex operations such as logarithm, cosine, and square root.

The task in charge of applying a predefined motion model that represents the estimated path that the object will follow is a good candidate to be vectorized, because the same operations are applied to all objects in the frame. Furthermore, to apply the motion model, it is necessary to generate a sequence of random numbers using the Box-Muller transformation, which makes use of expensive operations such as logarithm, cosine, and square root. The task that consumes most execution time is the guess updates based on the current location of the object. These new guesses are used by the following frame in the video to iterate again. This task is implemented in a nested for loop, which performs a sequential search returning an index value to update the arrays *arrayX* and *arrayY*. This task can be implemented by first using a vector comparison instruction to obtain a mask representing the active element in the generated mask and its corresponding position. When the criteria are met, the position of each active element is obtained to finally use the *vpopc.m* instruction to check if all elements in the vector have been set, breaking the inner loop. Otherwise, the program continues with a new iteration until all elements get the updated position.

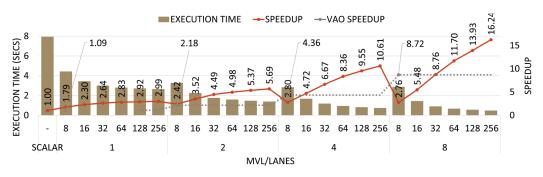

Table 6 presents some statistics for the PF application. This application presents a very high percentage of vectorization increasing as the MVL is increased, achieving up to 91% of vectorization. However, the number of instructions for an MVL=8 is reduced by 4x, and as the MVL is increased, the number of instructions decreases up to 16x. The slight variation in the number of *Vector Operations* is similar to the case presented in Jacobi-2D. Instructions outside of the nested loops are responsible for this slight variation.

As was the case for previous applications, it is possible to get an initial insight about the expected performance. By analyzing PF, it is possible to get VAO speedup of 1.27x for the MVL=8 and up to 10.16x for eight-lane configuration. Unlike Blackscholes and Jacobi-2D applications, which are regular and high DLP applications, Particle Filter presents a mix of DLP. Nevertheless, by using *vfirst.m* and *vpopc.m* vector instructions, it is possible to handle the less-structured control flow in a relatively easy way. For sure, this will cause some implications in terms of performance, since

|                                | Scalar Code    | Vectorized Code |                 |                  |

|--------------------------------|----------------|-----------------|-----------------|------------------|

|                                |                | MVL=8 elements  | MVL=64 elements | MVL=256 elements |

|                                |                | each 64-bit     | each 64-bit     | each 64-bit      |

| Total Instructions             | 20,232,505,095 | 4,993,215,636   | 1,617,632,096   | 1,260,531,622    |

| Scalar Instructions            | 20,232,505,095 | 3,446,128,079   | 1,423,641,027   | 1,211,546,181    |

| Vector Memory Instructions     |                | 1,607,712       | 200,992         | 50,272           |

| Vector Arithmetic Instructions |                | 1,545,479,845   | 193,790,077     | 48,935,169       |

| Total Vector Instructions      |                | 1,547,087,557   | 193,991,069     | 48,985,441       |

| Vector Operations              |                | 12,376,700,456  | 12,415,428,416  | 12,540,272,896   |

| % of Vectorization             |                | 78%             | 90%             | 91%              |

| Average VL                     |                | 8               | 64              | 256              |

## Table 6. Instruction-level Characterization of Particle Filter Application

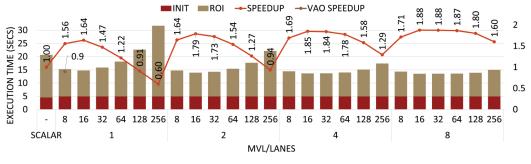

Table 7. Instruction-level Characterization of Pathfinder Application

|                                | Scalar Code   | Vectorized Code |                 |                  |

|--------------------------------|---------------|-----------------|-----------------|------------------|

|                                |               | MVL=8 elements  | MVL=64 elements | MVL=256 elements |

|                                |               | each 64-bit     | each 64-bit     | each 64-bit      |

| Total Instructions             | 6,213,455,512 | 1,337,948,580   | 402,094,500     | 301,824,392      |

| Scalar Instructions            | 6,213,455,512 | 1,037,138,340   | 364,493,220     | 292,424,072      |

| Vector Memory Instructions     |               | 100,270,080     | 12,533,760      | 3,133,440        |

| Vector Arithmetic Instructions |               | 120,324,096     | 15,040,512      | 3,760,128        |

| Vector Ele Manipulation Instr  |               | 80,216,064      | 10027008        | 2,506,752        |

| Total Vector Instructions      |               | 300,810,240     | 37,601,280      | 9,400,320        |

| Vector Operations              |               | 2,406,481,920   | 2,406,481,920   | 2,406,481,920    |

| % of Vectorization             |               | 70%             | 87%             | 89%              |

| Average VL                     |               | 8               | 64              | 256              |

both instructions cause intensive communication with the scalar core. It is expected that many of the remaining scalar instructions cannot be amortized underneath vector execution.

4.1.5 *Pathfinder.* The Pathfinder application uses the ghost zone optimization technique to find the shortest paths on a 2-D grid. This application was taken from Rodinia, and a detailed description can be found in Reference [22]. The reason to select this application is due to the high percentage of vector element manipulation instructions.

One interesting aspect of this application is that the algorithm implemented to find the shortest paths inside *run* function is composed of a nested loop. For each node, comparisons with its corresponding neighboring nodes are performed to find the smallest weight and adding it to the current node weight. This task is easily implemented using the vector *slide1up* and *slide1down* operations to accommodate the neighboring nodes in the same position and operate on it to finally store the resultant data. Vector element manipulation instructions reported in Table 7 consume 26% of the total vector instructions, meaning that the lane interconnection can be stressed by this application. The number of instructions for MVL=8 is reduced by 4.6x, and as the MVL is increased, the number of instructions decreases up to 20.5x. However, the percentage of vectorization increases as the MVL is increased, achieving up to 89% of vectorization.

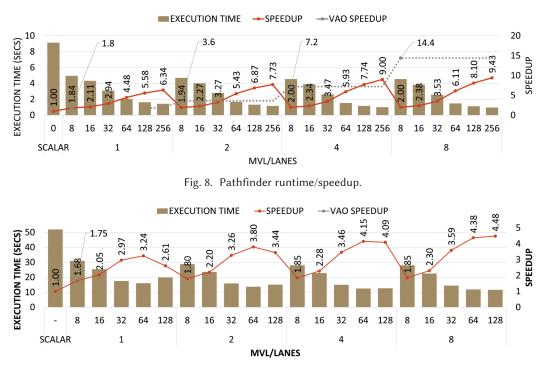

|                                | Scalar Code    | Vectorized Code |                 |                  |

|--------------------------------|----------------|-----------------|-----------------|------------------|

|                                |                | MVL=8 elements  | MVL=64 elements | MVL=128 elements |

|                                |                | each 64-bit     | each 64-bit     | each 64-bit      |

| Total Instructions             | 36,068,326,139 | 6,349,730,434   | 2,599,142,070   | 2,331,242,835    |

| Scalar Instructions            | 36,068,326,139 | 4,325,602,994   | 2,241,943,122   | 2,093,110,203    |

| Vector Memory Instructions     |                | 952,530,560     | 119,066,316     | 59,533,158       |

| Vector Arithmetic Instructions |                | 1,071,596,880   | 238,132,632     | 178,599,474      |

| Total Vector Instructions      |                | 2,024,127,440   | 357,198,948     | 238,132,632      |

| Vector Operations              |                | 16,193,019,520  | 22,860,732,672  | 30,480,976,896   |

| % of Vectorization             |                | 79%             | 91%             | 94%              |

| Average VL                     |                | 8               | 64              | 128              |

Table 8. Instruction-level Characterization of Streamcluster Application

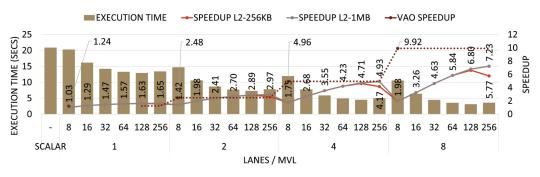

As initial insight for Pathfinder application based on the data presented in Table 7, it is possible to obtain a VAO speedup of 1.8x for an MVL=8 and one-lane configuration. Also, it would be expected to obtain a linear increase as the number of lanes increase, achieving up to 14.4x for eight-lane configuration. Finally, for larger MVLs it is possible to achieve higher speedups than 1.8x.