# A Retrospective and Futurespective of Rowhammer Attacks and Defenses on DRAM

Zhi Zhang, Jiahao Qi, Yueqiang Cheng, Shijie Jiang, Yiyang Lin Yansong Gao, Surya Nepal, Yi Zou, Jiliang Zhang, Yang Xiang (IEEE Fellow)

Abstract—Rowhammer has drawn much attention from both academia and industry in the last few years as rowhammer exploitation poses severe consequences to system security. Since the first comprehensive study of rowhammer in 2014, a number of rowhammer attacks have been demonstrated against ubiquitous dynamic random access memory (DRAM)-based commodity systems to cause denial-of-service, gain privilege escalation, leak sensitive information or degrade DNN model inference accuracy. Accordingly, numerous software defenses have been proposed to protect legacy systems while hardware defenses aim to protect next-generation DRAM-based systems. In this paper, we systematize rowhammer attacks and defenses with a focus on DRAM. Particularly, we characterize rowhammer attacks comprehensively, shedding lights on possible new attack vectors that have not yet been explored. We further summarize and classify existing software defenses, from which new defense strategies are identified and worth future exploring. We also categorize proposed hardware defenses from both industry and academia and summarize their limitations. In particular, most industrial solutions have turned out to be ineffective against rowhammer while on-die ECC's susceptibility to rowhammer calls for a comprehensive study. Our work is to inspire the software-security community to identify new rowhammer attack vectors while present novel defense solutions against them in legacy systems. More importantly, both software and hardware security communities should work together to develop more effective and practical defense solutions.

Index Terms—Rowhammer, Attacks and Defenses, DRAM.

# arXiv:2201.02986v2 [cs.CR] 29 Apr 2022

#### **1** INTRODUCTION

**Rowhammer:** Recent years have witnessed an infamous hardware vulnerability, termed as *rowhammer*, which is essentially a circuit-level interference problem that exists in several mainstream memories (e.g., NAND Flash Memory [1], MRAM [2] and DRAM [3]). Among them, rowhammer on DRAM (Dynamic Random Access Memory) has caused serious security implications as DRAM is widely used in mainstream computer systems. In as early as 2014, Kim et al. [3] performed the first comprehensive study of rowhammer on DRAM, which showed that frequent accessing (i.e., hammering) DRAM rows (known as *aggressor rows*) could cause bit flips in their adjacent rows (*victim rows*) without accessing the victim rows.

In a case where a victim row hosts sensitive data (e.g., page tables), an unprivileged adversary can induce

- Z. Zhang and S. Nepal are with Data61, CSIRO. E-mail: {zhi.zhang;surya.nepal}@data61.csiro.au

- J. Qi, S. Jiang and Y. Lin are with School of Microelectronics, South China University of Technology, China. E-mail: {miqjh;mijiangshijie;milinyiyang}@mail.scut.edu.cn.

- Y. Cheng is with NIO. E-mail: yueqiang.cheng@nio.io.

- Y. Gao is with School of Computer Science and Engineering, Nan-Jing University of Science and Technology, China. E-mail: yansong.gao@njust.edu.cn.

- Y. Zou is with School of Microelectronics, South China University of Technology, China and Pazhou Lab, Guangzhou, China. E-mail: zouyi@scut.edu.cn.

- J. Zhang is with College of Integrated Circuits, Hunan University, China. E-mail: zhangjiliang@hnu.edu.cn.

- Y. Xiang is with School of Software and Electrical Engineering, Swinburne University of Technology, Australia. E-mail: yxiang@swin.edu.au.

rowhammer-based bit flips to corrupt the data even if she has no access to the victim row, implying that a rowhammer exploit can break memory management unit (MMU)enforced memory isolation even in the absence of software vulnerabilities, posing severe consequences to the whole system security. As a result of the study from Kim et al. [3], a myriad of rowhammer attacks have been demonstrated to cause denial-of-service to the system [4], [5], or even gain privilege escalation [6], [7], [8], [9], [10], [11], [12], [5], [13], [14], or leak sensitive information [15], [16], [17], [18], [19], or undermine the inference accuracy of target Deep Neural Network (DNN) models [20], [21].

To counteract rowhammer as well as its attacks, numerous countermeasures have been proposed from academic and industry. In general, they can be classified into two categories, i.e., software and hardware defenses, among which software solutions are building a defense wall for legacy systems while hardware solutions aim to mitigate rowhammer-induced bit flips for recent DRAM modules.

With denser DRAM cells, newer DRAM modules are more susceptible to rowhammer [22], continuously heating up the arms race between rowhammer attacks and defenses. In this work, we aim to perform a systematic study of existing rowhammer attacks and defenses, shedding lights on future attacks and defenses. Thus, we are interested in the following three questions for attacks:

- What are the primary steps to demonstrate a rowhammer attack in a commodity computer system?

- What are the mainstream techniques to implement each attack step?

- What are the possible real attack scenarios in future

<sup>•</sup> Z. Zhang and J. Qi are joint first authors.

explorations?

For defenses, we specifically ask:

- What is the status quo of software and hardware defense strategies?

- What are the specific future directions in the software or hardware side?

The only existing survey published in 2019 [23] cannot answer the above questions. First, after its publication, a large number of newly proposed attacks, software and hardware defenses have been reported. Second, only a few major attacks and defense solutions were briefly described, with a focus on the authors' previously proposed hardware solution (i.e., PARA [3]). Although the survey believed that more novel attacks and defenses would be proposed in the near future, few specific directions were discussed.

Our Work: With this motivation, we conduct a retrospective and futurespective survey of attacks and defenses on DRAM to answer the aforementioned questions. Compared to the existing survey, we show a taxonomy of all attacks against commodity systems based on the hardware architecture where an attack originates, the threat model and the attacker objective (see Table 1). We then characterize existing attacks by presenting the primary steps that an unprivileged rowhammer attacker must follow and systematically summarize the techniques in each attack step. We also classify existing software defenses based on their design objectives (see Table 3), from which we can clearly see that all of them aim to prevent one of the primary attack steps. However, each category of the defenses has its own limitations in terms of keeping their security guarantee and applicability to commodity systems. We further categorize existing hardware defenses from industry as well as those proposed from academia based on their security objectives and prototype locations (see Table 4). This is followed by a summary of their limitations in terms of keeping their security guarantees, scalability to an increasingly small MAC (maximum activation count that a row can bear before its adjacent rows have any bit flips), memory efficiency, cooperation between the memory controller (MC) and DRAM.

Following a comprehensive study of existing attacks and defenses, we provide explicit research directions for future attacks and defenses by identifying four potential attacks and two possible defenses. Specifically, an unprivileged attacker is likely to trigger rowhammer, break hypervisor-enforced memory isolation and gain hypervisor privilege, bypassing all existing DRAM-aware memory isolation defenses in an industrial hardware-assisted environment provided by mainstream cloud service providers (CSPs). She may also launch an attack from an isolated GPU in x86, particularly in a real-world scenario where GPU and its memory are shared in a multi-tenant manner. Besides, a rowhammer attack may originate from RISC-V, an increasingly popular architecture, and target a RISC-V-enforced trusted execution environment. It may be of interest for the security community to conduct a comprehensive study of rowhammer on RISC-V-based products. Alternatively, the attacker may be interested in the impacts of rowhammer against on-die Error Correction Code (ECC) as it has been adopted in recent DRAM chips such as LPDDR4 [24] and DDR5 [25]. As a defender, she may reinforce DRAM-aware memory isolation

solutions in hardware-assisted virtualization to address the potential threats from specific rowhammer attacks. A practical isolation prototype may reside in kernel-based virtual machine (KVM), as it is in the Linux kernel and widely used as a hypervisor by mainstream cloud platforms. On top of that, she may detect attacks at a much broader range based on the abnormal pattern of DRAM power consumption, as rowhammer always requires frequent memory accesses to DRAM rows.

**Summary of Contributions:** In summary, we have made three main contributions as follows:

- We *comprehensively characterize* existing rowhammer attacks from their attack vectors, present the primary steps that an attack follows and systematically summarize the techniques in each attack step.

- We *rigorously categorize* existing software and hardware defenses and abstract their key defense strategies. With the categorization, their key limitations are summarized.

- We show our insights about *concrete research directions* for future rowhammer attacks and defenses, that is, four potential attacks and two possible defenses are identified.

The rest of the paper is structured as follows. In Section 2, we introduce DRAM organization, rowhammer characteristics in DRAM. In Section 3, we discuss a comprehensive study of existing attacks on DRAM. We focus on existing defenses against rowhammer in Section 4. Based on the study, we share our detailed insights on future explorations in Section 5. We then conclude this paper in Section 6.

# 2 BACKGROUND

In this section, we first describe DRAM organization as well as its operations and address mappings. We then discuss major rowhammer characteristics in DRAM that are leveraged for the purpose of rowhammer attacks or tests.

# 2.1 DRAM Organization

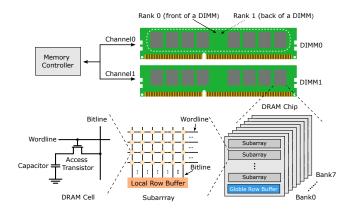

Figure 1 presents an overview of a modern DRAM organization. Specifically, a memory controller (MC) communicates with dual inline memory modules (DIMMs) through channels and each channel consists of a command, an address bus and a data bus. A DIMM has one or more ranks (e.g., single/dual-rank). A rank has a set of chips that operate in lockstep to reply to commands from the MC. Each chip has several banks. In a typical case where the data bus is 64-bit wide, a rank has 8 chips with 8 banks in a chip to serve the data bus. If multiple ranks share the same channel, the ranks are multiplexed. A bank is composed of subarrays and a global row buffer (made up of sense amplifiers). Each subarray is a two-dimensional array of cells with a local row *buffer*. The cells in a row are connected horizontally through a wordline. The cells in a column are connected vertically through a bitline to the local row buffer. The local row buffers are wired to the global row buffer via global bitlines. A cell consists of an access transistor serving as a switch and a capacitor storing a single bit. A cell has two types, i.e., true cell and anti cell. A true cell stores a logic value of '1' or '0' when its capacitor is charged or discharged. An anti-cell works in the opposite way.

**DRAM Operation:** From the view of the MC, it only sees a logical bank organization rather than a physical one. The logical bank is a two-dimensional array (i.e., rows and columns) of cells with a row buffer (i.e., a one-dimensional array of sense amplifiers) for data access. To access data from DRAM, the MC issues the following three commands to communicate with a logical bank.

*First*, an activate command (ACT) is sent to *open* a desired row, whose data will be read into the row buffer. *Second*, a read/write (RD/WR) command is issued to access desired columns from the row buffer. *Last*, a precharge (PRE) command is used to *close* the row and clear the row buffer for subsequent accesses to another row.

As a cell leaks charge gradually over time, a minimum time period that a cells retains its bit is referred to as *retention time*. The MC periodically issues a refresh command (REF) to the banks to ensure all rows are refreshed before the retention time expires. The refresh interval for a row is normally 64 ms [26], [27] (i.e., tREFW), within which at least 8192 REF commands are issued and thus each command is issued every 7.8  $\mu$ s (i.e., tREFI).

**DRAM Address Mapping:** There are two DRAM address mappings. The first one is enforced by the MC that maps physical addresses to logical DRAM addresses. A logical DRAM address refers to a 3-tuple of (bank index, row index, column index), in which the bank index includes DIMM, channel, and rank. The second one is a DRAM internal mapping that primarily remaps logical DRAM addresses to physical DRAM addresses. As such, logical rows that are adjacent to each other in the view of the MC are likely to be physically non-adjacent in DRAM.

For the first mapping, it is available in AMD's architectural manuals while publicly undocumented in other major architecture vendors such as Intel. Although undocumented, the mapping has been reverse-engineered by previous works [28], [11], [29] through a timing side channel [30], that is, accessing a pair of virtual addresses mapped to different rows of the same bank causes higher access latency than that of the addresses residing in different banks or in the same row of the same bank.

The second remapping is generally implementationspecific and kept as confidential by DRAM manufacturers. As hammering a row causes most bit flips on its two physically-adjacent rows above and below, prior works [31], [22], [32], [33] have reverse-engineered the remapping scheme. Particularly, Cojocar et al. [32] experiment with multiple server-class DDR4 modules from three major DRAM manufacturers, results of which show that some logical rows do not map linearly to physical rows, and two halves of a logical row can be mapped to different physical rows. Kim et al. [22] present that every two consecutive logical rows share the same physical row in their tested LPDDR4 modules.

#### 2.2 Rowhammer in DRAM

A variety of prior works have identified different characteristics that affect rowhammer-induced bit flips [3], [22], [33], [34] in DRAM-based systems. In the following, we introduce the major characteristics that are of interest to rowhammer exploits or tests.

Fig. 1: DRAM Organization.

#### 2.2.1 Hammer Pattern

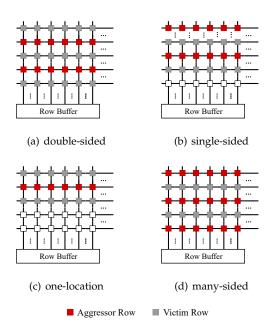

To trigger rowhammer, row buffer is bypassed and one or more rows are hammered [3]. Thus, a *hammer pattern* refers to how rows are hammered. As shown in Figure 2, there are four existing hammer patterns and each has different effectiveness in triggering bit flips.

Fig. 2: Four existing hammer patterns. (For the purpose of illustration, only rows adjacent to the aggressor rows are assumed to be vulnerable. We note that rows that are not adjacent to the aggressor rows can also be vulnerable [3], [22] and the row distance from an aggressor row to a row

*Double-sided Hammer* hammers two rows that have one row apart within the same bank. As can be seen from Figure 2(a), all rows adjacent to the hammered rows are likely to be victims, among which the row sandwiched by the two aggressor rows is the most likely to be flipped, as its charges in the capacitors are interfered by the rows above and below.

with bit flips is called *blast radius*.)

*Single-sided Hammer* randomly selects two rows for hammering, with the hope that the selected rows are within the same bank and thus the row buffer is bypassed [6]. When the rows being hammered happen to be in the same bank, each row neighboring the aggressor row is likely to be a victim. This is shown in Figure 2(b).

*One-location Hammer* is illustrated by Figure 2(c) where it only picks one row for hammering [5]. It only applies to specific systems where the (MC) employs a close-page policy, that is, the MC preemptively closes an accessed row without opening another row, implicitly forcing the DRAM to flush the row buffer.

*Many-sided Hammer* shown in Figure 2(d), hammers more than two rows within the same bank one after another [35]. It is the first effective pattern in triggering a number of bit flips in DDR4 modules where target row refresh [36] is deployed. Following the work in [36], Blacksmith [37] is a variant of this pattern where many aggressor rows are hammered in a non-uniform way, unlike the hammer patterns above where each aggressor row is hammered at the same frequency. Compared to the original many-sided hammer pattern, this variant is much more effective in DDR4 modules.

**Hammer Count:** It refers to the number of activations that aggressor rows adjacent to a victim row are being hammered. Take the double-side hammer as an example, the number of activations to two aggressor rows sandwiching a target row is referred as hammer count (HC) [22]. DRAM's susceptibility can be quantified by the minum hammer count to induce the first bit flip, i.e.,  $HC_{first}$ , which can be as low as in the order of 20 K on DDR3 modules and 10 K on DDR4 modules [22].

**Blast Radius:** The rows that are not adjacent to the aggressor rows can also be affected, and the maximum row distance between an aggressor row to a victim row is referred to as blast radius. Kim et al. [22] empirically observe that the blast radius of DRAM modules can be up to 6.

# 2.2.2 Data Pattern

Besides the hammer pattern, values stored in the aggressor and victim rows also significantly affects bit-flip effectiveness, coined as *data pattern* [3]. There are four main data patterns, i.e., Solid (all cells store '0' or '1'), RowStripe (rows storing '0' are interleaved with rows storing '1'), ColStripe (columns storing '0' are interleaved with columns storing '1'), and Checkered (cells storing either '0' or '1' in a checkerboard way). Among these patterns, RowStripe is the most effective [3].

For a single vulnerable cell, whether it can be flipped depends on not only itself but also the logic values of cells above and below [3]. For a true cell that is in a charged state and thus stores '1', it can be flipped to '0' only when the cells above and below it store '0', but not when both cells store '1'. If a true cell is in a discharged state and thus stores '0', it cannot be flipped to '1' no matter what the above and below values are. For anti cells, their bit-flip direction is also monotonic and works in the opposite way. With this key observation, Ji et al. [38] develop effective data patterns at the granularity of a single cell to trigger bit flips in targeted cells while suppress bit flips in other unwanted cells.

# **3 ROWHAMMER ATTACKS**

By scrutinizing all existing rowhammer attacks in Table 1, we summarize the following critical steps to demonstrate a meaningful rowhammer attack.

- An attacker abuses built-in features of either software or hardware to place target sensitive objects into desired rows and the sensitive objects have close proximity in DRAM to attacker-induced objects.

- 2 The attacker induces frequent accesses (i.e., hammer) to attacker-induced objects in aggressor rows without involving processor caches and row buffer, triggering desired bit flips.

- 3 The attacker exploits the bit flips to compromise system security, that is, causing denial-of-service (DoS) of the system, or breaking memory isolation.

We refer to the DoS-based attacks as non meaningful and thus they do not require step **1**. In the following, we discuss each step in detail.

#### 3.1 Placing Sensitive Objects onto Desired Rows

Existing attacks have abused different built-in features from modern operating systems (OSes) and proposed corresponding techniques to implement this step in a probabilistic or deterministic way. These techniques have their unique names while some do not necessarily reflect the techniques. Thus, in this section, we introduce the techniques based on the features that have been exploited.

**mmap:** It is a posix user interface, by which a user can specify a file to be memory-mapped and access it from her own address space. In case of Linux, the kernel loads the file content into physical memory and allocates page-table entries accordingly in an on-demand manner, that is, the physical memory and page-table entries are not allocated until the file is accessed by the user process. Thus, the attacker can repeatedly invoke this feature, forcing the kernel to create a large number of page-table pages. These pages are sensitive objects and some are highly likely to be physically adjacent to the attacker pages in aggressor rows [6], [41], [42].

**fork:** It is a system call, by which a (parent) process can create a new child process. Similar to the invoking process, the child process has its own kernel structures, such as struct task\_struct and struct cred. Among the structures, struct cred is of interest to an attacker, as it stores the user id of a process. An attacker can repeatedly invoke fork to create a large number of processes and thus sprays the memory with sensitive structures, with the hope that some struct cred will be placed next to the attacker pages in aggressor rows [41], [42].

**WebGL:** It is a JavaScript API for web developers to accelerate 2D and 3D images rendering in mainstream browsers. WebGL reserves a memory cache pool for storing free textures and the pool contains 2048 pages. To prevent vulnerable pages of textures from being freed to the pool, GLitch [44] releases 2048 previously-allocated textures to the pool. Right after releasing vulnerable textures, it applies for a large memory allocation of target JavaScript objects ArrayObjects. Thus, some ArrayObjects can reuse the freed vulnerable texture pages and thus can be corrupted by rowhammer.

| Architecture | Hardware Originator | Assumpti           | on              | Real-World Attack                                                          | Objective                                                                                                             |

|--------------|---------------------|--------------------|-----------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| x86          | NIC w/ RDMĂ<br>CPU  | Remote*            | Network Packets | Throwhammer [14]<br>Nethammer [39]                                         | Gain privilege of a memcached application.<br>Cause denial of service.                                                |

|              | CPU                 | Local              | Browser Sandbox | Bosman et al. [15]<br>SMASH [40]<br>Seaborn et al. [6]<br>Gruss et al. [7] | Escape sandbox.                                                                                                       |

|              |                     |                    | Native Process  | Seaborn et al. [6]<br>CATTmew [41]<br>PThammmer [42]                       | Gain kernel privilege.                                                                                                |

|              |                     |                    |                 | Gruss et al. [5]<br>Bhattacharya et al. [16]<br>RAMBleed [18]              | Gain root privilege or cause denial of service.<br>Leak cryptographic information.<br>Leak cryptographic information. |

|              |                     |                    |                 | SGX-Bomb [4]<br>DeepSteal [19]<br>SpecHammer [43]                          | Cause denial of service.<br>Leak weights of target DNN model.<br>Strengthen Spectre attacks.                          |

|              |                     |                    |                 | Hong et al. [20]<br>DeepHammer [21]                                        | Degrade target DNN model.                                                                                             |

|              |                     |                    | ParaVM          | Xiao et al. [11]                                                           | Gain hypervisor privilege.                                                                                            |

|              |                     |                    | HVM             | Razavi et al. [12]                                                         | Gain privilege of a target HVM.                                                                                       |

|              |                     |                    |                 | Future Exploration                                                         | Gain hypervisor privilege.                                                                                            |

|              | FPGA                | Local              | AFU             | JackHammer [17]                                                            | Leak cryptographic information.                                                                                       |

|              | Isolated GPU        | Future Exploration |                 |                                                                            |                                                                                                                       |

| ARM          | Integrated GPU      | Local              | Browser Sandbox | GLitch [44]                                                                | Escape sandbox.                                                                                                       |

|              | CPU                 | Local              | Native Process  | Drammer [8]<br>RAMpage [45]                                                | Gain kernel privilege.                                                                                                |

| RISC-V       | Future Exploration  |                    |                 |                                                                            |                                                                                                                       |

TABLE 1: A taxonomy of rowhammer attacks against commodity systems. For the discussion about future explorations, please refer to Section 5.1. (Remote means that an attacker requires no code execution in a target system.)

**Page deduplication:** To improve memory utilization, a running system merges physical pages that have the same content, coined as page deduplication. Particularly, this feature benefits CSPs as it allows CSPs to run more VMs with the same amount of physical memory. To abuse this feature, the attacker crafts an attacker page at a specified vulnerable page. This page has the same content as the target sensitive page of another VM in a cloud setting. Thus, the underlying VM monitor is lured into merging the two pages into the attacker-specified page [12]. While this feature is not always available in commodity systems (e.g., Linux), it is a default-on feature in windows 10 and has been successfully abused by Bosman et al. [15].

Per-CPU page-frame cache update policy: Linux buddy allocator divides system memory into multiple nonoverlapping zones, e.g., ZONE\_DMA, ZONE\_DMA32 and ZONE\_normal in the x86-64 architecture. If a process running on a CPU frees a page frame, the buddy allocator does not return the freed page frame to its corresponding zone. Instead, it pushes the freed page frame into a per-CPU pageframe cache (i.e., per-CPU pageset), which maintains a list of free page frames released by the CPU using the policy of Last-In-First-Out (LIFO). A consequence of this design is that the freed page frame is likely to be reused by the CPU and the page content is still hot in the per-CPU cache. Particularly, RAMBleed [18], DeepHammer [21] and SpecHammer [43] hold targeted page frames, and then free the page frames. After that, they immediately trigger targeted processes to run. With the update policy, the page frame cache will allocate the freed page frames for targeted sensitive pages of the processes.

**Page frame allocation policy:** Linux buddy allocator manages system memory as memory blocks and each block has

a continuous physical memory region, size of which is a power-of-two number of page frames. For blocks that have the same size, they are maintained in the same block list. To serve a memory allocation request, Linux first searches each block list iteratively for a block that satisfies the request. If none of the blocks have the requested size, Linux splits a larger-sized block into two blocks, returns one block to fulfill the request, and adds the other block into an appropriate block list. Upon a memory deallocation request, Linux tries to merge the freed page frames with their neighboring free page frames (if possible), thus generating a bigger block and updating it into a block list. This allocation policy is to minimize external fragmentation of physical memory.

Drammer [8] and RAMpage [45] abuse this allocation policy by exhausting and freeing memory blocks in a predictable way, with the goal of placing a page-table page onto an available and vulnerable page frame. Similarly, SpecHammer [43] leverages the policy to create memory pressure, which will probably force the kernel to use a vulnerable user page to store targeted kernel stack variables. SMASH [40] consumes all the memory blocks that are smaller than 2MB and then requests additional 4KB page frames for JavaScript ArrayBuffers, which will force the buddy allocator to split a previously freed vulnerable 2 MB memory block. The split vulnerable 4 KB page frame is predicted to host JavaScript ArrayBuffer. Similar to SMASH, CATTmew [41] exhausts the memory blocks that are smaller than or equal to the DIMM row size. Then the buddy alloctor is forced to split a large memory block that is twice the row-size when the attacker allocates 4 KB attacker pages and uses mmap for 4KB page-table page allocations. As such, page-table pages are likely to be placed onto vulnerable pages next to attacker pages.

memcached item allocation policy: A memcached architec-

ture manages key-value pairs, which are stored in-memory as *items*. The corresponding data structure for each item is struct \_stritem and it has different sizes ranging from 96 bytes to 1 MB. The memcached maintains a singly linked list, i.e., hash chain, which stores different keys but with the same hashes (i.e., colliding keys). The hash is computed by a hash function with the key as an input. However, the function is not cryptographically secure and thus its computed hash value can be resulted from different keys. First, the attacker [14], as a remote client process, issues numerous SET requests to the memcached for crafting many 1 MB items in which each key is hashed to the same value. These items are chained together and can be read by the attacker. Then, the attacker sends a DELETE request to force the memcached to free a target 1 MB item, and then issues GET requests to lure the memcached into reusing the 1 MB item for smaller-sized item allocations, with the hope that one smaller item will land on a vulnerable DRAM location.

**Page cache eviction policy:** To boost system performance, Linux manages unused page frames as page cache. If a memory-mapped file is released by a process, Linux still keeps its data in the page cache. If the file is accessed again, Linux does not have to load the file from non-volatile storage such as disks and instead serves the access quickly from page cache. Linux considers pages in the page cache as available memory and thus will evict obsolete file data from these pages to load recently accessed files. Gruss et al. [5] observe that if Linux evicts file data from a pagecache page frame, it reloads the evicted file data onto a different page frame upon access. By abusing the eviction policy repeatedly, the attackers can relocate sensitive code of a setuid process onto vulnerable pages [5].

**Page table update policy in paravirtualization:** In Xen paravirtualization, each paravirtualized VM fills its page table entries with physical page frame numbers (PFNs) rather than pseudo PFNs. To isolate each VM, Xen hypervisor enforces an invariant that a VM cannot write its page tables directly. Instead, the VM must invoke a hypercall for page table updates. However, the VM is allowed to specify page frames that host its page tables. With this key observation, Xiao et al. [11] can place a target page-table page onto a specified vulnerable page frame without breaking the hypervisor-enforced invariant.

#### 3.2 Hammering Attacker-Induced Objects

The attacker-induced objects refer to either user data that are explicitly created and accessed by the attacker, or kernel data that are implicitly created and accessed by the attacker (i.e., a confused deputy). For example, page tables are implicitly created for the attacker's memory mapping and they can be accessed implicitly by the attacker through address translation [42].

For both types of attacker-induced objects, they will be first served from the processor caches as a modern integrated processor has a cache hierarchy to effectively reduce the time of accessing requested data in DRAM memory. To enable accessing the objects from the memory, the attacker has to refrain from using the cache of the processor. Alternatively, the attacker can abuse the feature of Direct Memory Access (DMA) to bypass the cache and achieve the

| Objective   |            | Technique                                                                                                                   |  |

|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Avoid using | CPU cache  | explicit cache-flush instruction<br>non-temporal instruction<br>(Intel CAT-assisted) cache eviction<br>direct memory access |  |

|             | GPU cache  | cache eviction                                                                                                              |  |

|             | row buffer | different hammer patterns                                                                                                   |  |

TABLE 2: A taxonomy of different techniques proposed by rowhammer attacks in avoiding CPU cache, GPU cache and row buffer.

same goal. As row buffer stores recently accessed data in a DRAM bank and acts like the cache, the attacker must also bypass row buffer before each target memory access. With bypassing cache and row buffer, the attacker can hammer the attacker-induced objects if explicitly or implicitly accessing them is frequent enough.

#### 3.2.1 Refraining from using CPU/GPU cache

As shown in Table 2, there are four techniques that have been proposed to avoid using either CPU or GPU cache and thus induce a DRAM memory access, that is, *explicit cache-flush instruction, non-temporal instruction, cache eviction* and *direct memory access*. In the following, each technique is introduced in detail.

**Explicit cache-flush instruction:** Existing x86-based rowhammer attacks have identified a couple of unprivileged instructions to explicitly flush the CPU cache, i.e., clflush and clflushopt. We note that clflush is available in all Intel-based microarchitectures while clflushopt is only available since the recent Intel 6th generation microarchitectures (e.g., SkyLake). Besides clflushopt outperforming clflush in terms of micro-ops, clflushopt alone can also result in a memory access, which makes itself a better instruction for hammering [32].

Non-temporal instruction: Alternatively, the attacker can invoke unprivileged non-temporal instructions to perform write access to data directly into memory and thus bypass CPU cache. Qiao et al. [46] and BitMine [47] have thoroughly analyzed non-temporal instructions on Intel microarchitectures and presented a string of available instructions, i.e., movnti, movntdq, movntpd, movntps, movntq, maskmovq and maskmovdqu.

Cache eviction: As CPU/GPU cache has limited capacity, the attacker can evict a target address from either CPU [7] or GPU [44] by accessing a set of many enough virtual addresses. The addresses in the set are congruent in a way that they are mapped to the same cache set and the same cache slice as the target address. This technique is particularly useful when launching an attack in a browser sandbox environment where the cache-flush and non-temporal instructions are not available. As Intel cache allocation technology (CAT) [48] allows system software to partition the CPU cache, each subset of the cache is dedicated to a process or virtual machine to mitigate cache thrashing. In such a case, the cache capacity for a process decreases significantly, indicating that the number of congruent addresses in the eviction set will decrease as well. Aga et al. [49] have abused Intel CAT to facilitate a rowhammer attack.

**Direct memory access:** Last, the attacker can access uncached memory directly by abusing the DMA feature. The DMA memory is marked as uncached and thus accessing it will bypass the CPU cache. Unlike the non-temporal instructions that require write access, DMA access can be any type, i.e., write, read or execute. In the x86 architecture, both Throwhammer [14] and Nethammer [39] launch the attack by sending network packets directly into DMA memory. In the ARM platform, Drammer [8] can access DMA memory even in a local unprivileged process.

#### 3.2.2 Bypassing Row buffer

As row buffer resides in each bank, the processor and peripheral devices cannot clear row buffer explicitly. To this end, the attacker can leverage the hammer patterns introduced in Section 2.2.1 to clear row buffer implicitly. For one-location hammer, the attacker only needs to access the target object addresses and waits for the memory controller to clear the row buffer. In the single-sided hammer, the attacker accesses several randomly picked addresses besides the target-object addresses. Clearly, these two hammer patterns are much less effective than double-sided hammer in DDR3 modules and many-sided hammer in DDR4 modules. To implement the latter hammer patterns, the attacker must know which rows to access and thus requires (partial) mappings from virtual addresses to physical addresses, physical addresses to logical DRAM addresses and logical to physical DRAM address.

For the last two mappings, they are either available from public documentation or have been reverse-engineered as discussed in Section 2.1. For the first mapping, an unprivileged process can acquire it through the *pagemap* interface but the interface has been restricted to root users since Linux version 4.0 [50] to mitigate rowhammer. Alternatively, the attacker can abuse the feature of huge page in the x86 architecture or Android ION in the ARM architecture to request a large block of continuous physical memory. Within the large memory, it is highly likely to find multiple samebank rows.

#### 3.2.3 Frequently Accessing Attacker-Induced Objects

Most attacks require putting objects explicitly created by the attacker onto aggressor rows and apply different techniques in Table 2 to avoid processor caches and row buffer for hammering the objects, which is coined as *explicit hammer* [42].

For objects that are implicitly created, the attacker cannot access them explicitly and instead she can use a benign entity to implicitly access the objects, the so-called *implicit hammer* [42]. The entity can be hardware (e.g., the processor) or software (e.g., system call handler). For instance, PThammer uses the page-table-walk feature of CPU while GhostKnight [51] abuses the speculative execution feature of CPU for implicit hammer. To trick the benign entity into frequently accessing the objects, the effective way for bypassing the caches is restricted to cache eviction [42].

#### 3.3 Exploiting Bit Flips

The consequences of the bit flips are devastating to the system security. In this section, we introduce how existing attacks, originating from different hardware, with different assumptions, exploit the bit flips to either crash the system (i.e., DoS) or break different forms of memory isolation in different architectures, as shown in Table 1. For meaningful rowhammer attacks, they exploit bit flips to break memory isolation, with the objective of gaining privilege escalation, leaking sensitive information or degrading inference accuracy of target deep neural network (DNN). In the following, we categorize existing attacks based on their respective objectives.

#### 3.3.1 Causing Denial-of-service

An attacker can demonstrate a DoS attack either locally or remotely. Both SGX-Bomb [4] and Gruss et al. [5] have demonstrated local DoS attack by abusing a feature of Intel SGX [52], i.e., data integrity check. Specifically, an SGX enclave has a physically contiguous memory region, which is encrypted in DRAM and protected from nonenclave memory accesses. If data in the enclave memory is corrupted, the corruption will be detected by SGX's memory encryption engine (MEE), resulting in a system halt. With this observation, the attacker can simply apply for an SGX enclave and induce a single bit flip in the enclave memory to make the whole system unresponsive.

Compared to local attacks, remote attacks do not require code execution from the attacker. Specifically, Nethammer [39] simply sends crafted network packets repeatedly to a target system. To handle the packets, the system frequently accesses (read, write or execute) relevant memory. If the system applies techniques in Table 2, bit flips can be induced remotely in the system and some of them can occur in the file system, thus crashing the entire system.

#### 3.3.2 Gaining Privilege Escalation

**Targeting browser:** A browser sandbox provides a browsercontrolled environment where an untrusted program is running with restricted permissions, separating untrusted code from trusted code within the same process. There are five attacks that have leveraged a malicious program to break the sandbox environment and gain privilege escalation. Among them, one uses native code and four are based on JavaScript code.

Google native client provides a sandboxing environment to run validated instructions from mainstream architectures such as x86 and ARM. Seaborn et al. [6] are the first to demonstrate a Chrome sandbox escape. Particularly, a malicious native client program uses bit flips to corrupt opcodes of validated instructions and turns them into unsafe ones, enabling arbitrary calls of host OS's syscalls. Gruss et al. [7] perform the first attack to escape a Firefox browser by crafting JavaScript code in a website and corrupting page tables through bit flips. SMASH [40] corrupts metadata of a JavaScript ArrayBuffer and compromises the latest Firefox browser of 2021. Bosman et al. [15] are the first to compromise a Microsoft Edge browser through rowhammer. They abuse the page deduplication feature to craft counterfeit JavaScript Uint8Array objects and corrupt the objects with bit flips, resulting in an arbitrary read/write primitive within the browser. GLitch [44] is the first rowhammer attack originating from integrated graphics processing unit (GPU) on a mobile platform, which corrupts elements of JavaScript ArrayObject and escapes a Firefox sandbox.

**Targeting memcached server application:** A memcached server application allows a remote client process to send network packets directly into a specified memory region, the so-called remote DMA (RDMA). Throwhammer [14] is the first attack that uses RDMA-enabled NIC to compromise the entire memcached server application with arbitrary write and code execution. It abuses the memcached item allocation policy to corrupt memcached items by simply issuing network packets without requiring any local code execution

Targeting setuid process: setuid is for set user ID on execution, which is a type of file permission in Unix-like operating systems such as Linux. When an unprivileged user launches a binary with setuid, the binary will run with root privilege rather than the user privilege. Gruss et al. [5] mount the first attack as an unprivileged process against a setuid process. They break MMU-enforced interprocess isolation and bypass all existing defenses prior to their proposed attack. Particularly, they abuse the page cache eviction policy to corrupt opcodes of critical branches in the setuid process, resulting in root privilege escalation.

**Targeting Kernel:** Kernel is one of the most appealing target and there are four attacks breaking user-kernel isolation and corrupting page tables, resulting in kernel privilege escalation from an unprivileged native process.

Specifically, Seaborn et al. [6] mount the first rowhammer attack against kernel in the x86 architecuture. They propose abusing the mmap interface to spray the last-level page-table pages, some of which will be placed adjacent to attackeraccessible pages. CATTmew [41] demonstrate the first attack against CATT [53], the first DRAM-aware user-kernel isolation. They have observed the so-called memory-ownership weakness of CATT, that is, there exist kernel buffers that are still accessible to unprivileged users in the presence of CATT. With this observation, they hammer video buffers or SCSI Generic buffers and trigger bit flips in some page tables created by mmap. PThammer [42] introduces the first implicit hammer-based attack, which tricks the CPU into hammering page tables, resulting in other page table corruption. Drammer [8] performs the first rowhammer attack in the ARM architecture. It abuses the page frame allocation policy of Linux buddy allocator to surgically induce bit flips in a target page-table entry.

**Targeting paravirtualized hypervisor:** In Xen paravirtualization, a VM has no write access but only read access to its own page tables. Thus, the VM's page table updates must be approved by the underlying hypervisor. Xiao et al. [11] propose the first rowhammer attack against the paravirtualized hypervisor. They abuse the page table update policy in paravirtualization to flip bits in page tables and gain write access to them, thus breaking the MMU-enforced VMhypervisor isolation and gaining the hypervisor privilege.

Targeting victim HVM: Compared to the paravirtual VM, a hardware-assisted VM (HVM) is unaware of underlying hypervisor and other HVMs. dFFS [12] demonstrates the first rowhammer attack against a KVM-based HVM from another HVM. It abuses the page deduplication feature to corrupt targeted files (i.e., OpenSSH public keys, Debian URLs in sources.list and trusted public keys in trusted.gpg) residing in the page cache of a victim HVM, compromsing the MMU-enforced inter-HVM isolation and

gain full control of the victim HVM.

#### 3.3.3 Leaking sensitive information

**Targeting cryptographic algorithm:** Cryptographic algorithms have been applied to many security-sensitive scenarios such as digital signature, data confidentiality, integrity authentication. RSA, as a public-key cryptosystem, is one of most widely used asymmetric cryptography algorithms. It has been implemented in various secure data transmission protocols and thus becomes the attack targets for three rowhammer attacks.

Specifically, Bhattacharya et al. [16] are the first to induce a single bit flip fault in the secret exponent of RSA public key exponentiation in the GNU-MP big integer library. Based on a faulty digital signature generated by the faulty key, they can leak the secret exponent. Similarly, JackHammer [17] induces bit flip faults in the WolfSSL RSA implementation, resulting in faulty signatures. We note that JackHammer mounts the first attack originating from an Accelerator Functional Unit (AFU) implemented in Field Programmable Gate Array (FPGA) logic. RAMBleed [18] is the first attack that uses rowhammer-induced bit flips as a read primitive to break inter-process isolation and leak an RSA key from the OpenSSH daemon.

**Targeting DNN model:** As training a model is resourceintensive and the relevant training data is sensitive., how to protect intellectual property of a DNN model on both server and mobile platforms has attracted a great deal of attention from security researchers. Similar to RAMBleed, DeepSteal [19] also uses the rowhammer bit flip as a read primitive and they are the first to leak weights from a target DNN model through this primitive.

#### 3.4 Degrading target DNN model

DNN has been pervasively used in many security-sensitive scenarios, such as autonomous driving, image classification, and malware detection, duo to its stunning inference accuracy. Hong et al. [20] mount the first rowhammer attack from an unprivileged process against a full-precision DNN model process. They break inter-process isolation and drastically change the weight values of a target model, which significantly degrades the inference accuracy of the model even without knowledge of the model. Following their work, Yao et al. [21] assume that they have knowledge of a quantized model, abuse the per-CPU page-frame cache update policy to corrupt specified weights in each model layer, reducing the model's average inference accuracy to random guess.

## **4 ROWHAMMER DEFENSES**

To mitigate rowhammer attacks, various countermeasures have been proposed from either hardware or software side. Hardware-based defenses eliminate or correct rowhammerinduced bit-flip faults and they require modifications to underlying hardware (e.g., memory controller and DRAM modules), making them unable to be backported. Unlike them, software-only defenses are compatible with legacy DRAM modules, which allows them better deployability in existing hardware.

|              | Objective                                                                  | Software Defense                        | Requirement                     |

|--------------|----------------------------------------------------------------------------|-----------------------------------------|---------------------------------|

|              | Double DRAM row refresh rate                                               | Computer manufacturers [54], [55], [56] | BIOS updates                    |

| Ad-Hoc       | Disallow cache-flush instructions<br>Disallow non-temporal instructions    | Chrome browser [57], [58]               | Browser sandbox updates         |

| Attempt      | Remove non-root access to pagemap                                          | Linux kernel [59]                       | Kernel updates                  |

|              | Disable page deduplication                                                 | VMWARE ESXi [60]                        | Hypervisor updates              |

|              | Reinforce user-kernel isolation                                            | CATT [53]                               |                                 |

|              | Reinforce inter-process isolation                                          | RIP-RH [61]                             |                                 |

| DRAM-Aware   | Reinforce RDMA-enabled DMA buffer isolation                                | ALIS [14]                               | Kernel updates                  |

| Isolation    | Reinforce ION-enabled DMA buffer isolation                                 | GuardION [45]                           | -                               |

|              | Reinforce page-table isolation                                             | CTA [62]                                |                                 |

|              | Reinforce intra-HVM isolation                                              | ZebRAM [63]                             | Kernel and hypervisor updates   |

|              | Reinforce inter-HVM isolation<br>Reinforce HVM-hypervisor isolation        | Future Exploration                      |                                 |

|              | Detect abnormal CPU cache misses<br>Detect abnormal memory-access patterns | ANVIL [64]                              | Add-on kernel module            |

| RH-Triggered | Detect abnormal EM emanations                                              | RADAR [10]                              | Software-defined radio device   |

| Detection    | Detect abnormal binary code                                                | MASCAT [65]                             | User-space static analysis tool |

|              | Detect abnormal row-access patterns                                        | SoftTRR [66]                            | Add-on kernel module            |

|              | Detect abnormal DRAM-consumed power                                        | Future Exploration                      |                                 |

TABLE 3: A taxonomy of software defenses. For the discussion about future explorations, please refer to Section 5.2.

#### 4.1 Software-only Defenses

Existing software-only defenses are proposed to defend commodity systems against rowhammer attacks and they can be classified into three categories, that is, ad-hoc attempts, DRAM-aware isolation and RowHammer(RH)triggered detection, as shown in Table 3. Each of them aims to mitigate the attack step **1** or **2**. In the following, we discuss each category in detail.

#### 4.1.1 Ad-Hoc Attempts

We introduce four major countermeasures in this category. *First*, multiple computer manufacturers such as Apple [54], HP [55], Lenovo [56] provide BIOS updates to double the DRAM refresh rate, that is, the DRAM refresh period is decreased from 64 ms to 32 ms. However, ANVIL [64] still can induce bit flips in the doubling refresh rate. Even worse, Kim et al. [22] observe that a bit flip can occur in mainstream DDR4 chips within 1 ms. Second, although Google chrome browser has disallowed the use of both explicit cache-flush instructions [57] and non-temporal instructions [58], there still are other available techniques in avoiding CPU cache in Table 2. Third, since version 4.0, Linux kernel removes nonroot access to the pagemap interface [59], which prevents potential attackers from acquiring the mapping from a virtual address to a physical address. Clearly, the countermeasure is not effective, as discussed in Section 3.2.2. Last, the page deduplication feature has been turned off by default only to mitigate specific attacks [12], [15] in commodity cloud platforms [60].

#### 4.1.2 DRAM-Aware Isolation

This category of defenses separates security-sensitive memory from attacker-accessible memory in DRAM by putting guarding rows in between. By doing so, the attackerinduced bit flips are absorbed by the guarding rows and will not affect target security domain. Existing schemes reinforce MMU-enforced isolation at different granularities to protect different security domains [53], [61], [63], [14], [45], [62].

**Reinforced user-kernel isolation:** To defend against rowhammer attacks targeting the kernel, CATT [53] parti-

tions the DRAM rows within each bank into two parts– one part for the user domain and the other part for the kernel domain, and uses at least one empty row to separate the two domains. As the empty rows will absorb the bit flips from the user domain, the kernel's integrity is protected.

**Reinforced page-table isolation:** As all existing kernelprivilege-escalation attacks target corrupting page tables, CTA [62] aims to reinforce DRAM-aware page table isolation. It proposes a two-step approach. In the first step, pagetable pages are allocated from a dedicated memory region that have high physical addresses and reside at the end of the memory space. In the second step, rows with true cells are selected from the memory region for page-table allocation. As the dedicated memory region is not separated from the rest memory region with guarding rows, a bit flip can occur in the page-frame-number field of a page-table entry (PTE). However, the corrupted PTE will only point to a new physical address lower than the original one and it will never point to another PTE. Thus, the attacker cannot gain access to a page-table page.

**Reinforced inter-process isolation:** To prevent rowhammer attacks targeting security-sensitive process such as setuid, RIP-RH [61] enforces DRAM-aware memory isolation for the targeted processes by segregating their physical memory into dedicated DRAM areas. As such, these processes are not allowed to share memory with other processes. Otherwise, the attacker can hammer the shared memory.

**Reinforced DMA isolation:** There are two reinforced DMA isolation schemes, that is, ALIS [14] on x86 and GuardION [45] on ARM. Specifically, ALIS surgically isolates DMA memory with guarding rows and thus every attacker-generated bit flip is confined to guarding rows, defending against Throwhammer [14]. Similar to ALIS, GuardION [45] mitigates DMA-based attacks particularly on mobile devices by isolating DMA buffers using guarding rows.

**Intra-HVM Isolation:** ZebRAM aims to protect an operating system in hardware-assisted virtualization (i.e., HVM) against all attacks. It leverages the hypervisor to split DRAM rows of a target HVM into two regions in a zebra pattern, that is, even rows for safe system data and odd rows for unsafe swap space. Thus, hammering even rows is effective in inducing bit flips in adjacent odd rows of swap space. However, hammering odd rows is too slow to incur a single bit flip in adjacent even rows where system data reside. For potentially corrupted data in the swap space, ZebRAM performs data integrity check before using them.

# 4.1.3 RH-Triggered Detection

In the aforementioned attack step ②, existing rowhammer attacks require hammering target objects, which results in abnormal software/hardware side effects. We note that MAD [67] detects meaningful rowhammer attacks that have abnormal behaviors in memory allocations. However, it has not been evaluated on a commodity system (e.g., security effectiveness and performance overhead) and thus is not listed in Table 3.

**Detecting abnormal CPU cache misses and memory-access patterns:** As a large majority of attacks has two characteristics, that is, high CPU cache misses and high spatial locality of memory accesses. ANVIL [64] proposes a two-step approach based on Intel-provided performance monitoring counters (PMCs). In the first step, it monitors CPU last-level cache (LLC) miss rate. If the miss rate becomes greater than a predefined threshold, it starts to sample physical addresses of memory accesses that miss the LLC in the second step. If the sampled addresses exhibit a high temporal locality, i.e., in the same DRAM bank, it will refresh rows adjacent to rows of the sampled addresses.

**Detecting abnormal binary code:** As shown in Table 1, most rowhammer attacks originate from CPU and present typical attributes of using explicit cache-flush instructions, non-temporal instructions or cache eviction sets for avoid-ing CPU caches. With this observation, Irazoqui et al. [65] implement a static analysis tool, coined MASCAT, to identify the typical rowhammer attributes within target binary code. They note that the tool is an extensible framework and can include other rowhammer attributes.

**Detecting abnormal EM emanations:** With a key observation that hammering activities emanate distinguishable electromagnetic (EM) signals, RADAR [10] leverages a \$299 radio-based external device to capture EM signals emanated from DRAM. After the EM emanations are processed, RADAR can expose recognizable hammering-correlated sideband patterns in the spectrum of the DRAM clock signal. To achieve effectiveness and robustness classification, RADAR feeds hammering-correlated spectrograms into a convolutional neural network (CNN) for training. If the CNN's inference indicates an ongoing rowhammer activity, RADAR can kill suspicious processes.

**Detecting abnormal row-access patterns:** With the same goal as in CTA [62], SoftTRR [66] is a software-only target-row-refresh technique that prevents page tables from being corrupted. Specifically, SoftTRR leverages the rsrv bits in page table entries to frequently track accesses to any rows that are adjacent to rows hosting page tables. When the tracked access counter reaches a pre-determined threshold, refreshes will be performed to corresponding rows with page tables.

# 4.1.4 Summary of Software Defenses

While the ad-hoc attempts clearly have security issues and have been discussed in Section 4.1.1, we, in the following, discuss the major limitations of the other two categories in Table 3 based on whether they hold their security objectives and whether they are applicable to real-world systems.

## Limitations of DRAM-aware isolation schemes:

- They are not practical. All of them have limited scope in their achieved objective while require modifying the memory allocator either in the kernel or the hypervisor to enforce DRAM-aware memory allocation, making them hard to adopt in commodity systems.

- They are not scalable. As rowhammer affects nonadjacent rows, the blast radius from a hammered row is highly dependent on specific DRAM chips. Based on the observation from Kim et al. [22], the blast radius of some chips can be up to 6. Thus, the defense need to determine the blast radius for given chips and waste the rows within the blast radius as the guarding rows or the swap-space memory.

- They are not secure. All these defenses except CTA [62] rely on the invalid assumption that logical and physical DRAM addresses are the same. Thus, they ignore the DRAM row remapping.

#### Limitations of RH-Triggered Detection schemes:

- RADAR [10] are not practical as it requires an antenna to be placed at a specific position and orientation for receiving EM signals. Besides, individuals and companies may not afford an external radio device worth of \$299 for each computer system.

- All the other schemes are not secure. Specifically, both ANVIL [64] and MASCAT [65] cannot defend against attacks that originate from non-CPU hardware components such as GLitch [44]. SoftTRR [66]'s implementation is ineffective in cases where the rowhammer blast radius is greater than 6-row.

#### 4.2 Hardware Defenses

As shown in Table 4, we classify existing hardware defenses into four categories, i.e., data integrity check, row activation count, row-activation-triggered probabilistic refresh and fabrication process improvement, among which some are from industry while the rest are from academia. They aim to reduce or prevent rowhammer-induced bit flips, which are introduced below.

#### 4.2.1 Data Integrity Check

This category of defenses uses different algorithms to detect or even correct bit flips by performing data integrity check.

**MC-Aware DRAM-based ECC:** As cosmic rays or alpha particles [100], [101] can corrupt data in DRAM chips accidentally, ECC is proposed to address the data-corruption problem by storing additional parity bits in separate chips next to the data bits in the original chips. Theoretically, ECC can correct  $n \ (n \ge 1)$  bit flips and detect more than n bit flips. An industrial use case of ECC is single-error-correction-double-error-detection (SECDED) hamming code. In this case, ECC functions are implemented

|                                          | Objective                                                       | Hardware Defense                                                                            | Prototype Location                   |

|------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------|

| Data Integrity                           | Correct/Detect bit flips                                        | MC-Aware DRAM-based ECC [68]                                                                | MC and DRAM<br>Additional DRAM chips |

| Check                                    | concer, beact on mps                                            | On-die ECC [69]<br>(Future Exploration*)                                                    | DRAM                                 |

|                                          | Detect bit flips                                                | Dynamic Skewed Hash Tree [70]                                                               | MC                                   |

|                                          | Detect bit hips                                                 | Dummy Cells [71]                                                                            | DRAM                                 |

|                                          |                                                                 | on-die TRR [36]<br>Panopticon [72]                                                          | DRAM                                 |

|                                          |                                                                 | CAT [73]<br>Graphene [74]                                                                   | MC                                   |

|                                          |                                                                 | CRĂ [75]                                                                                    | MC and DRAM                          |

|                                          |                                                                 | TWiCe [76]                                                                                  | DRAM (RCD)                           |

|                                          |                                                                 | Mithril [77]                                                                                | DRAM and/or MC                       |

|                                          | Refresh specific rows                                           | Silver Bullet [78], [79]<br>Bains et al. [80]                                               | MC or DRAM                           |

| Row Activation<br>Count                  |                                                                 | Bains et al. [81]<br>Greenfield et al. [82]<br>Bains et al. [83]<br>Cowles et al. [84]      | MC                                   |

|                                          |                                                                 | Bains et al. [85]<br>Fisch et al. [86]<br>Greenfield et al. [87]<br>Kim [88]<br>ProTRR [89] | DRAM                                 |

|                                          | Throttle specific row activations                               | BlockHammer [90]<br>Patent [91]                                                             | MC                                   |

| Row-Activation-Triggered                 |                                                                 | PARA [3]                                                                                    | MC                                   |

| Probabilistic Refresh                    | Refresh specific rows probabilistically                         | PRoHIT [92]<br>MRLoc [93]                                                                   | МС                                   |

| Cache Miss/Flush and<br>DMA Access Count | Relocate targeted data and/or<br>Disable DMA access temporarily | LightRoAD [94]                                                                              | МС                                   |

| Fabrication Process<br>Improvement       | Mitigate electromagnetic coupling                               | Yang et al. [95]<br>Gautam et al. [96]<br>Gautam et al. [97]<br>Gautam et al. [98]          | DRAM                                 |

|                                          | Reduce acceptor-type traps                                      | Ryu et al. [99]                                                                             | DRAM                                 |

TABLE 4: A taxonomy of hardware defenses. (Whether on-die ECC is effective against rowhammer has not been studied.)

in the MC on commodity processors, that is, the MC has 8bit hamming SECDED code with every 64-bit data. Thus, the data bus between DRAM and MC is extended from 64 bits to 72 bits and each rank has an extra chip to store ECC code. This MC-Aware DRAM ECC was believed to deter rowhammer-based attacks until ECCploit [102] in 2019 demonstrated that it was susceptible to rowhammer by inducing enough (e.g., 3) bit flips in a single code word (e.g., 72 bits).

To reinforce the MC-Aware DRAM-based ECC against rowhammer, a couple of new defenses [103], [104] have been proposed. Particularly, they use row-remapping schemes to distribute bit-flips to different rows, which significantly reduces the occurrences where undetectable multiple bit-flip errors occur in a single word. Further, the design principle of future ECC is expected to put more weight on its detection capability rather than its correction capability [105], thus achieving a better detection of rowhammer.

**On-die ECC:** Different from the aforementioned ECC, ondie ECC, as its name suggests, is integrated directly into the same DRAM chips and invisible to the MC [69], [106]. As the on-die ECC operates entirely within the same DRAM chips, it is adopted by mainstream DRAM manufacturers to reduce the data-corruption rates in new generations of DRAM chips (e.g., LPDDR4 [24] and DDR5 [25]). As the DRAM manufacturers consider the on-die ECC functions as proprietary, its details cannot be found in public documentation and have been reverse-engineered in recent works [106], [107], [108]. Similar to the traditional ECC, on-die ECC is also effective against rowhammer bit flips to some extent, and we note that *it is worth investigating whether on-die ECC memory is susceptible to rowhammer.*

**Dynamic Skewed Hash Tree:** Vig et al. [70] propose a lightweight scheme within the MC to check data integrity. Particularly, they apply a sliding window protocol to identify potentially corrupted victim rows and use a dynamic integrity tree structure with SHA-3 Keccak hash functions for bit-flip detection.

**Dummy Cells:** Gomez et al. [71] propose the so-called *dummy cells* to perform data integrity checks. Compared to regular cells, the dummy cells are intrinsically more susceptible to rowhammer as they have smaller capacitance and larger transistors. Every row will contain a dummy cell that is fully charged during the DRAM refresh time. If the MC reads out a row with its dummy cell value bit-flipped, it indicates an early warning of data loss and thus the MC can refresh it and its adjacent rows.

#### 4.2.2 Row Activation Count

In theory, DRAM or MC manufacturers can apply a hardware counter to count the number of activations per row within a DRAM refresh period. If the count for a row exceeds a predefined threshold, either its adjacent rows are refreshed, or further accesses to this row are throttled. However, allocating one counter per row is expensive in terms of area and energy cost and thus this category of solutions proposes optimization algorithms at different levels of the DRAM organization.

**Row-Level Count with One Counter per Row:** CRA [75], as an early scheme published in 2014, maintains a counter per row using a portion of the DRAM memory. In such a case, every time a row is activated, its counter needs to be updated, resulting in doubled memory-access latency. To reduce the latency, CRA implements a cache of recently updated counters within the MC. Thus, a row counter is accessed from DRAM if it cannot be found from the cache. Similar to CRA, Panopticon [72], a recent scheme in 2021, also maintains a counter in DRAM for each row. Unlike CRA, Panopticon rearranges DRAM's subarrays' layout in a staggered way, and thus a counter can be updated alongside a row activation.

Row-Level Count with One Counting Logic per Bank: DRAM manufacturers implement different schemes of ondie Target Row Refresh (TRR) [36] to prevent data in DRAM from being flipped. As its name suggests, TRR counts rows that are being activated and refreshes their adjacent rows when the counts reach a predefined threshold. Similar to the on-die ECC, the on-die TRR is also publicly undocumented. Although security cannot be achieved only through obscurity, the DRAM manufacturers still advertise their TRR-equipped DRAM chips as rowhammer-free. Recently, different TRR implementations from three major DRAM manufacturers have been reverse-engineered [35], [109]. Based on the reverse-engineered results, a typical TRR implementation that implements a bank-level counter table, for instance, only counts a limited number (e.g., 16) of different rows within the same bank.

TWiCe [76] manages a counter table for each DRAM bank in the register clock driver (RCD), which is inside a DIMM but separated from chips. Each entry of the counter table comprises of a valid bit, a row address, an activation counter, and a lifetime counter. When a row is being activated, TWiCe increments its activation counter if it exists in the table, otherwise allocates a spare entry. If the counter reaches a predefined threshold, its adjacent rows are refreshed. For every periodic DRAM refresh command, TWiCe starts to prunes the table. When a row's average activation rate is lower than a specific threshold during its lifetime, its entry is pruned with its valid bit set to 0. After each pruning, the remaining entries' lifetime counters are incremented. Whenever a row's activation count reaches the threshold value, TWiCe will issue a new command called Adjacent Row Refresh (ARR) by extending the DRAM protocol to inform the DRAM of the aggressor row's address, which will then refresh the adjacent victim rows.

Graphene [74], implemented in the MC, maintains a counter table and a spillover counter for each DRAM bank. Each entry of the counter table uses a row address as the key and an estimated counter as the value. The spillover counter is a special register and its value represents the upper bound of ACT command counts for all rows which are currently not in the table. Graphene uses the Misra-Gries algorithm to track aggressor rows. Specifically, upon

a row activation, if the row address is already in the table, the relevant estimated counter is incremented by one. If the address is not in the table and the table is not full, it will be inserted into the table with the estimated counter set to one. If the table is full, Graphene first checks whether there is an entry whose estimate counter is equal to the spillover counter. If there is, it replaces this entry with the row address that needs to be inserted and increments the existing estimated counter by one. Otherwise, it skips the row address by simply increasing the spillover counter by one. In order not to miss more new row addresses, both the counter table and spillover counter are reset periodically. Within each reset window, if a row's estimated counter reaches a threshold, Graphene will issue a new nearby row refresh (NRR) command by extending the DRAM protocol to refresh the row's adjacent rows. To prevent non-adjacent rowhammer bit flips, Graphene can modify the number of rows that the NRR command covers. Similarly, Mithril [77] leverages a newly introduced DRAM command called refresh management (RFM) in DDR5 [25] to implement a customized Misra-Gries algorithm. ProTRR [89] proposes an in-DRAM Misra-Gries algorithm to optimize TRR. Unlike Graphene, these two defenses do not require any change to the DRAM protocol.

Instead of refreshing the potential victim rows in advance, BlockHammer [90] proactively throttles memory accesses that are considered malicious. Implemented in the MC, BlockHammer contains two components: RowBlocker and AttackThrottler. RowBlocker employs two counting bloom filters per bank to alternately track the activation rates of all DRAM rows in a rolling time window. If a row's activation rate exceeds a predefined threshold, RowBlocker will blacklist this row. RowBlocker also maintains a firstin-first-out (FIFO) history buffer per rank to record rows that have been activated in the last fixed time window of  $t_{Delay}$ . If a row is not only blacklisted but also in the history buffer (i.e., recently activated), RowBlocker will block any further activations to this row for  $t_{Delay}$  to prevent the row from being further hammered. Based on the results from RowBlocker, AttackThrottler cuts the memory bandwidth provided to threads that are identified as potential attackers, thus allowing co-running benign threads to have higher performance when accessing memory.

Similarly, most existing patents count row activations in a specified time period (e.g., tREFI) by maintaining a counting logic per memory portion (e.g., DRAM bank). If a row's activation count exceeds a predefined threshold, either its victim rows will be refreshed [87], [81], [85], [80], [82], [86], [83], or subsequent ACT commands sent to the row will be throttled [91].

**RowSet-Level Count:** CAT [73] applies one counter to a set of rows and every access to rows within the set will be counted. However, in an intuitive implementation where rows are evenly assigned to each counter, some counters can become quite "busy" and some remain "idle", as benign workloads in production computing environments have memory access locality and specific memory regions of rows are accessed more often ("hot") than other memory regions. To address this problem, CAT leverages *adaptive trees* to dynamically update the number of rows one counter

manages. By doing so, more counters are allocated for a "hot" memory region and less counters are for a "cold" memory region.