# Performance Investigation of p-FETs Based on Highly Air-stable Mono-layer Pentagonal PdSe<sub>2</sub>

Keshari Nandan, *Graduate Student Member, IEEE*, Amit Agarwal, Somnath Bhowmick, and Yogesh S. Chauhan, *Fellow, IEEE*

Abstract-Pentagonal PdSe2 is a promising candidate for layered electronic devices, owing to its high air-stability and anisotropic transport properties. Here, we investigate the performance of p-type FET based on PdSe2 mono-layer using multiscale simulation framework combining Density functional theory and quantum transport. We find that mono-layer PdSe2 devices show excellent switching characteristics (< 65 mV/decade) for the source-drain direction aligned along both [010] and [100] directions. Both directions also show good on-state current and large transconductance, though these are larger along the [010] direction for a 15 nm channel device. The channel length scaling study of these p-FETs indicates that channel length can be easily scaled down to 7 nm without any significance compromise in the performance. Going below 7 nm, we find that there is a severe degradation in the sub-threshold swing for 4 nm channel length. However, this degradation can be minimized by introducing an underlap structure. The length of underlap is determined by the trade-off between on-state current and the switching performance.

Index Terms—Field-effect transistors (FETs), Density functional Theory (DFT), Maximally-localised Wannier functions (MLWFs), Non-equilibrium Greens function (NEGF), Quantum Transport (QT).

## I. INTRODUCTION

THE demonstration of mono-layer molybdenum disulfide  $(MoS_2)$  based FET by Radisavljevic  $et\ al.\ [1]$  in 2011 opened up the field for exploration of layered materials' based FETs for future technology nodes. Since then, there has been remarkable progress on the synthesis of layered materials and devices based on them. Both the material and device communities are actively exploring novel 2D materials [2] and device concepts based on them. Several promising devices viz. two-dimensional electrostrictive field-effect transistor (2D-EFET) [3], Dirac-source FET (DS-FET) [4], and dual transport FET (DT-FET) [5] have been demonstrated employing these materials properties, in the last five years.

Beyond  $\mathrm{MoS}_2$  [6]–[8], several other layered materials have been explored for device applications. Most of them are isotropic, but some of them show interesting anisotropic behavior. The isotropic/anisotropic property is a consequence

This work was partially supported by the Humboldt Foundation and the Swarnajayanti Fellowship (Grant No. – DST/SJF/ETA-02/2017-18) of the Department of Science and Technology (DST), Government of India.

K. Nandan and Y. S. Chauhan are with the NanoLab, Department of Electrical Engineering, Indian Institute of Technology Kanpur, India, 208016, e-mail: keshari@iitk.ac.in, chauhan@iitk.ac.in.

A. Agarwal is with the Department of Physics, Indian Institute of Technology Kanpur, India.

S. Bhowmick is with the Department of Material Science and Engineering, Indian Institute of Technology Kanpur, India.

of high/low lattice symmetry. The anisotropic materials, with hexagonal buckled or puckered structure such as phosphorene [9]–[12], silicene [13], [14], arsenene [15], [16], germanene [17], [18], and stanene [19], have great potential for device application, but their realization in a stable form is still a great challenge. Stability is one of the most important parameters for a material to be considered for electronic applications and large-scale production.

Motivated by this, we study the electronic properties and device characteristics of mono-layer PdSe2 based devices. It is another low symmetric material that has no soft modes in their mono- and few- layers' phonon spectrum [20], [21]. Experimentally, it has been shown that the air-stability of pentagonal-PdSe<sub>2</sub> is higher (> 60 days) than other puckered and buckled layered materials [20]. The experimental band gap value is 1.3 eV for this mono-layer. This band gap value indicates an excellent semiconductor that can absorb light for electronic and optoelectronic devices. This value is not far from silicon, and it is satisfactory for logic switches to sharply discriminate between two logic states. Till now, only few-layer pentagonal-PdSe<sub>2</sub> based FETs have been demonstrated [20], [22], and, hence the performance for mono-layer is unknown. Mono-layer of pentagonal PdSe2 has better electrical transport properties for holes than electrons [21]. Hence, We have chosen to study p-type FET.

In contrast to conventional materials (bulk Si/Ge, III-V), for new materials, the device simulation becomes more challenging as their characterization parameters are not known. Thus, we start from first-principles calculations of the electronic properties and use these to construct tight-binding (TB) Hamiltonian within maximally-localised Wannier functions (ML-WFs) basis. Our device simulations are based on the effective TB model [23]–[28], which makes them computationally more efficient, compared to first-principles based device simulation approaches. Our device simulations reveal the following:

- The best performance of our devices meets the highperformance (HP) expections of International Technology Roadmap for Semiconductors (ITRS) 2013 for the year 2028.

- 2) The best performance of our device for low power (LP) fulfils  $\sim 51\%$  requirement of ON current mentioned in ITRS 2013 roadmap for the year 2028.

- 3) Our device's best performance is better than Si FinFET (see Table III).

This paper is organized as follows: The methodology is described in section II. Results and discussion on electronic

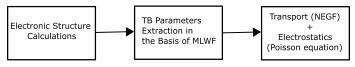

**Fig. 1: Methodology:** Schematic of simulation flow (from DFT to QT). It starts with solving the Kohn-Sham equation for a relaxed and periodic system, followed by Wannier transformation and device simulation.

structures and device performance are presented in section III, and the conclusive remarks are given in section IV.

#### II. METHODOLOGY

Figure 1 shows the simulation methodology used in this work and this methodology is described as follows:

# A. Electronic Structure Calculations

We use Quantum Espresso (QE) [29], [30], a Density-functional theory (DFT) based tool, for electronic structure calculations from first-principles. The Projector Augmented Wave method (PAW) [31], [32] with a plane wave basis set is used for the DFT calculations. The exchange correlation effect are approximated by the generalized gradient approximation (GGA) within the Perdew-Burke-Ernzerhof (PBE) formulation [33]. The energy cutoffs for wave-functions and charge-density are set to 60 Ry and 600 Ry, respectively. The Brillouin zone is sampled using  $10 \times 10 \times 1$  Monkhorst-Pack grids [34]. A 30 Å thick vacuum layer is used in simulations to avoid the interaction between spurious neighboring layers in the out of plane direction. The primitive unit cell structure is optimized until all components of forces are less than  $10^{-3}$  Ry/a.u..

# B. Maximally-localised Wannier Functions (MLWFs) Tight-Binding Hamiltonian

First-principles calculations provide the electronic structure in terms of Bloch states. The Bloch states corresponding to conduction and valance bands, which lie near the band gap, are mapped to MLWFs using the Wannier90 suite of codes [35] in continuous space of unitary matrices [36]–[38]. Five d-orbitals and three p-orbitals of each Pd and each Se atom are used to generate an initial guess for mapping of Bloch states, to capture eighteen highest valance bands and four lowest conduction bands. Once the Wannier functions (WFs) are known, the on-site energy and hopping parameters are calculated to generate the elements of Hamiltonian matrix  $(H_{ijk}^{mn})$ . The  $H_{ijk}^{mn}$  couples m<sup>th</sup> Wannier function in the home unit cell (0,0,0) to the n<sup>th</sup> Wannier function in the unit cell (i,j,k). Using unit cell coupling terms, we construct the device Hamiltonian, which is given as input to the NEGF solver.

#### C. Device Simulations

At each bias point  $(V_{GS}, V_{DS})$ , Non-equilibrium Green's functions (NEGF) and Poisson equation are solved self-consistently to obtain the converged values of charge, potential, and transmission coefficient for the device. In this formalism, transmission coefficient can be expressed as,

$$T(E, k, V_{GS}, V_{DS}) = Trace[\Gamma_L(E, k, V_{GS}, V_{DS})G^R(E, k, V_{GS}, V_{DS})] G^R(E, k, V_{GS}, V_{DS})].$$

(1)

Here,  $G^R$  and  $G^A = [G^R]^\dagger$  are retarded and advance Green functions, respectively.  $\Gamma_{L/R} (=i[\Sigma_{L/R} - \Sigma_{L/R}^\dagger])$  is the broadening from left/right contacts.  $\Sigma_{L/R}$  is the left/right contact self-energy matrix. k is the wave-vector in transverse (channel width) direction.

The current is calculated using the Landauer-Büttiker approach [39]. The source to darin current  $(I_{SD})$  for a given bias  $(V_{GS}, V_{DS})$  can be expressed as,

$$I_{SD}(V_{GS}, V_{DS}) = \frac{2q}{h} \int_{-\infty}^{\infty} \sum_{k} T(E, k, V_{GS}, V_{DS})$$

$$[f(E - \mu_D) - f(E - \mu_S)] dE , \qquad (2)$$

Equation. 2 can also be written as,

$$I_{SD}(V_{GS}, V_{DS}) = \int_{-\infty}^{\infty} I_{SD}(E, V_{GS}, V_{DS}) dE ,$$

where,  $V_{GS}$  and  $V_{DS}$  are gate to source and drain to source voltages, respectively. q is the elementry charge, h is the Planck constant,  $T(E,V_{GS},V_{DS})=\sum_k T(E,k,V_{GS},V_{DS})$  is the transmission coefficient at Energy E for a given bias  $(V_{GS},V_{DS}),\ \mu_{S/D}$  is the chemical potential at source/drain, and  $f(E-\mu_{S/D})$  is the Fermi-Dirac distribution function at source/drain.

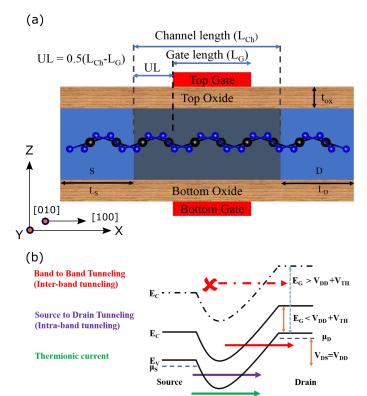

The  $I_{SD}$  has three components, namely thermionic  $(I_{thermal})$ , source-to-drain tunneling  $(I_{SDT})$  and BTBT  $(I_{BTBT})$  currents. These components shown in Fig. 3 (b), can be expressed as,

$$I_{thermal}(V_{GS}, V_{DS}) = \int_{-\infty}^{E_{V_{min},Ch}} I_{SD}(E, V_{GS}, V_{DS}) dE ,$$

$$I_{SDT}(V_{GS}, V_{DS}) = \int_{E_{V_{min},Ch}}^{E_{V,source}} I_{SD}(E, V_{GS}, V_{DS}) dE ,$$

$$(3b)$$

$$I_{BTBT}(V_{GS}, V_{DS}) = \int_{E_{V,source}}^{\infty} I_{SD}(E, V_{GS}, V_{DS}) dE ,$$

$$(3c)$$

Here,  $E_{V_{min},Ch}$  and  $E_{V,source}$  are the minimum valance band energy level in the channel and valance band energy level in the source.  $I_{SD}(E,V_{GS},V_{DS})$  is current value at energy E for given bias  $(V_{GS},V_{DS})$ .

We use Poisson and NEGF modules implemented in NanoTCAD ViDES suites of codes [26]. Periodic boundary conditions in the transverse direction are considered using 30 uniform wave vector points. Transport is assumed to be ballistic in nature due to short channel length used in this work. All transport simulations are performed at room temperature  $(T=300\ K)$ .

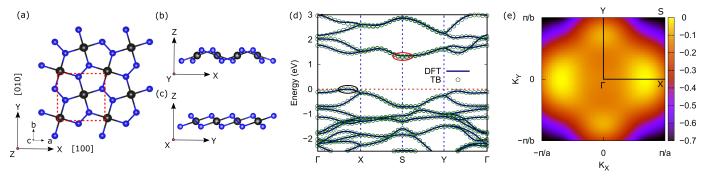

Fig. 2: Geometric and Electronic Structures: (a) Top view, (b) side view in x-z plane, and (c) side view in y-z plane of pentagonal PdSe<sub>2</sub>. The Crystallographic directions [100] and [010] are equivalent to X and Y directions of Cartesian coordinate system. The blue and red balls represent Pd and Se atoms, respectively. The dotted red color rectangle in (a) is primitive unit cell of the system. (d) Comparison of energy bands calculated from DFT and tight binding Hamiltonian (in MLWF basis) along high symmetry paths ( $\Gamma$ -X-S-Y- $\Gamma$ ) in Brillouin zone for mono-layer of pentagonal-PdSe<sub>2</sub>. VBM is shifted to zero energy. (e) Contour plot of the highest valance band. High symmetry points and transport directions are also indicated in (e).

#### III. RESULTS

# A. Geometric and Electronic Structures

Figure 2 (a) shows the top view and (b) and (c) show side view along two different lateral directions of pentagonal PdSe<sub>2</sub> mono-layer. The mono-layer of pentagonal-PdSe<sub>2</sub> is buckled type and belongs to the space group  $P2_1/c$ . This mono-layer is a net of pentagonal networks, and each network consists of two Pd and three Se atoms (see Fig. 2 (a)). We start with the experimental bulk structure having lattice parameters a = 5.741 Å, b = 5.886 Å, and c = 7.691 Å. Then, we take out mono-layer structure from bulk and optimize it with 30 Å thick vacuum layer in the |z|-direction. Comparison of optimized lattice constants (a and b) and bond lengths ( $d_{Pd-Se}$  and  $d_{Se-Se}$ ) with earlier works is shown in Table I. It's clear from Table I that our values are consistent with earlier results [20], [21], [40]–[42].

Figure 2 (d) shows the electronic band structure of monolayer pentagonal-PdSe $_2$  from DFT (navy blue line) and TB (hollow green circle) along the high symmetry path ( $\Gamma$ -X-S-Y- $\Gamma$ ). The red and black color circles in Fig. 2 (d) indicate the location of conduction band minima (CBM) and valance band maxima (VBM), respectively. The band gap value is 1.35 eV (indirect) and is very close to experimental value ( $E_{\rm G,exp} \sim 1.3 \pm 0.2 {\rm eV}$ ) [20]. The band structure from TB shows good agreement with DFT in the vicinity of VBM. The VBM lies on the way from  $\Gamma$  to X, hence the valley degeneracy is two. Figure 2 (e) shows the contour plot of the highest valance band. In the plot, symbols and black lines indicate the high symmetry points ( $\Gamma$ , X, S, Y) and transport directions ([100] ( $\Gamma$ -X) and [010] ( $\Gamma$ -Y)), respectively.

**TABLE I:** The optimized lattice constants (a and b) and bond lengths between Pd-Se and Se-Se for mono-layer pentagonal  $PdSe_2$ .

| Work                       | a (Å), b (Å)   | $d_{Pd-Se}$ (Å), $d_{Se-Se}$ (Å) |

|----------------------------|----------------|----------------------------------|

| This work                  | 5.748, 5.923   | (2.457, 2.469), 2.420            |

| Soulard et al. [40] (Exp.) | 5.7457, 5.8679 |                                  |

| Lan et al. [21]            | 5.74, 5.91     | (2.45, 2.46), 2.41               |

| Deng et al. [41]           | 5.749, 5.495   |                                  |

| Qin et al. [42]            | 5.7538, 5.9257 |                                  |

| Oyedele et al. [20]        | 5.72, 5.93     |                                  |

Fig. 3: Device Structure and Current Components: (a) Schematic of the device under investigation.  $L_{\rm Ch}$  and  $L_{\rm S/D}$  are channel length and source/drain extension.  $L_{\rm G}$  is gate length. UL is underlap length.  $t_{\rm ox}$  is thickness of top and bottom gate oxide. (b) The schematic of p-MOSFET band diagram in the OFF state for two different conditions of  $E_{\rm G}$  ( $E_{\rm V}$  is taken as reference): i) if  $E_{\rm G} < V_{\rm DD} + V_{\rm T}$  (solid black line represents  $E_{\rm C}$ ) and ii) if  $E_{\rm G} > V_{\rm DD} + V_{\rm T}$  (dashed black line represent  $E_{\rm C}$ ). The red, violet, and green arrows indicate the path for thermionic, SDT, and BTBT, respectively. A large  $E_{\rm G}$  in this material ensures the condition  $E_{\rm G} > V_{\rm DD} + V_{\rm T}$ . Hence, BTBT is negligible in our devices.

## B. Electrical Characteristics and Performance Metrics

Figure 3 (a) shows the schematic of the device. The device is a double gate (DG) MOSFET. The gate oxide is  $\mathrm{SiO}_2$ , and the thicknesses of top and bottom gate oxides are the same. The channel material is pentagonal-PdSe $_2$ . The source/drain is highly doped with p-type doping density of  $2\times10^{17}~m^{-2}$ .  $L_{\mathrm{Ch}}$ ,  $L_{\mathrm{G}}$ ,  $t_{\mathrm{ox}}$ ,  $L_{\mathrm{S/D}}$  and UL, which are geometrical parameters of

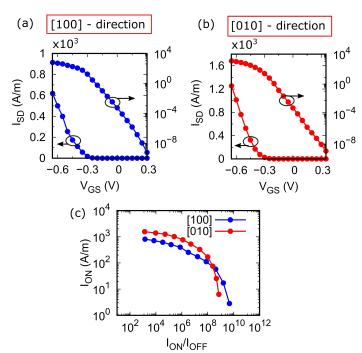

Fig. 4: Transfer Characteristics:  $I_{SD}$  vs  $V_{GS}$  of FET for transport direction (a) [100] and (b) [010] with  $L_{\rm Ch} \sim 15.50$  nm. The UL length and EOT are 0.0 nm and 0.6 nm, respectively. The power supply voltage ( $V_{\rm DD}$ ) is 0.5V. (c) ON current ( $I_{\rm ON}$ ) vs ON-OFF ratio ( $I_{\rm ON}/I_{\rm OFF}$ ).

the device, represent channel length, gate length, oxide thickness, source/drain extension, and underlap length, respectively.

1) Transfer Characteristics and the On Current: Figure 4 (a) and (b) show the transfer characteristics of the device for channel with transport directions along [100] and [010] axes. The channel length is 15.50 nm without underlap (i.e.,  $L_{\rm Ch}=L_{\rm G}$ ), the supply voltage ( $V_{\rm DD}$ ) is 0.50 V, and the source/drain extension region ( $L_{\rm S/D}$ ) is 10 nm. For this channel length, source-to-drain tunneling (SDT) is negligible. The band-to-band tunneling (BTBT) is also negligible due to large band gap of this material. Figure 4 (c) shows the ON current ( $I_{\rm ON}$ ) vs. ON/OFF ratio ( $I_{\rm ON}/I_{\rm OFF}$ ) for both transport directions.  $I_{\rm ON}$  is one of the important metrics for logic switches, because the maximum operating speed is pro-

**TABLE II:** Performance comparison of mono-layer pentagonal PdSe<sub>2</sub>\*\* p-FETs against International Roadmap for Devices and Systems (IRDS) 2020\* [43] requirements for the year 2034.

|        | $L_{G}$ | Transport | UL   |           | I <sub>ON</sub> | $I_{OFF}$ |

|--------|---------|-----------|------|-----------|-----------------|-----------|

|        | (nm)    | direction | (nm) | mV/decade | (A/m)           | (A/m)     |

|        | ~ 15.50 | [100]     | 0.00 | 61        | 618             | $10^{-1}$ |

|        | ~ 15.50 | [100]     | 0.00 | 61        | 463             | $10^{-2}$ |

|        | ~ 15.50 | [100]     | 0.00 | 61        | 176             | $10^{-4}$ |

|        | ~ 15.50 | [010]     | 0.00 | 63        | 1205            | $10^{-1}$ |

|        | ~ 15.50 | [010]     | 0.00 | 63        | 883             | $10^{-2}$ |

|        | ~ 15.50 | [010]     | 0.00 | 63        | 348             | $10^{-4}$ |

| Y-2034 |         |           |      |           |                 |           |

| HP     | 12      | -         | -    | 70        | 1504            | $10^{-2}$ |

| LP     | 12      | -         | -    | 65        | 861             | $10^{-4}$ |

$<sup>^*</sup>V_{\rm DD}$  = 0.55 V;  $^{**}V_{\rm DD}$  = 0.50 V, EOT = 0.60 nm, and  $\rm L_{\rm S/D}$ =10 nm.

portional to  $I_{\rm ON}$ . For  $I_{\rm ON}/I_{\rm OFF}\sim 10^4~(10^5)$ , ON current for [010] direction  $I_{\rm ON-[010]}~(\sim 1.38\times 10^3 A/m~(1.14\times 10^3 A/m))$  is approximately double than ON current for [100] direction  $I_{\rm ON-[100]}~(\sim 6.86\times 10^2 A/m~(5.23\times 10^2 A/m))$ . The reason for higher ON current in the [010] direction compared to the [100] direction is smaller effective mass in the [010] direction,  $(m_{[010]}^*\sim 0.25m_o)$  than [100]  $(m_{[100]}^*\sim 0.40m_o)$ .

We benchmark the performance of mono-layer pentagonal PdSe<sub>2</sub> p-FETs against International Roadmap for Devices and Systems (IRDS) 2020 [43] requirements for the year 2034 in Table II. According to the IRDS roadmap, option for the logic device is lateral gate-all-around (LGAA)-3D for the year 2034. The [010] ([100]) transport direction based p-FETs meets  $\sim 41\%$  (21%) and  $\sim 60\%$  (31%) requirement of ON current expected in IRDS roadmap for LP and HP applications, respectively.

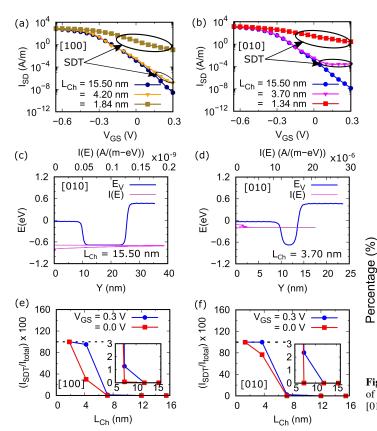

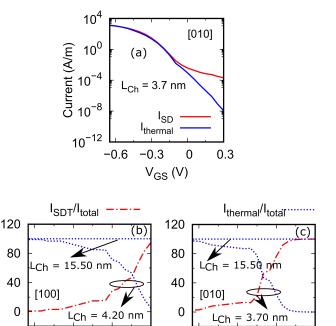

2) Channel Length Scaling: Now, we scale the channel length to study the impact of SDT on the device performance. The SDT decides the limit of gate length scaling [44] and plays a significant role in determining the subthreshold slope (SS) and, hence OFF current ( $I_{\rm OFF}$ ) at short channel length. Figure 5 (a) and (b) show the transfer characteristics for different channel lengths with transport directions along [100] and [010]. The EOT, UL, and  $V_{\rm DD}$  are 0.60 nm, 0.0 nm, and 0.50 V, respectively. The effect of SDT is more prominent for [010] transport direction than [100], because tunneling probability from source to drain is proportional to  $exp(-\sqrt{m^*})$  [45] and  $m_{[010]}^{st} < m_{[100]}^{st}$  . Figure 5 (c) and (d) show the energy resolved current spectrum and valance band for  $L_{Ch} = 15.50$  and 3.70 nm, channel with transport direction [010] for  $(V_{DS}, V_{GS})$ = (0.50, 0.30) V, which clearly indicate that  $I_{SDT}$  majorly contributes to  $I_{SD}$  for  $L_{Ch}$  = 3.70 nm. We plot the contribution percentage of  $I_{SDT}$  to  $I_{total}$  vs.  $L_{Ch}$  at  $V_{GS}$  = 0.3 and 0.0 V in Fig. 5 (e) and 5 (f). For short channel lengths ( $\sim 1.5$  and 4.0 nm), the contribution of  $I_{SDT}$  is  $\sim 100\%$  to  $I_{total}$  (i.e.,  $I_{total} \simeq I_{SDT}$ ) for both transport directions at  $V_{GS} = 0.30$ V. But, for  $V_{GS}$  = 0.00 V and  $L_{Ch} \sim 4$  nm, it decreases to  $\sim 30\%$  and  $\sim 75\%$  for tansport directions [100] and [010], respectively. For  $L_{\rm Ch} > 10$  nm, the contribution is  $\sim 0\%$  (i.e.,  $I_{total} \simeq I_{thermal}$ ) for both transport directions at  $V_{GS} = 0.0$ V and 0.3 V. For  $V_{GS}$  = 0.3 V and  $L_{Ch} \sim 7$  nm, it is  $\sim 1\%$ and 2.5% for transport directions [100] and [010], respectively. Whereas, for  $V_{GS}$  = 0.0 V and  $L_{Ch} \sim 7$  nm, the contribution is 0% for both transport directions. Figure 6 (a) shows the thermionic part of total current and total current vs.  $V_{GS}$  for transport direction [010] and  $L_{\rm Ch}$  = 3.70 nm. The contribution percentage of  $I_{SDT}$  to  $I_{total}$  and  $I_{thermal}$  to  $I_{total}$  vs.  $V_{GS}$ for transport directions [010] and [100] are shown in Fig. 6 (b) and (c), respectively.

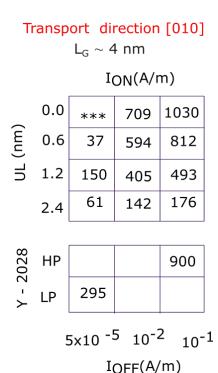

The benchmarking of [010] transport direction (because this transport direction gives best performance) based p-FETs against ITRS 2013 requirements for the year 2028 is shown in Fig. 9. For LP applications, the OFF state current is not meeting expected ITRS requirements. For HP applications, our device shows 15% more ON current than expected in ITRS roadmap. Our simulations provide an upper-performance limit, as the transport is assumed to be ballistic in nature.

Fig. 5: Channel Length Scaling: Transfer characteristics for different values of  $L_{\rm Ch}$  (down to  $\sim 1.5$  nm) for transport directions (a) [100] and (b) [010]. Energy resolved current spectrum for (c)  $L_{\rm Ch}=15.50$  nm and (d)  $L_{\rm Ch}=3.70$  nm for transport direction [010]. The contribution percentage of  $I_{SDT}$  to  $I_{total}$  (=  $I_{SDT}+I_{thermal}$ ) vs  $L_{\rm Ch}$  for transport directions (e) [100] and (f) [010]. Insets in (e) and (f) show the contribution percentage for 5 nm <  $L_{\rm Ch}$  <15.50 nm.

However, the effect of phonon-scattering is very weak for short-channel devices. For  $\sim 10$  nm channel length, at least  $\sim 80\%$  ballisticity has been shown for  $MoS_2$  [46] and BP [47] based FETs. In fact, > 90% ballisticity is reported for channel length below 5 nm [46].

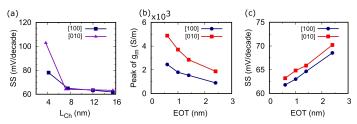

3) Gate Control: In addition to  $I_{\rm ON}$ , SS and  $g_m$  are crucial figures of merit for device performance. They reveal the gate control in the sub-threshold and above-threshold region. Smaller value of SS indicates better gate control.

Figure 7 (a) shows that variation of SS with  $L_{\rm Ch}$ . The SS degradation in transport direction [010] is more prominent than [100]. The excellent switching characteristics (SS < 70 mv/decade) are seen in both transport directions for  $L_{\rm Ch} >$  7 nm. For  $L_{\rm Ch} <$  7 nm, SDT plays a significant role in deciding OFF-current and SS (see Table II, Fig. 7 (a), 5 (e), and 5 (f)).

The variation of gate control parameters peak of  $g_m$  and SS with EOT are shown in Fig. 7 (b) and (c). The  $g_m$  is given by,

$$g_m = \frac{\partial I_{DS}}{\partial V_{GS}},\tag{4}$$

**Fig. 6:** (a)  $I_{thermal}$  and  $I_{SDT}$  vs.  $V_{GS}$ , (b) and (c) contribution percentage of  $I_{SDT}$  and  $I_{thermal}$  to  $I_{total}$  vs.  $V_{GS}$  for transport direction [100] and [010], respectively.

0.3

and, hence

-0.6

-0.3

$V_{GS}(V)$

0

$$g_m \propto v_h \frac{\partial Q_{Ch}}{\partial V_{GS}}.$$

(5)

-0.6

-0.3

$V_{GS}(V)$

0

0.3

The density of states (D(E)) determines  $\partial Q_{Ch}/\partial V_{GS}$  and is given by,

$$D(E) = \frac{g_s g_v m_o}{2\pi\hbar^2} \sqrt{m_{[100]}^* m_{[010]}^*}$$

(6)

where,  $g_s$  and  $g_v$  are spin and valley degeneracy.  $Q_{Ch}$  is channel charge and  $v_h$  is carrier velocity.

We find that both control parameters degrade almost linearly with EOT. The  $g_m$  is higher for the [010] direction because small variation in  $V_{GS}$  leads to same amount of change in channel charge (as D(E) is independent of channel orientation) for both transport directions and carrier velocity is more in [010] than [100] direction. In this work, we consider the gate as an ideal insulated electrode, but thin gate oxide leads to gate leakage current and hence, insulator thickness has a limit.

Fig. 7: Gate Control Parameters : (a) SS vs  $L_{\rm Ch}.$  (b) Peak transconductance vs EOT. (c) SS vs EOT.

Fig. 8: Underlap Scaling: Transfer characteristics for transport directions (a) [100] for  $L_{\rm G}=4.20$  nm and (b) [010] for  $L_{\rm G}=3.70$  nm for different UL lengths. (c) SS vs. UL length for the same  $L_{\rm G}$  in (a) and (b). (d) Valance band diagram of device for transport direction [100] for different UL lengths. The contribution percentage of  $I_{SDT}$  to  $I_{total}$  vs UL lengths for transport directions (e) [100] and (f) [010]. EOT = 0.60 nm,  $V_{\rm DD}=0.50$  V.

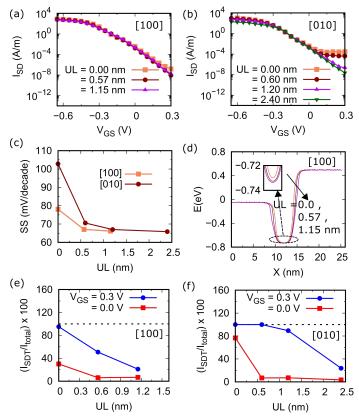

4) Underlap Scaling: The tunneling width and the barrier height play vital roles in reducing the SDT at short channel length, which in turns leads to weaker gate control. Gate underlap [48] structures overcome these shortcomings by increasing the effective channel length and consequently the tunneling width and the barrier height. But, a large underlap region can degrade the device performance, because the gate has better control underneath gate length region in channel compared to the UL region. Therefore, the UL length has to be optimized. Figure 8 (a) and (b) show the transfer characteristics for different UL lengths for  $L_{\rm G}\sim 4$  nm for channel orientation along [100] and [010] directions. The SS vs UL length is plotted in Fig. 8 (c) to see the effect of UL length on gate control in sub-threshold region.

The impact of SDT in transport direction [100] is lower than in [010] and hence, in [100] channel, when UL length is increased from 0.0 to 1.15 nm, the contribution percentage of  $I_{SDT}$  to  $I_{total}$  reduces from  $\sim$  100% to 30% for  $V_{GS}$  = 0.3 V and 30% to 6% for  $V_{GS}$  = 0.0 V (see Figure 8 (e)), which in turn reduces the SS from  $\sim$  78 to 66 mV/decade ( $I_{\rm ON}$  drops by  $\sim$  30%). However, in [010] channel, when UL is increased from 0.0 to 2.4 nm, the contribution percentage of  $I_{SDT}$  to  $I_{total}$  for  $V_{GS}$  = 0.3 V reduces from  $\sim$  100% to 30% and for  $V_{GS}$  = 0.0 V, 30% to 4% (see Figure 8 (f)), which in turn reduces the SS from  $\sim$  103 to 66 mV/decade ( $I_{\rm ON}$  drops by

Fig. 9: Performance comparison of mono-layer pentagonal  $PdSe_2^{**}$  p-FETs against ITRS 2013\* [49] requirements for the year 2028. \* $V_{\rm DD} = 0.64$  V, EOT = 0.41 nm; \*\* $V_{\rm DD} = 0.50$  V, EOT = 0.60 nm, and  $L_{\rm S/D}$ =10 nm; \*\*\* $I_{\rm OFF}$  requirement can not be reached.

$\sim 83\%$ ).

Figure 9 shows the benchmarking of p-FETs ( $L_{\rm G} \sim 4 {\rm nm}$  and [010] transport direction) against ITRS 2013 requirements. For LP applications: (i) without underlap, the OFF state current is not meeting expected ITRS requirements, (ii) introduction of underlap structure with UL = 0.60 nm and 1.20 nm meet  $\sim 13\%$  and 51% requirement of on current expected in ITRS roadmap, respectively, and (iii) further increasing the UL leads to decrease in on current. For HP applications, UL = 0.60 nm, 1.20 nm, and 2.40 nm meet  $\sim 90\%$ , 55%, and 20% requirement of ON current expected in ITRS roadmap.

#### IV. CONCLUSION

We have studied the electronic structure and device characteristics of p-FETs based on mono-layers of pentagonal PdSe<sub>2</sub>. We explicitly calculate the TB parameters of monolayer PdSe<sub>2</sub> in the MLWF basis. Using these TB parameters we solve the coupled Poisson and Schrödinger equations, via recursive non-equilibrium Green's function formulation. We found that: (1) p-FETs show anisotropic transport behavior, (2) [010] oriented channel gives superior on-state performance than [100] oriented channel almost double ON current and  $g_m$ , (3)  $I_{ON}$  (>  $10^3$  A/m) is higher for transport direction [010] for  $I_{\rm ON}/I_{\rm OFF}\sim 10^4$  and  $10^5,$  (4) Both transport directions show the sub-threshold slope less than 65 mV/decade, (5) the impact of SDT is more pronounced for the [010] oriented channel than [100] for very short channel length, (6) our device meets the HP ON current expected in ITRS 2013 roadmap for the year 2028, and (7) for LP, the upper performance limit of device meets  $\sim 52\%$  ON current expected in ITRS 2013 roadmap for

**TABLE III:** Comparison of p-FET with experimental data of Si based FinFET technology.  $I_{\rm OFF} \sim 10^{-1} A/m$ .

|                         | $L_{G}$  | $V_{\mathrm{DD}}$ | SS      | $I_{ON}$ | $I_{ON}$             |

|-------------------------|----------|-------------------|---------|----------|----------------------|

|                         | (nm)     | (V)               | mV/dec. | (A/m)    | $I_{ m OFF}$         |

| DG FinFET [50]          | 10       | 1.2               | 125     | 446      | $4.46 \times 10^{3}$ |

| GAA FinFET [51]         | 5        | 1.0               | 208     | 497      | $4.97 \times 10^{3}$ |

| PdSe <sub>2</sub> p-FET | $\sim 4$ | 0.5               | 103     | 1030     | $1.03 	imes 10^4$    |

the year 2028. We expect that our findings may pave the way for realizing mono-layer pentagonal PdSe<sub>2</sub> based p-FETs in the near future.

#### V. ACKNOWLEDGMENT

K. Nandan thanks Prof. Amit Verma for fruitful discussions on electron transport, Barun Ghosh for help with first principles calculations, and Dr. Sarvesh S. Chauhan for his valuable feedback.

#### REFERENCES

- B. Radisavljevic, A. Radenovic, J. Brivio, V. Giacometti, and A. Kis, "Single-layer mos2 transistors," *Nature Nanotechnology*, vol. 6, no. 3, pp. 147–150, Mar 2011, doi: 10.1038/nnano.2010.279.

- [2] K. S. Novoselov, "Graphene: Materials in the flatland (nobel lecture)," Angewandte Chemie International Edition, vol. 50, no. 31, pp. 6986–7002, 2011, doi: 10.1002/anie.201101502.

- [3] S. Das, "Two dimensional electrostrictive field effect transistor (2d-efet): A sub-60mv/decade steep slope device with high on current," *Scientific Reports*, vol. 6, no. 1, p. 34811, Oct 2016, doi: 10.1038/srep34811.

- [4] C. Qiu, F. Liu, L. Xu, B. Deng, M. Xiao, J. Si, L. Lin, Z. Zhang, J. Wang, H. Guo, H. Peng, and L.-M. Peng, "Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches," *Science*, vol. 361, no. 6400, pp. 387–392, 2018, doi: 10.1126/science.aap9195.

- [5] N. Oliva, J. Backman, L. Capua, M. Cavalieri, M. Luisier, and A. M. Ionescu, "Wse2/snse2 vdw heterojunction tunnel fet with subthermionic characteristic and mosfet co-integrated on same wse2 flake," npj 2D Materials and Applications, vol. 4, no. 1, p. 5, Apr 2020, doi: 10.1038/s41699-020-0142-2.

- [6] Y. Yoon, K. Ganapathi, and S. Salahuddin, "How good can monolayer mos2 transistors be?" *Nano Letters*, vol. 11, no. 9, pp. 3768–3773, 2011, doi: 10.1021/nl2018178.

- [7] D. Lembke and A. Kis, "Breakdown of high-performance monolayer mos2 transistors," ACS Nano, vol. 6, no. 11, pp. 10070–10075, 2012, doi: 10.1021/nn303772b.

- [8] L. Zeng, D. Zhang, T. Gao, F. Gong, X. Qin, M. Long, Y. Zhang, and W. Zhao, "Performance evaluation and optimization of single layer mos2 double gate transistors with schottky barrier contacts," *IEEE Transactions on Electron Devices*, vol. 64, pp. 2999–3006, 2017.

- [9] H. Liu, A. T. Neal, Z. Zhu, Z. Luo, X. Xu, D. Tománek, and P. D. Ye, "Phosphorene: An unexplored 2d semiconductor with a high hole mobility," ACS Nano, vol. 8, no. 4, pp. 4033–4041, 2014, doi: 10.1021/nn501226z.

- [10] L. Kou, C. Chen, and S. C. Smith, "Phosphorene: Fabrication, properties, and applications," *The Journal of Physical Chemistry Letters*, vol. 6, no. 14, pp. 2794–2805, 2015, doi: 10.1021/acs.jpclett.5b01094.

- [11] A. Carvalho, M. Wang, X. Zhu, A. S. Rodin, H. Su, and A. H. Castro Neto, "Phosphorene: from theory to applications," *Nature Reviews Materials*, vol. 1, no. 11, p. 16061, Aug 2016, doi: 10.1038/natrevmats.2016.61.

- [12] F. Liu, Y. Wang, X. Liu, J. Wang, and H. Guo, "Ballistic transport in monolayer black phosphorus transistors," *IEEE Transactions on Electron Devices*, vol. 61, no. 11, pp. 3871–3876, 2014, doi: 10.1109/TED.2014.2353213.

- [13] P. Vogt, P. De Padova, C. Quaresima, J. Avila, E. Frantzeskakis, M. C. Asensio, A. Resta, B. Ealet, and G. Le Lay, "Silicene: Compelling experimental evidence for graphenelike two-dimensional silicon," *Phys. Rev. Lett.*, vol. 108, p. 155501, Apr 2012, doi: 10.1103/PhysRevLett.108.155501.

- [14] L. Tao, E. Cinquanta, D. Chiappe, C. Grazianetti, M. Fanciulli, M. Dubey, A. Molle, and D. Akinwande, "Silicene field-effect transistors operating at room temperature," *Nature Nanotechnology*, vol. 10, no. 3, pp. 227–231, Mar 2015, doi: 10.1038/nnano.2014.325.

- [15] C. Kamal and M. Ezawa, "Arsenene: Two-dimensional buckled and puckered honeycomb arsenic systems," *Phys. Rev. B*, vol. 91, p. 085423, Feb 2015, doi: 10.1103/PhysRevB.91.085423.

- [16] G. Pizzi, M. Gibertini, E. Dib, N. Marzari, G. Iannaccone, and G. Fiori, "Performance of arsenene and antimonene double-gate mosfets from first principles," *Nature Communications*, vol. 7, no. 1, p. 12585, Aug 2016, doi: 10.1038/ncomms12585.

- [17] Z. Ni, Q. Liu, K. Tang, J. Zheng, J. Zhou, R. Qin, Z. Gao, D. Yu, and J. Lu, "Tunable bandgap in silicene and germanene," *Nano Letters*, vol. 12, no. 1, pp. 113–118, 2012, doi: 10.1021/nl203065e.

- [18] A. Acun, L. Zhang, P. Bampoulis, M. Farmanbar, A. van Houselt, A. N. Rudenko, M. Lingenfelder, G. Brocks, B. Poelsema, M. I. Katsnelson, and H. J. W. Zandvliet, "Germanene: the germanium analogue of graphene," *Journal of Physics: Condensed Matter*, vol. 27, no. 44, p. 443002, oct 2015, doi: 10.1088/0953-8984/27/44/443002.

- [19] S. Saxena, R. P. Chaudhary, and S. Shukla, "Stanene: Atomically thick free-standing layer of 2d hexagonal tin," *Scientific Reports*, vol. 6, no. 1, p. 31073, Aug 2016, doi: 10.1038/srep31073.

- [20] A. D. Oyedele, S. Yang, L. Liang, A. A. Puretzky, K. Wang, J. Zhang, P. Yu, P. R. Pudasaini, A. W. Ghosh, Z. Liu, C. M. Rouleau, B. G. Sumpter, M. F. Chisholm, W. Zhou, P. D. Rack, D. B. Geohegan, and K. Xiao, "Pdse2: Pentagonal two-dimensional layers with high air stability for electronics," *Journal of the American Chemical Society*, vol. 139, no. 40, pp. 14 090–14 097, 2017, doi: 10.1021/jacs.7b04865.

- [21] Y.-S. Lan, X.-R. Chen, C.-E. Hu, Y. Cheng, and Q.-F. Chen, "Penta-pdx2 (x = s, se, te) monolayers: promising anisotropic thermoelectric materials," *J. Mater. Chem. A*, vol. 7, pp. 11134–11142, 2019, doi: 10.1039/C9TA02138H.

- [22] F. Giubileo, A. Grillo, L. Iemmo, G. Luongo, F. Urban, M. Passacantando, and A. Di Bartolomeo, "Environmental effects on transport properties of pdse2 field effect transistors," *Materials Today: Proceedings*, vol. 20, pp. 50–53, 2020, doi: j.matpr.2019.08.226.

- [23] S. Datta, Quantum transport: atom to transistor. Cambridge university press, 2005.

- [24] M. Luisier, A. Schenk, W. Fichtner, and G. Klimeck, "Atomistic simulation of nanowires in the  $sp^3d^5s^*$  tight-binding formalism: From boundary conditions to strain calculations," *Phys. Rev. B*, vol. 74, p. 205323, Nov 2006, doi: 10.1103/PhysRevB.74.205323.

- [25] J. Guo, M. Lundstrom, and S. Datta, "Performance projections for ballistic carbon nanotube field-effect transistors," *Applied Physics Letters*, vol. 80, no. 17, pp. 3192–3194, 2002, doi: 10.1063/1.1474604.

- [26] S. Bruzzone, G. Iannaccone, N. Marzari, and G. Fiori, "An open-source multiscale framework for the simulation of nanoscale devices," *IEEE Transactions on Electron Devices*, vol. 61, no. 1, pp. 48–53, 2014, doi: 10.1109/TED.2013.2291909.

- [27] P. Rastogi, T. Dutta, S. Kumar, A. Agarwal, and Y. S. Chauhan, "Quantum confinement effects in extremely thin body germanium n-mosfets," *IEEE Transactions on Electron Devices*, vol. 62, no. 11, pp. 3575–3580, 2015, doi: 10.1109/TED.2015.2477471.

- [28] T. Dutta, P. Kumar, P. Rastogi, A. Agarwal, and Y. S. Chauhan, "Atomistic study of band structure and transport in extremely thin channel inp mosfets," *physica status solidi* (a), vol. 213, no. 4, pp. 898– 904, 2016, doi: 10.1002/pssa.201532727.

- [29] P. Giannozzi, S. Baroni, N. Bonini, M. Calandra, R. Car, C. Cavazzoni, D. Ceresoli, G. L. Chiarotti, M. Cococcioni, I. Dabo, A. D. Corso, S. de Gironcoli, S. Fabris, G. Fratesi, R. Gebauer, U. Gerstmann, C. Gougoussis, A. Kokalj, M. Lazzeri, L. Martin-Samos, N. Marzari, F. Mauri, R. Mazzarello, S. Paolini, A. Pasquarello, L. Paulatto, C. Sbraccia, S. Scandolo, G. Sclauzero, A. P. Seitsonen, A. Smogunov, P. Umari, and R. M. Wentzcovitch, "QUANTUM ESPRESSO: a modular and open-source software project for quantum simulations of materials," *Journal of Physics: Condensed Matter*, vol. 21, no. 39, p. 395502, sep 2009, doi: 10.1088/0953-8984/21/39/395502.

- [30] P. Giannozzi, O. Andreussi, T. Brumme, O. Bunau, M. B. Nardelli, M. Calandra, R. Car, C. Cavazzoni, D. Ceresoli, M. Cococcioni, N. Colonna, I. Carnimeo, A. D. Corso, S. de Gironcoli, P. Delugas, R. A. DiStasio, A. Ferretti, A. Floris, G. Fratesi, G. Fugallo, R. Gebauer, U. Gerstmann, F. Giustino, T. Gorni, J. Jia, M. Kawamura, H.-Y. Ko, A. Kokalj, E. Küçükbenli, M. Lazzeri, M. Marsili, N. Marzari, F. Mauri, N. L. Nguyen, H.-V. Nguyen, A. O. de-la Roza, L. Paulatto, S. Poncé, D. Rocca, R. Sabatini, B. Santra, M. Schlipf, A. P. Seitsonen, A. Smogunov, I. Timrov, T. Thonhauser, P. Umari, N. Vast, X. Wu, and S. Baroni, "Advanced capabilities for materials modelling with

- quantum ESPRESSO," *Journal of Physics: Condensed Matter*, vol. 29, no. 46, p. 465901, oct 2017, doi: 10.1088/1361-648x/aa8f79.

- [31] G. Kresse and D. Joubert, "From ultrasoft pseudopotentials to the projector augmented-wave method," *Phys. Rev. B*, vol. 59, pp. 1758–1775, Jan 1999, doi: 10.1103/PhysRevB.59.1758.

- [32] P. E. Blöchl, "Projector augmented-wave method," *Phys. Rev. B*, vol. 50, pp. 17953–17979, Dec 1994, doi: 10.1103/PhysRevB.50.17953.

- [33] J. P. Perdew, K. Burke, and M. Ernzerhof, "Generalized gradient approximation made simple," *Phys. Rev. Lett.*, vol. 77, pp. 3865–3868, Oct 1996, doi: 10.1103/PhysRevLett.77.3865.

- [34] H. J. Monkhorst and J. D. Pack, "Special points for brillouin-zone integrations," *Phys. Rev. B*, vol. 13, pp. 5188–5192, Jun 1976, doi: 10.1103/PhysRevB.13.5188.

- [35] A. A. Mostofi, J. R. Yates, G. Pizzi, Y.-S. Lee, I. Souza, D. Vanderbilt, and N. Marzari, "An updated version of wannier90: A tool for obtaining maximally-localised wannier functions," *Computer Physics Communications*, vol. 185, no. 8, pp. 2309 2310, 2014, doi: 10.1016/j.cpc.2014.05.003.

- [36] N. Marzari, A. A. Mostofi, J. R. Yates, I. Souza, and D. Vanderbilt, "Maximally localized wannier functions: Theory and applications," *Rev. Mod. Phys.*, vol. 84, pp. 1419–1475, Oct 2012, doi: 10.1103/RevModPhys.84.1419.

- [37] I. Souza, N. Marzari, and D. Vanderbilt, "Maximally localized wannier functions for entangled energy bands," *Phys. Rev. B*, vol. 65, p. 035109, Dec 2001, doi: 10.1103/PhysRevB.65.035109.

- [38] Y.-S. Lee, M. B. Nardelli, and N. Marzari, "Band structure and quantum conductance of nanostructures from maximally localized wannier functions: The case of functionalized carbon nanotubes," *Phys. Rev. Lett.*, vol. 95, p. 076804, Aug 2005, doi: 10.1103/PhysRevLett.95.076804.

- [39] M. Büttiker, Y. Imry, R. Landauer, and S. Pinhas, "Generalized many-channel conductance formula with application to small rings," *Phys. Rev. B*, vol. 31, pp. 6207–6215, May 1985, doi: 10.1103/PhysRevB.31.6207.

- [40] C. Soulard, X. Rocquefelte, P.-E. Petit, M. Evain, S. Jobic, J.-P. Itié, P. Munsch, H.-J. Koo, and M.-H. Whangbo, "Experimental and theoretical investigation on the relative stability of the pds2- and pyrite-type structures of pdse2," *Inorganic Chemistry*, vol. 43, no. 6, pp. 1943–1949, 2004, doi: 10.1021/ic0352396.

- [41] S. Deng, L. Li, and Y. Zhang, "Strain modulated electronic, mechanical, and optical properties of the monolayer pds2, pdse2, and ptse2 for tunable devices," ACS Applied Nano Materials, vol. 1, no. 4, pp. 1932–1939, 2018, doi: 10.1021/acsanm.8b00363.

- [42] D. Qin, P. Yan, G. Ding, X. Ge, H. Song, and G. Gao, "Monolayer pdse2: A promising two-dimensional thermoelectric material," *Scientific Reports*, vol. 8, no. 1, p. 2764, Feb 2018, doi: 10.1038/s41598-018-20918-9.

- [43] IRDS 2020: https://irds.ieee.org/editions/2020,.

- [44] J. Wang and M. Lundstrom, "Does source-to-drain tunneling limit the ultimate scaling of mosfets?" in *Digest. International Electron Devices Meeting*,, ser. Digest. International Electron Devices Meeting,, 2002, doi: 10.1109/IEDM.2002.1175936. pp. 707–710

- [45] D. J. Griffiths and D. F. Schroeter, *Introduction to quantum mechanics*. Cambridge University Press, 2018.

- [46] L. Liu, Y. Lu, and J. Guo, "On monolayer mos<sub>2</sub> field-effect transistors at the scaling limit," *IEEE Transactions on Electron Devices*, vol. 60, no. 12, pp. 4133–4139, 2013, doi: 10.1109/TED.2013.2284591.

- [47] A. Szabo, R. Rhyner, H. Carrillo-Nunez, and M. Luisier, "Phonon-limited performance of single-layer, single-gate black phosphorus n-and p-type field-effect transistors," in 2015 IEEE International Electron Devices Meeting (IEDM), 2015, doi: 10.1109/IEDM.2015.7409680. pp. 12.1.1-12.1.4.

- [48] A. Bansal, B. C. Paul, and K. Roy, "Modeling and optimization of fringe capacitance of nanoscale dgmos devices," *IEEE Transactions* on Electron Devices, vol. 52, no. 2, pp. 256–262, 2005, doi: 10.1109/TED.2004.842713.

- [49] ITRS 2013: "https://www.semiconductors.org/resources/ 2013-international-technology-roadmap-for-semiconductors-itrs/,.

- [50] Bin Yu, Leland Chang, S. Ahmed, Haihong Wang, S. Bell, Chih-Yuh Yang, C. Tabery, Chau Ho, Qi Xiang, Tsu-Jae King, J. Bokor, Chenming Hu, Ming-Ren Lin, and D. Kyser, "Finfet scaling to 10 nm gate length," in *Digest. International Electron Devices Meeting*, 2002, doi: 10.1109/IEDM.2002.1175825.

- [51] H. Lee, L. E. Yu, S. W. Ryu, J. W. Han, K. Jeon, D. Y. Jang, K. H. Kim, J. Lee, J. H. Kim, S. Jeon, G. Lee, J. Oh, Y. Park, W. Bae, J. Yang, J. Yoo, S. Kim, and Y. K. Choi, "Sub-5nm all-around gate finfet for ultimate scaling," in 2006 Symposium on VLSI Technology, 2006. Digest of Technical Papers., ser. 2006 Symposium

on VLSI Technology, 2006. Digest of Technical Papers., 2006, doi: 10.1109/VLSIT.2006.1705215.