# Modeling Short-Range Microwave Networks to Scale Superconducting Quantum Computation

Nicholas LaRacuente<sup>1,\*</sup>, Kaitlin N. Smith<sup>1</sup>,

Poolad Imany<sup>2,3</sup>, Kevin L. Silverman<sup>2</sup>, Frederic T. Chong<sup>1</sup>

<sup>1</sup>University of Chicago, Chicago, IL 60642, USA

<sup>2</sup>National Institute of Standards and Technology, Boulder, CO 80305, USA

<sup>3</sup>University of Colorado Boulder, Boulder, CO 80309, USA

\*nlaracuente@uchicago.edu

A core challenge for superconducting quantum computers is to scale up the number of qubits in each processor without increasing noise or cross-talk. Distributed quantum computing across small qubit arrays, known as chiplets, can address these challenges in a scalable manner. We propose a chiplet architecture over microwave links with potential to exceed monolithic performance on near-term hardware. Our methods of modeling and evaluating the chiplet architecture bridges the physical and network layers in these processors. We find evidence that distributing computation across chiplets may reduce the overall error rates associated with moving data across the device, despite higher error figures for transfers across links. Preliminary analyses suggest that latency is not substantially impacted, and that at least some applications and architectures may avoid bottlenecks around chiplet boundaries. In the long-term, short-range networks may underlie quantum computers just as local area networks underlie classical datacenters and supercomputers today.

#### I. INTRODUCTION

Quantum computing is at the forefront of emerging technologies, owing to its promise to solve some algorithms dramatically faster than classical counterparts. Quantum computers (QCs) evaluate quantum circuits in a manner similar to classical computers assessing classical circuits. However, quantum information's ability to leverage superposition, interference, and entanglement is anticipated to provide QCs significant advantage in tasks ranging from security protocols [1] and optimization [2], to simulation of quantum dynamics [3]. To harness the power of quantum computation, quantum bits, or qubits, are needed which are the core individual element for information representation and storage. Useful QCs require many qubits that are interconnected to each other in a low-noise and fault-tolerant manner. Many different architectures have been used to encode gubits, such as superconducting circuits (SCs) [4–6], trapped ions [7], neutral atoms [8], quantum dots [9], and photons [10, 11]. To date, SC quantum computers have been one of the most promising platforms, with the largest quantum computers in terms of interconnected gubits demonstrated with these circuits. Recent demonstrations of quantum advantage have shown that interference with just over 50 qubits can be harnessed for computational speedups [4, 6, 10], but more and cleaner qubits will be required to exploit quantum computing for practical applications.

State of art QCs, sometimes called Noisy Intermediate Scale Quantum (NISQ) devices, are error prone and up to hundreds of qubits in size [12]. The qubits on these QCs are not error corrected and often have limited connectivity. NISQ qubits are characterized by their sensitivity to interactions with their environment and each other, and the gates and measurements required for meaningful computation are implemented with imperfect, error-

prone operations. To achieve the realm of usefulness for quantum devices, many more qubits, approximately one million or more, and lower noise figures are essential [13]. Concerningly, as noted in [13], "quantum computer designers face a trade-off between trying to optimize for quantum computers with many physical qubits and quantum computers with very low gate error rate."

Potentially nonlinear scaling of physical resources with qubit number or circuit size may impede useful quantum advantages. Some forms of near-term quantum advantage rely on precise ratios of quantum to classical resources [14, 15]. Even larger quantum-classical separations could be in jeopardy under an inverse relationship between qubit quality and system size. Many long-term approaches to quantum computing, such as fault tolerance, conventionally require per-qubit noise to remain below a fixed threshold for arbitrarily large systems. The need to keep error rates bounded and total resource costs close to linear motivates approaches to reduce unwanted coupling within a single quantum computer [16].

Scaling up the qubit number without increasing noise comes across many challenges: (1) SC qubits operate inside a dilution refrigerator (DR) around 10s of mK, requiring a coax cable feed-through each to address individual qubits. The number of coax lines that can go into a DR poses an important engineering challenge in the number of qubits that can exist and operate inside each DR. To overcome this challenge however, using optical fibers and photodetectors instead of coax cables and use of wavelength division multiplexing to address multiple gubits with each fiber feed-through has been proposed [17]. (2) Placing many qubits in close proximity to each other can increase their connectivity, helpful for engineered gubit-gubit interactions. However, this comes at the cost of increased cross-talk which causes the gubits to decohere faster. (3) Fabricating many qubits on a single

wafer reduces the yield of keeping a high average performance for the qubits, since a single faulty qubit can drastically reduce the average performance of the processor as a whole. Furthermore, due to the large footprint of SC qubits, about  $1 \ mm^2$  [18], even a 12-inch wafer can only house around 100,000 qubits.

All of these challenges point towards the use of a chiplet architecture and distributed quantum computing [16, 19]. To move towards modular QC systems, technical hurdles associated with loss, fidelity, latency, and scalibility of the interconnect technology must be addressed [20]. Nonetheless, increasingly large devices [6, 21] are more likely to be error-limited for algorithms requiring many cross-device qubit movements, while smaller devices may achieve low noise without exceeding the range of classical state vector simulation. A grand challenge of quantum computing is to achieve the best of both. A major advance would be an architecture achieving competitive fidelities today and the ability to add connected qubits with little impact on attributes of pre-existing qubits.

Classical computing saw similar challenges associated with scaling the system-on-chip (SoC) model [22]. Integrated circuit (IC) yield loss is a result of manufacturing defects caused randomly by environmental particulates or by systematic sources such as unavoidable variation or errors during fabrication [23]. Because a larger chip has a higher probability of containing a defect that renders the entire system unusable, fabricating fewer, large SoCs on a wafer results in lower yields than ICs with a smaller wafer footprint. This observation has led to the increase in popularity of chiplet-based architectures for improved cost and flexibility in system design and use [24]. Just as pitfalls were eventually observed for monolithic classical computing devices, it is anticipated that continuing to pack qubits on single chip will push the capabilities of manufacturing, cooling, and control technologies to their limit. Thus, to develop QCs containing the millions of gubits required fault-tolerance, we are motivated to pursue a modular approach based on multiple cores working in sync to accomplish computational tasks in a distributed manner.

Distributed quantum architectures have been proposed in [25–27]. Related works present techniques for targeting a network of quantum chips for unified computing tasks [28, 29]. Major players in quantum computing have noted the potential of distribution for scaling quantum computers [16, 30].

Our main contribution is to bridge the physical and network layers in evaluating if and how short-range, high-performance links could accelerate progress in quantum computing. Our primary focus is distinct from conventional studies of quantum communication or networking applications, examining what underpins these networks instead of assuming common protocols. By connecting the physical with network and application layers, we begin to concretely answer questions about when and how linked chiplets obtain advantages over monolithic architectures. Maybe surprisingly, today's quantum pro-

cessors and links are probably near the point at which chiplets begin to show benefits.

Modeling quantum networks is complicated due its wide range of possible technologies, paradigms, uses, and aspects. In this study, we focus on microwave links between nearby, superconducting processors. Motivating this focus is spectacular progress in microwave link hardware. Microwave links already achieve transfer fidelities and latencies on scales not far from local processing. Such performance underpins the proposal to use quantum links for the low-level implementation of quantum computers. In this picture, fault tolerance and entanglement distillation are not assumed as network abstractions. Instead, a chiplet architecture at the physical layer may underlie these and other abstractions, accelerating the path to relevant thresholds.

#### A. Main Contributions & Where This Work Fits

A key contribution of this work is to bridge the gap from understanding microwave links at the physical layer to using them in distributed quantum computing applications. Rather than encapsulate network overheads as abstract cost functions, we analyze how noise and costs in both cross-chiplet links and local processing impact the eventual fidelity and feasibility of computations. Our models start and extrapolate from observations of real hardware and experimental physics models. We propose practical, concrete schemes to detect and reduce errors on near-term links and processors. Broad themes in potential applications are evaluated for feasibility on devices with limited connectivity.

This work does not attempt to provide a complete picture of exactly how quantum intranets will function, as this would involve much speculation about future developments. Instead, the analyses herein should be a spring-board for co-design. Quantum software researchers may use these analyses to answer the question of whether a proposed algorithm can reasonably and should be distributed on near-term quantum hardware. For experimentalists, these results should motivate efforts to integrate cutting edge, SC processors with microwave links, even before local fault-tolerance or efficient microwave to optical transduction. With these advances combined, quantum architects can design sophisticated computing systems that stitch all elements of the QC stack together.

The structure of this paper is as follows: In Section II, we review some related literature including analogous approaches to similar questions. Section III is about modeling quantum links and local gates at the physical layer, including a comparison of Hamiltonians between optical and microwave links, a review of hardware challenges for local processing, and quantum channel models of relevant operations. We present a quantum channel model that captures realistic noise on both microwave links and local SWAP operations, setting up later comparions. In Section IV, we compare monolithic with chiplet architectures

at the network layer, incorporating physical information to derive expected fidelities of qubit transfers in addition to topological metrics. We also derive a detailed channel model that includes both links and local swaps, which we use to propose a simple error detection scheme for the regime of high-quality local processing with lossy links. Finally, we conclude with some open problems and areas for potential follow-up research.

#### II. BACKGROUND

Front runners in the effort to scale quantum computers are increasingly distributed designs as a solution to scaling challenges [16, 30]. In this section, a sample of particularly relevant recent and concurrent work in the distributed quantum computing space is reviewed. Since this space is large, this Section serves to frame the focus of this work in the context of related but distinct efforts.

#### A. Two major regimes in quantum networking

A frequently described idea that is not the main focus of this work is the quantum internet [26, 31, 32], a long-range union comprising of numerous networks between many quantum computers. Information transfer within the quantum internet relies on establishing shared entanglement between remote nodes. Quantum information travels great distances over optical links, assisted by quantum repeaters that mitigate signal loss. These systems will be sophisticated as traveling quantum information works in synergy with classical transmissions to implement teleportation-based communication [33]. Network end-nodes will comprise of a variety of QCs, heterogeneous in terms of base technology, and quantum sensing nodes. Many simulation tools are emerging as an effort to study how resources and applications are allocated in quantum network architectures [34–36] - see [37, Section 6] or [38] for a summary of related work. A major challenge to date involves developing high-efficiency and high-fidelity methods from matter qubits used primarily and processors and mobile qubits used in transfers. A prime example is connecting SC processors with mobile, photonic qubits [39, 40]. Progress is being made in the multidiscipinary effort to network quantum devices [41– 44] at large distances.

In contrast, the primary focus of this paper is the possibility for quantum intranets [16]: short-range, low-latency, quantum networks near the physical layer. A quantum intranet addresses fundamentally different questions from the quantum internet. Rather than provide future applications for quantum computers, quantum intranets may accelerate progress toward those quantum computers being a reality. Relating the quantum internet with quantum intranets are two primary considerations:

- 1. As noted in [45, Technical Recommendation 1], "only a handful of anticipated use cases [for long-range quantum networks] have been identified," so governments and other sectors "must continue to invest in research on the potential advantages (and associated requirements) of quantum networks to justify future development." Small, efficient, high-performance test beds for quantum networks promote exploration, prototyping, and innovation. Ideas tested and invented on short-range networks may preview uses for long-range, long-term networks at relatively low cost.

- 2. Underlying the quantum internet will be many abstractions and assumed basic protocols. Common "primitives" include teleportation, entanglement distillation, quantum storage, routing, real-time feedback, and sufficient local processing to support these operations without draining resources from computation. Just as today's supercomputers and data centers use local networks to combine parallel subunits, large quantum computers may consist of locally connected chiplets. The quantum internet might never replace these local intranets, just as today's classical Internet has not replaced local networks.

While the quantum internet is an active focus of both scientific research and institutional attention, the near-term impact of quantum intranets might be frequently understated. This paper primarily focuses on the potential for intranets as a competitive quantum computing architecture, rather than as a small analog of the quantum internet.

Despite major progress in and even commercial applications of quantum networks, an effective bridge between quantum communication and computing remains a challenge. Conventional approaches rely on future protocols and abstractions, including reliable quantum memory, entanglement distillation, and encodings that achieve finite rates with vanishing error. In contrast, because of microwave links' high transfer fidelity and low latency, short-range networks built on this technology show promise to improve computation without relying on these underlying abstractions. Instead, short, high-quality links could help local quantum computers reach the scale and quality at which operations such as encoding and distillation will be more feasible.

# B. Ongoing work in short-range link hardware

Experimental work has shown that quantum communication between devices is preliminary yet feasible. In the space of microwave links, the work of [46] shows that superconducting qubits and microwave links can couple at high efficiency, mediated by coupling resonators. The systems in [47] and [48] demonstrate high-fidelity (80-91%) qubit state transfer and entanglement between

two nodes separated by a meter within one DR and five meters between separated cryostats, respectively. Similarly, [49] describes SWAP operations between four quantum modules, each containing a single qubit, with a microwave quantum state router. These demonstrations are promising as a cold waveguide provides a reliable means to transfer microwave signals between superconducting qubits, perhaps enabling near-term, networked QC architectures.

In Section III, we describe the physics and characteristics of these links, comparing them with matter-optical transduction.

#### C. Algorithms and applications

Recent investigations have studied resource requirements of algorithms transpiled to multiple quantum processors. Additionally, methods to understand the impact of network topology on the distribution of entanglement within quantum networks have been proposed using graph-based analysis [50, 51]. Studies have also examined the tradeoffs of teleporting information vs. gates for various network topologies [52]. This research will eventually enable application-level compilers that optimize use distributed quantum software according to cost functions based on link use [53]. For example, in the area of protocols that route network traffic, the work in [54] presents Quantum MPI, inspired by classical messaging passing interface (MPI), to standardize qubit messaging and entanglement distribution between nodes for distributed and parallel quantum computing. Much has yet to be defined in the space of quantum network protocols due to ambiguity in how quantum networks will be physically realized.

At the application level, past work has explored extending the capabilities of near-term quantum hardware by employing classical hardware with techniques such as entanglement forging [55], circuit cutting followed by reconstructive post-processing [56], and translating tensor network algorithms to quantum circuits [57]. These methods, however, are intended for use on individual QCs coupled with both classical resources and runtimes that scale with the size of the targeted, quantum application. Hence these techniques are more designed to bypass distributing quantum computation than to realize it.

Finally, limited communication among non-local qubits drives the search for algorithms that are well-suited for the distributed space. Variational quantum algorithms (VQAs) have emerged as a prime candidate algorithm class for distributed quantum computing. For example, circuit partitioning and cutting was applied toward distributing quantum variational optimization over multiple QCs linked with classical communication channels [58]. Additionally the work in [59] contributes a methodology for decomposing the accelerated variational quantum eigensolver ( $\alpha$ -VQE) algorithms for ansatz initialization in a distributed setting where available re-

sources that connect quantum nodes include classical control networks and entanglement networks.

# III. PHYSICAL COMPONENTS OF A DISTRIBUTED NETWORK

#### A. On-chip hardware

SCs are popular quantum technology that are expected to be favorable to scaling. They employ circuit components that demonstrate "atom-like" behavior, and the qubits can be customized to enable specific operation regimes and properties. Here, we focus on transmon QCs used by IBM [60], and in the past five years, devices have grown from 5 to 127 qubits in size. Quantum technology roadmaps predict that 1000+ qubit devices will be available by the end of 2023 [61].

The performance of a QC cannot be measured in number of qubits alone. Features such as connectivity, gate fidelity, state preparation and measurement (SPAM) errors, and coherence time must also be considered. Because of the 2-D nature of superconducting devices, qubit-qubit connectivity has largely been limited to nearest-neighbor communication. An example of this type of topology is a grid where all neighbors communicate, but limitations associated with device control along with cross-talk between circuit elements has lead to the popularization of the "heavy-hex" layout [62] where each on-chip gubit is connected to either two or three of its neighbors. Although room for improvement is seemingly limited with respect to on-chip connectivity using 2-D layouts, gate fidelity, SPAM errors, and coherence times are expected to improve with time. The singlenumber metric of Quantum Volume (QV) takes all of the aformentioned QC device properties into consideration, making it a valuable tool to benchmark quantum hardware [63].

At time of writing, IBM quantum devices demonstrate average single-qubit gate infidelity ranging from  $10^{-3}$  to  $10^{-4}$ . Average two-qubit gate infidelity is about an order of magnitude worse at around  $10^{-2}$  to  $10^{-3}$  [64]. These values result from randomized benchmarking [65– 67]. While it may not be as critical as fidelity metrics, gate execution time should also be noted as it influences the amount of computation a QC can perform within coherence windows. On IBM transmon devices, singlequbit gates implemented with a microwave DRAG pulse require 10s of ns, while two-qubit gates implemented as either a direct controlled-NOT (CX) gate or a crossresonance gate (CR) have a duration requiring 100s of ns. Because two-qubit operations dominate in terms of infidelity and duration, they are often emphasized more in system cost than single-qubit operations.

#### B. Link hardware

To transfer quantum information, photons are ideal candidates owing to traveling with the speed of light and long coherence times. For these photonic links, low-noise and fast quantum transfer with high probability of success is required to connect quantum processors in a quantum manner. In terms of speed, all the quantum processing has to take place before the qubits decohere, which is on the order of 100s of  $\mu s$  for SC qubits. Quantum links are similar to two-qubit gates in that they also connect two qubits to each other, but from different and sometimes distant quantum processors. Therefore, we should compare the performance of links with local two-qubit gates for each processor.

Two types of photonic links are used in quantum networks: optical and microwave. Optical links can operate with low thermal noise at room temperature due to their high frequency (around 200 THz), and are compatible with fiber-optical infrastructures and even satellite communications [68], therefore can envision a large-scale network of quantum processors. However, bridging the five orders of magnitude energy, or frequency, gap between SC qubits and optical photons is an outstanding task. Electro-optical approaches have been used to overcome this challenge [69, 70], with efficiencies approaching 0.02% [69]. To achieve higher efficiencies and lower noise figures with current technologies, intermediate quantum systems have been proposed, such as mechanical acoustic resonators [39, 71, 72] or solid-state quantum emitters [73, 74]. As an example, a system with one intermediate mechanical step is considered, where the microwave and mechanical frequencies are the same [39]. The large frequency difference between the mechanical and optical modes however, can be mediated by a strong optical pump red-detuned from an optical cavity by the mechanical frequency. In such cases, the interaction Hamiltonian between the optical and mechanical mode can be linearized from  $g_{om}a_0^{\dagger}a_0(b_m+b_m^{\dagger})$  to  $g_{om}(b_ma_o^{\dagger}+b_m^{\dagger}a_o)$ , with  $b_m^{\dagger}(a_o^{\dagger})$  and  $b_m(a_o)$  denoting the creation and annihilation operators for the mechanical (optical) mode, respectively, and  $g_{om}$  the coupling rate between optics and mechanics. The overall interaction Hamiltonian is then simplified to

$$\hat{H}_{int} = g_{qm}(\sigma_{qe}b_m^{\dagger} + \sigma_{eq}b_m) + g_{om}(b_m a_o^{\dagger} + b_m^{\dagger}a_o) \quad (1)$$

with  $g_{qm}$  representing the coupling rate between the SC qubit and the mechanical mode. Recently, converting quantum information between SC qubits and optical photons, or quantum transduction, has been demonstrated with an overall efficiency of  $10^{-5}$  and an addition of 0.57 noise photon per every transduced quanta [39].

Microwave links on the other hand, consist of photons with frequencies in the GHz range. Even though these links have to operate at mK temperatures to avoid thermal noise, the similarity between their frequency to that of SC qubits means the possibility for direct coupling

between these two quantum systems through microwave resonators with high efficiency [47]. The principle of state transfer between a SC qubit through a microwave link is the SC qubit emitting a photon into the link when it relaxes from the excited to ground state. The interaction Hamiltonian of this process has the form

$$\hat{H}_{int} = g_m(\sigma_{qe}a^{\dagger} + \sigma_{eq}a) \tag{2}$$

where  $\sigma_{ge}$  and  $\sigma_{eg}$  are the operators swapping the qubit between the ground and excited states.  $a^{\dagger}$  and a are creation and annihilation operators for a microwave photon, respectively, in a standing-wave mode of and  $g_m$  is the coupling rate between the SC qubit and the link channel. Recently, a 1 m-long microwave link between two threequbit SC quantum processors has been demonstrated, with a fidelity of 0.91 and success probability of 0.88 [47]. These links also operate at speeds on the order of 100 ns, comparable to that of two-qubit gates on chip. However, due to the low energy carried by each photon, these links have to operate at 10s of mK temperature to keep the thermal noise low, which makes long-distance microwave links out of reach. To date, a 5 m-long link between two DRs has been the only demonstration of a microwave link between distant DRs [48]. This multi-meter microwave link experiment reported fidelity of 0.86. It is suggested that state transfer fidelity could reach as high as 0.96 as processes are refined [48].

In this article, we focus on NISQ devices, and therefore, microwave links which show a more near-term path for scalability due to their reasonable fidelity, success probability, and speed. We show that chiplet architectures with microwave links [75] can result in integration of small arrays of high-performance SC qubits to achieve an overall higher performance compared to a monolithic larger quantum processor.

Modular quantum systems will consist of compute clusters, chiplets, characterized by high coherence times, robust gate sets, and dense connectivity between qubits. These compute qubits will likely have rigid design constraints associated with the devices in which they are housed that will limit scaling. Transmission lines between clusters will ease the burdens associated with scaling up qubits.

#### C. Modeling link-based and local SWAP operations

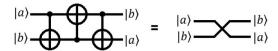

A standard SWAP gate is formed from 3 controlled-NOT (CX) gates (pictured in Figure 1). A quantum channel in finite dimension d is fully characterized by its Choi matrix, the resulting density from the input of a  $d \times d$  Bell pair through one side of the channel. We derive a rough estimate of the SWAP Choi matrix using channel tomography on qubit pairs within the  $ibmq\_brooklyn$ , a 65-qubit processor. For this procedure, we applied Qiskit's built-in channel process tomography in parallel

Figure 1: CX implementation of SWAP operation between two qubits.

to neighboring qubits. For a two-qubit channel, the inferred Choi matrix has dimension  $16 \times 16$ . To simplify the notation we use brakets to express the computational basis states  $|0\rangle \dots |15\rangle$  and denote by  $(\hat{1}/16)$  the completely mixed state. Approximately, the inferred Choi matrix is

(3)

After calculating a Choi matrix as an average of 42 different single-swap Choi matrices between adjacent qubits, we average the result element-wise, apply basic readout error mitigation using a matrix pseudo-inverse, and drop elements with magnitude below 0.025. After this process, the matrix is still not fully normalized, so the remaining contribution is assumed to be depolarizing. An ideal SWAP Choi matrix would be the density matrix corresponding to the state

$$\frac{1}{2}(|0000\rangle + |0110\rangle + |1001\rangle + |1111\rangle).$$

This estimate should be considered rough and likely underestimates the fidelity of a SWAP operation due to incomplete mitigation of readout and preparation errors.

We may alternatively regard a SWAP operation or link as a pair of single-qubit channels, moving a qubit state from the ith to jth physical qubit. Though this picture is less complete, it vastly simplifies the analysis of multiple moves as in Section IV, characterizing a single-qubit channel via tomography rather than a channel of dimension exponential in the length of the SWAP chain. Empirically, we observed in the experiments for Section IVB2 that a long chain model composed from single qubit SWAP tomographies more accurately recovers that of a long chain than does a reduced two-qubit model. We believe this discrepancy reflects cross-talk in nearby measurements or complications in readout error mitigation. The single qubit channel probably characterizes the SWAP more accurately by incorporating less readout noise. Here we again determine an average Choi matrix based on data from the 27-qubit *ibmq\_montreal*:

$$\begin{pmatrix}

0.4961 & 0.4726 \\

0.0083 & \\

0.0194 & 0.4762

\end{pmatrix} .$$

(4)

This matrix compares with the ideal given by ( $|00\rangle + |11\rangle$ )/2.

For the microwave link, we obtain a rough Choi matrix of

$$\begin{pmatrix} 0.50 & 0.39 \\ & 0.16 \\ 0.39 & 0.34 \end{pmatrix}$$

(5)

as an average of Choi matrices inferred from the plots in [46] and [48], and having fidelity of 0.97 between either of these and [76]. The transfer fidelity is roughly 0.81. Microwave link noise is almost completely amplitude damping. More recently, [47] obtain a transfer fidelity of roughly 0.91. Though we do not infer a full Choi matrix from this newer result, we primarily use it in later analyses, inferring an amplitude damping channel with  $\eta \approx 0.12$ .

The Choi matrix captures only the noise aspect of the link and local SWAPs, omitting latency. Though links are often presumed slow, latency does not appear to be a major problem for microwave links. Our analysis of the above papers finds a typical link latency of roughly 200 ns. A CX gate on the ibmq\_montreal takes roughly 400 ns, leading to a 1200 ns local SWAP time. Even with microwave-optical transduction, the latency of a link is likely to be on the scale of microseconds, only slightly worse than local qubit movements.

The time required to reset a link between uses is often noted as a potential bottleneck, but it does not appear to be a fundamental constraint. The 50 kHz rate from [46] suggests a waiting time of around 20  $\mu s$  before link re-use, and [48] may have a time as slow as 300  $\mu s$ . These slow rates arise, however, from issues of tuning that in principle would be improved by orders of magnitude in an experiment optimized for repetition. The links used in [47] reset on timescales closer to their latency, hundreds of nanoseconds. Furthermore, each transfer on this system is a two-way exchange, doubling the effective bandwidth in many scenarios. In the future, link repetition times will plausibly be as short as  $1-4\mu s$ .

In contrast to a common assumption that links are slow compared to local processing, links may reach the same timescales as local SWAPs. Rather than focus on latency, we therefore shift to issues of network topology and transferred state fidelity.

# IV. MAIN RESULTS: MODELING DISTRIBUTED ARCHITECTURES AND COMPARING TO MONOLITHIC

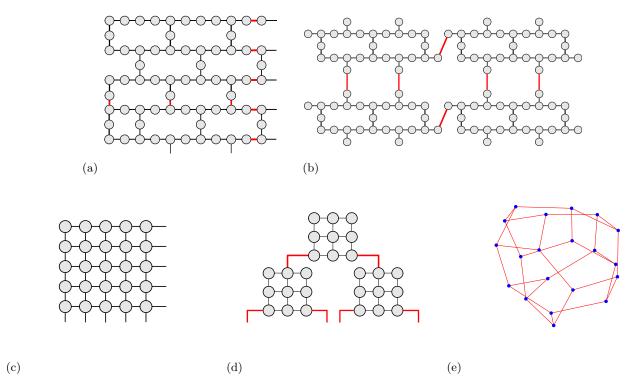

There are many ways to define the local connectivity of a QC architecture, where popular candidates include two-dimensional grid-like connectivity and IBM's heavyhex layout, representing different tradeoffs between connectivity and noise [77]. Some previous analyses have evaluated alternative architectures based on the costs of entanglement creation [50, 51]. Sophisticated connectivity graphs such as trees and expanders may show advantages over straightfowardly two-dimensional layouts. We start by examining several layouts that appear to be strong or popular candidates.

# A. Connectivities and graph metrics

We consider the following graph topologies:

- 1. As a monolithic comparison point, we consider the standard two-dimensional grid, in which each qubit not on the boundary has four neighbors.

- 2. Removing some links from the monolithic grid yields a chiplet grid containing the same qubit number but distributed in 25-qubit blocks. We use this as a chiplet grid architecture. Since each local subgrid has up to 4 links, the qubit-to-link ratio is at least 12.5.

- 3. Inspired by the study of [50], we consider a tree of 25-qubit grids. Each non-root node connects to its parent via the middle qubit on top, and each non-leaf connects to each of its children through a bottom corner. With 3 links per chiplet, the qubit-to-link ratio is at least 16.6.

- 4. As a second monolithic comparison point, we consider a monolithic heavy-hex chip. The overall structure is chosen to be as square as possible for a given chip number.

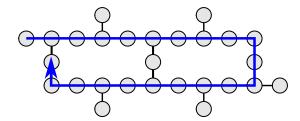

- 5. We split the heavy-hex layout into chiplets by replacing some connections with links. This has little effect on topology but may change the error tradeoffs as described in Subsection IVB. In particular, we partition the chiplet into 80-qubit blocks, each with up to 16 links for a qubit-to-link ratio of at least 10. A smaller version of this layout is shown in Figure 2(c). Unlike the grid case, here we can maintain a reasonable qubit-to-link ratio while maintaining the heavy-hex structure across the entire device. We expect topological properties similar to the monolithic heavy-hex but impose a rectangular overall structure, which might be less square than its monolithic counterpart due to the minimum block size.

- 6. We consider linking 27-qubit IBM Falcon processors in a layout that nearly preserves heavy-hex structure, as illustrated in Figure 2(b). There are 6 qubits of a Falcon processor that each have local coordination number one. Since these 6 qubits are relatively isolated, they may intuitively serve as natural joining points, buffering the main processors from potential noise around links. This layout yields a qubit-to-link ratio of at least 9.

7. Depending on the link medium, it may sometimes be possible to bypass the constraints of two-dimensional layouts. Expander graphs may achieve high connectivity with relatively few links, avoiding bottlenecks by allowing links to criss-cross in a more complex structure. Each of these connects to such a point on another Falcon processor for qubit-to-link ratio of 9. To generate expander graphs, we use a well-known result that random graphs frequently have good expansion properties [78]. For each desired chip number, we search 800 random expander graphs and 60 random ways of embedding chiplets within each for that with the largest spectral gap, a figure of merit described below.

Though some figures of merit could be derived analytically, others are somewhat complicated, and the random generation of expander graphs is best automated. Hence the analyses in this Subsection are computed using the NetworkX library, a standard tool for graph analysis [79].

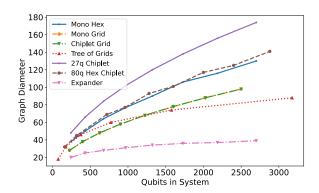

The maximum time required to move a qubit via SWAP operations, including link uses, is proportional to the graph diameter of the system's connectivity graph.

**Definition IV.1.** The graph diameter is given by taking maximum over all pairs of nodes of the shortest path between those nodes.

Figure 3 shows graph diameters for the above topologies. In some cases, the graph diameter is not hard to calculate by hand. For the example of a square grid, the graph diameter is equal to twice the side length minus one, and it is exactly the same for the chiplet grid architecture. For heavy hex, one may estimate the graph diameter by counting the number of connections needed to move from left to right, then from top to bottom, and again add up effective side lengths. Graph diameter for a tree or expander is logarithmic in node number.

In addition to graph diameter, we consider the spectral gap of a graph to quantify connectivity on a busy network. Here we take the smallest non-zero eigenvalue of the graph's normalized Laplacian matrix as the spectral gap (see [80, Lecture 7], in particular the interpretation given by Cheeger's inequality).

**Definition IV.2.** For a graph G on n vertices given by its edge set,  $G \subset \{(v_1, v_2) \in \{1...n\} \times \{1...n\}\}$ , the adjacency matrix  $A_G$  is an  $n \times n$  matrix given such that  $A_{ij} = 1$  when  $(i, j) \in G$ , and zero elsewhere. The graph's Laplacian matrix is given by  $L = \hat{1} - D^{1/2}AD^{1/2}$ , where D is the diagonal matrix such that  $D_{ii}$  is the degree of node  $i \in 1...n$ . The spectral gap  $\lambda_2$  is the second smallest eigenvalue of L.

As summarized in [81], a graph's spectral gap relates to the rate at which random walks on that graph approach random node choice. Furthermore, the spectral gap yields bounds on a graph's Cheeger constant, quantifying the ratio between the size of any subgraph and the number of links connecting it to the rest. Hence the spectral gap measures the extent to which a graph has few

Figure 2: The black lines connecting physical qubits indicate on-chip connections while the red lines indicate interchip microwave links. (a) Heavy-hex, where red lines illustrate possible link placements in 38-q chiplet. (b) Four 27-q chiplets with links on nodes of local coordination number 1. (c) Monolithic grid. (d) Tree of  $3 \times 3$  grids. (e) Random graph with degree 3 and good spectral gap. Here each node (shown in blue) would be replaced by connections to a chiplet.

Figure 3: Comparison of QC topology graph diameter vs. number of qubits for proposed architectures.

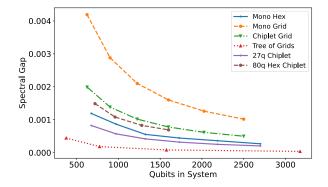

bottlenecks. While graph diameter quantifies the cost of sparse or sequential qubit movements, spectral gap is more relevant when many transfers should occur in parallel. In contrast to graph diameter (for which smaller is better), a large spectral gap is desirable. Computed spectral gaps appear in Figure 4.

Some results in Figures 3 and 4 are as expected. The monolithic grid architecture is overall more connected than the heavy-hex or chiplet architectures, so it has a

lower or comparable graph diameter and higher spectral gap. The tree of grids achieves a good graph diameter but poor spectral gap, because while the hierarchical structure promotes fast routing, it is highly bottlenecked at the root node.

The chiplet grid incurs a larger spectral gap penalty versus its monolithic counterpart than the heavy-hex chiplet architectures. This drop in spectral gap results from the bottlenecks between chiplets. Grid architectures maintain a better ratio of qubits to links, but because of their higher internal connectivity, its not clear that they would more effectively buffer against noise at links or cross-talk over links.

Although topological metrics appear to favor the monolithic grid over other planar layouts, this does not necessarily imply superiority as a quantum computing architecture. As noted in [82], heavy-hex and related layouts achieve lower coordination numbers, taking pressure off of other considerations and potentially enabling technique for higher fidelity.

The difference between distributed and monolithic topologies is often smaller in heavy-hex than in grids. To maintain grid topology would require a link number proportional to the entire chiplet surface area. For the 25-qubit chiplets, this would yield 20 links per chiplet and a qubit-to-link ratio of only 2.5. Since heavy-hex is less internally connected to begin with, one can maintain

Figure 4: Comparison of QC topology spectral gap vs. number of qubits for proposed architectures.

better qubit-to-link ratios or better isolate the qubits at link endpoints with much smaller disruption to the layout. The chiplet and monolithic architectures based on heavy-hex layouts have similar spectral gaps and graph diameters to each other, which is consistent with expectations. We note that the 80g heavy-hex chiplet sometimes has larger spectral gap than its monolithic counterpart this small discrepancy probably arises from the extent to which each layout can be made closer to square overall. Applications originally mapped to monolithic grids will likely need to be re-organized around the bottlenecks, while those originally on monolithic heavy-hex avoid this problem. The lack of an obvious bottleneck in distributed heavy-hex layouts motivates the focus of the next Subsection, in which we consider qubit movements from the perspective of noise.

Finally, we note the combined advantages of expander topologies, which appear to exceed other layouts in spectral gap and graph diameter with a reasonable qubit-to-link ratio, low coordination number, and strong potential isolation of linked qubits. In theory, there exist particularly strong expanders known as Ramanujan graphs [81]. Ramanujan graphs have a constant number of connections per node and constant (non-decaying) spectral gap with total node number. The properties of expanders show how by dropping the commonly assumed constraint of planarity, novel architectures may

achieve vast improvements. Expanderized chiplets may show large advantages in quantum error correction using LDPC codes [83], which often use non-planar connectivity to improve ratios of logical to physical qubits.

#### 1. Bandwidth Considerations for Applications

The spectral gap may serve as a coarse proxy for an architecture's tendency to avoid bottlenecks in arbitrary computations. In the long-term, a complete analysis of bandwidth likely requires optimizing compilers designed to make best use of connectivity at multiple layers of abstraction, possibly including identifying how problem instances can be mapped to computations that optimize locality of computation. Though chiplets introduce extra heterogeneity, the problem is closely related to that of mapping quantum ciruits to monolithic architectures, in which it is nonetheless useful to minimize overhead of moving data around the device. Though quantum compilation is an active research area, to our knowledge the problem of quantum compilation on large, planar chips remains wide open.

As described in [82], error correcting codes exist for heavy-hex and similar layouts designed to minimize the number of connections to each qubit. Such codes are likely to perform comparably on linked architectures such as those shown in Figure 2 (a) and (b). Though it is beyond the scope of this paper to evaluate error correction thresholds under the heterogeneous noise types induced by chiplets, it is likely that improved on-chip fidelities compensate for the higher likelihood of errors at links.

An alternative strategy is to identify classes of problems that may naturally map to heterogeneous connectivity. In the near-term, chiplet architectures may best suit a class of problems in an intermediate regime between those accessible to classically-connected devices and those requiring densely-connected qunatum architectures. As a point of comparison, some techniques emulate entanglement via classical post-processing [55, 84, 85]. Figures 2 and 3 of [85] suggest how a quantum circuit or physical system might be more amenable than usual to distribution. Good uses of chiplet architectures should require more quantum communication than is tractable to emulate, but possibly less than would general computations.

In entanglement forging [55] , an observable on a whole system is rewritten as a linear (not necessarily convex) combination of observables on two subsystems via Schmidt decomposition. Entanglement forging simulates the expectation of an observable  $\langle \mathcal{O} \rangle_{|\psi\rangle}$  on an n-qubit system with operator norm error  $\epsilon$  via repeated uses of an n/2-qubit system. The distributed scheme would use two n/2-qubit systems and a number of link uses proportional to the entanglement needed between subsystems. In principle, if each bidirectional link use exchanges up to two qubits of entanglement, the number of link uses is logarithmic in the number of non-zero Schmidt coef-

ficients. For comparability, one should allow a chiplet mapping to approximate the true state within precision  $\epsilon$  as well. If we post-select on successful transfers via the two-use code discussed in Section IV D, then we may convert link uses and noise into a failure probability. The chance that each double-transfer fails is  $1/\eta,$  where  $\eta$  is an exponentiated amplitude damping parameter. In this formulation, we can directly compare the number of retrials expected using  $\frac{1}{2}\log_2\left|\left\{i:\tilde{\lambda}_i>0\right\}\right|$  quantum link transfers vs. entanglement forging:

Entanglement Forging | Chiplet Architecture

$$\frac{1}{\epsilon^2} \left( \sum_{k,m} |\lambda_k \lambda_m| \right)^2 = \exp \left( \frac{1}{2} \eta \log_2 |\{i : \tilde{\lambda}_i > 0\}| \right)$$

If one can tolerate link noise or detect and retry entanglement creation, then the polynomial scaling of retrial numbers in the distributed scheme yields a major advantage in scaling. This advantage is unsurprising, because we expect that for highly entangled systems, a reasonably clean quantum computer should exponentially outperform a classical emulator on tasks involving large, complex entanglement. Applications of quantum pseudorandom states my present such a regime, requiring superlogarithmic but sublinear entanglement across a bipartition [86]. Other potential examples may emerge in quantum chemistry [87].

# B. Modeling qubit movements

As noted in the previous Subsection, graph-based figures of merit do not capture tradeoffs between higher connectivity and local noise. Indeed, metrics such as graph diameter achieve optima for all-to-all connectivity, as does the ease of designing quantum algorithms and codes. Graph topology is a good way to analyze high-level networks that abstract away problems such as loss and error mitigation, reducing costs to latency, bandwidth, and similar. Graph topology may however be too high an abstraction level to capture important challenges of scaling up quantum computation. As the focus of this paper is on how short-range quantum networks may accelerate the path to scale, quantum advantage, and ultimately fault-tolerance, here we consider noise in both links and local processing to be significant.

Pursuing chiplet architectures may be the most practical route for quantum devices to scale up while keeping noise low. Such may seem counter-intuitive at first glance, because qubits will incur higher noise when traversing links than during usual local gates. In contrast, chiplets may improve local error rates for several reasons:

SC qubits at fixed frequency require individual addressing. Qubits that are too close both physically and spectrally may experience cross-talk in controls.

- Unintended coupling between nearby qubits induces cross-talk, especially during operations such as two-qubit gates and readout.

- Cosmic rays and other effects induce strongly correlated errors between nearby qubits, potentially evading error correction designed for single-qubit, independent errors [88, 89].

- Variance in the manufacturing process leads to random fluctuations in chip performance, including occasionally defective, unusable qubits (see [4, Figure 1] for a dramatic example). Splitting into chiplets could greatly increase the efficiency of defect rejection. For example, if each qubit has a 1% chance of being defective, the chance of 1000 qubit array emerging with zero defects is roughly 0.4 × 10<sup>-5</sup>, likely requiring hundreds of thousands of discarded attempts. As the chance of a 50-qubit array emerging defect-free is about 0.6, one expects to obtain 20 of these (for 1000 total qubits) in about 34 attempts.

- Beyond thousands of qubits per chip, new scaling barriers will likely appear [48, 90]. As fault-tolerance may need 10<sup>3</sup> 10<sup>4</sup> physical qubits for each logical qubit [91], achieving this crucial milestone probably requires some combination of redesigning current chips and DRs, major advances in error correction efficiency, and/or distributed computing.

A recent meta-analysis [13] begins to quantify the tradeoff between qubit number and noise rates. These authors estimate the correlation between qubit number and error as within the interval (-0.11, 0.48) with a confidence of 0.84 that the correlation is positive. In other words, as monolithic devices increase in size, it is likely that the average fidelity of two-qubit operations will decrease. In contrast, small chips joined by short wires could avoid or reduce many of these penalties to scaling.

In this Subsection, we combine ideas from the physical channels models described in Subsection III C with the network modeling of the previous Subsection IV A and the aforementioned chip size vs. noise tradeoffs. We study the noise incurred by a single qubit traversing the graph diameter, calculating the impact of each local SWAP gate or microwave link. We focus on the 27-qubit Falcon processor as chiplet model as illustrated in Figure 2 for several reasons.

- As described in Subsubsection IV B 2, we have access to and can analyze IBM Falcon processors in detail.

- 2. This layout attaches links to qubits that each have only a single local connection. Because linking qubits are reasonably well-isolated and at the physical edge of chiplets, we make the simplifying assumption that chiplet internal SWAP gate noise

does not increase with the number of chiplets in a system, only with the number of locally-connected chips.

- 3. Though the relatively small ratio of qubits to links is a potential caveat to the previous point, we believe this is accounted for in the analysis. Since we count extra noise incurred at each link, high link density results in pessimistic estimates. Future engineering considerations will probably favor larger chiplets, such as the 127-qubit IBM Eagle processor. We expect the metrics herein to be more favorable for larger chiplets, since they would require fewer link crossings. Similarly, expander-based graphs should achieve vastly improved performance. Hence we take the linked Falcon architecture as pessimistic on the metrics we quantify and relatively safe on those we cannot.

- 4. As concluded in the previous Subsection IV A, similarity between the chiplet and monolithic architectures motivates analyzing this layout entirely in terms of noise incurred during qubit movements. In this Subsection, we do not directly address bandwidth or latency, which should be only slightly worse than in monolithic heavy-hex.

#### 1. A simple model: decaying fidelity

We aim to model the process fidelity of state transfer cross-system, or the graph diameter path, using values based on today's real machines, reported trends, and thresholds for error correction. A logical SWAP operation between two qubits allows qubit information to move cross-chip, and as seen in Figure 1, a SWAP can be decomposed into three CX operations. The IBM quantum gate library includes the two-qubit CX, so the Figure 1 circuit is commonly used for communication between non-local qubits. Thus, average CX fidelity is an integral part of state transfer process fidelity analysis.

A recent, public competition sought pulse-level controls to minimize SWAP gate noise, potentially replacing the standard 3-CX implementation [92]. Unfortunately, crowdsourced solutions did not exceed the 50% improvement standard set by the competition organizers. Therefore, the 3-CX implementation still represents a good if rough model of how local SWAPs work on real devices.

Here we propose a noise model based on standard, simplifying assumptions, in particular that noise is typically depolarizing. As noted in Subsection III C, the depolarizing noise assumption is not physically realistic for current microwave links, which primarily induce amplitude-damping noise. It is more reasonable for local SWAP gates and compatible with the randomized benchmarking techniques used by IBM to obtain average CX gate errors as reported [65–67]. It is not physical realism but a simplifying abstraction that we seek here. In the

next Subsubsection, we will address the physical picture in much greater detail.

The basic tradeoff assumes that as the number of locally connected qubits increases, the fidelity of local operations falls. To model the direct relationship between monolithic CX gate fidelity,  $F_{CX,mono}$ , and qubit count, N, we calculate monolithic CX fidelity as

$$F_{CX,mono} = 1 - ((N - n_{chip}) \times \Delta_{infid.} + (1 - F_{CX,chip}))$$

(6)

for intra-device operations on the monolithic QC where  $\Delta_{infid}$  is average gate infidelity increase per additional monolithic-system qubit above the number of qubits in one chiplet,  $n_{chip}$ . Each 27-qubit chip modeled after a Falcon processor is initially assigned the two-qubit gate fidelity of  $F_{CX,chip} = F_{CX,Mumbai}$ .  $F_{CX,mono}$ , as defined in Equation 6, is calculated using  $F_{CX,chip}$  and the total number of qubits in the system, N.

$F_{CX}$  and  $F_{link}$  values described above are used to approximate total process fidelity of cross-system state transfer on various sizes of the monolithic and chiplet architectures. Process fidelity is approximated with average infidelity as outlined in [93]. Although there is no provably direct connection between average gate fidelity and error rate [93], approximation of the combined noise process for each operation is feasible. Using methods found in [93], we estimate the total noise, r, at each step in the SWAP chain before values are combined to approximately model the success of a cross-system SWAP chain. If we assume that all noise is depolarizing, then r is the noise parameter under the depolarizing channel in dimension d given by

$$\rho \mapsto (1-r)\rho + r\frac{\hat{1}}{d}.$$

As depolarizing noise eventually reduces the state to a complete mixture rather than one orthogonal to its original value, the relationship between r and fidelity depends on dimension. We will also work with the non-depolarizing parameter R:=1-r. Qubit state transfer, a single qubit operation, over a microwave link is modeled with the error parameter

$$r_{link} = 2 \times (1 - F_{link}), R_{link} = 1 - r_{link}.$$

(7)

An on-chip CX operation, as a two-qubit operation, is modeled with the error parameter

$$r_{CX} = \frac{4}{3} \times (1 - F_{CX}), R_{CX} = 1 - r_{CX}.$$

(8)

An on-chip SWAP is comprised of three CX operations, as pictured in Figure 1. Thus,

$$R_{SWAP} = (R_{CX})^3. (9)$$

The formula does not change after tracing out one of the qubits, yielding the non-depolarizing ratio for a single-qubit transfer via SWAP gates. The primary convenience

of this model is that non-depolarizing ratios multiply.  $R_{total}$  is determined by taking the product of  $R_{link}$  or  $R_{SWAP}$  values along the system's longest path. Finally, total process fidelity is approximated using the correction

$$F_{process} = 1 - \frac{1 - R_{total}}{2}. (10)$$

Though this model begins to incorporate some physical effects of qubit movements, it is still highly abstracted, ignoring qualitative distinctions between types of noise. In the next Subsubsection, we we validate this model by comparing to one of much greater physical realism.

#### 2. Modeling Qubit Movements via Physically Inferred Channels

We seek to address two primary concerns lingering after the previous analyses. First, while analyzing the fidelity of moved qubits gives a broad picture of where distributed quantum computing could show advantages over monolithic, efforts to evaluate specific algorithms or applications might need to consider specifically what kind of errors occur in each setting. In Section IV D, we use the more detailed models to suggest error detection for links.

Second, we hope to understand whether abstractions are useful rather than hiding important aspects. As in Section IV A, models based purely on network topology favor as much connectivity as possible. We know however that there are constraints and tradeoff. Section IV B 1 begins to address these tradeoffs, incorporating them into a model that shows where distributed and monolithic architectures may compete. We still however must acknowledge that the fidelity calculations ignore qualitative differences in the kind of noise from SWAP gates and links. In this Section, we examine the more physically detailed models underlying and abstracted by the fidelity calculations. The results herein validate those abstractions while illuminating their limitations.

In principle, the one-qubit link and local SWAP channels given by Choi matrices in Equations (4) and (5) should compose to the channel undergone by a qubit moving through any sequence of local SWAP operations and links. In practice, several effects limit the accuracy of such a procedure: heterogeneity in the device, variation of parameters over time, inability to fully extract readout errors from local SWAP and link tomographies, etc. In practice, we find that a different model yields a better combination of accuracy and simplicity.

To infer the channel that a moving qubit undergoes from local SWAP operations, we apply a one-qubit channel tomography with preparation on the starting qubit and measurements on the final location. We consider SWAP chains starting at length zero (qubit 0 is prepared, then measured), and going to length 20 (a qubit is prepared, then a chain of SWAP gates moves its state via a long route, which is measured). The particular path

Figure 5: Path of SWAP gate chains through IBM Falcon processors.

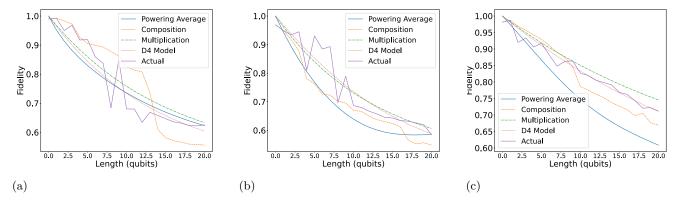

is shown in Figure 5. We obtain expected output fidelities by four methods, as shown in Figures 6. Channel tomographies were performed using IBM Qiskit's builtin process tomography routines [94]. We then applied a relatively simple form of readout error mitigation, first applying the inverse matrix calculated (see [95]). To ensure that the matrix would be positive and normalized, we first added complete mixture to counteract any negative terms, then scaled the matrix by its inverse trace.

We also initially considered SWAP chains on the  $ibmq\_brooklyn$ , a 65-qubit processor allowing longer chains. Unfortunately, the longer chains encountered constraints on the number of circuits executable within a single job via IBM's cloud interface. Because they were split across jobs, these produced anomalous results due to temporal fluctuations in device parameters.

In truth, moving a qubit through the device touches every qubit crossed. We may however assume roughly that each qubit on the path undergoes the noise associated with a single SWAP as modeled by Equation (3). Though this simplification requires some assumptions, it avoids having to do expensive multi-qubit tomographies. A 20-qubit tomography would not be tractable on today's devices as the number of required circuits scales exponentially with number of qubits.

We consider five ways of calculating the fidelity at the end of a SWAP chain, including four that calculate the eventual Choi matrix, here listed in order of increasing abstraction.

- 1. Actual: SWAP chain channel tomography, treating the SWAP-chain as a one-qubit channel as described in Subsection III C.

- 2. Composition: individual channel tomographies are performed on pairs of neighboring qubits. We perform multiple trials to get most pairs, leaving one idle qubit between simultaneously evaluated pairs to reduce readout cross-talk. One-qubit SWAP channels are composed to estimate the channel of the full chain.

- 3. Powering Average: the average of the one-qubit SWAP channels is taken to the power corresponding to the chain length. This method is less detailed than the above channel composition method, because the averaged channel erases knowledge about

heterogeneity of different qubits on the same device.

- 4.  $D^4$  Model: described below.

- 5. Multiplication: the calculation as in Section IV B 1.

Noise in real systems often includes mixing, relaxation, and unintended rotation. We capture most of the noise we observed in what we call the *Depolarizing-Damping-Dephasing-Drift* (  $\mathbf{D}^4$  ) model. Depolarizing, amplitude-damping, and dephasing noise are respectively described for a qubit density  $\rho$  by the quantum channels:

$$\Phi_{\text{depo}(a)}(\rho) = (1-a)\rho + a \begin{pmatrix} 1/2 & 0 \\ 0 & 1/2 \end{pmatrix}

\Phi_{\text{damp}(a)} \begin{pmatrix} \rho_{11} & \rho_{12} \\ \rho_{21} & \rho_{22} \end{pmatrix} = \begin{pmatrix} \rho_{11} + a\rho_{22} & \sqrt{1-a}\rho_{12} \\ \sqrt{1-a}\rho_{21} & (1-a)\rho_{22} \end{pmatrix} (11)

\Phi_{\text{deph}(a)} \begin{pmatrix} \rho_{11} & \rho_{12} \\ \rho_{21} & \rho_{22} \end{pmatrix} = \begin{pmatrix} \rho_{11} & (1-a)\rho_{12} \\ (1-a)\rho_{21} & \rho_{22} \end{pmatrix}.$$

Here a is a parameter between 0 and 1 controlling the noise strength. In real chains of SWAPs on the IBM QCs, we also noticed a rotation contribution of the form

$$\Phi_{\text{rota}(\theta)} \begin{pmatrix} \rho_{11} & \rho_{12} \\ \rho_{21} & \rho_{22} \end{pmatrix} = \begin{pmatrix} \rho_{11} & e^{i\theta} \rho_{12} \\ e^{-i\theta} \rho_{21} & \rho_{22} \end{pmatrix}. \tag{12}$$

Since amplitude damping and depolarizing noise do not commute, there is some ambiguity in how one models a quantum process that imposes both. We take the combined channel model corresponding to the continuous limit of both noise types occurring simultaneously. This approach yields a quantum Markov semigroup, a family of channels parameterized continuously by time. The obtained form has a unique and usually full rank fixed point state as long as depolarizing strength is nonzero, a useful property in theoretical analysis and in estimating rates of decay to equilibrium [96, 97]. While the D<sup>4</sup> form contains some unitary rotation, because this rotation commutes with the restriction to the fixed point algebra, one may still apply recent results showing exponential decay of relative entropy to the fixed point [98-100].

We let  $\Phi_{D(\epsilon,\eta,\delta,\theta)}$  denote the qubit channel given by the  $\mathrm{D}^4$  model, where  $\epsilon$  is the strength of depolarizing noise,  $\eta$  is the strength of amplitude-damping,  $\delta$  is the strength of dephasing, and  $\theta$  is the rotation angle. Let  $\rho_{44}^{(eq)} = \epsilon/4(\epsilon+\eta)$ . A quantum channel in finite dimension d is fully characterized by its Choi matrix, the resulting density from the input of a  $d \times d$  Bell pair through one side of the channel. The Choi matrix of  $\Phi_{D(\epsilon,\eta,\delta,\theta)}$  is then given by

$$\begin{pmatrix}

\frac{1}{4}(1+e^{-\epsilon t}) & 0 & 0 & \frac{1}{2}e^{-\epsilon-\eta/2-\delta+i\theta} \\

0 & \frac{1}{4}(1-e^{-\epsilon t}) & 0 & 0 \\

0 & 0 & (\frac{1}{2}-\rho_{44}^{(eq)})(1-e^{-(\epsilon+\eta)t}) & 0 \\

\frac{1}{2}e^{-\epsilon-\eta/2-\delta-i\theta} & 0 & 0 & \rho_{44}^{(eq)}+(\frac{1}{2}-\rho_{44}^{(eq)})e^{-(\epsilon+\eta)t}

\end{pmatrix}.$$

(13)

In common notation,  $\eta=1/T_1$ , the relaxation time, while  $\delta=1/T_2$  is the dephasing time. The equilibrium population of the  $|11\rangle$  state, given by  $\rho_{44}^{(eq)}=\epsilon/4(\epsilon+\eta)$ , arises from the tradeoff between depolarizing and damping noise in the long time limit. The D<sup>4</sup> channels corresponding to different depolarizing vs. damping noise levels will not necessarily commute with each other. Since we will usually consider discrete SWAP gates and link uses, we treat the "time" parameter t as discrete, counting the number of identical SWAP gates or link uses. Here we may think of the parameters  $\epsilon, \eta, \delta, \theta$  has having natural units of the inverse time needed for one basic qubit movement.

Listed in Table I are the fidelities of reconstructed Choi matrices against actual from channel tomographies. We observe:

- As expected, the primary contribution to irreversible noise from SWAP gates is depolarizing.

- There is a substantial contribution from coherent

phase drift. With calibration, it might be possible to correct this drift by applying phase gates or pulses after SWAP and even CX gates.

- The D<sup>4</sup> model obtains average channel reconstruction fidelities above 95%. Unlike channel composition, the D<sup>4</sup> model enables simple extrapolation to longer chains. The powering average method also naturally extrapolates but yields noticeably worse reconstructions.

- The simplified fidelity calculation as in Equation (10) is more than 90% accurate on average despite ignoring the distinction between qualitatively different errors.

These SWAP chain results motivate the simplified fidelity from Equation (10) and the  $\,\mathrm{D}^4$  model as well balanced between capturing enough physics to be realistic and abstracting enough detail to simplify calculations.

In Figure 6, show the calculated and actual fidelities of

| Device   | $\epsilon$ | η     | δ     | $\theta$ | Pow  | CC   | $D^4$ | Fid  |

|----------|------------|-------|-------|----------|------|------|-------|------|

| montreal | 0.048      | 0.013 | 0.026 | -0.024   | 0.82 | 0.94 | 0.96  | 0.93 |

| sydney   | 0.052      | 0.004 | 0.014 | -0.056   | 0.83 | 0.94 | 0.95  | 0.93 |

| mumbai   | 0.030      | 0.008 | 0.005 | -0.025   | 0.82 | 0.96 | 0.97  | 0.94 |

Table I: D<sup>4</sup> parameters and reconstruction fidelities for swap chain tomographies on 3 IBM devices. As column headings, "Pow," "CC," and "D<sup>4</sup>" refer respectively to the process fidelities of reconstructed Choi matrices using the powering average, composition, and D<sup>4</sup> methods as described above. The last column labeled "Fid" contains the average percent correctness simplified fidelity calculation as in Equation (10), where percent correctness is given by one minus the difference between calculated and actual fidelity over the actual fidelity. All data in this table were taken on November 29, 2021 remotely via IBM Qiskit.

swap chains with the identity channel on 3 IBM Falcon processors.

We may include links in a  $D^4$  or channel composition model of a SWAP chain. For a hypothetical device, we should have a simple way to extrapolate beyond observed qubits, which favors a linearized  $D^4$  or powered average approach. Based on accuracy and simplicity, the  $D^4$  approach actually appears stronger. Since the link and local SWAP channels in the  $D^4$  model probably do not commute with each other, we cannot simply add up parameters. The matrix multiplications are however easy numerically. A simple model for a long link-SWAP chain across many chiplets is given by

$$\Phi^k = \left(\Phi^m_{D(\epsilon,\eta,\delta,\theta)} \Phi_{D(0,\tilde{\eta},0,0)}\right)^k, \tag{14}$$

where m is the number of local SWAP gates before traversing each link, k is the total number of chiplets traversed, and  $\tilde{\eta}$  is the damping parameter of the link. This model is actually very reasonable on highly regular architectures. For example, a one-dimensional line of connected grids would have m equal to the width of each chiplet, and k equal to the total chiplet number. For a corner-to-corner path on a two-dimensional grid, we would roughly set m equal to width plus height of each rectangular chiplet, and k equal to the number of chiplets across two sides.

Comparing the D<sup>4</sup> model to the simplified model of Equation (10), we find reasonable agreement. We consider the difference in estimated fidelit across values of m and k each ranging from 1 to 20, D<sup>4</sup> parameters from each row of Table I and a link with  $\eta = 0.12$ . The largest difference between fidelities calculated via D<sup>4</sup> and Equation (14) remains below 0.045, which is below 10% of the estimated value from either. Ultimately, the results of this Subsection justify the use of Equation (10) in broadly estimating fidelities. Nonetheless, the more detailed D<sup>4</sup> model will likely be useful in fine-grained analysis and designing applications. As discussed in Subsection IV D,

knowing the qualitative form of noise enables simplified and improved error handling.

#### 3. Chiplet vs. monolithic performance on qubit movements

In this Section, we compare the fidelity of a qubit that has been moved around a device on monolithic against

On September 7, 2021 the 27-qubit  $ibmq\_mumbai$  reported an average CX fidelity of approximately  $F_{CX,Mumbai} = 1-0.009$  while the 65-qubit  $ibmq\_brooklyn$  reported  $F_{CX,Brooklyn} = 1-0.018$  [101]. This comparison likely represented a much better day for the  $ibmq\_mumbai$  than for the  $ibmq\_brooklyn$  and is not a statistically rigorous expectation of typical values. It nonetheless gives a pessimistic of  $\Delta_{infid}$ , which we take as an upper bound on how infidelity of monolithic processors may scale.

$$\frac{F_{CX,Mumbai} - F_{CX,Brooklyn}}{N_{Brooklyn} - N_{Mumbai}} = \frac{0.991 - 0.982}{65 - 27} \approx 0.0002.$$

(15)

As a lower bound, we may assume  $\Delta_{infid.} = 0$ , corresponding to no excess noise for larger chips. Since our analysis specifically considers Falcon processors, we do not attempt to incorporate the broader numerical estimates from [13]. Our bounds on  $\Delta_{infid.} = 0$  are extremely coarse, representing high uncertainty. Rather than attempt to make detailed predictions about forthcoming technologies, we aim to capture a wide range of possibilities.

We consider three cases for microwave state transfer fidelity between chips in our proposed systems based on the state-of-art. For the purpose of this analysis, we will treat  $F_{link}$  as the average gate fidelity inter-chip, single-qubit state transfer. First, the lower bound in is assigned  $F_{link} = 0.86$  as reported in [48]. The recent demonstration in [47] serves as our second point of comparison for link performance with a value of  $F_{link} = 0.91$ . It is suggested that state transfer fidelity could reach as high as 0.96 as processes are refined [48], so  $F_{link} = 0.96$  serves as the upper bound for link performance.

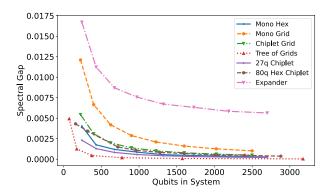

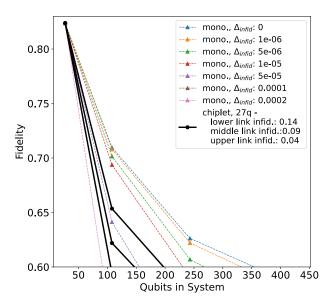

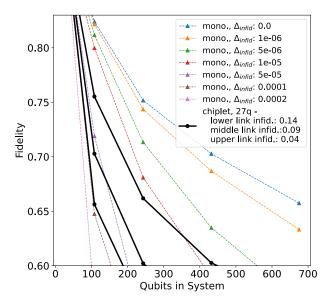

Results are featured in Figure 7. Figure 7 includes a comparison of total process fidelity of qubit state transfer on the 27-qubit chiplet architecture vs. monolithic. When examining process fidelity of similarly-sized systems containing more than one chiplet, the both architectures perform similarly.

The black curves of Figure 7 enclose a space where our model predicts chiplet architecture performance depending on the quality of the link. The black curve forming the lower boundary of this space represents a chiplet architecture as it increases in size with  $F_{CX,chip} = F_{CX,Mumbai} = 1-0.009$  and  $F_{link} = 0.86$ . These values are constant even as system sizes increase under the assumption that modular elements of a chiplet architecture can be consistently manufactured to meet design specifications that require minimum performance thresholds. The middle black curve represents a chiplet architecture

Figure 6: Computed output fidelity with the identity process by the 5 chosen methods from (a) *ibmq\_montreal* (b) *ibmq\_sydney* (c) *ibmq\_mumbai*.

Figure 7: Plots approximating total process fidelity of qubit state traversing a system's graph diameter. Proposed 27-q chiplet architectures with  $F_{CX,chip} = 0.991$ ,  $F_{CX,Mumbai}$  are compared to monolithic architectures. The black curves define a space where modeling predicts chiplet architecture performance depending on the quality of the link (lower boundary:  $F_{link} = 0.86$ / middle curve:  $F_{link} = 0.91$ / upper boundary:  $F_{link} = 0.96$ ). Various monolithic curves coarsely approximate different trends in monolithic, two-qubit gate infidelity as devices scale past the size of the chiplet (27 qubits).

as it increases in size with  $F_{CX,chip} = F_{CX,Mumbai}$  and  $F_{link} = 0.91$ . The upper boundary of the chiplet process fidelity space represents the optimistic outlook where  $F_{CX,chip} = F_{CX,Mumbai}$  and the link transfer fidelity is

equal to  $F_{link} = 0.96$ . We anticipate future improvements in link technology will allow network performance to fall within the bounds of the chiplet region of Figures 7(a-b), moving closer to the top over time. As a note, our analysis here holds  $F_{CX,chip}$  constant as 1) a reference point for  $F_{CX,mono}$  and 2) a minimum average gate fidelity target for mass produced QC chiplets. Future developments will likely improve  $F_{CX,chip}$  as well.

Included in Figures 7(a-b) are various monolithic curves that coarsely approximate SWAP chain process fidelity according to different trends in monolithic, two-qubit gate infidelity as devices scale past the size of the chiplet (27 qubits). The top, light-blue curve represents the optimistic outlook where two-qubit gate infidelity of monolithic devices consistently match chiplet two-qubit infidelity (i.e.  $1 - F_{CX,mono} = 1 - F_{CX,chip}$ ) at all N. This is an unlikely scenario. The remaining curves for monolithic SWAP chain fidelity see the anticipated, negative correlation between number of qubits and two-qubit average gate fidelity. Each curve represents a different average gate infidelity increase,  $\Delta_{infid}$ , per additional monolithic-system qubit. The lowest pink curve, is a pessimistic outlook where the infidelity trend scaling from the 27-qubit to 65-qubit machine is extrapolated.

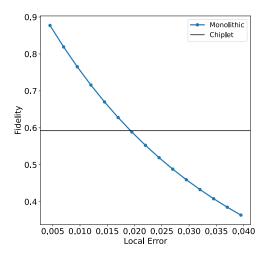

One might ask if potential chiplet advantages extend to better local processors, as future devices are expected to exceed the performance of the  $ibmq\_mumbai$ . For a more optimistic estimate of local error, we will consider a relevant error correction threshold. A hybrid surface and Bacon-Shor error correcting code with an error threshold of approximately 0.0045 is targeted for use on the heavy-hex lattice [82]. As a note, surface code has an error tolerance of approximately 0.01 while traditional Bacon-Shor codes require errors lower than  $2 \times 10^{-5}$  [91].

We estimate SWAP chain process fidelity using  $F_{CX,chip} = 1 - 0.0045$  based on the hybrid surface and Bacon-Shor error threshold [82]. As a note, the infidelity of the hybrid Bacon-Shor threshold is half of the observed average CX infidelity of  $ibmq\_mumbai$ ,  $1 - F_{CX,Mumbai}$ . All other parameters are the same as described in Sec-

tion IVB1. Figure 8 presents SWAP chain process fidelity in a system where the on-chip qubits demonstrate average CX fidelity required for hybrid Bacon-Shor. However, since  $F_{link}$  ranges from 0.86-0.96, the described chiplet systems are still not robust enough to implement error correction - either link quality must improve, or even better error rates in the local processor may compensate. Figure 8 includes a comparison of total process fidelity of qubit state transfer on the 27-qubit chiplet architecture vs. monolithic. Fidelity values are noticeably higher than those featured in 7, but the qualitative relationships between ranges chiplet vs. monolithic advantage remain.

Figure 8: Plots approximating total process fidelity of qubit state traversing a system's graph diameter on proposed 27-q chiplet and architecture with  $F_{CX,chip} = 0.9955$ , the hybrid surface/Bacon-Shor threshold, are compared to monolithic architectures. The black curves define a space where modeling predicts chiplet architecture performance depending on the quality of the link (lower boundary:  $F_{link} = 0.86$ / middle curve:  $F_{link} = 0.91$ / upper boundary:  $F_{link} = 0.96$ ). Various monolithic curves coarsely approximate different trends in monolithic, two-qubit gate infidelity as devices scale past the size of the chiplet (27 qubits).

All but two of the monolithic SWAP chain process fidelity curves in Figures 7(a-b) eventually intersect with the upper bound chiplet process fidelity, regardless of base chip size. If a negative correlation between qubit count and gate error cannot be avoided, chiplet architectures may provide the best route to boosting QC frontiers.

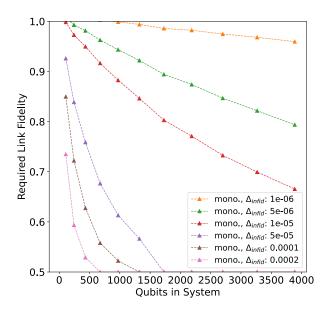

We expand our modeling to gain a better understanding of the link fidelity needed to achieve equal network

diameter SWAP chain process fidelity for the chiplet and monolithic architectures of size N. We set our sights on fault tolerance, so in this analysis, we utilize on-chip thresholds required for hybrid surface and Bacon-Shor codes. Figures 9(a) and (b) include a plot of required link fidelity,  $F_{link}$  vs. qubits for the 27-qubit chiplet architecture, respectively, when compared to corresponding monolithic implementations. The curves here use the same projected rates of change for the negative correlation between monolithic system size and average twoqubit gate fidelity as seen in Fig 7. In this model,  $F_{CX,chip} = 1 - 0.0045$ . As  $\Delta_{infid}$  increases, link fidelity thresholds required for competing chiplet architectures to match monolithic SWAP chain process fidelity are significantly reduced in systems up to thousands of qubits in size.