# Enabling Flexibility for Sparse Tensor Acceleration via Heterogeneity

Eric Qin\*, Raveesh Garg\*, Abhimanyu Bambhaniya\*, Michael Pellauer<sup>†</sup>, Angshuman Parashar<sup>†</sup>,

Sivasankaran Rajamanickam<sup>‡</sup>, Cong Hao\* and Tushar Krishna\*

\*Georgia Tech, Atlanta, USA. {ecqin,raveesh.g}@gatech.edu, callie.hao@gatech.edu, tushar@ece.gatech.edu

<sup>†</sup>*NVIDIA*, Westford, USA. {mpellauer, aparashar}@nvidia.com

<sup>‡</sup>Sandia National Labs, Albuquerque, USA. srajama@sandia.gov

Abstract—Recently, numerous sparse hardware accelerators for Deep Neural Networks (DNNs), Graph Neural Networks (GNNs), and scientific computing applications have been proposed. A common characteristic among all of these accelerators is that they target tensor algebra (typically matrix multiplications); yet dozens of new accelerators are proposed for every new application. The motivation is that the size and sparsity of the workloads heavily influence which architecture is best for memory and computation efficiency. To satisfy the growing demand of efficient computations across a spectrum of workloads on large data-centers, we propose deploying a flexible 'heterogeneous' accelerator, which contains many 'sub-accelerators' (smaller specialized accelerators) working together. To this end, we propose: (1) HARD TACO, a quick and productive C++ to RTL design flow to generate many types of sub-accelerators for sparse and dense computations for fair design-space exploration, (2) AESPA, a heterogeneous sparse accelerator design template constructed with the sub-accelerators generated from HARD TACO, and (3) a suite of scheduling strategies to map tensor kernels onto heterogeneous sparse accelerators with high efficiency and utilization. AESPA with optimized scheduling achieves  $1.96 \times$  higher performance, and  $7.9 \times$  better energy delay product (EDP) than a Homogeneous EIE-like accelerator with our diverse workload suite.

## I. INTRODUCTION

Large datacenters are expected to compute a wide variety of workloads such as deep neural networks, graph neural networks, and scientific computing [13], [30], [37], [38], [44]. These workloads utilize tensors (a matrix is a twodimensional tensor, and a vector is a one-dimensional tensor) of different dimension sizes and sparsity characteristics. For example, matrix dimension sizes span from single digits to millions while matrix sparsity spans from  $\sim 10^{-5}$ % dense to fully dense [9]. The vast amount of workloads has led to many accelerator architecture proposals, as they achieve higher throughput than CPUs, and higher energy efficiency than GPUs [21], [46], [48]. There are numerous types of sparse accelerators because they typically target a specific application, which often have tensors with similar dimensions, sparsity, and structure.

Many of these accelerators are rigid in both the dataflow choice as well as the sparsity format employed. This makes them perform extremely well for certain workloads, but poorly for other workloads. For instance, a systolic array is most energy-efficient for dense computations, but not for workloads of high unstructured sparsity. ExTensor [19], on the other hand,

| Accelerator Type                                            | # PEs<br>(With area<br>constraint) | Peak<br>TFLOPS/s | Relative<br>EDP<br>Benefits* | MK<br>Sparsity<br>Support | KN<br>Sparsity<br>Support | Matrix Mult.<br>Parallelism<br>Dimension<br>Bound |

|-------------------------------------------------------------|------------------------------------|------------------|------------------------------|---------------------------|---------------------------|---------------------------------------------------|

| Homogeneous<br>TPU-like<br>(GEMM)                           | 17280                              | 34.56            | 0.13x                        | No                        | No                        | M*N                                               |

| Homogeneous<br>EIE-like                                     | 10176                              | 20.35            | 1.0x                         | No                        | Yes                       | N                                                 |

| (SpMM)                                                      | 10176                              | 20.35            | 1.0X                         | Yes                       | No                        | М                                                 |

| Homogeneous<br>ExTensor-like<br>(Inner-product<br>SpGEMM)   | 4992                               | 9.98             | 2.6x                         | Yes                       | Yes                       | M or N                                            |

| Homogeneous<br>OuterSPACE-like<br>(Outer-product<br>SpGEMM) | 12032                              | 24.06            | 0.4x                         | Yes                       | Yes                       | к                                                 |

| Homogeneous<br>MatRaptor-like<br>(Gustavson's<br>SpGEMM)    | 8320                               | 16.64            | 0.6x                         | Yes                       | Yes                       | Ν                                                 |

| Homogeneous<br>Hybrid<br>(TPU + EIE +<br>ExTensor-like)     | 4480                               | 8.96             | 6.2x                         | Yes                       | Yes                       | M*N, N, or<br>M                                   |

| Heterogeneous<br>AESPA <sup>+</sup><br>(This work)          | 11008                              | 16.90            | 7.9x                         | Yes                       | Yes                       | Variable<br>(Flexible)                            |

Fig. 1: Design characteristics of homogeneous sparse accelerators (consisting of one type of sub-accelerator) versus heterogeneous sparse accelerators (consisting of 2+ types of sub-accelerators). Matrix **A** is  $M \times K$  and Matrix **B** is  $K \times N$ .

performs well for workloads of high unstructured sparsity, but not for dense computations due to its sparse controller overhead. Large datacenters require flexibility, as in they must have the compute and memory resources to perform all current and future workloads efficiently. **To address this challenge,** we propose a new *heterogeneous* sparse accelerator and scheduling techniques to enable high efficiency across a diverse set of workloads. To realize this architecture, we identify three challenges that we address in this work.

**Challenge 1: Building Blocks.** The first challenge is to identify the right sparse sub-accelerator building blocks. Recently, numerous sparse architectures have been proposed for different applications [5], [15], [15], [18], [19], [40], [42], [43], [52], [53], [56], [59], [62]. There seems to be dozens of new sparse matrix multiplication accelerators proposed for every new application. This is a growing problem because there are many sparse accelerators that are similar. For example, both MatRaptor [52] and Gamma [59] utilize Gustavson's Algorithm. Detailed explanation is in Section III.

To address this challenge, we turn to TACO, a popular

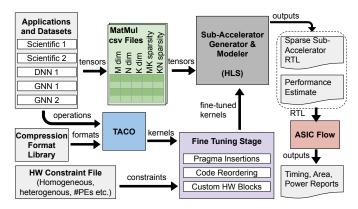

sparse tensor compiler [7], [8], [25]. Many of the subaccelerators can be described at an algorithmic level using insights from TACO. 'Dense' sub-accelerators operate on uncompressed input tensor operands, while 'sparse' subaccelerators operate on compressed input tensor operands. The compression format combination of the input tensors influence the type of dataflow the sparse sub-accelerator utilizes, which is discussed in Section II. We propose a new sparse subaccelerator design methodology named HARD TACO that can generate the RTL for different distinct sub-accelerators for fair performance, power, and area estimates. HARD TACO contains a hardware fine-tuning stage that adds pragmas on top of the TACO output kernel C++ code (shown in Fig 2). The updated code then goes to a HLS tool to generate functional sparse accelerators and controllers. Similar high productivity hardware generation tools include MAGNet [54] and Deepburning-GL [34], but they cannot generate all types of sparse sub-accelerators that HARD TACO can.

Challenge 2: Hardware Design-space Exploration. The second challenge relates to identifying the appropriate designpoint using the sub-accelerator building blocks and contrast it against homogeneous alternatives. From a physical die perspective, different sub-accelerators consume different area and power overhead. Under a given area constraint, sub-accelerators with smaller PEs can achieve higher TFlops/second than sub-accelerator with larger PEs which have significantly more control overhead. On the other hand sub-accelerator with larger PEs due to control logic can handle sparsity more efficiently. Additionally, to build a heterogeneous sparse accelerator, it is important to allocate the right amount of compute and memory resources. Some sub-accelerators require more memory accesses than others, and often lead to lower operational intensity. Fig 1 shows different types of homogeneous accelerators (consisting of one type of sub-accelerator). A homogeneous TPU-like accelerator [21] computes GEMM operations (dense matrix  $\times$ dense matrix), and a homogeneous EIE-like accelerator [18] computes SpMM operations (sparse matrix  $\times$  dense matrix or dense matrix  $\times$  sparse matrix). Homogeneous ExTensor [19], OuterSPACE [40], and MatRaptor-like [52] accelerators all compute SpGEMM operations (sparse matrix × sparse matrix); utilizing inner product, outer product and Gustavson's algorithm respectively. The different microarchitecture and sparse controller for each sub-accelerator results in different processing element (PE) sizes. With a normalized area constraint, a Homogeneous TPU-like accelerator can achieve  $3.4 \times$  higher peak TFLOPS/second. Additionally, the type of dataflow used for these accelerator can limit which the amount of parallelism achieved within the accelerator. The OuterSPACE accelerator is bounded by the workload's K dimension; therefore, there will be underutilization if the K dimension is smaller than the number of OuterSPACE PEs available. Fig 1 also presents homogeneous hybrid accelerators. These type of accelerators contain the necessary sparse controller to support multiple types of operations at the cost of lower max TFLOPS/s.

To address this challenge, we propose AESPA ( $\underline{a}$  heterogeneous sparse accelerator) that efficiently interconnect many different sub-accelerators and scratchpad memories. AESPA provides flexibility (variable parallelism dimension bounds) through heterogeneity by having many types of sub-accelerators while achieving higher TFLOPS/s than the homogeneous hybrid approach across a diverse set of workloads.

**Challenge 3: Scheduling/Mapping.** The third challenge, is to determine what scheduling strategies provide the best performance, energy efficiency, and utilization. This is actually the first work (to the best of our knowledge) to unravel the challenges of scheduling on heterogeneous sparse sub-accelerators while previous works look solely into heterogeneous dense sub-accelerators [3], [6], [16], [27].

To address this challenge, we propose various scheduling strategies aimed at utilizing all sub-accelerators. Specifically, we look into strategies that can (1) partition a single tensor kernel to utilize *all* sub-accelerators, and/or (2) partition independent tensor kernels across diverse sub-accelerators for multi-tenancy. Different sparse sub-accelerators may require input tensors to be of a certain format before computation (discussed in Section III), which we address by placing custom hardware format converters into AESPA.

# In summary, the key contributions of this paper are:

- We propose a new class of sparse tensor accelerators that leverages the idea of heterogeneous sub-accelerators, each optimized for a specific sparse dataflow (and corresponding compression format).

- We develop HARD TACO, a productive sparse and dense sub-accelerator generation design flow for quick performance, area, and power analysis. (Refer to Section III.)

- We design AESPA, a heterogeneous sparse accelerator that stitches different types of sub-accelerators together. (Refer to Section IV.)

- We propose various scheduling strategies for heterogeneous sparse accelerators. (Refer to Section V.)

- Our findings show that AESPA with optimized scheduling achieves 1.96× higher performance, and 7.9× better energy delay product (EDP) than a Homogeneous EIE-like accelerator with our diverse workload suite.

To the best of our knowledge, this is the first work to analyze how to build a heterogeneous sparse accelerator with various sub-accelerator types, and the first work to propose scheduling policies for such accelerators.

## II. BACKGROUND

This section first introduces the main compression formats used in this work. We use a taxonomy to express matrix multiplication algorithms and and sparse accelerator dataflows based on the operands' compression format.

#### A. Sparse Compression Formats

There are numerous types of compression formats, both structured and unstructured. For this taxonomy, we focus on unstructured compression formats used directly for computation. We refer to it as *compute compression format (CCF)* throughout the rest of the paper. To express CSR or CSC (shown in the top section of Fig 3), we follow a naming scheme inspired by TACO [7] and ExTensor [19]. Each dimension of a matrix (two-dimensional tensor) can be uncompressed or compressed. With this method, CSR and CSC can be thought of as the same format, but compressed in a different mode orientation [31].

Following the  $M \times N \times K$  matrix multiplication convention, Matrix **A** has dimensions  $M \times K$  and Matrix **B** has dimensions  $K \times N$ . If Matrix **A** is stored in CSR format, then there is a row pointer for every row and a column index for every nonzero value. We represent CSR by  $U_M C_K$  with 'U' meaning 'uncompressed' and 'C' meaning 'compressed'. The subscript variables represent the dimensions of the matrix. Dimension M is considered uncompressed as CSR follows a row-major ordering, and each row location must be specified by the row pointer. Alternatively, if Matrix **A** is stored in CSC format, we represent it by  $U_K C_M$ . If Matrix **B** is stored fully uncompressed (dense), it is  $U_K U_N$ .

# B. Proposed Taxonomy with TACO

Real world tensors are often sparse, which lead to ineffectual computations (e.g. multiplications with zero-valued operands) on dense hardware. CCFs enable algorithms that can skip these computations by utilizing bookkeeping metadata to indicate where the nonzero elements are located. Each tensor operand has its own compression format. Throughout the rest of the paper, we only read the CCFs in concordant fashion (following the same mode orientation). We propose a taxonomy template for matrix multiplications that follows:

# (A, B): format(TensorA), format(TensorB)

To illustrate the taxonomy template and how ineffectual computations are skipped, we use TACO (a tensor algebra compiler for kernel generation) to generate five different matrix multiplication kernels shown in Fig 2. For example, Fig 2c shows a SpGEMM kernel with Matrix **A** compressed in  $U_M C_K$  and Matrix **B** compressed in  $U_N C_K$ .

Using our template, we refer to this as:

$$(\boldsymbol{A},\boldsymbol{B}): U_M C_K, U_N C_K$$

Fig 2a shows a TACO generated kernel with both matrices computed uncompressed  $(U_M U_K, U_K U_N)$ . All loops depend on the dimensions of the GEMM operation. Since there is no way to distinguish whether the input matrices' elements are zero-valued or nonzero-valued, all computations are scheduled regardless of sparsity. Fig 2b shows a TACO kernel with the CCF combination of  $U_M U_K, U_N C_K$ . Matrix **B** is compressed with only nonzero values along the K dimensions, as shown in line 22. Matrix **A** is uncompressed, so a zerovalue (from Matrix **A**)  $\times$  nonzero-value (from Matrix **B**) computation can still occur. To completely eliminate any ineffectual computations from zero-value multiplications, both matrices must be compressed. Fig 2c shows a TACO kernel

```

// TPU-like (U_{_{\!M}}U_{_{\!K}},U_{_{\!K}}U_{_{\!N}}) TACO Modeling with UNROLL HLS Pragma

for (int32_t m = 0; m < A1_dimension; m++) {

#pragma HLS unroll</pre>

1

for (int32_t n = 0; n < B2_dimension; n++) {

3

ıgma HLS unroll

#pra

int32_t n0 = m * 02 dimension + n;

5

double tk0_val = 0.0;

for (int32_t k = 0; k < B1_dimension; k++) {

int32_t kA = m * A2_dimension + k;

int32_t nB = k * B2_dimension + n;</pre>

9

tkO_val += A_vals[kA] * B_vals[nB];

10

11

0_vals[n0] = tk0_val;

12

13

-}

(a)

14

15

16

// EIE-like (U_M U_K, U_N C_K) TACO Modeling with UNROLL HLS Pragma

17

for (int32 t m

0:

m < A1 dimension; m++)</pre>

for (int32_t n = 0; n < B2_dimension; n++)</pre>

19

#pragma HI

int32_t n0 = m * 02_dimension + n;

double tk0 val = 0.0;

21

domse tx__uar_ots;

for (int32 t kB = B2_pos[n]; kB < B2_pos[(n + 1)]; kB++) {

int32 t k = B2_cord[kB];

int32 t kA = m * A2_dimension + k;

tko_ual += A_uals[kA] * B_uals[kB];

22

23

24

25

26

0 vals[n0] = tk0 val;

27

28

}

(b)

29

}

- ຈຸດ-

// ExTensor-like (U<sub>N</sub>C<sub>k</sub>, U<sub>N</sub>C<sub>k</sub>) TACO Modeling with UNROLL HLS Pragma

for (int32_t m = 0; m < Al_dimension; m++) {

for (int32_t n = 0; n < B2_dimension; n++) {</pre>

31

32

33

pragma HLS unroll

int32 t n0 = m * 02 dimension + n;

34

35

int32_t k0 = m + O__utmension + k;

double tk0_val = 0.0;

int32_t kA = A2_pos[m];

int32_t pA2_end = A2_pos[(m + 1)];

int32_t kB = B2_pos[n];

36

37

38

39

40

41

int32_t pB2_end = B2_pos[(n + 1)];

while (kA < pA2_end && kB < pB2_end) {

int32_t kA0 = A2_crd[kA];

int32_t kB0 = B2_crd[kB];

int32_t k = TACO_MIN(kA0,kB0);

</pre>

42

43

44

45

46

47

if (kA0 == k && kB0 == k) {

tk0_val += A_vals[kA] * B_vals[kB];

48

49

kA += (int32_t) (kA0 == k);

50

kB += (int32_t) (kB0 == k);

51

52

0 vals[n0] = tk0 val;

}

53

(C)

54

55

56 // OuterSPACE-like (U<sub>k</sub>C<sub>k</sub>,U<sub>k</sub>C<sub>k</sub>) TACO Modeling with UNROLL HLS Pragma

57 for (int32_t k = 0; k < Bl_dimension; k++) {</pre>

58

uprol 1

#pragma HLS

for (int32_t mA = A2_pos[k]; mA < A2_pos[(k + 1)]; mA++) {</pre>

59

60

= A2 crd[mA];

int32 t m

for (int32_t nB = B2_pos[k]; nB < B2_pos[(k + 1)]; nB++) {</pre>

61

int32_t n = B2_crd[nB];

int32_t n0 = m * 02_dimension + n;

62

63

O_vals[n0] = O_vals[n0] + A_vals[mA] * B_vals[nB];

64

65

66

}

67

}

(d)

68-

// MatRaptor-like (U_{k}C_{k'}, U_{k}C_{k'}) TACO Modeling with UNROLL HLS Pragma for (int32 t n = 0; n < B2_dimension; n++) {

69

70

71

#pr

for (int32_t kB = B2_pos[n]; kB < B2_pos[(n + 1)]; kB++) {</pre>

72

73

B2 crd[kB];

Ints_t k = b_ctd(RB);

for (int32_t mA = A2_pos[k]; mA < A2_pos[(k + 1)]; mA++) {

int32_t m = A2_crd[mA];

int32_t n0 = m * 02_dimension + n;

74

75

76

77

O_vals[n0] = O_vals[n0] + A_vals[mA] * B_vals[kB];

78

79

(e)

}

80

```

Fig. 2: TACO generated matrix multiplication kernels with UNROLL HLS Pragma for different sub-accelerator types. Operand casting code omitted for brevity.

with the CCF combination of  $U_M C_K$ ,  $U_N C_K$ . Both matrices hold position indices (also commonly referred to coordinates) of the nonzero values along the K dimension, and both indices must match (refer to line 46) to indicate a valid nonzero computation. Fig 2d shows a TACO kernel with the CCF combination of  $U_K C_M$ ,  $U_K C_N$ . Line 57 shows that the kernel

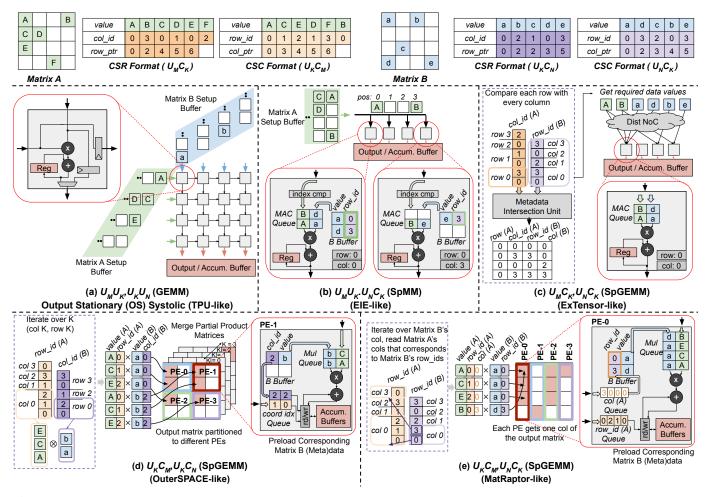

Fig. 3: Examples showing different MatMul accelerator classes. The top row shows two input matrices along with their compressed equivalents. *value* represents the nonzero value. *col\_id* and *row\_id* represent the coordinate (crd) of the nonzero value. *row\_ptr* and *col\_ptr* represent the position (pos) where a row or column begins. Inspired from state-of-the-art sparse accelerators, (a-e) presents how different Compute Compression Formats (CCFs) combinations can be mapped onto hardware.

is iterating over the uncompressed K dimension, while line 59 and line 61 show that it is iterating over compressed M and N dimension respectively. Different CCF combinations will generate different TACO outputs. Although the compression format of the output matrix (**O**) may vary, we default it to fully uncompressed (dense) for the rest of the paper, and can be hidden within the taxonomy unless compressed otherwise. The TACO kernels with different CCFs can be correlated to the computation behaviors of dense and sparse accelerators. The next section will describe more in detail on how Fig 2a,b,c,d,e correlate to TPU [21], EIE [18], ExTensor [19], OuterSPACE [40], and MatRaptor [52] respectively.

# III. HARD TACO: SPARSE SUB-ACCELERATORS GENERATOR

This section first introduces different sparse sub-accelerator microarchitectures, each utilizing a TACO kernel discussed in Section II. Then, this section proposes HARD TACO for productive generation of hardware for fast performance, power, and area estimates.

#### A. Classifying Custom Sparse Accelerators

In this subsection, we use the TACO based taxonomy to classify state-of-the-art sparse accelerators. The examples following show exactly how the compression formats are used for sparse computations, and which matrix dimension(s) is unrolled spatially on hardware, as presented in the most right column in Fig 1. The tensors are compressed in (A, B) order.

$U_M U_K, U_K U_N$  (GEMM, TPU-like). Fig 3a shows an output stationary systolic array [47]. Both input matrices are in dense (uncompressed) format and are fed into the Processing Element (PE) array in a store-and-forward manner. Each PE receives input data from the top and left side, computes a MAC operation, stores the partial sum locally, and forwards out data from the bottom and right side. Once all computations are finished, the completed partial sums are sent to the output accumulation buffer. With a flexible interconnect [15], [19], [28], it is possible to utilize M × N PEs in parallel.

$U_M C_K, U_K U_N$  or  $U_M U_K, U_N C_K$  (SpMM, EIE-like). Based on the accelerator EIE [18], Fig 3b shows a scenario in which Matrix **A** is in dense (uncompressed) format, and Matrix **B** is in  $U_N C_K$  format. Each column of Matrix **B** (row\_ids and values) is loaded into the buffer of a PE, hence it is possible to utilize a maximum of N PEs in parallel. Matrix A is streamed through a bus to all PEs. An index comparison module is used to find valid nonzero computations by using the bus position of Matrix **A** and row\_ids of Matrix **B**. The valid computations are then scheduled onto the MAC Queue. Each PE has an output register to accumulate the partial sums. Note that the architecture also support a scenario in which matrix A is compressed in  $U_M C_K$  and matrix B is uncompressed.

$U_M C_K, U_N C_K$  (SpGEMM, ExTensor-like). Based on the accelerator Extensor [19] (inner-product), Fig 3c shows Matrix **A** in  $U_M C_K$  format, and Matrix **B** in  $U_N C_K$  format. Comparing each row of Matrix **A** with every column of Matrix **B**, Matrix **A**'s *col\_ids* and **B**'s *row\_ids* go into a hardware intersection unit that quickly finds matching indices. Using the indices, the corresponding *values* are fetched from both matrices. The *values* are then distributed through a Networkon-Chip (NoC) to the corresponding PEs for computation. When comparing each row of Matrix **A** with every column of Matrix **B**, the maximum PE utilization is N. When comparing each column of Matrix **B** with every row of Matrix **A**, the maximum PE utilization is M.

$U_K C_M, U_K C_N$  (SpGEMM, OuterSPACE-like). Based on the accelerators OuterSPACE [40] and SCNN [42] (outerproduct), Fig 3d shows a scenario in which Matrix **A** is in  $U_K C_M$  format, and Matrix **B** is in  $U_K C_N$  format. Iterating over the K dimension <sup>1</sup>, the accelerator fetches the indices  $(row_ids, col_ids)$  and nonzero data (values) for outer product computation. Each PE owns a partition of the output matrix accumulation, and a NoC sends the fetched input meta(data) to the corresponding PE. Necessary Matrix **B**'s (meta)data is first loaded into the PEs' B buffers, and then Matrix **A**'s (meta)data is streamed in. Each PE also has its own accumulation buffer that contains the partial sums of each output matrix position the PE owns. The indices  $(row_ids, col_ids)$  are used to read and write to the correct location.

$U_K C_M, U_N C_K$  (SpGEMM, MatRaptor-like). Based on the accelerator MatRaptor [52] (column-wise-product or Gustavson's algorithm), Fig 3e shows a scenario in which Matrix **A** is in  $U_K C_M$  format, and Matrix **B** is in  $U_N C_K$  format. Iterating over Matrix **B**'s columns, a controller reads Matrix **A**'s columns that corresponds to Matrix **B**'s  $row_i ds$ . Each PE owns a column partition of the output matrix, hence the maximum PE utilization is N. Necessary Matrix **B**'s (meta)data is first loaded into the PEs' B buffers, and then Matrix **A**'s (meta)data is streamed in. Matrix **A**'s *col* is used to compare with Matrix **B**'s  $row_i ds$  to schedule useful computations into the MAC Queue. Matrix **A**'s  $row_i ds$  are used to read and write to the correct location within the accumulation buffer. Note that Gamma [59] also uses Gustavson's algorithm, although Gamma traverses row-wise through the matrices

<sup>1</sup>For hardware generation ease, we unrolled the K dimension spatially (shown in Fig 2d), hence the maximum PE utilization is K.

Fig. 4: *Hard TACO* design flow overview for estimating sub-accelerator performance, power, and area cost.

rather than column-wise.

# B. Hard TACO Design Flow

*Hard TACO* generates the sparse sub-accelerators in Section III-A to get fast performance and hardware resource consumption for design space exploration. Fig 4 shows our design flow at a high level. First, matrix multiplication operations using different CCFs are sent as inputs into the TACO compiler. The TACO compiler generates C++ code to the '*Fine Tuning Stage*' along with user defined hardware constraint parameters, which includes number of PEs, memory type, etc.

The 'Fine Tuning Stage' inserts pragmas and reorders the TACO output to meet the hardware constraints. Fig 2 shows where HLS UNROLL pragmas are inserted to unroll a loop spatially, which creates multiple hardware instances for parallel computations. The PIPELINE pragma attempts to achieve low initiation interval within a code block. BIND\_OP pragma hints operations to be synthesized using LUTs or DSPs. For this work, we use the BIND\_OP pragma to synthesize the accelerator PEs onto the DSPs. ALLOCATE pragma limits how many hardware instances can be generated of a particular compute function. ARRAY\_PARTITION pragma determines the local buffer bandwidth by modeling memory instances to behave like SRAMs or registers.

Next, the fine-tuned kernels go directly into the HLS tool. Many HLS tools translate code written in a high level language, such as C++, into RTL. For this work, we use Xilinx Vitis HLS, though we note that any other HLS tool could be used. The outputs include RTL, FPGA hardware consumption, and performance estimates. The RTL then goes through an ASIC flow to get more detailed timing, area, and power reports.

Hard TACO generates quick hardware cost estimates of various sparse sub-accelerators, which become building blocks for a larger heterogeneous accelerator design.

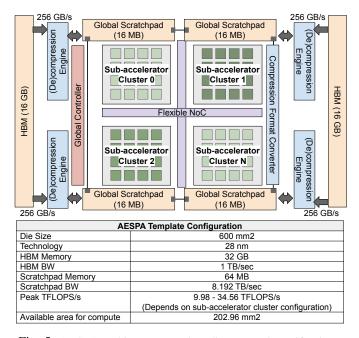

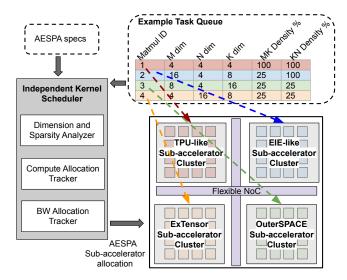

## **IV. AESPA ARCHITECTURE TEMPLATE**

This section proposes AESPA, a heterogeneous sparse accelerator. Fig 5 shows the high level architecture template and specification for building AESPA. The die size is capped at 600  $mm^2$ , which is approximately the same size as TPU v2 [22]. HBM memory size and bandwidth is set to 32 GB and 1 TB/second respectively. Global scratchpad size and bandwidth is set to 64 MB and 8.192 TB/second respectively. We utilize a highly flexible NoC, often used in previous works [5], [15], [19], [28], to send data from the global buffer to all PEs.

## A. Sub-Accelerator Cluster

The conglomerate of sub-accelerator type, memory system, workload dimension, and sparsity ratio determines the operational intensity and performance of a given kernel. AESPA enables flexibility by having various sub-accelerator clusters (shown in Fig 5). The number of PEs in each sub-accelerator cluster is decided based on performance and energy metrics across a diverse workload set. It is a parameter for design space exploration in the evaluation section (Section VII). Using the accelerator template, we create many possible configurations of AESPAs.

The number of PEs also depend on the available area for compute allocated on the die. After accounting for the memory and peripheral logic area, only 202.96  $mm^2$  of space is left for compute. Depending the type and quantity of sub-accelerators allocated, the peak TFLOPS/second ranges from 9.98 to 34.56.

# B. Flexible Global Buffer

AESPA consists of a double buffered and flexible Global scratchpad which can support flexible-sized partitions for different matrices and sub-matrices (Section V-A). The Global scratchpad is distributed such that each sub-accelerator is backed by one slice of the scratchpad. The Global scratchpad can store matrix and sub-matrix data and meta-data in multiple layouts and multiple compression formats as required by the sub-accelerators. For example, Outer-space like sub-accelerator requires both matrices in a K-major layout with M and N ranks compressed while Extensor-like sub-accelerator requires matrix A in the M-major layout and matrix B in the N-major layout, both matrices having K rank compressed.

## C. (De)compressor and Format Conversions

Decompressors are used so that the data in HBM can be stored in a format with low memory footprint [45]. This feature allows faster transfer time and better energy efficiency, as a word of memory transfer from main memory is  $\sim 6400 \times$ greater in energy consumption than a single integer add operation [18]. It is possible to bypass decompression if the sparse sub-accelerator needs to compute on the compressed format directly. Additionally, format converters are used to enable sub-accelerators under a scenario in which the data transferred from host is compressed in a format that does not match the accelerator's CCF. For example, a  $U_K C_M, U_K C_N$  based accelerator is instantiated, but the input tensor is transferred from host to accelerator as  $U_M C_K$ ; therefore, a  $U_M C_K \longrightarrow$  $U_K C_M$  hardware block next to the accelerator is required. A typical workaround is to convert the tensors to the right format in the host before transferring, but at the cost of potentially increasing the transfer size. Recent works propose

Fig. 5: AESPA architecture template diagram and specifications.

hardware units that do format conversion on the fly [1]. The AESPA template determines the type and quantity of sub-accelerators used to create a large heterogeneous sparse accelerator. Different AESPA configurations are explored in the evaluation section.

# V. SCHEDULING FOR AESPA

Scheduling matrix multiplication kernels onto sparse accelerators has its own set of problems. Input tensors are expected to be compressed in a specific format for computation. For example, a  $U_M U_K, U_N C_K$  sub-accelerator requires Matrix **A** to be in  $U_M U_K$  and Matrix **B** to be in  $U_N C_K$ . Homogeneous accelerators contain PEs that can utilize a specific compute format combination. Heterogeneous accelerators, on the hand, contains different PEs with unique sparse controller and microarchitectures. If the entire tensor matrix is compressed in one format, a portion of the PEs will remain underutilized.

The first scheduling technique (discussed in Section V-A) partitions the input tensors into different compression formats to maximize compute utilization of all sub-accelerators within a heterogeneous accelerator. This maximizes peak performance of a single kernel for latency critical tasks.

The second scheduling technique (discussed in Section V-B) allocates many independent kernels onto to the heterogeneous accelerator in parallel. This is similar in concept to multi-tenancy proposed in recent works [6], [16].

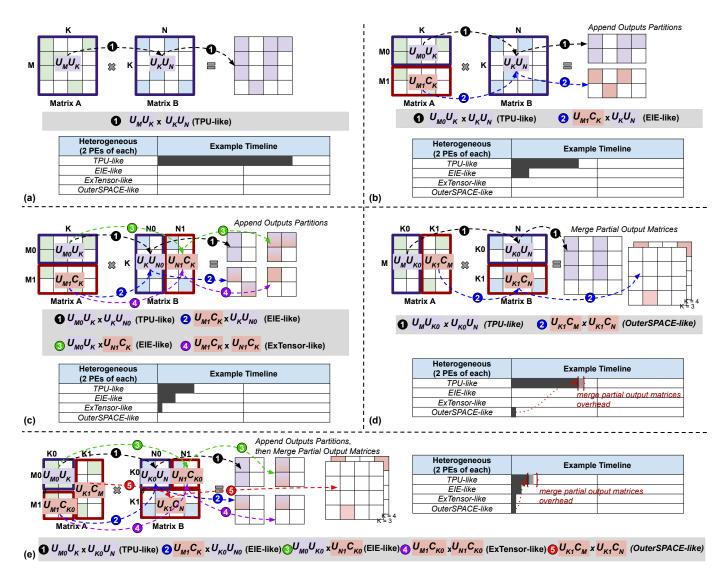

# A. Single Kernel Scheduling (Max TFLOPs) Example

Fig 6 shows the benefit of *single kernel scheduling* on a single matrix multiplication operation. The examples model a heterogeneous accelerator with four subaccelerators:  $U_M U_K, U_K U_N$  (TPU-like),  $U_M U_K, U_N C_K$  &  $U_M C_K, U_K U_N$  (EIE-like),  $U_M C_K, U_N C_K$  (ExTensor-like),

Fig. 6: Examples showing how a single matrix multiplication kernel can be scheduled onto heterogeneous sparse accelerator to achieve peak performance on a single kernel. (a) Scenario when only TPU-like sub-accelerator is active. (b) Scenario when TPU and EIE-like sub-accelerators are active. (c) Scenario when TPU, EIE, and ExTensor-like sub-accelerators are active. (d) Scenario when TPU and OuterSPACE-like sub-accelerators are active. (e) Scenario when TPU, EIE, ExTensor, and OuterSPACE-like sub-accelerators are active. Final runtime is the maximum runtime across sub-accelerators.

and  $U_K C_M$ ,  $U_K C_N$  (OuterSPACE-like). Each sub-accelerator has two PEs each for a total of 8 PEs. This example assumes that the system is compute bounded, and that there is sufficient memory bandwidth.

Fig 6a shows a baseline case of  $U_M U_K, U_K U_N$ . Only the TPU-like sub-accelerator can compute this CCF combination. As a result, 6 of the total 8 PEs remain idle. The runtime is approximated by the number of iterations from the nested loop shown in Fig 2a. In the case of Fig 6a, given that the M, N, K dimensions are all four, the total number of iterations is 64. With two parallel PEs for this TPU-like sub-accelerator, the total execution is 32 cycles.

Fig 6b shows an example with Matrix **A** split in half across the M dimension. The top half is uncompressed  $(U_{M0}U_K)$ and the bottom half is compressed in  $U_{M1}C_K$ . The hybrid format can be preprocessed beforehand, or converted with the hardware format converters found in AESPA. Both TPU and EIE like sub-accelerators are active. Note that the number of iterations for sparse sub-accelerators depends on the sparsity of the input tensor. In Fig 6b, there is approximately one nonzero element per row of  $U_{M1}C_K$ , which determines the loop count of line 22 of Fig 2. The TPU-like runtime is half of the previous example because the M dimension is split in half. The EIE-like runtime is 4 cycles, calculated by M1 × K × N × MK density divided by number of PEs.

Fig 6c has Matrix **A** split across the M dimension and Matrix **B** split across the N dimension. This scenario activates three out of the four sub-accelerators (TPU-like, EIE-like and ExTensor-like). The TPU-like sub-accelerator cluster has a runtime of 8 cycles, from M0  $\times$  K  $\times$  N0 / number of PEs.

Fig. 7: High level example showing how different workloads are allocated to different sub-accelerators in a heterogeneous sparse accelerator.

The EIE-like accelerator is utilized for two computation parts, highlighted in Fig 6c computation **2** and **3**. Part **2** runtime is half of Fig 6b's, as the N dimension is split by half. Part **3** runtime is similar to **2**. The total computation cycle for EIE-like is 4 cycles. ExTensor-like runtime is a cycle, approximated by M1  $\times$  K  $\times$  N1  $\times$  MK density  $\times$  KN density divided by number of PEs.

Fig 6d is split across the K dimension for both input matrices. The TPU-like runtime is 16 cycles, from  $M \times K0 \times N$  / number of PEs, while the OuterSPACE-like runtime is a cycle, approximated by  $M \times K1 \times N \times MK$  density  $\times$  KN density divided by number of PEs. Since the reduction dimension (K) is split, remaining partial output matrices are merged at the end.

Fig 6e is split across the M, N, and K dimension. This allows all of the sub-accelerator types to compute a single kernel together. The TPU-like sub-accelerator cluster has a runtime of 4 cycles, from M0  $\times$  K0  $\times$  N0 / number of PEs. The EIE-like accelerator is utilized for two computation parts, highlighted in Fig 6e computation 2 and 3. The runtime for EIE-like is 2 cycles (1 cycle for 2), and 1 cycle for 3). ExTensor-like runtime is a cycle, approximated by M1  $\times$  K0  $\times$  N1  $\times$  MK density  $\times$  KN density divided by number of PEs. OuterSPACE-like runtime is a cycle, similar to that of Fig 6d. Since the reduction dimension (K) is split, remaining partial output matrices are merged at the end.

Our single kernel scheduling strategy for heterogeneous sparse accelerators enables high utilization for all available PEs of various sub-accelerator types. As shown in Fig 6e, the strategy improves performance, which is important for latency critical kernels. The performance benefit depends on the AESPA configuration, memory bandwidth, and workload. (Discussed in more detail in (Section VII).

TABLE I: Tensor characteristics found in various applications.

| Name            | Application    | Dimension<br>(M,K,N)           | Density %<br>(MK,KN) |

|-----------------|----------------|--------------------------------|----------------------|

| chem97ZtZ       | Stat Problem   | $2.5k \times 2.5k \times 1.2k$ | 0.11,100             |

| journals        | Weighted Graph | 124×124×62                     | 78.5,100             |

| m3plates        | Acoustics      | $11k \times 11k \times 5.5k$   | 0.0054,100           |

| synthetic_dense | Varies         | $5k \times 5k \times 2.5k$     | 100,100              |

| bibd_81_3       | Combinatorial  | $3.2k \times 85k \times 43k$   | 0.093,100            |

| speech          | Deep Learning  | $7.7k \times 2.6k \times 1.3k$ | 5,100                |

| gnmt            | Deep Learning  | $1.6k \times 1k \times 36k$    | 50,30                |

| transformer     | Deep Learning  | $32k \times 84 \times 1k$      | 50,30                |

| citeseer        | GNN            | $3.3k \times 3.3k \times 3.7k$ | 0.11,0.85            |

#### B. Many Kernels Scheduling Example

For large datacenters, it is common to have many kernels in a queue waiting to be executed. Rather than partitioning the tensors into hierarchical formats to achieve high TFLOPS/second per kernel as observed in the 'single kernel scheduling', 'many kernels scheduling' optimizes for multiple kernels, each with tensors compressed in one format. Fig 7 shows a high level figure with four matrix multiplication kernels in the task queue. The figure also shows an AESPA configuration of four sub-accelerator types (TPU, EIE, ExTensor, and OuterSPACE-like) with 16 PEs each.

The first task (red) is ideal for the TPU-like sub-accelerator. This is because the tensors are completely dense, and all 16 PEs can be utilized from the  $M \times N$  bound (refer to the parallelism dimension bound table in Fig 1). The second task (blue) is ideal for the EIE-like sub-accelerator. This is because the M dimension can be fully unrolled onto the PEs, and there is one input matrix that is relatively sparse. The third (green) and fourth (orange) tasks have two matrices that are relatively sparse, so they run more efficiently on sub-accelerators that support SpGEMM. The third (green) has a K dimension that can fully unrolled onto an OuterSPACE-like sub-accelerator, and the fourth (orange) has a N dimension that can be fully unrolled onto an ExTensor-like sub-accelerator.

Our many kernel scheduling strategy enables good utilization for multiple kernels running in parallel. However, this again depends heavily on the memory bandwidth, workload, and AESPA configuration. (Discussed in more detail in (Section VII).

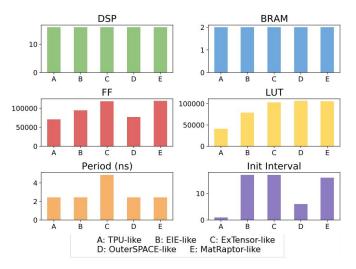

#### VI. METHODOLOGY

We first model each basic sub-accelerator class (refer to Sec III-A) using the *Hard TACO* design flow. For HLS tool, we used Xilinx Vitis and ran hardware emulation on Alveo U50. Functional correctness was verified for all sub-accelerators. We get the RTL, estimated FPGA hardware resource consumption and performance from Vitis. The generated RTL then goes through an ASIC flow using 28nm technology for a more detailed area, power, and timing report. Synopsys DC compiler was used for synthesis and Cadence Innovus was used for place and route.

The hardware generation time on Vitis was significant when modeling large designs (128 PEs +), so we designed small subaccelerator cores, each utilizing 16 int32 PEs. Each core was

Fig. 8: Xilinx U50 FPGA hardware resource and performance report on different sub-accelerator types with 16 PEs each.

also implemented to have a local buffer, which stores three 16  $\times$  16 tiles (one for each tensor operand). The local buffer size is different for sparse sub-accelerators as they require more metadata storage. Floating point units were not enabled when generating the sub-accelerators from Vitis. To approximate the cost of enabling floating point operations, we add the ASIC area and power costs of our internal FP units to the post-ASIC flow sub-accelerator reports. We scale the area and power of the generated small sub-accelerator units to larger designs (4196 PEs +) linearly. Though not realistic, we believe that it is still a fair estimation, given each generated sub-accelerator is self sufficient on its own (contains its own local buffers and controllers). With the generated sub-accelerators, we are able to approximate the amount of TFLOPS/s achievable given an area constraint.

To generalize how an architecture will behave for realistic workloads (HPC [9], DNN [10], and GNN [24], [57]) shown in Table I, we developed an analytical model that approximates the performance by first estimating the tripcount of the compute loop of each matrix multiplication kernel shown in Fig 2. The number of iterations depend on the tensor dimension and sparsity. We assume uniform random sparsity. The memory bandwidth of the AESPA system is also integrated into the model, as sparse computations are often memory bounded [19], [52], [62]. For energy cost, we consider the utilization of the accelerator and the on-chip data movement.

To schedule operations onto heterogeneous accelerators, we conduct a search to find the best way to partition/configure a certain operation derived from our proposed strategies. For simplicity, we assume that the data compressed in the desired format(s) is sent directly from the host. Different configurations of AESPA are evaluated against state-of-the art accelerators presented in Fig 1.

## VII. EVALUATION

This section first analyzes the sub-accelerator costs using HARD TACO. Then, we evaluate the performance of AESPA

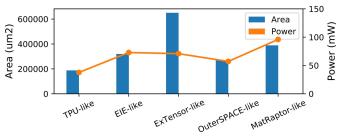

Fig. 9: 28nm ASIC area and power report on different subaccelerator types with 16 PEs each.

with our scheduling techniques against state of the art accelerator designs.

## A. Hard TACO Reports

Fig 8 shows the Xilinx U50 FPGA results on different subaccelerators. There are 16 PEs in each HLS design, hence why there are 16 DSPs. The number of FFs is high for ExTensor and MatRaptor-like sub-accelerators, while the number of LUTs is high for ExTensor, OuterSPACE, and MatRaptorlike sub-accelerators. TPU-like design has the least number of FFs and LUTs. This is intuitive because it does not need any extra metadata controller or index indirections that are required in sparse sub-accelerators. This TPU-like property is confirmed by the initiation interval of 1. An initiation interval of 1 means that it is completely pipelined, while a high initiation interval will induce a lot of stalls. EIE, Extensor, and MatRaptor-like all have initiation intervals of 17, 17, and 16 respectively. OuterSPACE-like design has a relatively lower initiation interval of 6. The period of ExTensor-like on the FPGA is almost  $2 \times$  greater than the others. The inner product dataflow that ExTensor implements contain lots of metadata intersections, which may not be efficient on the FPGA fabric.

To gain better understanding on the sub-accelerator designs, we synthesize the generated RTL on a 28nm process. Fig 9 shows the area and power report. All sub-accelerators met timing at 1 GHz. Floating point units overhead are added on top. Additionally, 32 32-bit wide FIFOs of depth 10 are added per initiation interval. This is a rough estimate to predict what the sub-accelerator overhead would be if it is fully pipelined with custom ASIC implementations. ExTensorlike's area is the largest, with almost  $3 \times$  greater than a TPUlike design. MatRaptor-like design is the most power-hungry among all, while OuterSPACE-like design is relatively low in area and power. We emphasize that custom hand-designed ASIC implementations may differ from the results gathered from the HLS tool, though we believe they are fair estimates of the building blocks for design space exploration. We utilize the area overhead of each sub-accelerator to find the peak TFLOPS/second of various accelerator types shown in Fig 1.

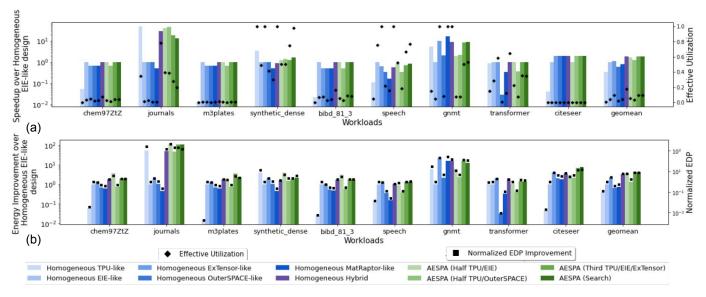

# B. AESPA Single Kernel Scheduling Evaluations

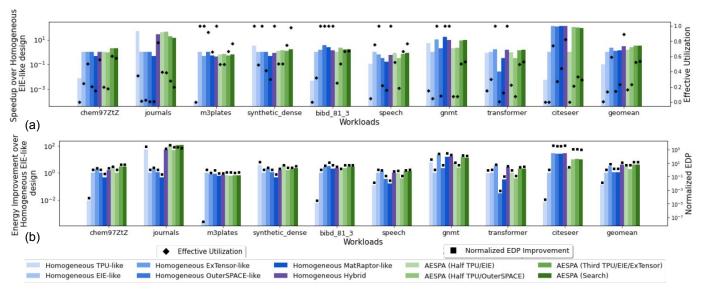

Fig 10 and Fig 11 shows how AESPA compares to other baselines when computing individual matrix multiplications.

Fig. 10: Evaluation against Homogeneous EIE-like with limited memory bandwidth. (a) shows speedup and effective utilization. (b) shows normalized energy and EDP improvement.

Fig. 11: Evaluation against Homogeneous EIE-like with unlimited memory bandwidth. (a) shows speedup and effective utilization. (b) shows normalized energy and EDP improvement.

The first six baselines are homogeneous accelerators. A homogeneous accelerator only contain one type of sub-accelerator. We also compare against a homogeneous hybrid design, in which the sub-accelerator can support the dataflows of all TPU-like, EIE-like, and ExTensor-like. The cost of this flexibility is extra area and power, which then reduce the peak TFLOPS/s achievable under an area constraint. Fig 1 shows that the TFLOPS/s of a homogeneous hybrid is just 8.96. For heterogeneous designs (AESPA), it is possible to achieve flexibility while still using basic sub-accelerators that can only support one type of sparse dataflow.

Fig 10 and Fig 11 show performance graphs with 1 TB/s

and unlimited memory bandwidth respectively. Both figures Part A shows the speedup over Homogeneous EIE-like design on the left Y axis and effective utilization on the right Y axis. Effective utilization is the percentage of effectual work done by the accelerator. It depends on (1) the parallelism dimension bound and the sparsity support the sub-accelerator enables (shown in Fig 1). Part B left Y axis shows the energy efficiency improvements over a Homogeneous EIE-like design, and the right Y axis shows the normalized EDP improvement.

M3plates (refer to Table I) has a very sparse Matrix **A**. The operational intensity is low and gets limited by the memory bandwidth, as shown by the low utilization points across all

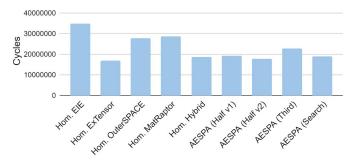

Fig. 12: Total cycles for completing all workloads using many kernel scheduling.

designs in Fig 10a. Fig 11a shows that with unlimited bandwidth, the performance utilization points increase drastically. Homogeneous TPU-like's utilization in this case is still low because it does not have any sparsity support. Citeseer also follows a similar pattern. Fig 10a shows significant performance degradation for Homogeneous OuterSPACE-like on Transformer. This is because the K dimension for the workload is small (value of 84), and OuterSPACE-like is generated with the K dimensions unrolled spatially; therefore, the utilization is bounded by the dimension of the workload. AESPA is able to have variable parallelism bounds, hence why AESPA (Half TPU/OuterSPACE) is able to achieve higher utilization. We compared against four configurations of AESPA, the first three have fixed ratios of sub-accelerators, while the last is high performance configuration searched by our model. Homogeneous hybrid has the highest effective utilization, for both limited and unlimited bandwidth. However, the smaller peak TFLOPS/s prevent it from obtaining larger speedup.

AESPA with our single kernel scheduling strategy is able to achieve  $1.96 \times$  speedup and  $7.9 \times$  EDP geomean improvement over Homogeneous EIE-like at a 1 TB/s memory bandwidth. With unlimited bandwidth, AESPA is able to achieve  $3.3 \times$  speedup and  $14.1 \times$  EDP geomean improvement. Against a Homogeneous Hybrid design, AESPA achieves  $1.03 \times$  speedup and  $1.28 \times$  EDP geomean improvement. With unlimited bandwidth, it becomes  $1.13 \times$  speedup and  $1.20 \times$ EDP geomean improvement.

# C. AESPA Many Kernel Scheduling Insights

Rather than achieving peak performance for a single kernel, as shown in the previous section, it is also possible to run multiple kernels in parallel on AESPA. The workload characteristics and resource availability determine which kernel gets mapped to which sub-accelerator cluster. In Fig 12, we evaluated all designs with unlimited bandwidth. AESPA is able to stay within 6% of the best baseline configuration for total runtime. With limited bandwidth, we observe more memory contention across parallel kernels, significantly impacting performance. We note that this analysis is very dependent on the workloads given, but it shows that there are many valid ways to run applications on a heterogeneous sparse accelerator.

# VIII. RELATED WORK

**Pre-RTL accelerator DSE**: Aladdin is a pre-RTL, powerperformance accelerator simulator [49]. Aladdin is an alternate methodology to HARD TACO to quickly get hardware and performance estimates. Interstellar [58], MAESTRO [26] and Timeloop [41] are analytical performance models for DNN accelerators. Herald [27] is an optimization framework for heterogeneous accelerator substrates for dense DNN workloads. It finds the optimal resource allocation for multiple-sub accelerators and determines the optimal schedule of multi-DNN workloads on the dense heterogeneous substrate. However, Herald only looked into dense accelerators, while we expand it to sparse accelerators. Numerous other works look into exploring parallelism for popular workloads [4], [12], [20], [51], [56].

Accelerator RTL Generators. Spiral is a HLS wrapper for FFTs [14] and MAGNet is a modular accelerator generator for neural networks [54]. DeepBurning-GL is a framework that generates different accelerators for GNNs. [34]. *Hard TACO* takes a unique approach by utilizing the output of an established sparse tensor compiler [8] to generate RTL. This allows people with compiler/algorithms background to intuitively understand what each sparse sub-accelerator is doing and their differences.

**Sparse accelerators**: Sparsity has been a key optimization target for HPC and AI workloads. Numerous accelerators have been proposed for SpMM and SpGEMM acceleration [2], [5], [11], [15], [17], [18], [19], [23], [29], [32], [34], [35], [39], [40], [43], [50], [52], [53], [56], [60]. Though there are a lot of unique sparse accelerators, we believe that they can all be grouped into classes based on their computation dataflow.

Recent works look into co-designing for sparse architectures. Sanger prunes the attention matrix for its reconfigurable architecture to exploit [36]. ESCALATE utilized kernel decomposition to accelerate CNN models [33]. G-Cos does a co-search on both the GNN and the accelerator to maximize accuracy and hardware efficiency. The authors also looked into sub-accelerator designs with various sparse dataflows [61]. SpAtten does pruning and quantization to achieve high energy efficiency [55].

## IX. FUTURE WORKS AND DISCUSSION

There is a wide range of sparse accelerators presented in industry and academia, each with some unique optimizations that cannot be modeled efficiently with HLS. These optimizations include load balancing mechanisms, structured sparsity support, etc. Although HLS is perfect for fast architecture exploration, it is more realistic to build custom IPs for deployment. Additionally, the field of scheduling on heterogeneous sparse accelerators is relatively unexplored compared to its dense counterpart. There are numerous opportunities for new hierarchical compression formats to utilize different sparse sub-accelerators.

## REFERENCES

- B. Asgari, R. Hadidi, J. Dierberger, C. Steinichen, and H. Kim, "Copernicus: Characterizing the performance implications of compression formats used in sparse workloads," *IISWC*, 2021.

- [2] A. Auten, M. Tomei, and R. Kumar, "Hardware Acceleration of Graph Neural Networks," DAC, 2020.

- [3] E. Baek, D. Kwon, and J. Kim, "A multi-neural network acceleration architecture," in 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA), 2020, pp. 940–953.

- [4] X. Chen, Y. Wang, X. Xie, X. Hu, A. Basak, L. Liang, M. Yan, L. Deng, Y. Ding, Z. Du *et al.*, "Rubik: A hierarchical architecture for efficient graph neural network training," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2021.

- [5] Y. Chen, T. Yang, J. Emer, and V. Sze, "Eyeriss v2: A flexible accelerator for emerging deep neural networks on mobile devices," *IEEE Journal* on Emerging and Selected Topics in Circuits and Systems, vol. 9, no. 2, pp. 292–308, 2019.

- [6] Y. Choi and M. Rhu, "Prema: A predictive multi-task scheduling algorithm for preemptible neural processing units," in 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA), 2020, pp. 220–233.

- [7] S. Chou, F. Kjolstad, and S. Amarasinghe, "Format abstraction for sparse tensor algebra compilers," *Proceedings of the ACM on Programming Languages*, vol. 2, no. OOPSLA, pp. 1–30, 2018.

- [8] T. T. T. A. Compiler, "http://tensor-compiler.org/," 2021.

- [9] T. A. Davis and Y. Hu, "The university of florida sparse matrix collection," 2011. [Online]. Available: https://doi.org/10.1145/2049662. 2049663

- [10] B. DeepBench, "https://github.com/baidu-research/deepbench," 2016.

- [11] C. Deng, Y. Sui, S. Liao, X. Qian, and B. Yuan, "Gospa: An energyefficient high-performance globally optimized sparse convolutional neural network accelerator," in 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA), 2021, pp. 1110–1123.

- [12] Z. Du, R. Fasthuber, T. Chen, P. Ienne, L. Li, T. Luo, X. Feng, Y. Chen, and O. Temam, "Shidiannao: Shifting vision processing closer to the sensor," in *Proceedings of the 42nd Annual International Symposium on Computer Architecture*, 2015, pp. 92–104.

- [13] M. Fey and J. E. Lenssen, "Fast graph representation learning with pytorch geometric," arXiv preprint arXiv:1903.02428, 2019.

- [14] F. Franchetti, T. M. Low, D. T. Popovici, R. M. Veras, D. G. Spampinato, J. R. Johnson, M. Püschel, J. C. Hoe, and J. M. Moura, "Spiral: Extreme performance portability," *Proceedings of the IEEE*, vol. 106, no. 11, pp. 1935–1968, 2018.

- [15] T. Geng, A. Li, T. Wang, C. Wu, Y. Li, R. Shi, A. Tumeo, S. Che, S. Reinhardt, and M. Herbordt, "Awb-gcn: A graph convolutional network accelerator with runtime workload rebalancing," *MICRO*, 2020.

- [16] S. Ghodrati, B. H. Ahn, J. Kyung Kim, S. Kinzer, B. R. Yatham, N. Alla, H. Sharma, M. Alian, E. Ebrahimi, N. S. Kim, C. Young, and H. Esmaeilzadeh, "Planaria: Dynamic architecture fission for spatial multi-tenant acceleration of deep neural networks," in 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), 2020, pp. 681–697.

- [17] A. Gondimalla, N. Chesnut, M. Thottethodi, and T. Vijaykumar, "Sparten: A sparse tensor accelerator for convolutional neural networks," in *Proceedings of the 52nd Annual IEEE/ACM International Symposium* on *Microarchitecture*, 2019, pp. 151–165.

- [18] S. Han, X. Liu, H. Mao, J. Pu, A. Pedram, M. A. Horowitz, and W. J. Dally, "Eie: efficient inference engine on compressed deep neural network," in *ISCA*, 2016.

- [19] K. Hegde, H. Asghari-Moghaddam, M. Pellauer, N. Crago, A. Jaleel, E. Solomonik, J. Emer, and C. W. Fletcher, "Extensor: An accelerator for sparse tensor algebra," in *MICRO*, 2019.

- [20] R. Hwang, T. Kim, Y. Kwon, and M. Rhu, "Centaur: A chiplet-based, hybrid sparse-dense accelerator for personalized recommendations," *ISCA*, 2020.

- [21] N. P. Jouppi, , C. Young, N. Patil, D. Patterson, G. Agrawal, R. Bajwa, S. Bates, S. Bhatia, N. Boden, A. Borchers, R. Boyle, P. I. Cantin, C. Chao, C. Clark, J. Coriell, M. Daley, M. Dau, J. Dean, B. Gelb, T. V. Ghaemmaghami, R. Gottipati, W. Gulland, R. Hagmann, C. R. Ho, D. Hogberg, J. Hu, R. Hundt, D. Hurt, J. Ibarz, A. Jaffey, A. Jaworski, A. Kaplan, H. Khaitan, D. Killebrew, A. Koch, N. Kumar, S. Lacy, J. Laudon, J. Law, D. Le, C. Leary, Z. Liu, K. Lucke,

A. Lundin, G. MacKean, A. Maggiore, M. Mahony, K. Miller, R. Nagarajan, R. Narayanaswami, R. Ni, K. Nix, T. Norrie, M. Omernick, N. Penukonda, A. Phelps, J. Ross, M. Ross, A. Salek, E. Samadiani, C. Severn, G. Sizikov, M. Snelham, J. Souter, D. Steinberg, A. Swing, M. Tan, G. Thorson, B. Tian, H. Toma, E. Tuttle, V. Vasudevan, R. Walter, W. Wang, E. Wilcox, and D. H. Yoon, "In-datacenter performance analysis of a tensor processing unit," in *Proceedings of the 44th Annual International Symposium on Computer Architecture (ISCA)*, 2017.

- [22] N. P. Jouppi, D. H. Yoon, G. Kurian, S. Li, N. Patil, J. Laudon, C. Young, and D. Patterson, "A domain-specific supercomputer for training deep neural networks," *Communications of the ACM*, vol. 63, no. 7, pp. 67– 78, 2020.

- [23] K. Kanellopoulos, N. Vijaykumar, C. Giannoula, R. Azizi, S. Koppula, N. M. Ghiasi, T. Shahroodi, J. G. Luna, and O. Mutlu, "Smash: Codesigning software compression and hardware-accelerated indexing for efficient sparse matrix operations," in *Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture*, 2019, pp. 600–614.

- [24] K. Kersting, N. M. Kriege, C. Morris, P. Mutzel, and M. Neumann, "Benchmark data sets for graph kernels, 2016," URL http://graphkernels.cs.tu-dortmund.de, vol. 795, 2016.

- [25] F. Kjolstad, S. Kamil, S. Chou, D. Lugato, and S. Amarasinghe, "The tensor algebra compiler," *Proceedings of the ACM on Programming Languages*, vol. 1, no. OOPSLA, pp. 1–29, 2017.

- [26] H. Kwon, P. Chatarasi, M. Pellauer, A. Parashar, V. Sarkar, and T. Krishna, "Understanding reuse, performance, and hardware cost of dnn dataflow: A data-centric approach," in *Proceedings of the 52nd Annual IEEE/ACM International Symposium on Microarchitecture*. ACM, 2019, pp. 754–768.

- [27] H. Kwon, L. Lai, M. Pellauer, T. Krishna, Y.-H. Chen, and V. Chandra, "Heterogeneous dataflow accelerators for multi-dnn workloads," in 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2021, pp. 71–83.

- [28] H. Kwon, A. Samajdar, and T. Krishna, "Maeri: Enabling flexible dataflow mapping over dnn accelerators via reconfigurable interconnects," ACM SIGPLAN Notices, vol. 53, no. 2, pp. 461–475, 2018.

- [29] C.-E. Lee, Y. S. Shao, J.-F. Zhang, A. Parashar, J. Emer, S. W. Keckler, and Z. Zhang, "Stitch-x: An accelerator architecture for exploiting unstructured sparsity in deep neural networks," in *SysML Conference*, vol. 120, 2018.

- [30] J. Li, Y. Ma, X. Wu, A. Li, and K. Barker, "Pasta: a parallel sparse tensor algorithm benchmark suite," *CCF Transactions on High Performance Computing*, vol. 1, no. 2, pp. 111–130, 2019.

- [31] J. Li, J. Sun, and R. Vuduc, "Hicoo: Hierarchical storage of sparse tensors," in SC18: International Conference for High Performance Computing, Networking, Storage and Analysis. IEEE, 2018, pp. 238– 252.

- [32] J. Li, A. Louri, A. Karanth, and R. Bunescu, "Gcnax: A flexible and energy-efficient accelerator for graph convolutional neural networks," in 2021 IEEE International Symposium on High Performance Computer Architecture (HPCA), 2021, pp. 775–788.

- [33] S. Li, E. Hanson, X. Qian, H. H. Li, and Y. Chen, "Escalate: Boosting the efficiency of sparse cnn accelerator with kernel decomposition," in *MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture*, ser. MICRO '21. New York, NY, USA: Association for Computing Machinery, 2021, p. 992–1004. [Online]. Available: https://doi.org/10.1145/3466752.3480043

- [34] S. Liang, C. Liu, Y. Wang, H. Li, and X. Li, "Deepburning-gl: an automated framework for generating graph neural network accelerators," in 2020 IEEE/ACM International Conference On Computer Aided Design (ICCAD). IEEE, 2020, pp. 1–9.

- [35] S. Liang, Y. Wang, C. Liu, L. He, L. Huawei, D. Xu, and X. Li, "Engn: A high-throughput and energy-efficient accelerator for large graph neural networks," *IEEE Transactions on Computers*, 2020.

- [36] L. Lu, Y. Jin, H. Bi, Z. Luo, P. Li, T. Wang, and Y. Liang, "Sanger: A co-design framework for enabling sparse attention using reconfigurable architecture," in *MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture*, ser. MICRO '21. New York, NY, USA: Association for Computing Machinery, 2021, p. 977–991. [Online]. Available: https://doi.org/10.1145/3466752.3480125

- [37] P. Mattson, C. Cheng, C. Coleman, G. Diamos, P. Micikevicius, D. Patterson, H. Tang, G.-Y. Wei, P. Bailis, V. Bittorf *et al.*, "Mlperf training benchmark," *arXiv preprint arXiv:1910.01500*, 2019.

- [38] M. Naumov, D. Mudigere, H. M. Shi, J. Huang, N. Sundaraman, J. Park, X. Wang, U. Gupta, C. Wu, A. G. Azzolini, D. Dzhulgakov, A. Mallevich, I. Cherniavskii, Y. Lu, R. Krishnamoorthi, A. Yu, V. Kondratenko, S. Pereira, X. Chen, W. Chen, V. Rao, B. Jia, L. Xiong, and M. Smelyanskiy, "Deep learning recommendation model for personalization and recommendation systems," *CoRR*, vol. abs/1906.00091, 2019. [Online]. Available: https://arxiv.org/abs/1906. 00091

- [39] S. Pal, A. Amarnath, S. Feng, M. O'Boyle, R. Dreslinski, and C. Dubach, "Sparseadapt: Runtime control for sparse linear algebra on a reconfigurable accelerator," in *MICRO-54: 54th Annual IEEE/ACM International Symposium on Microarchitecture*, ser. MICRO '21. New York, NY, USA: Association for Computing Machinery, 2021, p. 1005–1021. [Online]. Available: https://doi.org/10.1145/3466752. 3480134

- [40] S. Pal, J. Beaumont, D.-H. Park, A. Amarnath, S. Feng, C. Chakrabarti, H.-S. Kim, D. Blaauw, T. Mudge, and R. Dreslinski, "Outerspace: An outer product based sparse matrix multiplication accelerator," in *ISCA*, 2018.

- [41] A. Parashar, P. Raina, Y. S. Shao, Y. Chen, V. A. Ying, A. Mukkara, R. Venkatesan, B. Khailany, S. W. Keckler, and J. Emer, "Timeloop: A systematic approach to dnn accelerator evaluation," in 2019 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS), 2019, pp. 304–315.

- [42] A. Parashar, M. Rhu, A. Mukkara, A. Puglielli, R. Venkatesan, B. Khailany, J. Emer, S. W. Keckler, and W. J. Dally, "Scnn: An accelerator for compressed-sparse convolutional neural networks," ACM SIGARCH Computer Architecture News, vol. 45, no. 2, pp. 27–40, 2017.

- [43] E. Qin, A. Samajdar, H. Kwon, V. Nadella, S. Srinivasan, D. Das, B. Kaul, and T. Krishna, "Sigma: A sparse and irregular gemm accelerator with flexible interconnects for dnn training," in 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA), 2020, pp. 58–70.

- [44] V. J. Reddi, C. Cheng, D. Kanter, P. Mattson, G. Schmuelling, C.-J. Wu, B. Anderson, M. Breughe, M. Charlebois, W. Chou *et al.*, "Mlperf inference benchmark," in 2020 ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2020, pp. 446– 459.

- [45] M. Rhu, M. O'Connor, N. Chatterjee, J. Pool, Y. Kwon, and S. W. Keckler, "Compressing dma engine: Leveraging activation sparsity for training deep neural networks," in 2018 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2018, pp. 78–91.

- [46] K. Rocki, D. Van Essendelft, I. Sharapov, R. Schreiber, M. Morrison, V. Kibardin, A. Portnoy, J. F. Dietiker, M. Syamlal, and M. James, "Fast stencil-code computation on a wafer-scale processor," in SC20: International Conference for High Performance Computing, Networking, Storage and Analysis. IEEE, 2020, pp. 1–14.

- [47] A. Samajdar, J. M. Joseph, Y. Zhu, P. Whatmough, M. Mattina, and T. Krishna, "A systematic methodology for characterizing scalability of dnn accelerators using scale-sim," in 2020 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). IEEE, 2020, pp. 58–68.

- [48] Y. S. Shao, J. Clemons, R. Venkatesan, B. Zimmer, M. Fojtik, N. Jiang, B. Keller, A. Klinefelter, N. Pinckney, P. Raina *et al.*, "Simba: Scaling deep-learning inference with multi-chip-module-based architecture," in *Proceedings of the 52nd Annual IEEE/ACM International Symposium* on Microarchitecture, 2019, pp. 14–27.

- [49] Y. S. Shao, B. Reagen, G.-Y. Wei, and D. Brooks, "Aladdin: A pre-rtl, power-performance accelerator simulator enabling large design space exploration of customized architectures," in 2014 ACM/IEEE 41st International Symposium on Computer Architecture (ISCA). IEEE, 2014, pp. 97–108.

- [50] F. Shi, A. Y. Jin, and S.-C. Zhu, "Versagnn: a versatile accelerator for graph neural networks," arXiv preprint arXiv:2105.01280, 2021.

- [51] L. Song, J. Mao, Y. Zhuo, X. Qian, H. Li, and Y. Chen, "Hypar: Towards hybrid parallelism for deep learning accelerator array," in 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2019, pp. 56–68.

- [52] N. Srivastava, H. Jin, J. Liu, D. Albonesi, and Z. Zhang, "Matraptor: A sparse-sparse matrix multiplication accelerator based on row-wise product," in 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO). IEEE, 2020, pp. 766–780.

- [53] N. Srivastava, H. Jin, S. Smith, H. Rong, D. Albonesi, and Z. Zhang, "Tensaurus: A versatile accelerator for mixed sparse-dense tensor computations," in 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2020, pp. 689–702.

- [54] R. Venkatesan, Y. S. Shao, M. Wang, J. Clemons, S. Dai, M. Fojtik, B. Keller, A. Klinefelter, N. Pinckney, P. Raina *et al.*, "Magnet: A modular accelerator generator for neural networks," in 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD). IEEE, 2019, pp. 1–8.

- [55] H. Wang, Z. Zhang, and S. Han, "Spatten: Efficient sparse attention architecture with cascade token and head pruning," in 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, pp. 97–110.

- [56] M. Yan, L. Deng, X. Hu, L. Liang, Y. Feng, X. Ye, Z. Zhang, D. Fan, and Y. Xie, "Hygcn: A gcn accelerator with hybrid architecture," in 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA), 2020, pp. 15–29.

- [57] P. Yanardag and S. Vishwanathan, "Deep graph kernels," in *Proceedings* of the 21th ACM SIGKDD International Conference on Knowledge Discovery and Data Mining, 2015, pp. 1365–1374.

- [58] X. Yang, M. Gao, Q. Liu, J. Setter, J. Pu, A. Nayak, S. Bell, K. Cao, H. Ha, P. Raina et al., "Interstellar: Using halide's scheduling language to analyze dnn accelerators," in *Proceedings of the Twenty-Fifth International Conference on Architectural Support for Programming Languages* and Operating Systems, 2020, pp. 369–383.

- [59] G. Zhang, N. Attaluri, J. S. Emer, and D. Sanchez, "Gamma: leveraging gustavson's algorithm to accelerate sparse matrix multiplication," in *Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems*, 2021, pp. 687–701.

- [60] S. Zhang, Z. Du, L. Zhang, H. Lan, S. Liu, L. Li, Q. Guo, T. Chen, and Y. Chen, "Cambricon-x: An accelerator for sparse neural networks," in 2016 49th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO). IEEE, 2016, pp. 1–12.

- [61] Y. Zhang, H. You, Y. Fu, T. Geng, A. Li, and Y. Lin, "G-cos: Gnnaccelerator co-search towards both better accuracy and efficiency," *arXiv* preprint arXiv:2109.08983, 2021.

- [62] Z. Zhang, H. Wang, S. Han, and W. J. Dally, "Sparch: Efficient architecture for sparse matrix multiplication," in 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2020, pp. 261–274.