# Scalable Al<sub>2</sub>O<sub>3</sub>-TiO<sub>2</sub> Conductive Oxide Interfaces as Defect Reservoirs for Resistive Switching Devices

Yang Li<sup>1\*</sup>, Wei Wang<sup>1</sup>, Di Zhang<sup>2</sup>, Maria Baskin<sup>1</sup>, Aiping Chen<sup>2</sup>, Shahar Kvatinsky<sup>1</sup>, Eilam Yalon<sup>1</sup>, and Lior Kornblum<sup>1\*</sup>

<sup>1</sup>The Andrew and Erna Viterbi Faculty of Electrical and Computer Engineering, Technion -Israel Institute of Technology, Haifa, 3200003, Israel

<sup>2</sup>Center for Integrated Nanotechnologies (CINT), Los Alamos National Laboratory, Los Alamos, New Mexico 87545, USA

**KEYWORDS**: two-dimensional electron gas (2DEG), conductive oxide interfaces, valence change memory (VCM), resistive switching, resistive switching memory, atomic layer deposition (ALD).

### ABSTRACT

Resistive switching devices herald a transformative technology for memory and computation, offering considerable advantages in performance and energy efficiency. Here we employ a simple and scalable material system of conductive oxide interfaces and leverage their unique properties for a new type of resistive switching device. For the first time, we demonstrate an Al<sub>2</sub>O<sub>3</sub>-TiO<sub>2</sub> based valence-change resistive switching device, where the conductive oxide interface serves both as the back electrode and as a reservoir of defects for switching. The amorphous-polycrystalline Al<sub>2</sub>O<sub>3</sub>-TiO<sub>2</sub> conductive interface is obtained following the technological path of simplifying the fabrication of the two-dimensional electron gases (2DEGs), making them more scalable for practical mass integration. We combine physical analysis of the device chemistry and microstructure with comprehensive electrical analysis of its switching behavior and performance. We pinpoint the origin of the resistive switching to the conductive oxide interface, which serves as the bottom electrode and as a reservoir of oxygen vacancies. The latter plays a key role in valence-change resistive switching devices. The new device, based on scalable and complementary metal-oxide-semiconductor (CMOS)

technology-compatible fabrication processes, opens new design spaces towards increased tunability and simplification of the device selection challenge.

## **INTRODUCTION**

The two-dimensional electron gases (2DEGs) formed at some oxide interfaces provide a fertile ground for many physical phenomena<sup>1-6</sup> that do not exist in the corresponding bulk oxide material. These phenomena and the sheet resistance tunability of the 2DEG make it interesting for various device applications such as the channel in transistors<sup>7–9</sup> and the electrode in resistive switching memories<sup>10–14</sup>. Resistive switching memory, which has a metal-oxide-metal sandwiched structure, is a promising candidate for next-generation memories to address the vast data storage requirement in the big data era<sup>15,16</sup>. Its conductance tunability emulating the synaptic plasticity makes it applicable for brain-inspired in-memory computing<sup>17–20</sup>, which can overcome the memory bottleneck in the traditional von Neumann architecture and drastically decrease the energy consumption.

Several 2DEGs based valence change memory (VCM) devices were reported on various materials systems<sup>10,12-14</sup>, which share a common feature of using single-crystal SrTiO<sub>3</sub> substrates. The 2DEGs in these works function as the bottom electrodes of the devices. Originally, 2DEGs were fabricated exclusively by oxide epitaxy, typically by pulsed laser deposition (PLD) at high temperatures of 600-800 °C. The epitaxial oxide layer was subsequently replaced by amorphous oxides such as Al<sub>2</sub>O<sub>3</sub>, which lowered the deposition temperature to  $\sim 300$  °C by the use of atomic layer deposition (ALD)<sup>21</sup>. However, the use of SrTiO<sub>3</sub> single crystal substrates hinders the scalability and makes direct integration of such devices too complicated for the CMOS process. Recent works have reported 2DEG at the interface of amorphous Al<sub>2</sub>O<sub>3</sub> and polycrystalline TiO<sub>2</sub><sup>8,11,22-24</sup>, both deposited in a single ALD process. The mechanism of the 2DEG formation was determined to be the formation of oxygen vacancies at the TiO<sub>2</sub> surface through a reduction caused by the Al ALD precursor in the initial stages of Al<sub>2</sub>O<sub>3</sub> deposition.<sup>23</sup> These negative charges at the TiO<sub>2</sub> side of the interface result in a downward band bending at the TiO<sub>2</sub> surface, which was shown to localize the 2DEG carriers near the interface.<sup>8</sup> The use of low-temperature ALD opens the opportunity for scalable fabrication of resistive switching memory devices with CMOS-compatible processes and materials that can be integrated on the Si backend or a variety of other substrates. An electrochemical metallization (ECM) device of Cu/Ti/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> has been reported<sup>11</sup>, where the resistive switching is based on the formation and rupture of filaments consisting of Cu metal

ions from the top electrode. The 2DEG formed at the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> interface is inherently driven by oxygen vacancies, and it can thus act as an oxygen vacancy reservoir for VCM type resistive switching memory devices in addition to its more conventional role as a bottom electrode.

Here we report the first demonstration of VCM devices based on the 2DEGs formed at the  $Al_2O_3/TiO_2$  interface. The interface is fabricated at low temperatures (<300 °C) using the scalable ALD technique. The use of the low-temperature ALD and simple binary oxide materials system provides a unique feature of the 2DEG based devices being able to be integrated with the back-end-of-line CMOS process, in contrast to most previously reported 2DEG based VCM devices<sup>10,12–14</sup>. Note that for the sake of convenience, we use the term 2DEG very loosely to describe conductive oxide interfaces, in many of which the conductivity is not limited to a 2D sheet exactly at the interface, and it may extend deeper into the bottom material.

Unlike standard resistive switching devices, where the bottom electrode is a metal, a distinct feature of the 2DEG electrode is that it can be switched off, via depletion by field effect<sup>8</sup>. This feature of 2DEGs opens prospects of depleting the device's bottom electrode via the top electrode, which would result in a strongly asymmetric behavior. The asymmetry provides the potential to design *self-rectifying* resistive switching devices<sup>16,25</sup>. This is an attractive approach for inhibiting sneak-path currents, which circumvents the necessity of additional transistors or selector devices in cross-bar arrays<sup>26</sup>. As such, self-rectifying devices can dramatically simplify the large-scale integration of resistive switching memory arrays. Our demonstration of scalable 2DEG based VCM devices paves the way towards fulfilling this promise.

#### **RESULTS AND DISCUSSION**

We start by understanding the 2DEGs' features and mechanism and then follow on their role in the device.

#### Conductive Interface between Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub>

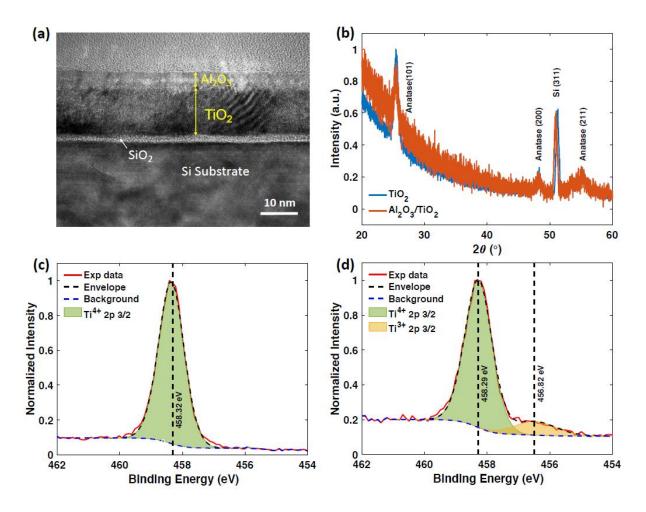

The Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> 2DEG sheet resistance is determined as  $5000 \pm 40 \text{ }\Omega$ /square using the Van der Pauw configuration. The substrate is connected in parallel to the 2DEG, but it does not significantly affect the 2DEG's role in the resistive switching given its high resistivity ( $\approx$ 70 k $\Omega$ ·cm) and vertical distance (SiO<sub>2</sub>+TiO<sub>2</sub> layers) from the resistive switching layer, Al<sub>2</sub>O<sub>3</sub>. The cross-sectional transmission electron microscopy (TEM) image of the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> heterostructure is shown in Figure 1a. The phase contrast from the TiO<sub>2</sub> layer indicates that it is primarily polycrystalline. The crystallinity of TiO<sub>2</sub> is anatase as indicated by grazing incident x-ray diffraction (GIXID, Figure 1b, ICDD card #00-21-1272), and the thickness is 14.8 ± 0.6

nm determined by X-ray reflectivity (XRR, Figure S1). No phase contrast or a clear crystal lattice is observed in the TEM image of the Al<sub>2</sub>O<sub>3</sub> layer. Our prior results<sup>27</sup> and current data (Figure 1b) indicate that the Al<sub>2</sub>O<sub>3</sub> layer is amorphous.

The mechanism behind the interface conductivity is probed by x-ray photoelectron spectroscopy (XPS) analysis of the Ti 2p region in TiO<sub>2</sub> (Figure 1c and d). A spectrum of the surface of the uncapped TiO<sub>2</sub> (also  $14.8 \pm 0.6$  nm thick, without an Al<sub>2</sub>O<sub>3</sub> overlayer) shows a nearly stoichiometric Ti<sup>4+</sup> originating in TiO<sub>2</sub> (Figure 1c). A similar sample with a 2 nm thick Al<sub>2</sub>O<sub>3</sub> capping layer shows a significant Ti<sup>3+</sup> component, constituting  $15 \pm 0.5\%$  of the Ti 2p total peak area (Figure 1d). This lower oxidation state results from a reduction of the TiO<sub>2</sub> by the Al precursor during the early stages of the ALD-Al<sub>2</sub>O<sub>3</sub> process<sup>23</sup>, leading to the generation of oxygen vacancies. These oxygen vacancies act as n-type dopants in the otherwise insulating TiO<sub>2</sub>, and they are therefore the source of the 2DEG<sup>8</sup>. This XPS fingerprint of 2DEG formation is also commonly observed in 2DEGs based on SrTiO<sub>3</sub> substrates<sup>21,28-30</sup>. Samples without the Al<sub>2</sub>O<sub>3</sub> layer, showing no Ti<sup>3+</sup> features (Figure 1c), are electrically insulating (R<sub>8</sub>>10<sup>9</sup> Ω/square, out of test equipment limit), showing only negligible contribution of conductivity from the Si substrate below (or no measurable conductivity when deposited on a glass substrate for comparison).

Therefore, the process described here for Al<sub>2</sub>O<sub>3</sub> deposition results in the formation of 2DEGs at the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> interface, as observed by the interface conductivity and the significant Ti<sup>3+</sup> component (Figure 1d).

Figure 1. The uncapped TiO<sub>2</sub> and the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> 2DEG heterostructure material characterization. (a) TEM crosssectional view of the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> film stack. (b) Grazing incident X-ray diffraction (GIXRD) of the uncapped TiO<sub>2</sub> film and the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> 2DEG film stack on SiO<sub>2</sub>/Si substrates. The peaks are at  $2\theta$ =25.5°, 48.2°, 55.0° correspond to anatase (101), (200), and (211), respectively. The peak at  $2\theta$ =51.0° corresponds to Si (311). X-ray photoelectron spectroscopy (XPS) spectra of Ti 2p of (c) the uncapped TiO<sub>2</sub> film and (d) the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> 2DEG heterostructure. The Al<sub>2</sub>O<sub>3</sub> layer is 2nm thick.

Here the Al<sub>2</sub>O<sub>3</sub> (2nm) acts as a protection layer for the 2DEG formed in the surface of TiO<sub>2</sub><sup>29</sup>. It was intentionally made thin to allow the XPS to probe the underlying TiO<sub>2</sub>, whereas, in the device to follow, thicker Al<sub>2</sub>O<sub>3</sub> layers (5 nm) will be employed. The reduction process may well extend the range of the oxygen vacancies into the TiO<sub>2</sub> layer, making the conductivity not limited strictly to the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> interface. Therefore, the use of the term 2DEG is not rigorously justified, rather it is used here loosely for convenience <sup>31</sup>.

#### **2DEG Based VCM Devices**

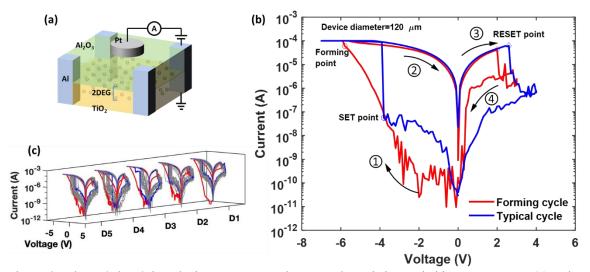

Having set the ground with the analysis of the 2DEGs, we then fabricate VCM devices from Pt (50 nm)/Al<sub>2</sub>O<sub>3</sub> (5 nm)/TiO<sub>2</sub> (14.8 nm) structures. The Pt layer acts as the top electrode, and the Al<sub>2</sub>O<sub>3</sub> layer acts as the resistive switching layer. The conductive 2DEG at the Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> interface acts as the bottom electrode and as the oxygen vacancies reservoir for the VCM device here. The 2DEG electrode is contacted from contacts at the corners of the sample (Figure 2a).

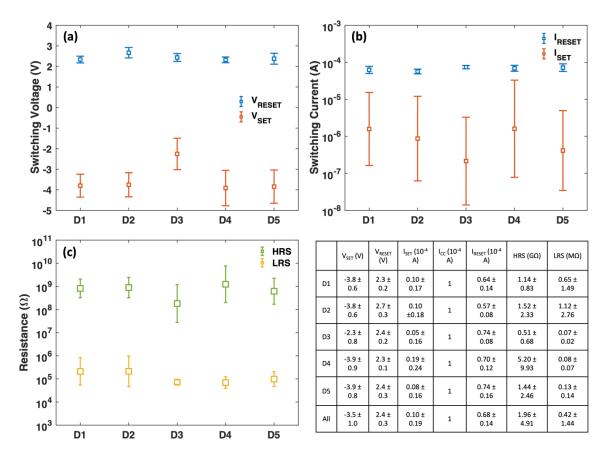

When operating the device, we apply the voltage on the Pt top electrode and ground the 2DEG bottom electrode (Figure 2a). The *I-V* curves of the forming cycle and a typical switching cycle are shown in Figure 2b. Five different devices are tested under DC mode using voltage sweeps, and each device is switched for 20 cycles after the forming process (Figure 2c), exhibiting comparable behavior and low device-to-device variability. The detailed switching parameters are provided in Figure S2.

Figure 2. The Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> device structure and DC mode resistive switching *I-V* curves. (a) Schematic illustration of the device structure with the 2DEG acting as the bottom electrode. The Pt acts as the top electrode and the Al<sub>2</sub>O<sub>3</sub> acts as the resistive switching layer. The voltage is always applied to the Pt top electrode, and the 2DEG is always grounded during the tests. (b) *I-V* curves of a forming cycle and a typical switching cycle in DC mode. The forming, SET, and RESET points are noted on the curves. The annotations of  $\oplus \odot \odot \oplus$  show the sequence of the voltage sweep and the arrows show the voltage sweep direction. (c) *I-V* curves of five devices. The red lines are the forming cycles. The blue lines represent the typical resistive switching cycles. The grey lines correspond to all *I-V* cycles after the forming cycles.

In addition to the 2DEG's role as the back electrode, it further functions as the source of oxygen vacancies responsible for the resistive switching behavior of the Al<sub>2</sub>O<sub>3</sub> layer. In a previous work, we deposited Al<sub>2</sub>O<sub>3</sub> layers with an identical recipe on conductive Nb:SrTiO<sub>3</sub> layers, where no interface vacancies were formed. These structures exhibit robust insulating properties, and no hysteresis behavior.<sup>32</sup> The key difference from the current case is the reduction of the TiO<sub>2</sub> surface, allowing us to pinpoint the interface as the source of vacancies

for resistive switching, which are injected (forming) into the Al<sub>2</sub>O<sub>3</sub> layer.<sup>13</sup> This differs from typical memristors where the resistive switching layer is intentionally rich with defects, whereas our approach allows the use of an initially low-defect and insulating Al<sub>2</sub>O<sub>3</sub>, which heralds a memory window of ~4 orders of magnitude at  $\pm 0.2$  V.

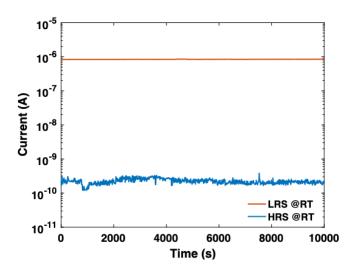

The retention of high resistive state (HRS) and low resistive state (LRS) using compliance current ( $I_{CC}$ ) of 10<sup>-4</sup> A (using the current limit function of the testing instrument) are tested at room temperature using 0.1 V read voltage and both resistance states remain stable for 10<sup>4</sup> s without degradation (Figure S3), which is comparable to other 2DEG based VCM devices on SrTiO<sub>3</sub> substrates<sup>10,12,14</sup>.

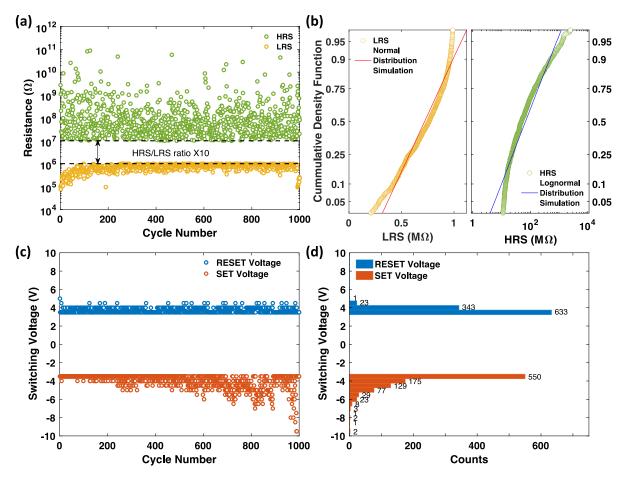

In addition to DC switching analysis, the endurance of the devices is tested under pulsed switching using 100 µs width voltage pulses (Figure 3). The resistance window is set to be 10, with the LRS lower than  $10^6 \Omega$  and the HRS higher than  $10^7 \Omega$  (Figure 3a). An operate-andverify programming scheme $^{33-36}$  is used here, which means more than a single pulse may be used in the SET or RESET operations. The voltage height in both SET and RESET will increase until the resistance is tuned to the destination resistance value. The details of the operate-andverify programming scheme are shown in Figure S4-S6. The reason for using the operate-andverify programming scheme is that the device might not reach the desired resistance range after a single pulse operation. To ensure the device's resistance is indeed programmed to the desired value, a verification step is necessary. This operate-and-verify programming scheme requires higher energy consumption compared to single-pulse programming scheme, but it is more reliable and it guarantees the resistance modulation success for each cycle. All the HRS and LRS in both DC mode and pulse mode are read at a voltage of 0.1 V. Due to the intrinsic stochastic nature of the devices' switching process which includes the formation and rupture of the conductive filament, the devices exhibit cycle-to-cycle variation (Figure 3a). The LRS values vary from 77 k $\Omega$  to 1 M $\Omega$  and follow a normal distribution ( $\mu$ =7.2×10<sup>5</sup>  $\Omega$ ,  $\sigma$ =2.1×10<sup>5</sup> Ω). The HRS vary from 10 MΩ to 87 GΩ and follow a lognormal distribution (Figure 3b). The resistances of the device show no observable degradation after  $10^3$  cycles of operation.

About 98% of the RESET cycles require no more than 2 pulses to switch the device from HRS to LRS, and about 85% of the SET cycles require no more than 3 pulses to switching the device from LRS to HRS (Figure 3c and 3d). The SET voltage and the number of pulses required to switch the device from HRS to LRS increase as the cycle number increases (Figure 3c), indicating that further engineering will be necessary to mature these devices for practical applications.

Figure 3. Endurance analysis of Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> devices under pulse mode using 100 µs voltage pulses. (a) The resistances of 10<sup>3</sup> cycles under pulse operation mode with a ten times resistance window defined in the program. (b) The cumulative density function of the resistances. The red line is the simulated normal distribution of the LRS ~ normal ( $\mu_1$ =7.2×10<sup>5</sup>,  $\sigma_1$ =2.1×10<sup>5</sup>). The blue line is the simulated lognormal distribution of the HRS ~ lognormal ( $\mu_2$ =16.55,  $\sigma_2$ =2.11). (c) The last SET and RESET voltage pulse height in each cycle of 10<sup>3</sup> resistive switching cycles. (d) The histogram of the switching voltages with the count numbers labeled right to the bars.

#### **Switching Mechanism**

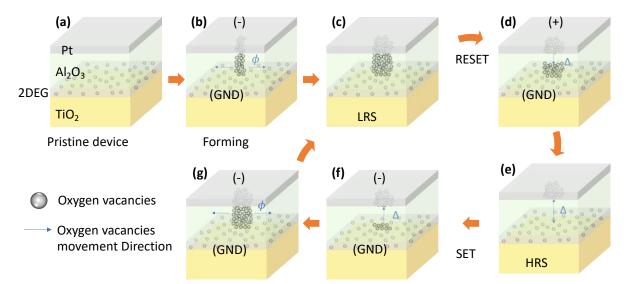

The resistive switching behavior of the Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> VCM devices can be explained by the formation and partial rupture of the conductive filaments (CFs) consisting of oxygen vacancies<sup>20,37–40</sup> inside the Al<sub>2</sub>O<sub>3</sub> layer, as illustrated in Figure 4.

The pristine device starts with no CFs inside the Al<sub>2</sub>O<sub>3</sub> layer (Figure 4a). During the forming process, an external negative voltage is applied to the Pt electrode and the positively-charged oxygen vacancies migrate towards the top electrode which leads to the formation of CF consisting of oxygen vacancies (Figure 4b $\rightarrow$ Figure 4c). The device switches from initial high resistance state to low resistance state.

In the RESET process, a positive voltage is applied to the Pt top electrode and the bottom electrode is grounded. The oxygen vacancies migrate towards the bottom electrode and the gap

length  $\Delta$  between the remnant CF grows, which leads to the rupture of CF (Figure 4c  $\rightarrow$  Figure 4d  $\rightarrow$  Figure 4e). The device resistance switches from low resistance state to high resistance state.

In the SET process, a negative voltage is applied to the top electrode and the bottom electrode is grounded. At first, the length of the gap  $\Delta$  decreases until the filament forms a continuous filament connecting the top and the bottom electrode (Figure 4e  $\rightarrow$  Figure 4f). Only after the continuous CF forms, the diameter of the CF begins to increase until the SET process finishes (Figure 4f  $\rightarrow$  Figure 4g). The device resistance switches from high resistance state to low resistance state.<sup>41</sup>

Figure 4. Schematic illustration of the filamentary resistive switching process of  $Pt/Al_2O_3/TiO_2$  VCM devices. (a) The initial state of a pristine device. (b) The forming process: formation of a continuous CF consisting of oxygen vacancies connecting the top and the bottom electrode, and the diameter of the CF increases until the forming voltage sweep finishes. (c) The low resistance state (LRS) of the device. (d) The RESET process: partial rupture of the conductive filament with the external positive voltage applied to the Pt top electrode and the oxygen vacancies drifting towards the 2DEG electrode, and the gap  $\Delta$  between the remnant CFs increases. (e) The high resistance state (HRS) of the device. (f) and (g) SET process: the gap  $\Delta$  between the remnant CFs decreases first, and the CF diameter  $\phi$  increases only after a continuous CF is formed.

One issue of using 2DEG as the bottom electrode is that the resistance of the 2DEG needs to be further decreased for large crossbar array device integrations. As for the advantages, we highlight the prospects of using 2DEGs as a bottom electrode that can be depleted, thus opening simple routes towards self-rectifying devices. Realizing the potential for self-rectification here requires controlling of the depletion behavior of the 2DEG, which can be obtained by tuning of the gate effective work function<sup>42</sup>, engineering (or adding) the insulator layer<sup>8</sup>, and with designing the device structure and contacts with an emphasis on the series resistance.

In addition, if the inert top electrode is replaced by an oxide conductor, e.g., indium tin oxide  $(ITO)^{22}$ , it can enable full oxide implementation of the resistive switching devices. This will pave the way toward transparent memory applications. This is another potential benefit of using binary oxide-based 2DEG as the bottom electrode and the oxygen reservoir in resistive switching devices.

# CONCLUSIONS

VCM devices based on 2DEG on Si are demonstrated for the first time. The 2DEG acts as both the bottom electrode and the oxygen reservoir. The Pt/Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> VCM devices show binary resistive switching in DC and pulse modes. An endurance of 10<sup>3</sup> cycles and retention of 10<sup>4</sup> s are obtained. The devices switch between HRS and LRS due to the formation and partial rupture of conductive filaments consisting of oxygen vacancies inside the Al<sub>2</sub>O<sub>3</sub> layer. The use of the Si substrate and simple binary oxide materials of Al<sub>2</sub>O<sub>3</sub> and TiO<sub>2</sub> demonstrate the feasibility of integrating 2DEG into Si-based and CMOS-compatible devices. The ability to deplete the 2DEGs provides a route towards self-rectifying devices, and the possibility of replacing the top metal electrode with a transparent oxide electrode also allows the device to be extended to wearable and flexible applications.

#### **EXPERIMENTAL SECTION**

The substrates used are (100) n-type unintentionally-doped Si (MTI Corp., resistivity  $\approx$  70k  $\Omega \cdot cm$ ) with ~2 nm native SiO<sub>2</sub>. The TiO<sub>2</sub> films are deposited on the substrates by atomic layer deposition (ALD, Ultratech/Cambridge Nanotech Fiji G2) at 250 °C using tetrakis(dimethyl amido)titanium (TDMAT) and Ar:O<sub>2</sub> (4:1) plasma as the Ti and oxygen precursors, respectively. The TDMAT is heated to 75 °C in the bubbler and introduced to the ALD reactor by 30 sccm of Ar carrier gas. The TiO<sub>2</sub> deposition sequence consists of TDMAT injection (0.025 s)/purge (10 s)/Ar:O<sub>2</sub> plasma (5 s)/purge (5 s). The samples are kept inside the ALD chamber under vacuum (~2×10<sup>-2</sup> Torr) after the TiO<sub>2</sub> deposition. The temperature is increased from 250 °C to 300 °C and stabilized at 300 °C, taking 15 minutes altogether. This step was found to be important for reducing the sheet resistance. Subsequently, 10 trimethylaluminum (TMA) reducing pulses (0.1 s pulse duration) are injected into the chamber prior to Al<sub>2</sub>O<sub>3</sub> deposition. Finally, 2 nm (for XPS characterization) or 5 nm (for device testing) Al<sub>2</sub>O<sub>3</sub> thin films are deposited on the TiO<sub>2</sub> at 300 °C. TMA and H<sub>2</sub>O are used as the Al and the oxygen precursors, respectively. The Al<sub>2</sub>O<sub>3</sub> deposition sequence<sup>32</sup> consists of TMA injection (0.1

s)/purge (10 s)/H<sub>2</sub>O (0.3 s)/purge (5 s). Pt top electrodes (50 nm thick) are deposited on top of the Al<sub>2</sub>O<sub>3</sub> layer through a shadow mask with a diameter of 120  $\mu$ m using e-beam deposition. Contacts to the 2DEG are done by scratching the samples' corners from the top of the samples' surface following depositing a layer of 50 nm thick Al by e-beam deposition (Evatec BAK-501A) at room temperature on the surface of the samples' edges.

Cross-sectional specimens were prepared through a conventional TEM sample preparation routine. Starting with cutting and gluing, the TEM specimens are then ground, planar parallel polished, and further thinned in the center by dimpling. Ar ion milling is used to obtain a perforation and electron transparent thin area with a Gatan Precision Ion Polishing System (PIPS II 695, Gatan Inc.). The microstructure is characterized by FEI Tecnai F30 analytical TEM operating at 300 kV.

The films' crystallinity is analyzed by grazing incident X-ray diffraction (GIXRD), and the film's thickness is analyzed by X-ray reflectivity (XRR) using Rigaku SmartLab diffractometer. The GIXRD incident angle is 0.5°. The samples are mounted on zero-diffraction discs (MTI Corp.) during the test.

X-ray Photoelectron Spectroscopy (XPS) measurements are performed in UHV  $(2.5 \times 10^{-10}$  Torr base pressure) using the 5600 Multi-Technique System (PHI, USA). The samples are irradiated with an Al K $\alpha$  monochromated source (1486.6 eV), and the outcome electrons are analyzed by a Spherical Capacitor Analyzer using a slit aperture of 0.8 mm. All spectra are shifted to align the adventitious C1s peak at 284.8 eV.

The sheet resistance of the 2DEG is measured using the Van der Pauw configuration at room temperature. The sheet resistance and DC device analysis is done using a light-sealed probe station with a Keithley 2450 source measurement unit. For resistive switching measurements the current compliance is applied through the current limit function of the instrument. AC pulse testes are measured using an Agilent B1500A.

## **CORRESPONDING AUTHORS**

\*E-mail: yangli@campus.technion.ac.il

\*E-mail: liork@ee.technion.ac.il

#### ACKNOWLEDGEMENTS

The authors are grateful for the support of the Israeli Science Foundation (ISF Grant No. 375/17). Partial support in the fabrication and characterization of the samples was provided by the Technion's Micro-Nano Fabrication & Printing Unit (MNF&PU) and the Russell Berrie Nanotechnology Institute (RBNI). The authors would like to thank the assistance and support from Dr. Kamira Weinfeld and Dr. Pini Shekhter for XPS characterization, Mrs. Valentina Korchnoy for ALD, Mr. Arkadi Gavrilov for e-beam evaporation, and Dr. Maria Koifman Khristosov for XRD characterization. Y. Li acknowledges partial support from a Technion Fellowship. W. Wang was supported in part at the Technion by the Aly Kaufman Fellowship.

The work at Los Alamos National Laboratory was supported by the NNSA's Laboratory Directed Research and Development Program, and was performed, in part, at the CINT, an Office of Science User Facility operated for the U.S. Department of Energy Office of Science. Los Alamos National Laboratory, an affirmative action-equal opportunity employer, is managed by Triad National Security, LLC for the U.S. Department of Energy's NNSA, under contract 89233218CNA000001.

#### REFERENCES

- (1) Ohtomo, A.; Hwang, H. Y. A High-Mobility Electron Gas at the LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Heterointerface. *Nature* **2004**, *427* (6973), 423–426. https://doi.org/10.1038/nature02308.

- Reyren, N.; Thiel, S.; Caviglia, A. D.; Fitting Kourkoutis, L.; Hammerl, G.; Richter, C.; Schneider, C. W.; Kopp, T.; Rüetschi, A. S.; Jaccard, D.; Gabay, M.; Muller, D. A.; Triscone, J. M.; Mannhart, J. Superconducting Interfaces Between Insulating Oxides. *Science (80-. ).* 2007, *317* (5842), 1196–1199. https://doi.org/10.1126/science.1146006.

- (3) Pai, Y. Y.; Tylan-Tyler, A.; Irvin, P.; Levy, J. Physics of SrTiO<sub>3</sub>-Based Heterostructures and Nanostructures: A Review. *Reports Prog. Phys.* 2018, 81 (3), 036503. https://doi.org/10.1088/1361-6633/aa892d.

- (4) Liu, Z.; Annadi, A.; Ariando. Two-Dimensional Electron Gas at LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Interfaces. In *Functional Materials and Electronics*; Yi, J., Li, S., Eds.; Apple Academic Press: Boca Raton, 2018; pp 35–95. https://doi.org/10.1201/9781315167367.

- (5) Trier, F.; Christensen, D. V.; Pryds, N. Electron Mobility in Oxide Heterostructures. J. Phys. D. Appl. Phys. 2018, 51 (29), 293002. https://doi.org/10.1088/1361-6463/aac9aa.

- Pryds, N.; Esposito, V. When Two Become One: An Insight into 2D Conductive Oxide Interfaces. J. Electroceramics 2017, 38 (1), 1–23. https://doi.org/10.1007/s10832-016-0051-0.

- Kornblum, L. Conductive Oxide Interfaces for Field Effect Devices. Adv. Mater. Interfaces 2019, 6 (15), 1900480. https://doi.org/10.1002/admi.201900480.

- (8) Seok, T. J.; Liu, Y.; Jung, H. J.; Kim, S. Bin; Kim, D. H.; Kim, S. M.; Jang, J. H.; Cho, D. Y.; Lee, S. W.; Park, T. J. Field-Effect Device Using Quasi-Two-Dimensional Electron Gas in Mass-Producible Atomic-Layer-Deposited Al2O3/TiO2 Ultrathin (<10 Nm) Film</p>

Heterostructures. *ACS Nano* **2018**, *12* (10), 10403–10409. https://doi.org/10.1021/acsnano.8b05891.

- (9) Moon, T.; Lee, H. J.; Hyun, S. D.; Kim, B. S.; Kim, H. H.; Hwang, C. S. Origin of the Threshold Voltage Shift in a Transistor with a 2D Electron Gas Channel at the Al<sub>2</sub>O<sub>3</sub>/SrTiO<sub>3</sub> Interface. *Adv. Electron. Mater.* **2020**, *6* (6), 1–8. https://doi.org/10.1002/aelm.201901286.

- Joung, J. G.; Kim, S. I.; Moon, S. Y.; Kim, D. H.; Gwon, H. J.; Hong, S. H.; Chang, H. J.; Hwang, J. H.; Kwon, B. J.; Kim, S. K.; Choi, J. W.; Yoon, S. J.; Kang, C. Y.; Yoo, K. S.; Kim, J. S.; Baek, S. H. Nonvolatile Resistance Switching on Two-Dimensional Electron Gas. *ACS Appl. Mater. Interfaces* 2014, 6 (20), 17785–17791. https://doi.org/10.1021/am504354c.

- (11) Kim, S. M.; Kim, H. J.; Jung, H. J.; Kim, S. H.; Park, J. Y.; Seok, T. J.; Park, T. J.; Lee, S. W. Highly Uniform Resistive Switching Performances Using Two-Dimensional Electron Gas at a Thin-Film Heterostructure for Conductive Bridge Random Access Memory. *ACS Appl. Mater. Interfaces* 2019, *11* (33), 30028–30036. https://doi.org/10.1021/acsami.9b08941.

- Wu, S.; Luo, X.; Turner, S.; Peng, H.; Lin, W.; Ding, J.; David, A.; Wang, B.; Van Tendeloo, G.; Wang, J.; Wu, T. Nonvolatile Resistive Switching in Pt/LaAlO<sub>3</sub>/SrTiO<sub>3</sub> Heterostructures. *Phys. Rev. X* 2013, *3* (4), 041027. https://doi.org/10.1103/PhysRevX.3.041027.

- (13) Miron, D.; Cohen-Azarzar, D.; Hoffer, B.; Baskin, M.; Kvatinsky, S.; Yalon, E.; Kornblum, L. Oxide 2D Electron Gases as a Reservoir of Defects for Resistive Switching. *Appl. Phys. Lett.* 2020, *116* (22), 223503. https://doi.org/10.1063/5.0003590.

- (14) Wu, S.; Ren, L.; Qing, J.; Yu, F.; Yang, K.; Yang, M.; Wang, Y.; Meng, M.; Zhou, W.; Zhou, X.; Li, S. Bipolar Resistance Switching in Transparent ITO/LaAlO<sub>3</sub>/ SrTiO<sub>3</sub> Memristors. *ACS Appl. Mater. Interfaces* 2014, 6 (11), 8575–8579. https://doi.org/10.1021/am501387w.

- (15) Lee, S. R.; Kim, Y. B.; Chang, M.; Kim, K. K. M.; Lee, C. B.; Hur, J. H.; Park, G. S.; Lee, D.; Lee, M. J.; Kim, C. J.; Chung, U. I.; Yoo, I. K.; Kim, K. K. M. Multi-Level Switching of Triple-Layered TaOx RRAM with Excellent Reliability for Storage Class Memory. In 2012 Symposium on VLSI Technology; Honolulu, HI, 2012; Vol. 52, pp 71–72. https://doi.org/10.1109/VLSIT.2012.6242466.

- (16) Hsu, C.-W.; Wang, I.-T.; Lo, C.-L.; Chiang, M.; Jang, W.; Lin, C.-H.; Hou, T.-H. Self-Rectifying Bipolar TaO<sub>x</sub>/TiO<sub>2</sub> RRAM with Superior Endurance over 10<sup>12</sup> Cycles for 3D High-Density Storage-Class Memory. In 2013 Symposium on VLSI Circuits (VLSI); IEEE: Kyoto, Japan, 2013; pp T166–T167.

- (17) Wang, W.; Song, W.; Yao, P.; Li, Y.; Van Nostrand, J.; Qiu, Q.; Ielmini, D.; Yang, J. J. Integration and Co-Design of Memristive Devices and Algorithms for Artificial Intelligence. *iScience*. Elsevier Inc. 2020, p 101809. https://doi.org/10.1016/j.isci.2020.101809.

- (18) Ielmini, D.; Ambrogio, S. Emerging Neuromorphic Devices. *Nanotechnology* 2020, 31 (9). https://doi.org/10.1088/1361-6528/ab554b.

- (19) Zidan, M. A.; Strachan, J. P.; Lu, W. D. The Future of Electronics Based on Memristive Systems. *Nat. Electron.* **2018**, *1* (1), 22–29. https://doi.org/10.1038/s41928-017-0006-8.

- (20) Dittmann, R.; Strachan, J. P. Redox-Based Memristive Devices for New Computing Paradigm. *APL Mater.* **2019**, 7 (11). https://doi.org/10.1063/1.5129101.

- (21) Lee, S. W.; Liu, Y.; Heo, J.; Gordon, R. G. Creation and Control of Two-Dimensional Electron Gas Using Al-Based Amorphous Oxides/SrTiO<sub>3</sub> Heterostructures Grown by Atomic Layer Deposition. *Nano Lett.* **2012**, *12* (9), 4775–4783. https://doi.org/10.1021/nl302214x.

- (22) Lee, H. J.; Moon, T.; An, C. H.; Hwang, C. S. 2D Electron Gas at the Interface of Atomic-Layer-Deposited Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> on SrTiO<sub>3</sub> Single Crystal Substrate. *Adv. Electron. Mater.* 2019, 5 (1), 1800527. https://doi.org/10.1002/aelm.201800527.

- (23) Seok, T. J.; Liu, Y.; Choi, J. H.; Kim, H. J.; Kim, D. H.; Kim, S. M.; Jang, J. H.; Cho, D.-Y.; Lee, S. W.; Park, T. J. In Situ Observation of Two-Dimensional Electron Gas Creation at the Interface of an Atomic Layer-Deposited Al<sub>2</sub>O<sub>3</sub>/TiO<sub>2</sub> Thin-Film Heterostructure. *Chem. Mater.* **2020**, *32* (18), 7662–7669. https://doi.org/10.1021/acs.chemmater.0c01572.

- (24) Kim, S. M.; Kim, H. J.; Jung, H. J.; Park, J. Y.; Seok, T. J.; Choa, Y. H.; Park, T. J.; Lee, S. W. High-Performance, Transparent Thin Film Hydrogen Gas Sensor Using 2D Electron Gas at Interface of Oxide Thin Film Heterostructure Grown by Atomic Layer Deposition. *Adv. Funct. Mater.* 2019, *29* (7), 1807760. https://doi.org/10.1002/adfm.201807760.

- (25) Zhou, J.; Cai, F.; Wang, Q.; Chen, B.; Gaba, S.; Lu, W. D. Very Low-Programming-Current RRAM with Self-Rectifying Characteristics. *IEEE Electron Device Lett.* 2016, 37 (4), 404– 407. https://doi.org/10.1109/LED.2016.2530942.

- (26) Li, C.; Han, L.; Jiang, H.; Jang, M. H.; Lin, P.; Wu, Q.; Barnell, M.; Yang, J. J.; Xin, H. L.; Xia, Q. Three-Dimensional Crossbar Arrays of Self-Rectifying Si/SiO<sub>2</sub>/Si Memristors. *Nat. Commun.* 2017, *8*, 15666. https://doi.org/10.1038/ncomms15666.

- (27) Cohen-Azarzar, D.; Baskin, M.; Kornblum, L. Band Offsets at Amorphous-Crystalline Al2O3-SrTiO3 Oxide Interfaces. J. Appl. Phys. 2018, 123, 245307. https://doi.org/10.1063/1.5030119.

- (28) Chen, Y.; Pryds, N.; Kleibeuker, J. E.; Koster, G.; Sun, J.; Stamate, E.; Shen, B.; Rijnders, G.; Linderoth, S. Metallic and Insulating Interfaces of Amorphous SrTiO<sub>3</sub>-Based Oxide Heterostructures. *Nano Lett.* **2011**, *11* (9), 3774–3778. https://doi.org/10.1021/nl201821j.

- (29) Drera, G.; Salvinelli, G.; Brinkman, A.; Huijben, M.; Koster, G.; Hilgenkamp, H.; Rijnders, G.; Visentin, D.; Sangaletti, L. Band Offsets and Density of Ti3+ States Probed by X-Ray Photoemission on LaAlO<sbu>3</sub>/SrTiO<sub>3</sub> Heterointerfaces and Their LaAlO<sub>3</sub> and SrTiO<sub>3</sub> Bulk Precursors. *Phys. Rev. B Condens. Matter Mater. Phys.* **2013**, *87* (7), 075435. https://doi.org/10.1103/PhysRevB.87.075435.

- (30) Li, M. H.; Li, H.; Gan, Y. L.; Xu, H.; Xiong, C. M.; Hu, F. X.; Sun, J. R.; Schmitt, T.; Strocov, V. N.; Chen, Y. Z.; Shen, B. G. Decoupling the Conduction from Redox Reaction and Electronic Reconstruction at Polar Oxide Interfaces. *Phys. Rev. Mater.* 2022, 6 (3), 035004. https://doi.org/10.1103/physrevmaterials.6.035004.

- (31) Li, Y.; Kvatinsky, S.; Kornblum, L. Harnessing Conductive Oxide Interfaces for Resistive Random-Access Memories. *Front. Phys.* **2021**, *9*, 642. https://doi.org/10.3389/fphy.2021.772238.

- (32) Miron, D.; Krylov, I.; Baskin, M.; Yalon, E.; Kornblum, L. Understanding Leakage Currents through Al<sub>2</sub>O<sub>3</sub> on SrTiO<sub>3</sub>. J. Appl. Phys. 2019, 126 (18), 185301. https://doi.org/10.1063/1.5119703.

- (33) Shim, W.; Seo, J. S.; Yu, S. Two-Step Write-Verify Scheme and Impact of the Read Noise in Multilevel RRAM-Based Inference Engine. *Semicond. Sci. Technol.* 2020, 35 (11), 115026. https://doi.org/10.1088/1361-6641/abb842.

- (34) Wang, S.; Wu, H.; Gao, B.; Deng, N.; Wu, D.; Qian, H. Optimization of Writing Scheme on 1T1R RRAM to Achieve Both High Speed and Good Uniformity. *Eur. Solid-State Device Res. Conf.* 2017, 1 (c), 14–17. https://doi.org/10.1109/ESSDERC.2017.8066580.

- (35) Puglisi, F. M.; Wenger, C.; Pavan, P. A Novel Program-Verify Algorithm for Multi-Bit Operation in HfO<sub>2</sub> RRAM. *IEEE Electron Device Lett.* **2015**, *36* (10), 1030–1032.

- (36) Lanza, M.; Wong, H. S. P.; Pop, E.; Ielmini, D.; Strukov, D.; Regan, B. C.; Larcher, L.; Villena, M. A.; Yang, J. J.; Goux, L.; Belmonte, A.; Yang, Y.; Puglisi, F. M.; Kang, J.; Magyari-Köpe, B.; Yalon, E.; Kenyon, A.; Buckwell, M.; Mehonic, A.; Shluger, A.; Li, H.; Hou, T. H.; Hudec, B.; Akinwande, D.; Ge, R.; Ambrogio, S.; Roldan, J. B.; Miranda, E.; Suñe, J.; Pey, K. L.; Wu, X.; Raghavan, N.; Wu, E.; Lu, W. D.; Navarro, G.; Zhang, W.; Wu, H.; Li, R.; Holleitner, A.; Wurstbauer, U.; Lemme, M. C.; Liu, M.; Long, S.; Liu, Q.; Lv, H.; Padovani, A.; Pavan, P.; Valov, I.; Jing, X.; Han, T.; Zhu, K.; Chen, S.; Hui, F.; Shi, Y. Recommended Methods to Study Resistive Switching Devices. *Adv. Electron. Mater.* 2019, 5 (1), 1–28. https://doi.org/10.1002/aelm.201800143.

- (37) Park, G. S.; Kim, Y. B.; Park, S. Y.; Li, X. S.; Heo, S.; Lee, M. J.; Chang, M.; Kwon, J. H.; Kim, M.; Chung, U. I.; Dittmann, R.; Waser, R.; Kim, K. In Situ Observation of Filamentary Conducting Channels in an Asymmetric Ta 2 O 5-x/TaO 2-x Bilayer Structure. *Nat. Commun.* 2013, *4*, 1–9. https://doi.org/10.1038/ncomms3382.

- (38) Mohammad, B.; Jaoude, M. A.; Kumar, V.; Al Homouz, D. M.; Nahla, H. A.; Al-Qutayri, M.; Christoforou, N. State of the Art of Metal Oxide Memristor Devices. *Nanotechnol. Rev.* 2016, 5 (3), 311–329. https://doi.org/10.1515/ntrev-2015-0029.

- (39) Cooper, D.; Baeumer, C.; Bernier, N.; Marchewka, A.; La Torre, C.; Dunin-Borkowski, R. E.; Menzel, S.; Waser, R.; Dittmann, R. Anomalous Resistance Hysteresis in Oxide ReRAM: Oxygen Evolution and Reincorporation Revealed by In Situ TEM. *Adv. Mater.* 2017, *29* (23), 1–8. https://doi.org/10.1002/adma.201700212.

- (40) Celano, U.; Op De Beeck, J.; Clima, S.; Luebben, M.; Koenraad, P. M.; Goux, L.; Valov, I.; Vandervorst, W. Direct Probing of the Dielectric Scavenging-Layer Interface in Oxide Filamentary-Based Valence Change Memory. ACS Appl. Mater. Interfaces 2017, 9 (12), 10820–10824. https://doi.org/10.1021/acsami.6b16268.

- (41) Ambrogio, S.; Balatti, S.; Gilmer, D. C.; Ielmini, D. Analytical Modeling of Oxide-Based Bipolar Resistive Memories and Complementary Resistive Switches. *IEEE Trans. Electron Devices* 2014, 61 (7), 2378–2386. https://doi.org/10.1109/TED.2014.2325531.

- (42) Robertson, J. Band Offsets and Work Function Control in Field Effect Transistors. J. Vac. Sci. Technol. B Microelectron. Nanom. Struct. 2009, 27 (1), 277. https://doi.org/10.1116/1.3072517.

# **Supplementary Information for:**

# Scalable Al<sub>2</sub>O<sub>3</sub>-TiO<sub>2</sub> Conductive Oxide Interfaces as Defect Reservoirs for Resistive Switching Devices

Yang Li<sup>1\*</sup>, Wei Wang<sup>1</sup>, Di Zhang<sup>2</sup>, Maria Baskin<sup>1</sup>, Aiping Chen<sup>2</sup>, Shahar Kvatinsky<sup>1</sup>, Eilam Yalon<sup>1</sup>, and Lior Kornblum<sup>1\*</sup>

<sup>1</sup>The Andrew and Erna Viterbi Faculty of Electrical and Computer Engineering, Technion -Israel Institute of Technology, Haifa, 3200003, Israel

<sup>2</sup>Center for Integrated Nanotechnologies (CINT), Los Alamos National Laboratory, Los Alamos, New Mexico 87545, USA

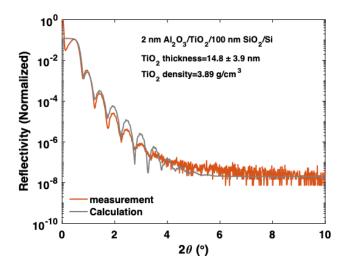

The TiO<sub>2</sub> film thicknesses are determined by using x-ray reflectometry (XRR, Figure S1).

Figure S1. X-ray reflectometry (XRR) of the 2 nm  $Al_2O_3/TiO_2/native SiO_2/Si$  film stacks. The thickness of the TiO<sub>2</sub> was calculated to be  $14.8 \pm 0.6$  nm using the TiO<sub>2</sub> film density of 3.89 g/cm<sup>3</sup>.

The XPS spectra are fitted using the CasaXPS software with a Shirley background and a Lorentzian-Gaussian line shape with a ratio of 30%. During the XPS data analysis, the Ti 2p 3/2 peak and Ti 2p 1/2 peak area ratio is fixed to 0.5. The XPS spectra are modeled using the parameters listed in Table S 1. The peak positions and full width at half maximum (FWHM) are similar to the reference<sup>39</sup>.

Table S 1 The binding energies and full width at half maximum (FWHM) of Ti oxidation states.

| Oxide State             | Binding Energy (eV)       |         |                                                  |         |                                 |        |

|-------------------------|---------------------------|---------|--------------------------------------------------|---------|---------------------------------|--------|

|                         | Uncapped TiO <sub>2</sub> |         | TiO <sub>2</sub> /Al <sub>2</sub> O <sub>3</sub> |         | D. Gonbeau et al. <sup>39</sup> |        |

|                         | Peak position             | FWHM    | Peak position                                    | FWHM    | Peak position                   | FWHM   |

| Ti <sup>4+</sup> 2p 3/2 | 458.32 eV                 | 0.95 eV | 458.29 eV                                        | 1.04 eV | 458.7 eV                        | 1.5 eV |

| Ti <sup>3+</sup> 2p 3/2 |                           |         | 456.82 eV                                        | 1.88 eV | 456.6 eV                        | 1.4 eV |

#### DC and AC resistive switching mode

A forming process, which is usually conducted in DC mode, is required to trigger the resistive switching behavior of the device. In the forming process, the voltage sweeps forward from 0 V to -6 V (red line annotated by  $\oplus$  in Figure 2b) and backward from -6 V to 0 V (red line annotated by  $\bigcirc$  in Figure 2b), i.e., the double voltage sweep between 0 V and -6 V, with a compliance current of 10<sup>-4</sup> A. The forming process switches the device resistance from the initial high resistance state (HRS) to low resistance state (LRS) and leads to the formation of conductive filaments (CFs) that are consist of oxygen vacancies<sup>40</sup> inside the Al<sub>2</sub>O<sub>3</sub> layer.

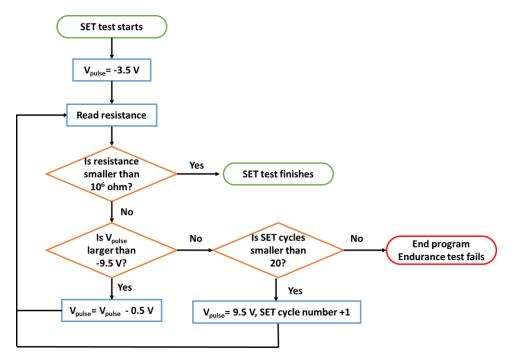

Except the first resistance switching from HRS to LRS is called forming, other following processes of switching the device resistance from HRS to LRS are called SET. In DC mode, the SET process is operated using a dual voltage sweep between 0 and -7 V with a compliance current of  $10^{-4}$  A. In pulse mode, the SET process is completed by applying negative voltage pulses with 100 µs pulse width. The height of the voltage pulse increases from -3.5 V to -9.5 V with a step size of 0.5 V until the device is switched back to LRS (Figure S 4).

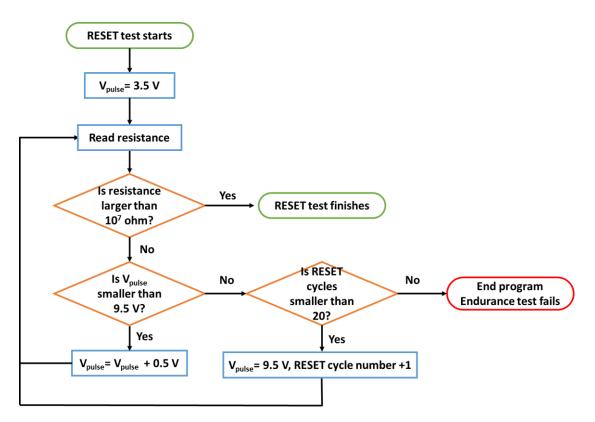

The opposite process of witching the device resistance from LRS back to HRS by partial rupturing of the CFs is called RESET. In DC mode, the RESET process uses a dual voltage sweep between 0 V and 3 V after the forming process (red line annotated by ③ and ④ in Figure 2b) or uses a dual voltage sweep between 0 V and 4V after the SET process. In pulse mode, the RESET process uses positive voltage pulses with 100  $\mu$ s width. A similar operate-and-verify programming scheme<sup>28,29</sup> is used (Figure S 5).

A full round of switching the device resistance from HRS to LRS and then back to HRS is called a switching cycle. The blue lines in Figure 2b represent a typical *I-V* curve of the resistive switching cycle after the first forming-and-RESET cycle. Figure S 6 shows a complete cycle of the switching process in pulse mode.

The switching points are the points where the current jumps up or down abruptly, indicating an abrupt change in device resistance. The switching points can be extracted from the DC I-V curves, as noted in Figure 2b. The voltages and the currents of the switching points are defined as the switching voltages and the switching currents, respectively. All the resistances are read at a voltage of 0.1 V.

**Figure S2.** Switching parameters of five different  $Pt/Al_2O_3/TiO_2$  devices under DC voltage sweep mode. (a) Error bar graph of the SET and RESET switching voltages, (b) error bar graph of the SET and RESET switching currents, (c) error bar graph of the HRS and LRS. The table on the bottom-right side lists all the parameters in detail.

Figure S3. Retention time of HRS and LRS at room temperature.

An operate-and-verify programming scheme is used here, which means more than a single pulse may be used in the SET or RESET operations. The voltage height in both SET and RESET process will increase until the resistance is tuned to the destination resistance value. The details of the operate-and-verify programming scheme is shown in Figure S4-S6. The reason for using the operate-and-verify programming scheme is that the device might not reach the desired resistance range after a single pulse operation. To ensure the device's resistance is indeed programmed to the desired value, the verification step is necessary. This operate-andverify programming scheme requires higher energy consumption compared to single-pulse programming scheme, but is more reliable and guarantees the resistance modulation success for each cycle.

Figure S4. Chart flow of the SET process under pulse mode.

Figure S5. Chart flow of the RESET process under pulse mode.

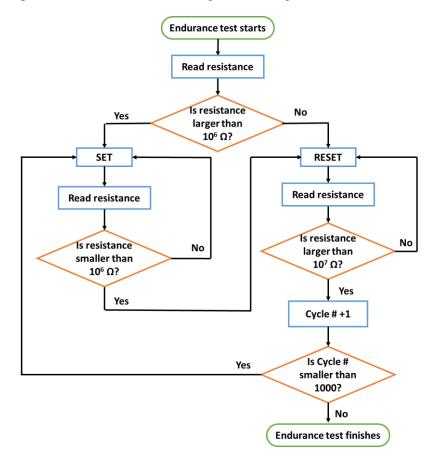

Figure S6. Chart flow of the endurance test under pulse mode.