## Fault-Tolerant Neural Networks from Biological Error Correction Codes

Alexander Zlokapa,  $^{1,\,2}$  Andrew K. Tan,  $^{3,\,2}$  John M. Martyn,  $^{1,\,2}$

Ila R. Fiete,<sup>4</sup> Max Tegmark,<sup>3,2</sup> and Isaac L. Chuang<sup>3,5,2</sup>

<sup>1</sup>Center for Theoretical Physics, Massachusetts Institute of Technology, Cambridge, MA 02139

<sup>2</sup> The NSF AI Institute for Artificial Intelligence and Fundamental Interactions

<sup>3</sup>Department of Physics, Massachusetts Institute of Technology, Cambridge, MA 02139

<sup>4</sup>McGovern Institute for Brain Research, Department of Brain and Cognitive Sciences,

Massachusetts Institute of Technology, Cambridge, MA 02139

<sup>5</sup>Department of Electrical Engineering and Computer Science,

Massachusetts Institute of Technology, Cambridge, MA 02139

It has been an open question in deep learning if fault-tolerant computation is possible: can arbitrarily reliable computation be achieved using only unreliable neurons? In the grid cells of the mammalian cortex, analog error correction codes have been observed to protect states against neural spiking noise, but their role in information processing is unclear. Here, we use these biological error correction codes to develop a universal fault-tolerant neural network that achieves reliable computation if the faultiness of each neuron lies below a sharp threshold; remarkably, we find that noisy biological neurons fall below this threshold. The discovery of a phase transition from faulty to fault-tolerant neural computation suggests a mechanism for reliable computation in the cortex and opens a path towards understanding noisy analog systems relevant to artificial intelligence and neuromorphic computing.

#### I. INTRODUCTION

Early in the development of computer science, it was unknown if unreliable hardware would make the construction of reliable computers impossible. Whenever a component failed, the resulting error had to be corrected by additional components that were themselves likely to fail. Inspired by ideas from error correction, the notion of *fault-tolerant computation* resolved this issue in standard frameworks of classical and quantum computation [1-7]. In these settings, every computation is evaluated by a sequence of faulty components such as Boolean gates (e.g., AND, OR, NOT). If each component's probability of failure falls below a sharp threshold, a strict criterion defining fault-tolerant computation is provably satisfied: computations of any length can be performed with arbitrarily low error. It is also worth noting that the distinction between error correction and fault-tolerance is vital here: while error correction uses noiseless gates to correct errors on a state, fault-tolerant computation only has access to faulty gates. We depict this distinction in Fig. 1.

In artificial intelligence, it is unresolved [8] if neural networks exposed to noise can satisfy an analogous criterion of fault-tolerance. That is, taking a noisy neuron as the fundamental component of computation, can any neural network be executed to arbitrary accuracy when the noise strength falls below a threshold? A similar question appears in neuroscience, where observations of the mammalian brain have shown that neural *representations* are protected against noise by error correction codes [9–11], yet it is unknown if such codes are powerful enough to protect *computations* to achieve arbitrarily small error.

We resolve both open questions in artificial intelligence and neuroscience by demonstrating fault-tolerant neural computation via carefully constructed error correction Error correction: errors on states, gates are noiseless

|       |   |       |            |       |   | _     | i i |

|-------|---|-------|------------|-------|---|-------|-----|

| Logic | • | Logic | ٢          | Logic | ~ | Logic |     |

| gate  |   | gate  | $\diamond$ | gate  |   | gate  |     |

| 0     |   | 0     |            | 0     |   | 0     |     |

Fault tolerance: errors on states and errors on gates

FIG. 1. Schematic comparison of error correction and faulttolerance. While error correction uses noiseless gates to correct errors (red crosses), fault-tolerance must use faulty gates to generate reliable output. Note that errors on states in the fault-tolerant setup can be rewritten as errors on gates, i.e., faulty wires do not have to be directly considered.

codes. This success hinges on generalizations of traditional fault-tolerance in Boolean formulas, as well as a modification of a biologically-observed error correction code known as the *grid code*. Beyond the analytic results proven here, we also provide a numerical estimate of the fault-tolerance threshold and show that naturally existing noisy biological neurons lie within the fault-tolerant regime.

Making the notion of fault-tolerance more precise, we begin by examining von Neumann's original result for fault-tolerant Boolean formulas, which perform universal computation using formulas of Boolean gates [1]. In this setting, one considers access to *physical* gates, which are erroneous and fail (i.e., output the incorrect bit) with some fixed probability p. In a fault-tolerant construction, each gate in the original error-free formula is replaced by a *logical* gate composed of many physical gates. The logical gate is built with error correction such as the repetition code: data is repeated in bundles of three and majority voting determines the outcome. Despite the voting itself being performed by faulty physical gates, von Neumann showed via a recursive repetition code that a fault-tolerant Boolean formula can be constructed if the failure probability p falls below some threshold  $p_0$ . As Boolean gates suffer discrete errors, we will refer to the fault-tolerance of Boolean formulas as *digital faulttolerance*, which is formally defined as follows:

**Digital Fault-Tolerance.** A Boolean formula containing N (error-free) gates can be simulated with probability of error at most  $\epsilon$ using  $\mathcal{O}(N \text{polylog}(N/\epsilon))$  faulty gates. Each gate may fail with probability p for  $p < p_0$ , where  $p_0$  is independent of N and independent of the noiseless formula depth.

In general, the value of  $p_0$  depends on the model of computation under study [2–6]; for example, Ref. [4] demonstrated a noise threshold for reliable computation of  $p_0 = (3 - \sqrt{7})/4 \approx 0.09$  for Boolean formulas constructed from 2-input NAND formulas, which are sufficient for universal computation.

The digital setting of traditional fault-tolerance strongly contrasts the analog computation paradigm of neuroscience and machine learning, where neurons operate using continuous rather than discrete values. Here, we consider two biologically-motivated sources of error. The first is (1) synaptic failure, where a connection between neurons is dropped [12, 13]; this may be modelled by having the neuron output 0 with some fixed probability p. This is in essence a discrete error (the connection is either present or it is not) and may be satisfactorily treated by an extension of von Neumann's construction. The second source of error is (2) analog noise afflicting the output of a neuron [14]; this may be modelled as additive Gaussian noise with standard deviation  $\sigma$ . This second type of error is more difficult to correct and will require specialized treatment via the grid code mentioned above.

To formalize the analog setting of computation, we adopt the framework of artificial neural networks [15], which are universal approximators of continuous functions [16] and have experienced wide success in applications resembling cognitive tasks [17]. The resilience of artificial neural networks to errors has been limited primarily to demonstrations of robustness to weight perturbations or other noise, and hardware fault-tolerance in neuromorphic computing [18–22], without considering biologically-motivated noise nor addressing the formal notion of fault-tolerance analogous to digital faulttolerance defined above.

We will ultimately prove the following result by using grid-code-based error-correcting mechanisms to achieve fault-tolerant neural computation:

Neural Network Fault-Tolerance. A Boolean formula of N (error-free) gates can

be simulated by a neural network with probability of error at most  $\epsilon$  using only faulty neurons. Each synapse entering a neuron fails with probability p; the output of each neuron is subject to additive Gaussian noise with mean zero and standard deviation  $\sigma$ ; a neuron admits at most a fixed number of synapses. There exist nonzero thresholds  $p_0$  and  $\sigma_0$  such that if  $p < p_0$  and  $\sigma < \sigma_0$ , simulating the formula requires  $\mathcal{O}(N \text{polylog}(N/\epsilon))$  faulty neurons.

In the spirit of previous fault-tolerance results [4, 23, 24], the core of our proof is the construction of a logical neuron from a configuration of noisy physical neurons.

An outline of this work is as follows. In Section II, we first provide a brief review of digital fault-tolerance and then demonstrate how this construction may be adapted to design neural networks that are robust against synaptic failure. This is followed by the design of a neuron that is robust to additive Gaussian noise by encoding data in the grid code in Section III; here we also demonstrate how error correction and computation may be achieved using a noisy neural network. We then showcase our fault-tolerant construction by designing a reliable circuit using our logical neuron subject to both modes of noise in Section IV, thereby proving our statement of neural network fault-tolerance. Finally, we provide some concluding remarks including a discussion of the biological plausibility of our assumptions in Section V.

## II. FAULT-TOLERANCE AGAINST DIGITAL ERRORS

First, we provide a review of concatenated faulttolerance results in digital circuits (Section II A). This is followed by a demonstration of an analogous technique for constructing neural networks that are robust against synaptic failure (Section II B).

#### A. Fault-tolerant Boolean circuits

The original construction of a fault-tolerant Boolean gate was initially proposed in Ref. [1] and more rigorously discussed in Ref. [25]. We begin by presenting an adaptation of this construction via a recursive concatenation of repetition codes. To best explain this scheme, let us consider a Boolean gate B, with associated function B(x) that accepts as input a string of bits x and outputs a single bit (for instance,  $B(x_0, x_1) = \text{NAND}(x_0, x_1) =$  $\neg(x_0 \lor x_1)$ ). Let us also consider its faulty counterpart  $B_p$  that fails (i.e., outputs the incorrect bit) with probability p. We would like to construct a fault-tolerant version of  $B_p$  whose error can be decreased arbitrarily for  $p < p_0$  for some threhsold  $p_0$ .

This is achieved by devising a recursive concatenation scheme wherein a *logical* B gate is constructed from *phys*-

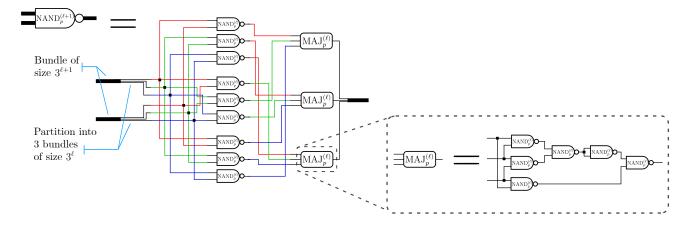

FIG. 2. The recursive concatenation scheme, based on a ternary repetition code, used to construct a logical NAND gate at concatenation level  $\ell + 1$  (denoted  $\text{NAND}_p^{(\ell+1)}$ ) from logical NAND gates at concatenation level  $\ell$ , with the base case  $\text{NAND}_p^{(0)} = \text{NAND}_p$ . The gates denoted  $\text{MAJ}_p^{(\ell)}$  indicate a majority voting operation built from  $\text{NAND}_p^{(\ell)}$  gates, whose explicit construction is illustrated in the inset.

ical B gates, these being the faulty  $B_p$  gates. In particular, a logical B gate at concatenation level- $\ell$ , which we denote by  $B_p^{(\ell)}$ , is recursively defined by a mapping of logical B gates at concatenation level  $\ell - 1$  (i.e.,  $B_p^{(\ell-1)}$ ), with the base case  $B_p^{(0)} = B_p$ . In this mapping,  $B_p^{(\ell)}$  is defined as a repetition code acting on multiple outputs of  $B_p^{(\ell-1)}$ , such that the error suffered by  $B_p^{(\ell)}$  is less than that of  $B_p^{(\ell-1)}$  for  $p < p_0$ . Thus, increasing  $\ell$  decreases the error arbitrarily.

In his seminal work on fault-tolerance [1], von Neumann employed a ternary repetition code, in which a logical bit is encoded as a bundle of physical bits. At concatenation level  $\ell$ , each bundle consists of  $3^{\ell}$  physical bits, and its corresponding logical bit may be decoded as the majority of its physical bits. For instance, the bundle 110 encodes the logical bit 1 at concatenation level  $\ell = 1$ . In this manner, the inputs and outputs to  $B_p^{(\ell)}(x)$ are bundles of size  $3^{\ell}$ , and the output is correct if its physical bits decode to the correct logical bit.

The recursive mapping from  $B_p^{(\ell)}$  to  $B_p^{(\ell+1)}$  is defined by this ternary repetition code: the inputs to  $B_p^{(\ell+1)}$ are each linearly partitioned into three smaller bundles, which are then copied and sent through nine  $B_p^{(\ell)}$  gates in parallel to generate nine independent outputs. To correct errors in these nine outputs, they are then split into three groups of threes, each of which is passed through a (faulty) majority voting gate, and the three resulting outputs are recombined to represent the final output of  $B_p^{(\ell+1)}$ . The majority voting gate is constructed from  $B_p^{(\ell)}$  gates, and hence is also imperfect; its explicit construction depends on the Boolean gate of interest and influences the fault-tolerance threshold. In general, the fewer the gates in the majority gate, the larger the threshold.

For clarity, we depict this fault-tolerance construction

applied to a NAND gate in Fig. 2. The specific arrangement of the wires fed into the majority voting gates is chosen is to prevent error propagation and produce a nonzero threshold. Not all arrangements will yield a nonzero threshold in the limit  $\ell \to \infty$ ; von Neumann's original presentation even suggests randomly permuting these wires. Numerics indicate that this particular construction produces a threshold  $p_0 \approx 2.36\%$ .

As the NAND gate is universal for Boolean computation, this construction enables arbitrarily accurate computation of any Boolean function from faulty NAND gates if the failure probability p lies below the threshold  $p_0$ . Moreover, for  $p < p_0$ , the logical error suffered decreases doubly-exponentially with increasing  $\ell$ , while the circuit size grows only exponentially with  $\ell$ . Hence, achieving a desired error  $\epsilon$  requires overhead  $\mathcal{O}(\text{polylog}(1/\epsilon))$  by the usual arguments for concatenation codes (see e.g. the fault-tolerance threshold theorem of Ref. [26]).

For a circuit of N gates, an overall error of  $\epsilon$  could be achieved by demanding individual gate errors  $\epsilon/N$  as per the union bound. Inserting this desired error rate into the above polylogarithmic overhead, we find a total gate count  $\mathcal{O}(N$ polylog $(N/\epsilon)$ ), in accordance with the digital fault-tolerance theorem discussed in Section I.

# B. Fault-tolerant neural networks for synaptic failure

The above fault tolerant construction may be adapted to devise a fault-tolerant neural network that is robust against synaptic failure, as this is in essence a discrete error. To illustrate this, let us consider a neural network constructed from rectified linear unit (ReLU) activation functions, where  $\text{ReLU}(x) = \max(0, x)$  on real inputs x. In this case, synaptic failure may be modeled by replacing each ReLU with a faulty ReLU that fails with probability p, i.e.,

$$\operatorname{ReLU}_p(x) := \begin{cases} \operatorname{ReLU}(x) & \text{with probability } 1-p \\ 0 & \text{with probability } p. \end{cases}$$

(1)

Like von Neumann's error model for Boolean gates, the output of this faulty ReLU is incorrect with some probability, and thus its errors may be corrected by employing a concatenated repetition code.

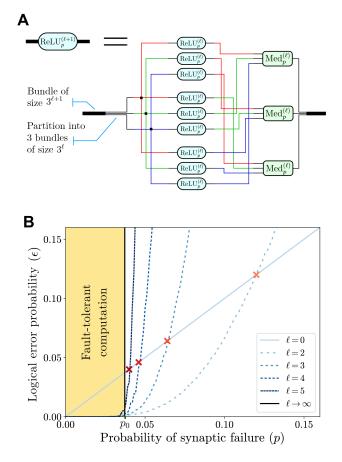

The aim is to construct a fault-tolerant ReLU activation function, which is equivalent to a fault-tolerant neuron. We will employ a concatenated ternary repetition code analogous to that presented above, replacing the logical Boolean gates with logical ReLU's. However, there is one important distinction in our construction: as inputs and outputs are now analog instead of binary, we will interpret the logical value carried by a bundle as the *median* of its values rather than the majority. Accordingly, the majority voting gate in the original repetition code is replaced by a median gate, which will appropriately correct errors that occur in a bundle. With this modification noted, we illustrate the complete recursive scheme in Fig. 3a; here, it is shown how to construct a logical ReLU at concatenation level  $\ell + 1$ (denoted  $\operatorname{ReLU}_p^{(\ell+1)}$ ) from logical ReLU's at concatenation level  $\ell$  (denoted  $\operatorname{ReLU}_p^{(\ell)}$ ), with the usual base case  $\operatorname{ReLU}_p^{(0)} = \operatorname{ReLU}_p.$

What remains is to construct the median operation out of ReLU's. At concatenation level  $\ell$ , we are interested in computing the median of three bundles, each of size  $3^{\ell}$ . Denoting this quantity as  $m = \operatorname{Med}_{p}^{(\ell)}(a, b, c)$ , where a, b, c represent each bundle, it may be computed with the following network of depth three:

$$x = \operatorname{ReLU}_{p}^{(\ell)}(a - b)$$

$$y = \operatorname{ReLU}_{p}^{(\ell)}(-a + c + x)$$

$$z = \operatorname{ReLU}_{p}^{(\ell)}(b - c + x)$$

$$m = \operatorname{ReLU}_{p}^{(\ell)}(a + b - c + y - z).$$

(2)

While the final ReLU is not strictly necessary for the computation of the median, it is included to prevent error propagation and achieve fault-tolerance. As a result, this median works only on positive inputs, but this is admissible as the output of  $\text{ReLU}_p^{\ell}$  (which is input into the median) is necessarily non-negative. We also note that expressing this median construction as a neural network requires skip connections to perform its computation.

We visualize the performance of this fault-tolerance construction in Fig. 3 by plotting the *pseudothresholds*: where the error probability at concatenation level  $\ell$  intersects that of  $\ell = 0$ . Plotting these for increasing levels of concatenation indicates a convergence to the threshold  $p_0 \approx 3.72\%$ . Therefore, this construction ultimately produces a fault-tolerant ReLU neuron, protected against synaptic failure for  $p < p_0$ . And by an argument analogous to the digital fault-tolerance of

FIG. 3. (A) The recursive concatenation scheme of digital fault-tolerance is extended to construct a logical ReLU at concatenation level  $\ell + 1$  from logical ReLUs at level  $\ell$ . Note how the fault-tolerant ReLU is a generalization of the fault tolerant NAND gate in Fig. 2. The gates denoted  $\operatorname{Med}_p^{(\ell)}$  indicate a median operation that is composed of  $\operatorname{ReLU}_p^{(\ell)}$ 's and used to correct errors; its explicit construction is presented in Eq. (2). This construction ultimately generates a logical neuron for a fault-tolerant neural network in the presence of synaptic failure. (B) The logical error probability of  $\operatorname{ReLU}_p^{(\ell)}(x)$  on random inputs  $x \in [-1, 1]$  as determined by numerical simulation. The pseudothresholds (red crosses) occur when the error probability intersects that of  $\ell = 0$ ; they converge exponentially to the threshold  $p_0 \approx 3.72\%$  (vertical black line) with increasing  $\ell$ .

Boolean circuits, achieving a desired error  $\epsilon$  requires overhead  $\mathcal{O}(\text{polylog}(1/\epsilon))$ . Using the argument presented at the end of Section II A, this translates to an overhead  $\mathcal{O}(N\text{polylog}(N/\epsilon))$  for a circuit of N gates, thus achieving neural-network fault-tolerance (excluding Gaussian noise) as presented in Section I.

### III. FAULT-TOLERANCE AGAINST ANALOG ERRORS

While a simple adaptation of fault-tolerant constructions on noisy Boolean circuits yields a neural network that is robust to synaptic failure, the treatment of additive Gaussian noise proves more difficult. In particular, the repetition-based scheme of von Neumann fails for Gaussian noise with nonzero standard deviation  $\sigma$ : unlike the exponential suppression found for digital errors, repeating N neurons in the presence of analog noise only reduces analog noise to  $\sigma/\sqrt{N}$ . Hence the requisite circuit size scales as  $O(1/\epsilon^2)$ , which does not achieve the  $O(\text{polylog}(1/\epsilon))$  performance desired by the neural network fault-tolerance theorem.

Instead, we turn to an analog error correction code: the grid code. Unlike the repetition code, the grid code achieves exponentially small error at asymptotically finite information rates, saturating the Shannon bound [27] and allowing effective error correction against Gaussian neural spiking noise [11] (see Appendix A for a more detailed discussion).

We start with a brief overview of the grid code and its properties in Section III A. Next, we detail the construction of an error correcting procedure using noisy neurons in Section III B. Finally, we describe in Section III C how the logical signal may be manipulated in a manner that allows for universal approximation and analyze its error threshold assuming a distribution of logical neural weights.

### A. Overview of the grid code

We first provide a brief, self-contained exposition of the original grid code results of Refs. [9–11]. These works study the entorhinal cortex in mammals and show that lattice neural firing patterns may correspond to a special encoding of the mammal's position (in 2D space), known as the *grid code*. In the grid code, a particular coordinate (say x or y in 2D space) takes values from a discrete set  $\{x_k\}$  of S possible values that lie within a fixed interval [0, X).

The encoding of each possible value  $x_k$  is modeled by a set of phases

$$\operatorname{Enc}\left[x_{k}\right] := \left\{\frac{e(x_{k})}{\lambda_{j}} \bmod 1\right\}_{j=1}^{M}, \quad (3)$$

which is defined over M relatively prime integers  $\{\lambda_j\}_{j=1}^M$ , referred to as *moduli* [9, 10], and a function e(x) referred to as the *encoding function*. The choice of relatively prime moduli ensures, by consequence of the Chinese Remainder Theorem, that all  $x \in [0, \prod_{j=1}^M \lambda_j)$  are encoded into distinct codewords. Restricting our domain as above, with  $X \ll \prod_{j=1}^M \lambda_j$ , allows the remaining phase space to be used for error correction. Moreover, in the

FIG. 4. (A) Biological setting of the grid code. Neuron firings form a hexagonal lattice with different spacings  $\lambda_j$ , with lattice sites corresponding to physical locations of an animal in the lab. (B) Example encoding performed by the grid code over M = 15 moduli { $\lambda_1, \ldots, \lambda_{15}$ }. Observe that these phases are well-approximated as being drawn uniformly at random, in accordance with the formalism of the grid code. (C) Example decoding of phases representing x = 0.5. The possible decodings allowed by a given phase (indicated by a unique color for each  $\lambda_j$ ) are periodic. Each decoded phase is subject to Gaussian noise (inset). Since the phases constructively add at the true decoded value, maximum likelihood estimation selects the value with the highest signal.

original grid code, the encoding function e(x) is chosen to be the identity. Here, we will instead perform neural network computations by selecting e(x) to implement an activation function; we will let e(x) be an arbitrary function for now, and specify it later. In general, we denote the vector of M phases produced by the encoder as  $\phi := \operatorname{Enc}[x_k] = \{\phi_j\}$ . An example of a firing pattern of the grid code, as well as its moduli, is illustrated in Fig. 4a.

To maintain the favorable error-correcting properties of the grid code, the  $x_k$ 's are chosen to satisfy  $x_k \ll X$ , and the minimum spacing between codewords  $\Delta x :=$  $\min_{k\neq j} |x_k - x_j|$  is chosen such that  $\max_j \lambda_j \ll \Delta x$ . More generally, when the encoding function e(x) is not the identity function, the same condition must be upheld for  $\Delta x$  given by  $\min_{i \neq j} |e(x_i) - e(x_j)|$  such that  $e(x_i) \neq e(x_j)$ .

In the limit  $\max_j \lambda_j \ll X$  for  $X \ll \prod_{j=1}^M \lambda_j$ , the codeword  $\phi$  encoding a randomly sampled  $x_{k^*} \in \{x_k\}$  is wellapproximated as being drawn from a uniform distribution  $(\phi_j \sim \mathcal{U}(0, 1))$  [11]. We visualize this fact in Fig. 4b by plotting the phases of an example grid code. This property provides a sensitive encoding that changes significantly if the input is slightly perturbed. Since each codeword consists of a vector of phases  $\{\phi_j\}$  with the period of each  $\phi_j$  determined by  $\lambda_j$ , decoding corresponds to the constructive interference of summed phases to yield the correct decoded position, as depicted in Fig. 4c.

An ideal decoder  $\text{Dec} [\phi]$  would perform maximum likelihood estimation (MLE) to recover the most probable value  $x_{k^*}$  given a codeword  $\phi$ . For ease of presentation, we modify the original biologically inspired neural decoder that approximates MLE [11] to a simpler but functionally equivalent form; this form will be more easily implemented by a neural network later in this work. Given phases  $\phi = \{\phi_j\}$ , we will recover the true position  $x_{k^*}$  by the MLE decoder

$$\operatorname{Dec}\left[\boldsymbol{\phi}\right] := \operatorname{arg\,max}_{x_k} \sum_{j=1}^{M} \cos\left[2\pi \left(\frac{x_k}{\lambda_j} - \phi_j\right)\right]. \quad (4)$$

To see that this procedure is indeed performing maximum likelihood estimation, observe that if  $x_{k^*}$  is known to belong to a discrete set of values  $\{x_k\}$ , then the estimated decoding  $\hat{x}$  is given by maximizing the conditional probability

$$\hat{x} = \operatorname*{arg\,max}_{r} \Pr(\boldsymbol{\phi}|x_k). \tag{5}$$

Assuming that the encoding  $\text{Enc} [x_k]$  is distributed in the codespace according to a spherical Gaussian with variance  $s^2$ , the likelihood function is a wrapped normal distribution

$$\Pr(\boldsymbol{\phi}|\boldsymbol{x}_k) \propto \prod_{j=1}^{M} \exp\left(-\frac{1}{2s^2} \|\operatorname{Enc}\left[\boldsymbol{x}_k\right]_j - \boldsymbol{\phi}_j\|^2\right), \quad (6)$$

where  $\|\phi\| := \min\{|\phi|, 1 - |\phi|\}$  denotes the distance between phases. In the limit of  $s \ll 1$  and taking  $e(x_k) = x_k$ , the likelihood function is well approximated by the more tractable circular normal function

$$\Pr(\boldsymbol{\phi}|x_k) \propto \prod_{j=1}^{M} \exp\left(\frac{1}{2\pi s^2} \cos\left[2\pi \left(\frac{x_k}{\lambda_j} - \phi_j\right)\right]\right).$$

(7)

Comparing Eq. (7) to Eq. (4), we see that the decoding scheme of Eq. (4) is indeed maximizing the likelihood.

Lastly, to more intuitively understand the grid code, note that because the M phases  $\phi_j$  fall between 0 and 1, the coding space is the unit hypercube  $[0,1]^M$ ; due to the unit modulo, the coding space satisfies periodic boundary conditions and thus corresponds to the Mtorus. The coding line [0, X) is thus a set of parallel line segments in the hypercube. In general, error correction codes may be described as a hypersphere packing problem: each codeword corresponds to an origin of a sphere in a high-dimensional space, and errors that fall within the radius of the sphere are correctable to the true codeword. Here, the grid code is a hypersphere packing problem in the M-1 dimensional hyperplane perpendicular to the coding line segments. Under this formalism, we arrive at a scaling of the minimum distance between line segments with the number of phases for fixed X of  $d_{\min} = \Theta(\sqrt{M})$  [11], denoting an asymptotic bound on  $d_{\min}$  from both above and below. Our choice of  $\lambda \ll \Delta x$ ensures that each  $\operatorname{Enc}[x_i]$  lies within a different line segment and is therefore also separated by at least  $d_{\min}$ , and consequently any perturbation in the phase space less than  $d_{\min}/2$  is correctable using the maximum likelihood decoder.

### B. The fault-tolerant logical neuron

Let us now use the grid code to present and analyze the construction of a fault-tolerant neuron. We assume an error model where Gaussian noise  $\xi \sim \mathcal{N}(0, \sigma)$  is added to the output of each neuron, representing the noise associated with neural spikes in a biological setting. We note that we do not account for synaptic failures at this stage, as the grid code is only tailored to analog noise; later in Section IV B, we address both additive Gaussian noise and synaptic failure.

Focusing on a single neuron in a larger neural network, we take the number of neurons connected from the previous layer to be  $m_0$ . As in the presentation of the grid code, each neuron carries a value that is guaranteed to belong to a discrete set of S values, which we parameterize here as  $\{x_k = k\Delta x\}$  for  $k = 0, \ldots, S-1$ , such that  $(S-1)\Delta x < X$  for some X. The M relatively prime moduli must satisfy  $\lambda_j \ll X \ll \prod_{j=1}^M \lambda_j$ , and thus the codewords are uniformly distributed for random  $x_{k^*}$ .

We however introduce the following modification to the underlying grid code. While the typical grid code assumes a range of values  $x_k \in [0, X)$ , here we will take advantage of the periodicity of the grid code due to the periodicity of the phases (as these are evaluated modulo 1), and introduce a smaller range of values [0, X'] to which the encoding function e(x) may output. That is, the encoding function e(x) is chosen such that encoded values  $e(x_k)$  exist in a condensed space [0, X') for some X' < X, while fully decoded values  $x_k$  can still exist in the larger space [0, X). A vanilla grid code with an identity encoding function  $e(x_k) = x_k$  has X' = X; here, we will select  $e(x_k)$  to be a non-identity function with X' < X, which will assist in building logical activation functions and thus performing neural network computation. Moreover, to remain consistent with the usual requirement that  $\lambda_j \ll X \ll \prod_{j=1}^M \lambda_j$ , we will also demand  $\lambda_j \ll X' \ll \prod_{j=1}^M \lambda_j$ . Turning now to the construction of our fault-tolerant

Turning now to the construction of our fault-tolerant neuron, we incorporate the traditional principles of fault tolerance: we perform computations in the codespace to protect against errors, and interleave each computation between encoding and decoding steps that correct errors and ensure that computation remains in the protected codespace. In the language of the grid code, this means performing computations on the phases  $\phi$ , these computations corresponding to the application of weights and biases followed by an activation function. Note that the result of our decoding step is a one-hot encoding of  $x_k$ , rather than  $x_k$  itself, and therefore the decoded signal remains redundantly encoded and protected from noise; this is in line with traditional fault-tolerant constructions where the signal is maintained redundantly throughout computation and error correction.

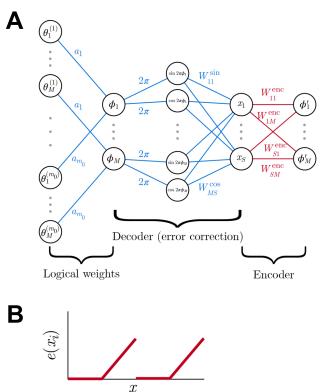

The general construction of the logical neuron is presented in Fig. 5a. This depicts a logical neuron decomposed into physical neurons, with time advancing to the right. The number of inputs to the physical neurons is unrestricted, and hence this construction has an unbounded fan-in.

In the illustration, a previous layer of logical neurons passes to the logical neuron a set of encoded phase vectors, which we denote as  $\boldsymbol{\theta}^{(i)} = [\theta_1^{(i)}, \dots, \theta_M^{(i)}]$  for the *M*-dimensional phase vector of the *i*th logical input neuron. Assuming that inputs to the network are all encoded in the same grid code, each input phase vector  $\boldsymbol{\theta}^{(i)}$  encodes a quantity that lies in [0, X') in the decoded space.

The logical neuron itself consists of three stages: (1) the logical weights, (2) the decoder, and (3) the encoder. First, (1) the logical weights correspond to the weights of the error-free neuron that one seeks to apply; we denote these by  $\{a_i\}_{i=1}^{m_0}$  for each of the  $m_0$  (logical) neurons of the previous layer. As depicted in the figure, the logical weights are each repeated M times and then applied to the inputs  $\boldsymbol{\theta}^{(i)}$ , mapping directly from grid code phases to grid code phases.

Second, (2) the decoder performs error correction via maximum likelihood estimation (MLE) as described in Section III A. The key observation is that the structure of the grid code allows MLE to be approximated by a neural network. This is achieved using sine and cosine activation functions with appropriately chosen weights. the combination of which implements the MLE decoding scheme of Eq. (4) and also imposes the periodicity of the resulting phase encoding. The particular choice of weights, denoted  $W_{ik}^{\sin}$  and  $W_{ik}^{\cos}$ , is explained and justified in the following section. Moreover, the decoder does not return to the original [0, X') space; instead, it outputs a value in the larger space [0, X), allowing the application of logical weights to decode to valid values. At the end of the decoding step, we are left with one-hot encoding representing the correct value  $x_k \in [0, X)$  with high probability due to the robustness of the maximum likelihood estimate.

FIG. 5. (A) Logical neuron decomposed into physical neurons to achieve fault-tolerance in the presence of analog noise. The neuron receives encoded neural outputs from the previous layer and performs a computation with time advancing to the right. The logical weights  $a_i$  are applied in the codespace, and the decoder recovers  $x_k$  by performing error correction. The encoder (red) performs a logical activation function (e.g., ReLU) using appropriate weights and encodes back to the codespace. (B) The logical ReLU encoding function  $e(x_i)$  used in the encoder (Eq. (13)) for X' = X/2. This function is a ReLU repeated over X/X' = 2 periods; the construction allows the fault-tolerant neural network to implement the standard ReLU activation function.

Lastly, (3) the encoder serves two roles: it re-encodes back into the codespace, and it also performs the computation via the application of a logical activation function (e.g., ReLU). Explicitly, the weights  $W_{ki}^{enc}$  are chosen such that this stage projects the one-hot representation of some  $x_k$  back to its appropriate codeword. The specific choice of weights also applies the logical activation function through a chosen encoding function  $e(x_k)$ , ultimately returning to the space [0, X'). The choice of weights  $W_{ki}^{enc}$  and encoding function e(x) for various activation functions are presented in the following sections.

# C. Neural network implementation of reliable computation

Let us now analyze the performance of the logical neuron in the fault-tolerant setting, where every physical neuron is subjected to noise. We will ultimately derive an analytical expression for the number of physical neurons needed to build a logical neuron with logical error at most  $\epsilon$ .

To streamline our presentation, we begin by looking at the encoder stage. Accounting now for the additive Gaussian noise  $\xi \sim \mathcal{N}(0, \sigma)$  suffered by the physical neurons, the encoder of Eq. (3) becomes

$$\widetilde{\operatorname{Enc}}\left[x_{k}\right] = \left\{\widetilde{\phi}_{j} = \frac{e(x_{k})}{\lambda_{j}} + \xi \bmod 1\right\},\qquad(8)$$

for i.i.d.  $\xi \sim \mathcal{N}(0, \sigma)$  sampled for each phase  $\phi_j$ . The decoder in the logical neuron uses only two layers (see Fig. 5a). The first layer multiplies each phase  $\phi_j$  by a weight  $2\pi$ ; the second layer uses sine and cosine activation functions to compute  $\sin(2\pi\phi_j)$  and  $\cos(2\pi\phi_j)$ , and then multiplies them by weights  $W_{jk}^{\sin}$  and  $W_{jk}^{\cos}$ , respectively. We select these weights to be  $W_{jk}^{\sin} = \sin\left(2\pi\frac{x_k}{\lambda_j}\right)$  and  $W_{jk}^{\cos} = \cos\left(2\pi\frac{x_k}{\lambda_j}\right)$ .

Upon applying a decoding, any error is 'reset' if the decoding  $\widetilde{\text{Dec}}\left[\widetilde{\phi}\right]$  is successful, such that the logical neuron will not propagate any additional error into future computations. Evaluating all noise contributions, we have

$$\operatorname{Dec}\left[\tilde{\boldsymbol{\phi}}\right] = \operatorname*{arg\,max}_{k} f(k),\tag{9}$$

$$f(k) := \xi + \sum_{j=1}^{M} \left[ f_1(j,k) + f_2(j,k) \right], \qquad (10)$$

where

$$f_1(j,k) = \sin\left(2\pi\frac{x_k}{\lambda_j}\right) \left[\sin\left(2\pi\tilde{\phi}_j\right) + \xi\right],\tag{11}$$

$$f_2(j,k) = \cos\left(2\pi \frac{x_k}{\lambda_j}\right) \left[\cos\left(2\pi \tilde{\phi}_j\right) + \xi\right],\qquad(12)$$

and as usual each  $\xi$  is sampled i.i.d.

Suppose that the correct neuron value corresponds to  $k = k^*$ , i.e., the value  $x_{k^*}$  is encoded in the phases. For the decoder to identify the correct neuron via a threshold cutoff, we require  $f(k = k^*) > f(k \neq k^*)$  for all k. If the mean of the correct neuron is greater than the mean of each incorrect neuron, a threshold will exist to distinguish the correct decoding from incorrect decodings in expectation. We use this insight to gain an analytical scaling for the number of physical neurons needed to construct a logical neuron with logical error  $\epsilon$ .

The key observation is that in the noiseless limit, the phases  $\phi_j$  are given by  $\phi_j = x_{k^*}/\lambda_j \mod 1$ . At  $k = k^*$ , the elements in the sum of Eq. (9) constructively add as  $f_1(j,k^*) + f_2(j,k^*) \approx 1$  for each j and thus  $f(k = k^*)$  has a non-zero mean. On the other hand, for all  $k \neq k^*$ , the neural network weights are sine or cosine of a uniformly distributed random variable and the terms in the sum

destructively interfere leaving  $f(k \neq k^*) \approx 0$  on average.

To make the scaling argument precise for computation, we need to characterize the noise in Eq. (9), which requires assumptions to be made about the statistical properties of the noise and logical weights. With this in mind, we make the following assumptions. In order to maintain properties of modular arithmetic, we restrict the logical weights to integer values  $a_i \in \mathbb{Z}$  such that  $\sum_i |a_i| \leq X/X'$ . We also assume that the logical weights  $a_i$  are approximately normally distributed from a Gaussian distribution with standard deviation  $\alpha$ . Additionally, we take both the number of moduli M and the number of neurons  $m_0$  connected from the previous layer to be much larger than one, allowing application of the central limit theorem.

As an example, we will select ReLU as the logical activation function of the logical neuron; other activation functions may be implemented analogously. A ReLU activation function may be implemented by the encoding function

$$e(x_i) = \begin{cases} 0 & (x_i \mod X') < X'/2\\ (x_i - X'/2) \mod X' & (x_i \mod X') \ge X'/2, \end{cases}$$

(13)

which behaves like a periodic ReLU. We depict this encoding function in Fig. 5b. This function corresponds to choosing weights on the physical neurons  $W_{ij}^{\text{enc}} = \frac{e(x_i)}{\lambda_j} \mod 1.$

The above analysis can now be made explicit to demonstrate the fault-tolerant properties of the logical neuron. Looking at the logical weights stage, the  $m_0$  logical neurons from the previous layer connected to the logical neuron are represented by codewords Enc  $[x^{(1)}], \ldots, \text{Enc } [x^{(m_0)}]$ , i.e., Enc  $[x^{(i)}] = \boldsymbol{\theta}^{(i)}$ . Therefore, the application of the logical weights must map from the  $m_0 \times M$  neurons in  $\{\text{Enc } [x_i]\}$  to a single set of phases  $\{\phi_j\}$  such that our activation function is applied after decoding and re-encoding, as per the order of operations in the logical neuron. By assigning weights  $W_{ij} = a_i \text{ from } \theta_j^{(i)}$  to  $\phi_j$  (as illustrated in the 'Logical weights' layer in Fig. 5a) with a linear activation function and bias  $-\frac{X'}{\lambda_j} \sum_{i:a_i < 0} a_i$ , we obtain the following phases in the absence of noise:

$$\phi_j = \left(\sum_{i=1}^{m_0} a_i \theta_j^{(i)}\right) - \left(\frac{X'}{\lambda_j} \sum_{i:a_i < 0}^{m_0} a_i\right).$$

(14)

We proceed to include noise in the analysis. Let us denote a noisy encoding by phases  $\tilde{\theta}_j^{(i)}$ . Each of the *S* neurons over the discretized decoded space have noise  $\xi$ , and each is multiplied by approximately uniformly distributed weights due to the phases over the moduli. Applying the central limit theorem to  $\sum_{i=1}^{S} u\xi$  for  $u \sim \mathcal{U}(0, 1)$ , we find this equivalent to noise with mean zero noise and variance  $\sigma^2 \cdot S/3$ . Adding this noise of the codespace neuron to the noise acquired from the physical neuron, we find  $\tilde{\theta}_j^{(i)} = \theta_j^{(i)} + \xi + \zeta$  for  $\zeta \sim \mathcal{N}(0, \sigma \sqrt{S/3})$ . Inserting noise in Eq. (14), we have

$$\tilde{\phi}_j = \left[\sum_{i=1}^{m_0} a_i \tilde{\theta}_j^{(i)}\right] - \left(\frac{X'}{\lambda_j} \sum_{i:a_i < 0} a_i\right) + \xi$$

$$= \phi_j + \xi + \sum_{i=1}^{m_0} a_i (\xi + \zeta).$$

(15)

Applying the central limit theorem to the last term  $\sum_{i=1}^{m_0} a_i(\xi + \zeta)$ , we find that its mean vanishes while its variance is  $\frac{1}{3}Sm_0\alpha^2\sigma^2$  in the large-S limit (having already applied the central limit theorem to S).

We can now formalize the above argument that correct decoding requires  $f(k = k^*) > f(k \neq k^*)$ . To simplify notation, we introduce the variable  $\beta := 4\pi^2(1 + Sm_0\alpha^2/3)$ . By applying the error correction analysis (Eq. (9)) to the phases after a step of computation (Eq. (14)) again in large M regime, we find that the true decoding after application of the logical neuron is distributed as

$$f(k = k^*) \sim \mathcal{N}\left(Me^{-\beta\sigma^2/2}, \sqrt{M\left(\frac{1}{2} + \frac{1}{2}e^{-2\beta\sigma^2} - e^{-\beta\sigma^2} + \sigma^2\right) + \sigma^2}\right),$$

(16)

while the incorrect decoding is centered at zero:

$$f(k \neq k^*) \sim \mathcal{N}\left(0, \sqrt{M\left(\frac{1}{2} + \sigma^2\right) + \sigma^2}\right),$$

(17)

where both distributions are seen to have standard deviations  $\mathcal{O}(\sqrt{M})$ . Upper-bounding the maximum element drawn from the distribution of  $f(k \neq k^*)$  out of S draws using Jensen's inequality and a union bound, we find that

$$f_{\max}(k \neq k^*) := \mathbb{E}[\max \text{ draw of } f(k \neq k^*)] \\ \leq \sqrt{[M(1+2\sigma^2)+2\sigma^2]\log S}.$$

(18)

Finally, to determine if  $\arg \max_k$  returns a value other than  $k^*$ , we compute the probability that this exceeds  $f(k = k^*)$ :

$\begin{aligned} &\Pr[\text{logical neuron fails}] = \Pr[f(k=k^*) < f_{\max}(k \neq k^*)] \\ &\leq \frac{1}{2} \text{erfc} \Bigg[ \frac{e^{-\beta \sigma^2/2} M - \sqrt{[M(1+2\sigma^2)+2\sigma^2] \log S}}{\sqrt{M\left(1+e^{-2\beta \sigma^2}-2e^{-\beta \sigma^2}+2\sigma^2\right)+2\sigma^2}} \Bigg]. \end{aligned}$

This error probability is the logical error, which we seek to upper bound by  $\epsilon$ . Expanding in small  $\epsilon$  and taking  $M, \beta \sigma^2 \gg 1$ , we find that the number of moduli required

to bound the logical error by  $\epsilon$  scales is

$$M(\epsilon) \approx \log(1/\epsilon) \left[ e^{\beta \sigma^2} (1 + 2\sigma^2) + e^{-\beta \sigma^2} - 2 \right]$$

$$\approx e^{\beta \sigma^2} (1 + 2\sigma^2) \log(1/\epsilon) = \mathcal{O}(e^{\beta \sigma^2} \log(1/\epsilon)),$$

(20)

where  $\beta$  is the aforementioned constant independent of the noise or error correction overhead. The  $\mathcal{O}(e^{\beta\sigma^2})$  dependence on  $\sigma$  originates from the constructive interference of the grid code: noisy phases for the true decoding contribute to a neuron with mean activation  $Me^{-\beta\sigma^2/2}$ , while the incorrect decoding yields a mean activation of zero. Although the noise produces neural activations of variance  $\mathcal{O}(\sigma\sqrt{M})$ , there always exists sufficiently large M to identify the correct decoding.

Note that the number of physical neurons in the logical neuron scales linearly in the number of moduli, as per its structure in Fig. 5a). Hence, a fault-tolerant neural network can be constructed under the presence of arbitrarily large additive Gaussian noise using  $\mathcal{O}(e^{\beta\sigma^2}\log(1/\epsilon))$  physical neurons for a constant  $\beta$ . For a network of N neurons, this translates to  $O(e^{\beta\sigma^2}N\text{polylog}(N/\epsilon))$  physical neurons as per the argument of Section II. This result is in agreement with the neural network fault-tolerance theorem of Section I (excluding synaptic failure, which we address in Section IV B), and also mirrors known results in digital fault-tolerance [24].

## IV. RELIABLE CIRCUITS FROM THE FAULT-TOLERANT NEURON

The fault-tolerant neural network presented above is a universal approximator of continuous functions due to the use of a ReLU activation function. In this section, we demonstrate the flexibility of the fault-tolerant neural network construction by building Boolean circuits from fault-tolerant neural networks and providing evidence of their reliability. In Section IV A, we numerically verify the predictions of Section III by simulating the code size requirement to implement a two-bit Boolean multiplication circuit constructed from neurons subject to additive Gaussian noise. In Section IVB, we combine the constructions of Section II and Section III to provide analytic and numerical evidence of the robustness of our faulttolerant neural network against both additive Gaussian noise and synaptic failure. Finally, in Section IVC, we move towards more biological code parameters by studying the more biologically realistic scenario where moduli are encoded redundantly.

#### A. Reliability in the presence of Gaussian noise

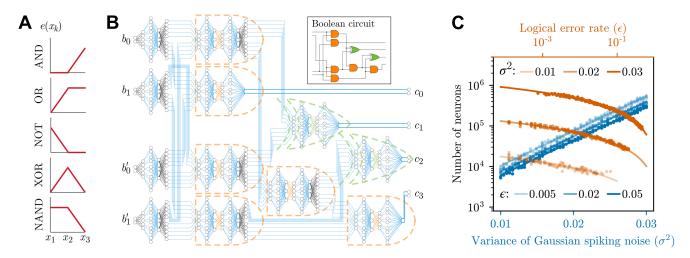

Building on the fault-tolerant neural network of Section III, a natural extension of this framework to Boolean gates emerges if additional encoding functions are introduced. In particular, as computations are done in the encoding step of the fault-tolerant neuron in Section III B, special encoding functions can be used to implement AND, OR, NOT, XOR, and NAND operations, among other Boolean gates. We illustrate these encoding functions in Fig. 6a, whose specific construction we discuss next. Afterwards, we will use these Boolean gate constructions to enable a fault-tolerant neural implementation of a multiplier circuit. Because these constructions use the faulttolerant neuron of Section III B, they are robust against Gaussian noise only; we account both Gaussian noise and synaptic failure in Section IV B.

To formalize this construction, define two logical input bits  $A, B \in \{0, a\}$ , interpreting 0 as False and a as True. Letting  $\Delta x = a$ , the decoder  $\text{Dec} [\phi]$  will only decode to the set of variables  $\{x_1 = 0, x_2 = a, x_3 = 2a\}$ . For notational convenience, we define codeword vectors

$$\boldsymbol{\phi}_a := \left\{ \phi_j = \frac{a}{\lambda_j} \mod 1 \right\},\tag{21}$$

$$\phi_0 := \left\{ \phi_j = \frac{0}{\lambda_j} \mod 1 \right\}.$$

(22)

Beginning with a NOT gate, define the NOT encoder Enc<sup>¬</sup> $[x_1] = \phi_a$  and Enc<sup>¬</sup> $[x_2] = \text{Enc<sup>¬</sup>}[x_3] = \phi_0$ . As before, this corresponds to a neural network with weights given by the codeword vectors. To compute  $\neg A$ , we simply compute Enc<sup>¬</sup>[Dec[A]], which applies error correction and re-encode into the codespace with a NOT computation.

To implement AND and OR gates, we require an additional layer of unity weights, producing the value  $\phi_i = \theta_i^A + \theta_i^B$  for input phases corresponding to bits A and B. Applying the decoder will give either 0, a or 2a based on the cases  $(A, B) \in \{(0,0)\}, \{(a,0), (0,a)\}$  or  $\{(a,a)\}$  respectively. The AND encoder is given by  $\operatorname{Enc}^{\wedge}[x_1] = \operatorname{Enc}^{\wedge}[x_2] = \phi_0$  and  $\operatorname{Enc}^{\wedge}[x_3] = \phi_a$ , and the OR encoder is given by  $\operatorname{Enc}^{\vee}[x_1] = \phi_a$ .

Likewise the XOR encoder is given by  $\operatorname{Enc}^{\oplus}[x_1] = \operatorname{Enc}^{\oplus}[x_3] = \phi_0$  and  $\operatorname{Enc}^{\oplus}[x_2] = \phi_a$ , and the NAND encoder by  $\operatorname{Enc}^{\bar{\wedge}}[x_1] = \operatorname{Enc}^{\bar{\wedge}}[x_2] = \phi_a$  and  $\operatorname{Enc}^{\bar{\wedge}}[x_3] = \phi_0$ . These Boolean gates furnish a universal gate set, from which arbitrary Boolean circuits, and thus arbitrary computations, may be achieved in a fault-tolerant manner. As per the results of Section III C, a fault-tolerant neural network assembled of these *neural-Boolean* gates satisfies the neural network fault-tolerance theorem (excluding synaptic failure) with  $\mathcal{O}\left(e^{\mathcal{O}(\sigma^2)}\log(1/\epsilon)\right)$  physical neurons.

As an application of these neural-Boolean gates, we use them to implement a fault-tolerant two-bit multiplier. In this construction, the individual Boolean gates of the two-bit multiplier circuit are replaced with their corresponding neural-Boolean gates. We depict this circuit in Fig. 6b. Here, the neural network takes in two 2-bit binary numbers  $b_0b_1$  and  $b'_0b'_1$  and outputs their product, suffering an error that can be decreased arbitrarily error by increasing the number of moduli. For this neural twobit multiplier, we numerically estimate the circuit size required to achieve a logical error rate  $\epsilon$  with respect to the Gaussian noise strength  $\sigma^2$ . The results are shown in Fig. 6c and are in good agreement with the analytic prediction of Eq. (20).

## B. Reliability in the presence of Gaussian noise and synaptic failure

Next, we study fault-tolerance with respect to both modes of noise: synaptic failure and additive Gaussian noise. Here, we consider a fault-tolerant neural NAND gate, which simplifies analysis as it is alone sufficient for universal Boolean computation. By comparing the NAND encoding function of Fig. 6a and the ReLU encoding function of Fig. 5b, we see that the NAND encoding function is the opposite of the ReLU encoding function. Hence, we can transfer over the Gaussian noise analysis of Section III C to the setting of the neural NAND gate, with the modification that we choose 0 to correspond to the True state and a to the False state. This makes the ReLU encoding function equivalent to the direct implementation of a NAND gate.

Repeating the noisy logical neuron analysis of Eq. (16), but now with logical weights  $a_i = 1$  and three decoder neurons, i.e., S = 3, as per the neural NAND gate construction, we find

$$f_{\text{NAND}}(k^*) \sim \mathcal{N}\left(M \cdot \frac{e^{-6\pi^2 \sigma^2} \operatorname{erf}^6(\sqrt{2\pi\sigma})}{2^9 \pi^3 \sigma^6}, \sqrt{M\left(\frac{1}{2} + \sigma^2 - \zeta\right) + \sigma^2}\right),$$

(23)

for

$$\zeta = \frac{e^{-12\pi^2 \sigma^2} \operatorname{erf}^{12} \left(\sqrt{2\pi\sigma}\right) - 4\pi^3 \sigma^6 e^{-24\pi^2 \sigma^2} \operatorname{erf}^6 \left(2\sqrt{2\pi\sigma}\right)}{2^{18} \pi^6 \sigma^{12}} \tag{24}$$

However, Eq. (17) remains unchanged, i.e.

$$f_{\text{NAND}}(k \neq k^*) \sim \mathcal{N}\left(0, \sqrt{M\left(\frac{1}{2} + \sigma^2\right) + \sigma^2}\right).$$

(25)

Repeating a similar analysis to estimate  $\Pr[f_{\text{NAND}}(k^*) < f_{\text{NAND}}(k \neq k^*)]$  yields the number of moduli

$$M(\epsilon) \approx \frac{2^{18} \pi^6 e^{12\pi^2 \sigma^2} \sigma^{12} \left(4\sigma^2 + 1\right) \log\left(\frac{3}{\epsilon}\right)}{\operatorname{erf}^{12} \left(\sqrt{2\pi\sigma}\right)}$$

(26)

$$= \mathcal{O}\left(e^{\beta\sigma^2}\log(1/\epsilon)\right),\tag{27}$$

consistent with the results of Section III C.

To also account for synaptic failure with probability p, we must modify Eqs. (23) and (25) to include the possi-

FIG. 6. (A) Encoding functions  $e(x_k)$  that induce appropriate logical activation functions to implement common Boolean gates. All logical weights  $\{a_i\}$  are set to unity when implementing a Boolean gate. (B) Fault-tolerant neural network implementation of the two-bit multiplication circuit. In the inset, we illustrate the two-bit multiplication circuit decomposed into six AND gates (orange) and two XOR gates (green). In the neural network implementation thereof, two 2-bit binary numbers  $b_0b_1$  and  $b'_0b'_1$  (using the 0 index to denote the least significant bit) are one-hot encoded (as per Eqs. (21) and (22)) as input to the noisy neural network. The output  $c_0c_1c_2c_3$  yields the product of the two numbers, and can achieve arbitrarily small error by increasing the number of moduli (M = 5 moduli illustrated). The grid code corrects Gaussian noise via the decoder (blue lines); neural encoders evaluate AND gates (orange outline) and XOR gates (green outline) to perform computation using appropriate encoder activation functions (shown in  $\mathbf{A}$ ); additional decoders and encoders are used to generate error-corrected copies of neural states (black). (C) Numerical simulation of the number of neurons required to perform two-bit multiplication with logical error probability  $\epsilon$  in the presence of Gaussian noise of variance  $\sigma^2$ . The fit confirms the analytic scaling  $\mathcal{O}(e^{a\sigma^2}N\log(N/\epsilon))$  of Eq. (20).

bility of this discrete mode of noise. While a functional synapse with additive Gaussian noise returns value  $y + \xi$ , a synaptic failure returns value 0. A careful treatment of synaptic failure is provided in Appendix B, the result of which is a new set of distributions  $f'_{\text{NAND}}(k \neq k^*)$  and  $f'_{\text{NAND}}(k = k^*)$  which depend on both the strength of Gaussian errors  $\sigma$  and on the probability of synaptic failures p. As with Eqs. (23) and (25),  $f'_{\text{NAND}}(k \neq k^*)$  is centered at zero with standard deviation  $\mathcal{O}(\sqrt{M})$ , and  $f'_{\text{NAND}}(k = k^*)$  is centered at  $\mathcal{O}(M)$  with standard deviation  $\mathcal{O}(\sqrt{M})$ .

In order to proceed, we must take a more careful treatment of the activation function required for the error correction step of the logical neuron. In a biological discussion of the grid code, winner-take-all dynamics are often used to describe the decoding process [11], i.e., it is assumed that the only neuron activated is that representing the decoded value with the largest signal, as per maximum likelihood decoding approach discussed in Section III A. This decoding approach implicitly assumes communication between the decoding neurons, e.g. through an argmax-type non-linearity. However, for transparency in the treatment of noise, we demonstrate how a local step activation function, parameterized by a cutoff c, can replace winner-take-all dynamics with a simpler decoder.

Because the separation of means of the correct and incorrect decoding distributions scales as  $\mathcal{O}(M)$  compared to their standard deviations which scale as  $\mathcal{O}(\sqrt{M})$ , an appropriate choice of threshold c is sufficient to distinguish between the two distributions with high probability (for large M). Since there are three decoding neurons, a correct decoding requires the correct neuron sampled from  $f'_{\text{NAND}}(k = k^*)$  to exceed c and the two incorrect neurons sampled from  $f'_{\text{NAND}}(k \neq k^*)$  to lie below c. Evaluating such probabilities is straightforward due to  $f'_{\text{NAND}}(k)$ being normally distributed in both cases. The probability that the logical NAND neuron succeeds is given by  $1 - \epsilon(\sigma, p)$ , where  $\epsilon(\sigma, p)$  is an error rate that depends on both the strength of Gaussian errors  $\sigma$  and the probability of synaptic failures p. A more detailed analysis of  $\epsilon(\sigma, p)$ , including its explicit expression, is provided in Appendix B.

To obtain a fault-tolerance threshold from this quantity, we apply the result of Evans and Pippenger [4] for fault-tolerant Boolean formulas built from NAND gates. Evans and Pippenger present a construction for that Boolean formulas built from NAND gates that achieves fault-tolerance if and only if the NAND probability of failure is below  $\epsilon_0 = (3 - \sqrt{7})/4$ . We appeal to this bound to prove fault tolerance of neural NAND gates, which is equivalent to placing the grid code inside the code of Evans and Pippenger. While their NAND construction only considers errors as bit flips – i.e., an error is triggered if a gate that should return 0 returns a 1, and vice versa – errors in the neural NAND gate are biased. This occurs because synaptic failures bias neurons towards zero output; if all neurons fail, the neural NAND defaults to 0. However, biased errors are strictly easier to correct than unbiased errors, and thus the threshold of Evans and Pippenger serves as an appropriate lower bound. To ensure the lower bound is applied correctly, we report the error rate of the neural NAND in a manner that counts zero output forced by synaptic failure as an error.

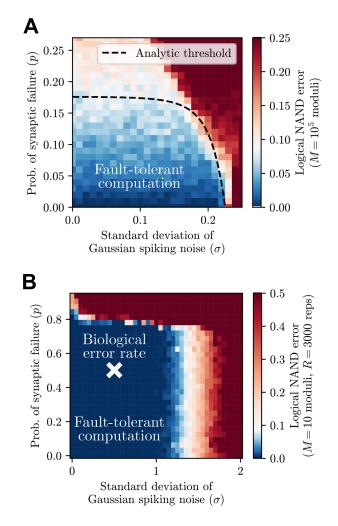

We use both this bound and the expression for  $\epsilon(\sigma, p)$ (see Appendix B) to analytically determine a faulttolerance threshold for p and  $\sigma$  at  $M = 10^5$  moduli. We analytically plot the neural NAND failure probability  $\epsilon(\sigma, p)$  in Fig. 7a, as well as a contour (the dashed line) corresponding to the logical error being equal to the aforementioned threshold  $\epsilon_0 = (3 - \sqrt{7})/4$ . This plot indicates a region of  $\sigma, p$  with logical error  $\epsilon(\sigma, p) < \epsilon_0$ , within which fault-tolerant computation is achievable, and a sharp transition to a region with  $\epsilon(\sigma, p) > \epsilon_0$  in which this fault-tolerant construction does not hold. In aggregate then, by appealing to the universality of the NAND gate, we have that for sufficiently small  $\sigma < \sigma_0$ and  $p < p_0$  (where  $\sigma_0$  and  $p_0$  may be determined by the contour of Fig. 7a), our fault-tolerant neuron may achieve fault-tolerant computation with polylogarithmic overhead, thus achieving neural network fault-tolerance as introduced in Section I.

## C. Concatenating grid code on top of repetition code

Above, we constructed a neural NAND that uses Mmoduli, where each modulus is stored without redundancy. While our constructions above have assumed  $M = 10^5$ , the grid cells in the mammalian cortex contain far fewer moduli, i.e.,  $M \sim 10$  [10]. However, in the biological setting, each modulus is itself encoded redundantly, with  $R \sim 10^3$  to  $10^4$  repetitions of each modulus [10]. This effectively concatenates the grid code on top of a repetition code, which provides another means by which to decrease the strength of the additive Gaussian noise. Roughly speaking, the central limit theorem reduces the variance  $\sigma^2$  to  $\sigma^2/R$ , which can drastically reduce the number of moduli required to suppress noise (Fig. 6c). To move towards a more biologically feasible setting, we examine a concatenation of the grid code on top of a repetition code.

Considering the logical neuron in Fig. 5a, the main modification is to replace each phase with R copies of the phase. Each successive layer then averages over the repetitions of the previous layer, correcting for the synaptic failure probability. For example, consider the neural NAND gate with R copies of the first phase  $\{\theta_{1,i}^{(1)}\}_{i=1}^{R}$  and R copies of the second phase  $\{\theta_{1,i}^{(2)}\}_{i=1}^{R}$ . In the absence of the repetition code, the phase  $\phi_1$  would be computed as  $\phi_1 = \theta_1^{(1)} + \theta_2^{(1)}$  as the neural NAND gate uses logical weights equal to 1. With the repetition code and a

FIG. 7. (A) The logical error of a neural NAND gate using only the grid code. Also plotted is an analytical fault-tolerance threshold corresponding to NAND error probability  $\epsilon_0 \approx 0.09$  required to achieve an arbitrarily low logical error using the optimal NAND fault-tolerance construction of Ref. [4]. The region in blue supports fault-tolerant computation, while the region in red suffers faulty computation. (B) Logical error of a neural implementation of the NAND gate using the grid code ( $M = 10 \mod u$ ) concatenated with a repetition code (R = 3000 repetitions). Notably, the fault-tolerant regime where the error falls below  $\epsilon_0 \approx 0.09$  (blue) encompasses biological error rates (white cross).

synaptic failure probability p, we instead choose

$$\phi_{1,j} = \frac{1}{R} \times \frac{1}{1-p} \sum_{i=1}^{R} \theta_{1,i}^{(1)} + \theta_{1,i}^{(2)}$$

(28)

which may be implemented by selecting weights  $\frac{1}{R} \times \frac{1}{1-p}$ , where the factor  $\frac{1}{1-p}$  accommodates for synaptic failure. This ensures that i.i.d. sampling of the Gaussian noise over R repetitions will reduce the variance from  $\sigma^2$  to  $\sigma^2/R$ .

The only remaining modification is to use a step func-

tion in the encoder to perform a majority vote over repetitions in the final layer. The goal is to ensure that the character of the noise remains the same after decoding. i.e., the noise after error correction should be describable as a combination of logical bit flips and continuous Gaussian noise. As in Section IVA, consider a set of three codewords  $x_1 = 0$ ,  $x_2 = a$ , and  $x_3 = 2a$ , interpreting  $x_1$  as False and  $x_2$  as True. In the previously studied construction where R = 1, the outputs of the error corrected NAND gate corresponding to  $\phi_i$  are simply multiplied by weights  $1/\lambda_j$ ,  $1/\lambda_j$ , and 0 respectively (see Eqs. (21) and (22) and Fig. 6a). In addition to rescaling by  $\frac{1}{1-p}$  to account for synaptic failures, we include an extra discretization step in the encoding stage of error correction (as in Fig. 5a). This is accomplished by choosing  $e(x_k)$  to be a step function in the encoder of Eq. (8). If  $x_1$  is recovered by the decoder, we re-encode  $e(x_1) = 0$ ; and if  $x_2$  is recovered by the decoder, we reencode  $e(x_2) = a/(1-p)$ . Since the weight associated with  $x_3$  is zero, the decoding neuron corresponding to  $x_3$ is not connected to the following layer of neurons.

We conduct numerical experiments on this neural NAND gate with redundantly encoded moduli, using M =10 moduli and  $R = 3 \times 10^3$  repetitions to remain in the biologically relevant regime. As before, errors are biased due to synaptic failure setting neurons to zero; hence, the threshold of Evans and Pippenger places a lower bound on the true threshold of the neural NAND, where zero output incurred by synaptic failure is appropriately counted as a logical error. Since the central limit theorem performs poorly on the small number of moduli M = 10 here, an analytic expression like that for  $\epsilon(\sigma, p)$  (Eq. (B5)) is a poor approximation. Instead, we numerically estimate the threshold as the contour where the logical NAND error crosses the Evans and Pippenger threshold  $\epsilon_0 = (3 - \sqrt{7})/4 \approx 0.09$ . We show results in Fig. 7b, with the threshold contour depicted as the white boundary separating the blue region (which represents fault-tolerant computation) and the red region (which represents faulty computation). This indicates approximate thresholds  $\sigma_0 \approx 1.4$  and  $p_0 \approx 0.7$ . Notably, the fault-tolerant regime encompasses the observed biological error rates (depicted as a white cross) of  $\sigma \approx 0.5$ (given a mean of approximately 0.5, due to random outputs in [0, 1]) and  $p \approx 0.5$  [12–14], thus suggesting that the grid code augmented with a repetition code suffices to enable reliable computation in faulty organisms.

### V. CONCLUDING REMARKS

In this work, we have demonstrated fault-tolerant constructions for neural networks subject to synaptic failure (Section II) and additive Gaussian noise (Section III). While synaptic failure is a digital error and may be treated with a traditional repetition code, Gaussian noise represents an analog error, which we treat using the more sophisticated grid code that emerged from studies of the mammalian cortex. We have further used these constructions to build neural networks that can reliably implement any Boolean formula in the presence of both errors modes (Section IV). In particular, for sufficiently small synaptic failure probability  $p < p_0$  and Gaussian noise standard deviation  $\sigma < \sigma_0$ , our construction enables the computation of arbitrary Boolean formulas (and thus arbitrary computation) with only polylogarithmic overhead, thus achieving neural network fault-tolerance as introduced in Section I. These results ultimately describe a phase transition from faulty neural computation into fault-tolerant neural computation.

Our analyses only place a lower bound on the faulttolerance threshold of neural computation; a more effective neural fault-tolerant construction may be exist. In particular, while the neural network fault-tolerance theorem is phrased in terms of digital Boolean gates composed of analog neurons, the fault-tolerant neural network size requirement of Section III C (Eq. (20)) holds for a general construction of neural networks with Gaussiandistributed weights. This standard form of artificial neural networks provides a more direct analog approach to computation without introducing logical digital gates, and it may ultimately realize a more efficient path towards a threshold for the fault-tolerant phase of neural computation.

Framed against the slowing pace of Moore's Law and increasingly prohibitive energy costs of deep learning [28, 29], the remarkable efficiency of biological computation places central importance on a deep understanding of noisy analog systems. The brain is a canonical example of a noisy analog system that is more energy-efficient than traditional faultless computation. By demonstrating the existence of fault-tolerant neural networks, our work provides a concrete path towards leveraging the favorable properties of such analog neural networks in a neuromorphic setting [30–32]. These results may also find use in novel hardware for machine learning acceleration, such as optical computing [33] and thermodynamic computing [34], which may achieve more resourceefficient computations at the expense of increased error. Our findings are suggestive of the power of naturally occurring error-correcting mechanisms: while the presence of fault-tolerant computation in the brain remains uncertain without experimental verification, we conclude that observed neural error correction codes are theoretically capable of achieving arbitrarily reliable computation.

### ACKNOWLEDGMENTS

AZ acknowledges support from the Hertz Foundation, and the Department of Defense through the National Defense Science and Engineering Graduate Fellowship Program. AKT acknowledges support from the Natural Sciences and Engineering Research Council of Canada (NSERC) [PGSD3-545841-2020]. MT acknowledges support from the Rothberg Family Fund for Cognitive Science. ILC, AKT, and MT acknowledge support in part from the Institute for Artificial Intelligence and Fundamental Interactions (IAIFI) through NSF Grant No. PHY-2019786.

- J. von Neumann, "Probabilistic logics and the synthesis of reliable organisms from unreliable components," in *Automata Studies. (AM-34), Volume 34*, edited by C. E. Shannon and J. McCarthy (Princeton University Press, 2016) pp. 43–98.

- [2] N. Pippenger, 26th Annual Symposium on Foundations of Computer Science (SFCS 1985), 30 (1985).

- [3] B. Hajek and T. Weller, IEEE Transactions on Information Theory 37, 388 (1991).

- [4] W. Evans and N. Pippenger, IEEE Transactions on Information Theory 44 (1998), 10.1109/18.669417.

- [5] W. Evans and L. Schulman, IEEE Transactions on Information Theory 45, 2367 (1999).

- [6] J. Gao, Y. Qi, and J. Fortes, IEEE Transactions on Nanotechnology 4, 395 (2005).

- [7] P. Shor, in Proceedings of 37th Conference on Foundations of Computer Science (1996) pp. 56–65.

- [8] C. Torres-Huitzil and B. Girau, IEEE Access 5, 17322 (2017).

- [9] T. Hafting, M. Fyhn, S. Molden, M.-B. Moser, and E. I. Moser, Nature 436, 801 (2005).

- [10] I. R. Fiete, Y. Burak, and T. Brookings, Journal of Neuroscience 28, 6858 (2008).

- [11] S. Sreenivasan and I. Fiete, Nature Neuroscience 14, 1330 (2011).

- [12] C. F. Stevens and Y. Wang, Nature **371**, 704 (1994).

- [13] N. A. Hessler, A. M. Shirke, and R. Malinow, Nature 366, 569 (1993).

- [14] W. Softky and C. Koch, Journal of Neuroscience 13, 334 (1993).

- [15] W. S. McCulloch and W. Pitts, The Bulletin of Mathematical Biophysics 5, 115 (1943).

- [16] K. Hornik, M. Stinchcombe, and H. White, Neural Networks 2, 359 (1989).

- [17] Y. LeCun, Y. Bengio, and G. Hinton, Nature **521**, 436 (2015).

- [18] C. Neti, M. Schneider, and E. Young, IEEE Transactions on Neural Networks 3, 14 (1992).

- [19] E. M. El Mhamdi and R. Guerraoui, in 2017 IEEE International Parallel and Distributed Processing Symposium (IPDPS) (2017) pp. 1028–1037.

- [20] T. Liu, W. Wen, L. Jiang, Y. Wang, C. Yang, and G. Quan, in 2019 56th ACM/IEEE Design Automation Conference (DAC) (2019) pp. 1–6.

- [21] C. Sequin and R. Clay, in 1990 IJCNN International Joint Conference on Neural Networks (1990) pp. 703– 708 vol.1.

- [22] U. Ruckert, I. Kreuzer, V. Tryba, and K. Goser, in *Proceedings. VLSI and Computer Peripherals. COMPEURO* 89 (1989) pp. 1/52–1/55.

- [23] J. von Neumann, Automata Studies **34**, 43 (1956).

- [24] W. Evans and L. Schulman, IEEE Transactions on Information Theory 49, 3094 (2003).

- [25] S. Winograd and J. D. Cowan, *Reliable Computation in the Presence of Noise* (MIT Press Cambridge, Mass., 1963).

- [26] M. A. Nielsen and I. L. Chuang, Quantum computation

and quantum information (Cambridge university press, 2010).

- [27] T. Goblick, IEEE Transactions on Information Theory 11, 558 (1965).

- [28] T. Brown, B. Mann, N. Ryder, M. Subbiah, J. D. Kaplan, et al., in Advances in Neural Information Processing Systems, Vol. 33, edited by H. Larochelle, M. Ranzato, R. Hadsell, M. Balcan, and H. Lin (Curran Associates, Inc., 2020) pp. 1877–1901.

- [29] J. Jumper, R. Evans, A. Pritzel, et al., Nature 596, 583 (2021).

- [30] G. Indiveri, B. Linares-Barranco, T. Hamilton, A. van Schaik, R. Etienne-Cummings, *et al.*, Frontiers in Neuroscience 5, 73 (2011).

- [31] S. K. Esser, P. A. Merolla, J. V. Arthur, A. S. Cassidy, R. Appuswamy, *et al.*, Proceedings of the National Academy of Sciences **113**, 11441 (2016).

- [32] Z. Wang, S. Joshi, S. Savel'ev, W. Song, R. Midya, et al., Nature Electronics 1, 137 (2018).

- [33] P. L. McMahon, Nature Reviews Physics 5, 717–734 (2023).

- [34] T. Conte, E. DeBenedictis, N. Ganesh, T. Hylton, J. P. Strachan, et al., "Thermodynamic computing," (2019), arXiv:1911.01968 [cs.CY].

## Appendix A: Comparison of repetition for discrete versus analog fault-tolerance

While the repetition code is sufficient to arrive at digital fault-tolerance when subject to digital errors, such as bit flips or synaptic failure, it is insufficient for analog computation in the presence of additive Gaussian noise. Key to this is the  $\mathcal{O}(\text{polylog}(1/\epsilon))$  scaling with respect to the desired output error rate  $\epsilon$  in the definition of faulttolerance. For Boolean (and more generally discrete) random variables, suffering from i.i.d. bit-flip errors at a rate p < 1/2, a repetition code of size M reduces errors exponentially as  $\sim p^M$ . Given a target error rate  $\epsilon$ , it is sufficient to choose

$$M \sim \frac{\log \frac{1}{\epsilon}}{\log \frac{1}{p}}.$$

(A1)

For a circuit of N gates, an overall error of  $\epsilon$  could be achieved by demanding individual gate errors  $\epsilon/N$  as per the union bound. Inserting this desired error rate into Eq. (A1), and using results of the concatenation scheme described in Section II A, we find that this translates to the desired  $\mathcal{O}(N\text{polylog}(N/\epsilon))$  scaling in the definition of fault-tolerance, so long as the error rate is below a threshold  $p_0$  that is dependent on the details of the error correcting circuit.

For analog variables, the repetition code does not suppress errors strongly enough to achieve this scaling. For additive Gaussian noise with standard deviation  $\sigma$ , a repetition code of size M suppresses errors not exponentially in M, but only as  $\sim \sigma/\sqrt{M}$ . For a target standard deviation  $\epsilon$ , the code size is required to scale as

$$M \sim \left(\frac{\sigma}{\epsilon}\right)^2$$

. (A2)

Analog computation using the repetition code would require an asymptotic lower bound of  $\Omega(\text{poly}(1/\epsilon))$  resources, and thus does not meet our definition of faulttolerance. In order to achieve analog fault-tolerance, we must make use of a stronger error correction code, such as the grid code utilized in this work.

## Appendix B: Detailed analysis of reliability in the presence of Gaussian noise and synaptic failure

In this Appendix, we expand on the analysis in Section IV B for the fully general case that takes into account both Gaussian errors and synaptic failure.

With the analysis for Gaussian failures worked out in Section IV A, we proceed to consider the effect of synaptic failure for each possible type of synapse in the logical neuron of Fig. 5a. The goal is to find an upper bound on the probability that the logical NAND fails, corresponding to a lower bound on the threshold for synaptic failure.

First, considering the synapses from the decoder neurons  $x_i$  to the new logical phases  $\phi'_i$  (i.e., the final layer of

Fig. 5a), a failed synapse may originate from the correct decoder neuron or an incorrect decoder neuron. We ignore the failed synapse from an incorrect decoding, consistent with upper-bounding the failure probability. If the correct decoding fails, the encoded phase may not fire. In the application of logical weights to the logical phase of the next neuron (i.e., the first layer of Fig. 5a), the synapse with a logical weight  $a_i$  may similarly fail. The two phenomena of a correct decoder synapse failing and a logical weight synapse failing produce the same outcome: an input phase  $\theta_i^{(1,2)}$  may fail. The effect of only a single input phase (e.g.  $\theta_i^{(1)}$ ) failing is different from the effect of both input phases failing (i.e.,  $\theta_i^{(1)}$  and  $\theta_i^{(2)}$ ). If one input phase fails, the logical phase  $\phi_i$  assumes a uniformly random value from 0 to 1. This has no impact on  $f_{\text{NAND}}(k \neq k^*)$ , but it reduces the mean of  $f_{\text{NAND}}(k = k^*)$  by removing one of the moduli and requires adjustment of the standard deviation by the inclusion of a random phase. If both input phases fail, the logical phase does not fire. Hence, one of the moduli is removed from both  $f_{\text{NAND}}(k \neq k^*)$  and  $f_{\text{NAND}}(k = k^*)$ . In total, 4Mp(1-p) single input phases are expected to fail and  $2Mp^2$  double input phases are expected to fail.

Next, consider the synapses into and out of the  $\sin 2\pi\phi_i$ and  $\cos 2\pi\phi_i$  neurons. Here, we also find two cases: if there is a failure of a single sine or cosine, the original distribution must be compensated by the remaining sine or cosine of the phase; if there is a failure of both, the modulus is removed entirely. In expectation, 2Mp(1-p)failures are expected for the former effect (for each of sine and cosine), and  $2Mp^2$  failures are expected for the latter. By adding each of the failure modes independently, we place an upper bound on logical failure due to double-counting failures that happen sequentially in the network.

To obtain  $f'_{\text{NAND}}(k \neq k^*)$  and  $f'_{\text{NAND}}(k = k^*)$ , we repeat the noisy logical neuron analysis of Eqs. (16) and (17) for the neural NAND construction including possibility of synaptic failure detailed above. We make the same assumptions as for Eqs. (23) and (25), namely logical weights  $a_i = 1$  and S = 3 decoder neurons as per the neural NAND gate construction. Assuming a large number of moduli  $M \gg 1$  and applying the central limit theorem, we obtain

$$\begin{aligned} f_{\text{NAND}}'(k = k^*) &= \\ \mathcal{N}\bigg(M \cdot \frac{e^{-6\pi^2 \sigma^2} \operatorname{erf} \left(\sqrt{2\pi\sigma}\right)^6}{2^9 \pi^3 \sigma^6} \cdot (2(p-3)p+1), \\ \sqrt{\sigma^2 - \frac{1}{2}M((2p(p+1)-1)(2\sigma^2+1)-\zeta')}}\bigg), \end{aligned}$$

(B1)

where

$$\zeta' = 2^{-18} \pi^{-6} \sigma^{-12} \left[ (p(3p-7)+1) e^{-24\pi^2 \sigma^2} \times \left( e^{12\pi^2 \sigma^2} \operatorname{erf} \left( \sqrt{2}\pi \sigma \right)^{12} - 4\pi^3 \sigma^6 \operatorname{erf} \left( 2\sqrt{2}\pi \sigma \right)^6 \right) \right],$$

(B2)

and

$$\begin{split} f'_{\text{NAND}}(k \neq k^*) &= \mathcal{N}\bigg(0, \\ & \sqrt{\sigma^2 - \frac{1}{2}M(2p(p+1) - 1)\left(2\sigma^2 + 1\right)}\bigg). \end{split} \label{eq:NAND} \end{split}$$

(B3)

Given Eqs. (B1) and (B3), we may evaluate the probability of successful decoding. As explained in Section IV B, we use a threshold non-linearity for decoding which is more biologically plausible than the alternative winner-take-all dynamics due to its locality. Choosing a threshold value of c, a correct decoding then requires the correct neuron sampled from  $f'_{\text{NAND}}(k = k^*)$  (Eq. (B1)) to exceed c and the two incorrect neurons sampled from  $f'_{\text{NAND}}(k \neq k^*)$  (Eq. (B3)) to lie below c, i.e.

$$1 - \epsilon(c; \sigma, p) := \Pr[f'_{\text{NAND}}(k = k^*) > c] \times \Pr[f'_{\text{NAND}}(k \neq k^*) < c]^2.$$

(B4)

Evaluated explicitly, we have