#

N.N. Orlova,<sup>1</sup> A.V. Timonina,<sup>1</sup> N.N. Kolesnikov,<sup>1</sup> and E.V. Deviatov<sup>1</sup>

<sup>1</sup>Institute of Solid State Physics of the Russian Academy of Sciences,

Chernogolovka, Moscow District, 2 Academician Ossipyan str., 142432 Russia

(Dated: April 5, 2022)

The concept of a polar metal proposes new approach of current-induced polarization control for ferroelectrics. We fabricate  $SnSe/WTe_2$  heterostructure to experimentally investigate charge transport between two ferroelectric van der Waals materials with different polarization directions. WTe<sub>2</sub> is a polar metal with out-of-plane ferroelectric polarization, while SnSe ferroelectric semiconductor is polarized in-plane, so one should expect complicated polarization structure at the  $SnSe/WTe_2$ interface. We study dI/dV(V) curves, which demonstrate sharp symmetric drop to zero dI/dV differential conductance at some threshold bias voltages  $\pm V_{th}$ , which are nearly symmetric in respect to the bias sign. While the gate electric field is too small to noticeably affect the carrier concentration, the positive and negative threshold positions are sensitive to the gate voltage. Also,  $SnSe/WTe_2$ heterostructure shows re-entrant transition to the low-conductive dI/dV = 0 state for abrupt change of the bias voltage even below the threshold values. This behavior can not be observed for single SnSe or WTe<sub>2</sub> flakes, so we interpret it as a result of the SnSe/WTe<sub>2</sub> interface coupling. In this case, some threshold value of the electric field at the  $SnSe/WTe_2$  interface is enough to drive  $90^{\circ}$ change of the initial SnSe in-plane polarization in the overlap region. The polarization mismatch leads to the significant interface resistance contribution, analogously to the scattering of the charge carriers on the domain walls. Thus, we demonstrate polarization state control by electron transport through the SnSe/WTe<sub>2</sub> interface.

#### INTRODUCTION

Recently, ferroelectric van der Waals materials attract significant interest both for the fundamental physics and for promising applications in quantum sensors, new memory devices, and for the ferroelectric field-effect transistors [1–4]. For the fundamental research, some of these materials represent a novel concept of the intrinsic polar metal [5–9]. The latter can be regarded as a ferroelectric in metals, it is characterized by intrinsic conduction and inversion symmetry breaking [5].

Due to the finite conductance in polar metals, they propose new approaches to control ferroelectric polarization. For example, it is possible to control polarization by charge current or, vice versa, to control charge transport by the ferroelectric polarization. Out-of-plane polarization can be affected or even switched in well conducting semimetals MoTe<sub>2</sub> and WTe<sub>2</sub> by piezoresponse force microscopy (PFM) [10, 11]. Also, the initial in-plane polarization can be managed in SnSe and SnTe semiconductors using scanning tunneling microscope (STM) technique [12, 13]. Manipulation of charge transport by ferroelectric polarization is important for ferroelectric fieldeffect transistors (FeFET), as it has been demonstrated for In<sub>2</sub>Se<sub>3</sub>-based structures [2]. Ferroelectric polarization can be controlled also by the in-plane current-induced electric field in  $WTe_2$  and SnSe thin films [14–16]. Van der Waals materials also offer strain control of ferroelectric polarization [17].

In the sense of the ferroelectric polarization control, it is quite natural to consider also van der Waals heterostructures with one or several ferroelectric materials and (possibly) some other layers. For example,  $MoS_2/h$ - $BN/graphene/CuInP_2S_6$  heterostructure has been proposed for long-retention memory [18], while GeSe/MoS\_2 heterojunction represents novel FeFET realization [19]. For the heterostructures with polar metals, theory predicts [5] realization of multiple states with different relative directions of polar displacements due to the interface coupling effects. If both the ferroelectric materials are conducting, like for WTe<sub>2</sub> and SnSe, the interface coupling, and, therefore, the polarization state, could be supposed to be controlled directly by electron transport through the heterostructure.

Here, we fabricate SnSe/WTe<sub>2</sub> heterostructure to experimentally investigate charge transport between two ferroelectric van der Waals materials with different polarization directions. WTe<sub>2</sub> is a polar metal with out-ofplane ferroelectric polarization, while SnSe ferroelectric semiconductor is polarized in-plane, so one should expect complicated polarization structure at the  $SnSe/WTe_2$  interface. We study dI/dV(V) curves, which demonstrate sharp symmetric drop to zero dI/dV differential conductance at some threshold bias voltages  $\pm V_{th}$ , which are nearly symmetric in respect to the bias sign. While the gate electric field is too small to noticeably affect the carrier concentration, the positive and negative threshold positions are sensitive to the gate voltage. Also, SnSe/WTe<sub>2</sub> heterostructure shows re-entrant transition to the low-conductive dI/dV = 0 state for abrupt change of the bias voltage even below the threshold values. This behavior can not be observed for single SnSe or WTe<sub>2</sub> flakes, so we interpret it as a result of the  $SnSe/WTe_2$

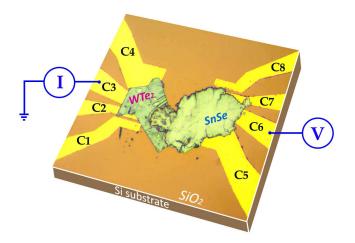

Figure 1. (Color online) Optical image of the WTe<sub>2</sub>/SnSe sample with electrical connections. 100 nm thick Au leads pattern is formed on a top of the standard oxidized silicon wafer. Thin WTe<sub>2</sub> flake is placed above the left group of the Au leads (C1-C4), then SnSe flake is situated to overlap both the  $WTe_2$  flake and the right leads (C5–C8). The Au leads outline can be seen under the flakes, so they are below 200 nm thickness. The right and the left leads are separated by 80  $\mu$ m interval, the flakes are about the same lateral size. Red dashed line denotes the WTe<sub>2</sub>/SnSe overlap region ( $\approx 40 \mu m \times 20 \mu m$ ), which is highly stable even for longperiod measurements. We study electron transport across the SnSe/WTe<sub>2</sub> interface (about 200 kOhm resistance value) in a two-point technique by applying voltage V to the contact C6 in respect to the C3 one, and measuring the current I in the circuit. Gate voltage can be applied to the silicon substrate.

interface coupling. In this case, some threshold value of the electric field at the  $SnSe/WTe_2$  interface is enough to drive 90° change of the initial SnSe in-plane polarization in the overlap region. The polarization mismatch leads to the significant interface resistance contribution, analogously to the scattering of the charge carriers on the domain walls.

## SAMPLES AND TECHNIQUES

WTe<sub>2</sub> is usually considered as a Weyl semimetal [20, 21], while now it is also an example of a polar metal with out-of-plane ferroelectric polarization [11]. The polarization is observed even for three-dimensional crystal due to broken inversion symmetry for Td crystal structure [22, 23]. SnSe is a semiconductor, the in-plane ferroelectric polarization appears [24] due to the distortion of centrosymmetric *Pnma* orthorhombic structure at low thicknesses [12]. The critical thickness can be estimated [25] as 300 nm for SnSe.

For the present experiment, SnSe compound was synthesized by reaction of selenium vapors with the melt of high-purity tin in evacuated silica ampules. The SnSe layered single crystal was grown by vertical zone melting in silica crucibles under argon pressure. WTe<sub>2</sub> compound was synthesized from elements by reaction of metal with tellurium vapor in the sealed silica ampule. The WTe<sub>2</sub> crystals were grown by the two-stage iodine transport [26]. Ultra-thin SnSe and WTe<sub>2</sub> flakes (about 100-200 nm) are obtained by regular mechanical exfoliation from the initial layered ingot. Thin single-crystal flakes of these materials have been well characterized in transport investigations [14–16, 27, 28].

We assemble  $SnSe/WTe_2$  heterostructure on the predefined Au leads pattern to avoid chemical or thermal treatment of the initial materials, similarly to singleflake samples [15, 16, 27–29]. 5  $\mu$ m separated leads are formed on the standard SiO<sub>2</sub> substrate by lift-off technique after thermal evaporation of 100 nm Au. To obtain separate contacts to the individual layers, thin SnSe and WTe<sub>2</sub> flakes are placed on two independent contact groups (the left and the right ones in Fig. 1), so Au-SnSe or Au-WTe<sub>2</sub> junctions are formed at the bottom surfaces of the individual flakes. This procedure provides electrically stable contacts with highly transparent metal-semiconductor interfaces, which has been verified for the individual flakes [15, 16, 27–29].  $SnSe/WTe_2$  heterostructure appears as a small  $(40 \ \mu m \times 20 \mu m))$  overlap of the flakes at the center of the structure in Fig. 1. Despite the apparent simplicity of the heterostructure fabrication, the samples are stable even for long-period measurements, the observed behavior can be well reproduced for different samples, as it is demonstrated below. Also,  $SiO_2$  substrate protects the flakes from any oxidation/contamination [29], so all measurements are taken at room temperature under ambient conditions.

The prepared heterostructure allows to measure electron transport across  $SnSe/WTe_2$  interface. In the case of high resistance samples, one have to use two-point technique with direct application of the voltage bias V to one of the left contacts in Fig. 1 in respect to one of the right contacts. We analyze differential conductance dI/dV behavior in dependence on the dc voltage bias. To obtain dI/dV(V) curves, the applied dc bias V is additionally modulated by a small (10 mV) ac component at about 1 kHz frequency. The ac current component is measured by lock-in, being proportional to differential conductance dI/dV at a given dc bias value. We verify that the obtained dI/dV(V) curves are independent of the modulation frequency in the range 1 kHz-10 kHz, which is determined by applied filters. Also, standard oxidized silicon substrate allows to apply the gate voltage  $V_g$  to the p-doped silicon across the 100 nm oxide layer. Even for relatively thick (100-200 nm) flakes, ferroelectric polarization is sensitive to the gate electric field [14], since the relevant (bottom) flake surfaces are adjoined to the  $SiO_2$  surface.

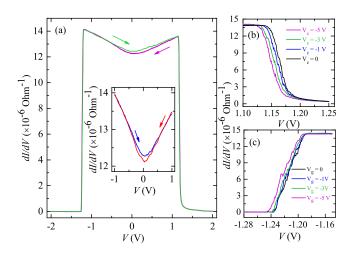

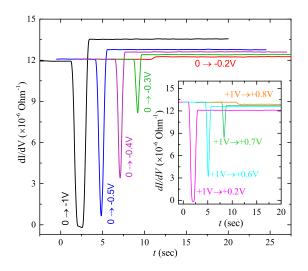

Figure 2. (Color online) (a) Examples of dI/dV(V) curves for two dc bias V sweep directions. The curves demonstrate abrupt symmetric drop to zero differential conductance at  $V_{th} \approx \pm 1.2$  V bias values. This dI/dV drop shows no hysteresis, so  $V_{th}$  does not depend on the voltage sweep direction. Inset shows an enlarged low-bias region with small hysteresis around the zero bias, which is known for the individual WTe<sub>2</sub> or SnSe flakes [14–16]. (b,c) Gate voltage dependence of the dI/dV(V) regions near positive and the negative thresholds. Negative gate voltages decrease the positive  $V_{th}$  value and simultaneously increase the negative one. In contrast, the gate electric field does not noticeably change the dI/dV conductance below the threshold, so the carrier concentration is nearly constant for the applied gate voltages. There is no gate leakage in the present gate voltage range.

# EXPERIMENTAL RESULTS

dI/dV(V) behavior is shown in Fig. 2 (a) for two dc bias V sweep directions for one of the SnSe/WTe<sub>2</sub> heterostructures. At low biases (below ±1.2 V), dI/dV(V)behavior is nonlinear with small hysteresis around the zero bias. This low-bias region is enlarged in the inset to Fig. 2 (a), both the hysteresis and dI/dV(V) behavior are known to originate from ferroelectric polarization for the individual WTe<sub>2</sub> and SnSe flakes [14–16].

For the SnSe/WTe<sub>2</sub> heterostructure, our main finding is the abrupt symmetric dI/dV conductance drop at high biases, which can not be observed for the individual SnSe or WTe<sub>2</sub> flakes [14–16]. In Fig. 2 (a), dI/dV(V) curves demonstrate a drop to zero conductance at  $V_{th} \approx \pm 1.2$  V bias values. This dI/dV conductance drop shows practically no hysteresis, so dI/dV is abruptly changed at the same threshold voltage value  $V_{th}$ , irrespectively to the voltage sweep direction. Also,  $V_{th}$  value is well reproducible in different voltage sweeps, it is unique for a particular sample:  $V_{th}$  value is inversely proportional to the zero-bias conductance (see below the description of Fig. 4).

The threshold position can be affected by the gate volt-

age, see Figs. 2 (b) and (c). Negative gate voltages decrease the  $V_{th}$  value for positive biases and simultaneously increase it for the negative one, so the dI/dV(V) curve is shifted monotonously to negative biases. The effect is well-noticeable, it is about 4% of the  $V_{th}$  value. In contrast, the gate electric field does not change the dI/dV conductance below the threshold, so the carrier concentration is constant for the applied gate voltages. We check, that there is no gate leakage in the present gate voltage range.

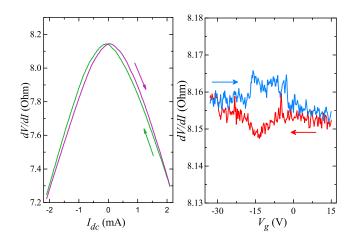

For a single SnSe or WTe<sub>2</sub> flake, the low-bias hysteresis reflects slow relaxation processes due to the additional polarization current in conductive ferroelectrics [14–16]. Fig. 3 shows this behavior for the individual WTe<sub>2</sub> layer. Even well-conducting WTe<sub>2</sub> single crystals demonstrate ferroelectricity at room temperature, which has been shown by direct visualization of ferroelectric domains [11]. In our setup, there are two possible directions of the external electric fields in the WTe<sub>2</sub> layer, the result is depicted in Fig. 3: (a) the source-drain field  $E_{sd} = \rho j$ , which is connected with the flowing current,  $E_{sd}$  is parallel to the WTe<sub>2</sub> surface; (b) The gate field,  $E_{gate} = V_g/d$ , where d = 300 nm is the SiO<sub>2</sub> oxide thickness,  $E_g$  is directed normally to the WTe<sub>2</sub> surface. Any variation of electric fields leads to the additional polarization current.

In the latter case we observe a standard Sawyer-Tower ferroelectric polarization loop [30, 31], similarly to the polarization change by high external electric field in Ref. [11]. The loop center is slightly shifted in Fig. 3 (b) due to the band bending at the gate dielectric interface. In the former case, source-drain field variation leads to the hysteresis of the same magnitude in Fig. 3 (a). Similar results can be obtained for the individual SnSe layer [15, 16].

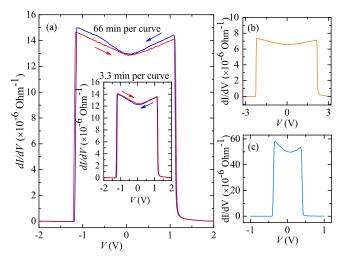

We also confirm the hysteresis sweep-rate dependence for low biases in Fig. 4 (a), but the threshold values  $V_{th} \approx \pm 1.2$  V are well stable for different rates, low hysteresis can be seen around  $V_{th} \approx \pm 1.2$  V position only for the highest sweep rate in the inset to Fig. 4 (a).

Qualitatively, similar dI/dV(V) behavior can be demonstrated for SnSe/WTe<sub>2</sub> heterostructures with strongly different initial conductance, see Fig. 4 (b) and (c). The threshold  $V_{th}$  positions are also symmetric, while the  $V_{th}$  values are different in the figure:  $V_{th}$  is inversely proportional to the zero-bias conductance for all three samples in Fig. 4, which implies constant threshold source-drain electric field, see the discussion below.

To our surprise, SnSe/WTe<sub>2</sub> heterostructure shows reentrant transition to zero-conductance state even at low biases  $V < V_{th}$ , by abrupt change of the bias value  $\Delta V$ , as it is shown in Fig. 5. Let us start from V = 0, as depicted in the main field of Fig. 5. For low  $\Delta V < 0.2$  V, dI/dV is monotonously increased in exact correspondence with the dI/dV(V) curve from Fig. 2 (a), the slow relaxation is insignificant for the scales in Fig. 5. For  $\Delta V > 0.3$  V, this increase goes through the initial

Figure 3. (Color online) (a) dV/dI(I) curves for the individual WTe<sub>2</sub> layer. Source-drain field variation leads to the additional polarization current in WTe<sub>2</sub> conductive ferroelectric [11], which appears as sweep direction dependence in dV/dI(I) curves. (b) Hysteresis of the same magnitude in the gate voltage dependence, which is a standard Sawyer-Tower ferroelectric polarization loop [30, 31], similarly to the polarization change by high external electric field in Ref. [11]. The loop center is slightly shifted due to the band bending at the gate dielectric interface.

dI/dV drop. The drop value grows with  $\Delta V$ , so differential conductance goes through the dI/dV = 0 region for  $\Delta V > 0.5$  V. This behavior does not depend on the initial bias  $V < V_{th}$  or the sign of the bias change  $\Delta V$ , as it is demonstrated in the inset to Fig. 5. Thus, the abrupt change of the bias voltage V leads to re-entrant switching to zero conductance at low biases  $V < V_{th}$ , while the zero-conductance dI/dV state is stable at high biases  $V > V_{th}$ .

#### DISCUSSION

As a result,  $\text{SnSe}/\text{WTe}_2$  heterostructure demonstrates sharp symmetric drop to zero dI/dV differential conductance at some threshold bias voltage  $V_{th}$ , which is sensitive to the gate voltage. Moreover,  $\text{SnSe}/\text{WTe}_2$ heterostructure shows re-entrant transition to the lowconductive state for abrupt change of the bias voltage even below the threshold. This behavior is well reproducible for different  $\text{SnSe}/\text{WTe}_2$  samples, while it can not be observed for single SnSe or WTe<sub>2</sub> flakes [14–16].

First of all, we should exclude sample overheating by the flowing current as the origin of the observed effects. WTe<sub>2</sub> crystal structure (Td) is known to be stable in a wide temperature range at ambient pressure [22, 23]. The martensitic phase transition is known [32] for SnSe at  $\approx$ 480-530° C, but it is necessarily accompanies by the prominent hysteresis of the transition point [16, 33],

Figure 4. (Color online) (a) dI/dV(V) curves for different sweep rates (66 minutes per a curve for the main field and 3.3 minutes for the inset) for the same sample as in Fig. 2, where it takes 10 minutes per a curve. The low-bias hysteresis is sensitive to the sweep rate, as it is expected for a single SnSe flake [15, 16]. However, the threshold values  $V_{th} \approx \pm 1.2$  V are well stable for different rates. (b,c) Similar dI/dV(V) curves for two other SnSe/WTe<sub>2</sub> heterostructures with strongly different initial (zero-bias) conductance values. The curves are symmetric, but  $V_{th}$  value is unique for a particular sample.

which is just opposite to the dI/dV(V) behavior in Figs. 2 and 4. Also, temperature-induced phase transition is inconsistent with the re-entrant transition to the low-conductive state in Fig. 5.

Also, any band bending/reconstruction effects at the interface should be strongly asymmetric in respect to the bias sign, while experimental dI/dV(V) curves are highly symmetric in Figs. 2 and 4, so any possible influence of the band bending/reconstruction effects is within the small difference between the positive and negative thresholds in Fig. 2 (b) and (c). It can be estimated as about 0.05 V, the gate voltage effect is of the same value. We can not expect significant band bending for the well-conducting WTe2 and SnSe materials.

It is important, that low-bias dV/dI(I) behavior reflects polarization dynamics in conductive ferroelectirics [14–16] in Figs. 2, 3, and 4. Thus, it is quite reasonable to ascribe the observed high-bias behavior to the interface coupling of the ferroelectric polarizations at the SnSe/WTe<sub>2</sub> interface, as it was predicted in Ref. [5]. WTe<sub>2</sub> is characterized by semimetal spectrum [20, 21] with out-of-plane ferroelectric polarization [11], so it is a good representation of the polar metal concept [5–9]. SnSe thin flake is a ferroelectric semiconductor with inplane polarization, while the SnSe conductivity is significant at room temperature [25]. Thus, SnSe/WTe<sub>2</sub> bilayer can be considered as a heterostructure between two conducting ferroelectrics with different polarization

Figure 5. Re-entrant transition to the low-conductive state for abrupt change of the bias voltage  $\Delta V$  for  $V < V_{th}$ . For low  $\Delta V < 0.2$  V, dI/dV(t) shows monotonous increase in exact correspondence with the dI/dV(V) dependence from Fig. 2 (a), the slow relaxation is insignificant for the present scales. For  $\Delta V > 0.3$  V values, this increase goes through the preliminary dI/dV drop. The drop value grows with  $\Delta V$ , so dI/dV goes through the dI/dV = 0 region for  $\Delta V > 0.5$  V. Inset shows similar behavior for another bias V and the sign of the bias change  $\Delta V$ . Time-dependent dI/dV(t) curves are shifted horizontally for clarity, so the starting point of the bias change coincides with the beginning of the dI/dV drop

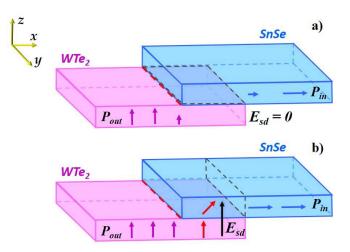

directions [5], as it is schematically depicted in Fig 6 (a).

Due to the interface coupling, one can expect complicated polarization structure at the  $SnSe/WTe_2$  interface: polarization should be continuously rotated within the overlap region [5]. However,  $WTe_2$  is characterized by high in-plane conductance [20, 21], which should efficiently screen the in-plane electric field component both in  $WTe_2$  and SnSe layers due to the proximity effect. Thus, for the macroscopic-size SnSe/WTe<sub>2</sub> overlap region (depicted by black dashed rectangular in Fig 6 (a), area is about 40  $\mu$ m×20 $\mu$ m), one should expect zero (or strongly diminished) ferroelectric polarizations both in  $WTe_2$  and SnSe layers, as it is shown in Fig 6 (a), so the polarization mismatch has low (or even zero) influence on the sample resistance. This conclusion is also supported by low-bias measurements. In our samples, the total resistance (e.g., between C3 and C6 in Fig. 1) consists of the in-series connected resistances of the  $SnSe/WTe_2$  interface and the resistances of the SnSe and  $WTe_2$  layers. The individual WTe<sub>2</sub> flake is of 10 - 100 Ohm resistance [14] (e.g. as measured between C3 and C4 contacts), the single SnSe layer is characterized by 50 - 200 kOhm values between C5 and C6, so there is no observable interface contribution. Low variation of the source-drain bias leads to the additional polarization current in the bulk SnSe  $(\rho_{SnSe} >> \rho_{WTe_2})$ , which we observe [14–16] as low-bias hysteresis in Fig. 2.

Figure 6. Schematic diagram for the ferroelectric polarization at the  $SnSe/WTe_2$  interface.  $WTe_2$  is characterized by out-of-plane ferroelectric polarization [11]  $P_{out}$ , while it is inplane oriented  $(P_{in})$  in SnSe thin flakes [25]. (a) At zero bias, polarization should be continuously rotated within the overlap region, depicted by the black dashed rectangular. However,  $WTe_2$  is characterized by high in-plane conductance [20, 21], which should efficiently screen the in-plane electric field component both in  $WTe_2$  and SnSe layers due to the proximity effect. Thus, for the macroscopic-size SnSe/WTe<sub>2</sub> overlap region, one should expect zero (or strongly diminished) ferroelectric polarizations both in  $WTe_2$  and SnSe layers. (b) At high biases, current-induced electric field  $E_{sd}$  enhances the out-of-plane polarization in the WTe<sub>2</sub> layer, and, due to the interface coupling [5], it should secondly switch the polarization out-of-plane also in the adjacent SnSe region at some threshold  $E_{sd}$  field. The planar contact (about 40  $\mu$ m×20 $\mu$ m) with zero polarization is transformed into the side junction  $(\approx 40 \mu \text{m} \times 100 \text{ nm})$  with strong polarization mismatch. The latter leads to the significant interface resistance contribution, which we observe as the strong conductivity drop.

To understand the high-bias switching, it is important that current-induced electric field  $E_{sd}$  is oriented normally to the SnSe/WTe<sub>2</sub> interface due to the high WTe<sub>2</sub> in-plane conductance. It enhances the out-of-plane polarization in the  $WTe_2$  layer, and, due to the interface coupling [5], it should secondly switch the polarization out-of-plane also in the adjacent SnSe region at some threshold  $E_{sd}$  field. The latter can be estimated from the experimental  $V_{th}$  values as  $E_{sd} \sim V_{th} \approx 10^4 - 10^5 \text{ V/m}.$ In this case, the planar contact (depicted by black dashed rectangular in Fig 6 (a), area is about 40  $\mu m \times 20 \mu m$ ) is transformed into the side junction in Fig 6 (b) with  $\approx 40 \mu \text{m} \times 100 \text{ nm}$  area. The polarization mismatch leads to the significant interface resistance contribution, analogously to the scattering of the charge carriers on the domain walls [34].

This effect is not sensitive to the bias sign, since both  $E_{sd}$  directions at the interface can drive 90° change of the initial SnSe in-plane polarization [5]. Similarly to

$E_{sd}$ , the gate electric field  $E_g$  is directed normally to the SnSe/WTe<sub>2</sub> interface. Thus, it increases the interface field for one  $E_{sd}$  direction and decreases it for the opposite one, as we observe in Fig. 2 (b,c). The proposed model is also confirmed by the excellent stability of the threshold regions in the experimental curves, see Figs. 2, and 4. Any contact or scattering effects should demonstrate random fluctuations from sample to sample. In contrast,  $V_{th}$  is inversely proportional to the zero-bias conductance for three different samples in Fig. 4, which implies constant, device-independent, threshold electric field  $E_{sd}$ .

The above picture is also confirmed by the timedependent curves in Fig. 5. At constant bias V, the WTe<sub>2</sub> flake is nearly equipotential because of low resistivity  $\rho_{WTe_2} \ll \rho_{SnSe}$ . Thus, the abrupt change in the bias  $\Delta V$  is applied initially at the SnSe/WTe<sub>2</sub> interface, while it is redistributed afterwards over the resistive SnSe flake. It, therefore, temporary forces the transition to the low-conducting state, which can not be preserved after the field redistribution at  $V \ll V_{th}$ . In Fig. 5, reentrant transition indeed depends on the  $\Delta V$  value, so the time-dependent behavior confirms our interpretation of the SnSe/WTe<sub>2</sub> polarization state control by electron transport through the interface.

# CONCLUSION

As a conclusion, we fabricate  $SnSe/WTe_2$  heterostructure to experimentally investigate charge transport between two ferroelectric van der Waals materials with different polarization directions.  $WTe_2$  is a polar metal with out-of-plane ferroelectric polarization, while SnSe ferroelectric semiconductor is polarized in-plane, so one should expect complicated polarization structure at the  $SnSe/WTe_2$  interface. We study dI/dV(V) curves, which demonstrate sharp symmetric drop to zero dI/dV differential conductance at some threshold bias voltages  $\pm V_{th}$ , which are nearly symmetric in respect to the bias sign. While the gate electric field is too small to noticeably affect the carrier concentration, the positive and negative threshold positions are sensitive to the gate voltage. Also, SnSe/WTe<sub>2</sub> heterostructure shows re-entrant transition to the low-conductive dI/dV = 0 state for abrupt change of the bias voltage even below the threshold values. This behavior can not be observed for single SnSe or  $WTe_2$  flakes, so we interpret it as a result of the  $SnSe/WTe_2$  interface coupling. In this case, some threshold value of the electric field at the SnSe/WTe<sub>2</sub> interface is enough to drive  $90^{\circ}$  change of the initial SnSe in-plane polarization in the overlap region. The polarization mismatch leads to the significant interface resistance contribution, analogously to the scattering of the charge carriers on the domain walls. Thus, we demonstrate polarization state control by electron transport through the

$SnSe/WTe_2$  interface.

### ACKNOWLEDGEMENT

We wish to thank S.S Khasanov for X-ray sample characterization. We gratefully acknowledge financial support by the Russian Science Foundation, project RSF-22-22-00229, https://rscf.ru/project/22-22-00229/.

- Rui Guo, Lu You, Yang Zhou, Zhi Shiuh Lim, Xi Zou, Lang Chen, R. Ramesh and Junling Wang, NATURE COMMUNICATIONS, 4, 1990 (2013).

- [2] Mengwei Si, Atanu K. Saha, Shengjie Gao, Gang Qiu Chang Niu, Haiyan Wang, Jingkai Qin, Yuqin Duan, Jie Jian, Wenzhuo Wu, Sumeet K. Gupta and Peide D. Ye, NATURE Electronics, 2, 580–586 (2019).

- [3] Bo-Bo Tian, Ni Zhong and Chun-Gang Duan, Chin. Phys. B, Vol. 29, No. 9, 097701 (2020).

- [4] Zhao Guan, He Hu, Xinwei Shen, Pinghua Xiang, Ni Zhong, Junhao Chu, and Chungang Duan, Adv. Electron. Mater., 6, 1900818 (2020).

- [5] Yue-Wen Fang and Hanghui Chen, COMMUNICA-TIONS MATERIALS, 1, 1 (2020).

- [6] Filippetti, A., Fiorentini, V., Ricci, F., Delugas, P. and Iniguez, J. Nat. Commun. 7, 11211 (2016).

- [7] T. H. Kim, D. Puggioni, Y. Yuan, L. Xie, H. Zhou, N. Campbell, P. J. Ryan, Y. Choi, J.-W. Kim, J. R. Patzner, S. Ryu, J. P. Podkaminer, J. Irwin, Y. Ma, C. J. Fennie, M. S. Rzchowski, X. Q. Pan, V. Gopalan, J. M. Rondinelli and C. B. Eom, Nature 533, 68 (2016).

- [8] Benedek, N. A. and Birol, T. J. Mater. Chem. C 4, 4000– 4015 (2016).

- [9] Z. Fei, W. Zhao, T. A Palomaki, B. Sun, M. K. Miller, Z. Zhao, J. Yan, X. Xu, D. H. Cobden, Nature 560, 336 (2018).

- [10] Shuoguo Yuan, Xin Luo, Hung Lit Chan, Chengcheng Xiao, Yawei Dai, Maohai Xie and Jianhua Hao, Nature Communications, 10, 1775 (2019).

- [11] P. Sharma, F.-X. Xiang, D.-F. Shao, D. Zhang, E.Y. Tsymbal, A.R. Hamilton, and J. Seide, Sci. Adv. 5(7), eaax5080 (2019).

- [12] K. Chang, F. Küster, B. J. Miller, J.-R. Ji, J.-L. Zhang, P. Sessi, S. Barraza-Lopez, and S. S. P. Parkin, Nano Lett. 20(9), 6590 (2020).

- [13] Kenji Yasuda, Xirui Wang, Kenji Watanabe, Takashi Taniguchi, Pablo Jarillo-Herrero, Science, 372, 6549, 1458-1462 (2021).

- [14] N.N. Orlova, N.S. Ryshkov, A.V. Timonina, N.N. Kolesnikov, and E.V. Deviatov, JETP Letters, 113, 389 (2021).

- [15] N. N. Orlova, A. V. Timonina, N. N. Kolesnikov, and E. V. Deviatov, Physical Review B 104, 045304 (2021).

- [16] N. N. Orlova, A. V. Timonina, N. N. Kolesnikov, and E. V. Deviatov, EPL, 135, 37002 (2021). https://doi.org/10.1209/0295-5075/ac2247

- [17] Wenhui Hou, Ahmad Azizimanesh, Arfan Sewaket, Tara Pena, Carla Watson, Ming Liu, Hesam Askari and

Stephen M. Wu, Nature Nanotechnology 14, 668–673 (2019).

- [18] Xiaowei Wang, Chao Zhu, Ya Deng, Ruihuan Duan, Jieqiong Chen, Qingsheng Zeng, Jiadong Zhou, Qundong Fu, Lu You, Song Liu, James H. Edgar, Peng Yu and Zheng Liu, NATURE COMMUNICATIONS, 12, 1109 (2021).

- [19] Yan Chen, Xudong Wang, Le Huang, Xiaoting Wang, Wei Jiang, Zhen Wang, Peng Wang, Binmin Wu, Tie Lin, Hong Shen, Zhongming Wei, Weida Hu, Xiangjian Meng, Junhao Chu and Jianlu Wang, Nature Communications, 12, 4030 (2021).

- [20] P.K. Das, D.D. Sante, I. Vobornik, J. Fujii, T. Okuda, E. Bruyer, A. Gyenis, B.E. Feldman, J. Tao, R. Ciancio, G. Rossi, M.N. Ali, S. Picozzi, A. Yadzani, G. Panaccione, and R.J. Cava, Nature Comm. 7, 10847 (2016).

- [21] B. Feng, Y.-H. Chan, Y. Feng, R.-Y. Liu,1 M.-Y. Chou, K. Kuroda, K. Yaji, A. Harasawa, P. Moras, A. Barinov, W. Malaeb, C. Bareille, T. Kondo, S. Shin, F. Komori, T.-C. Chiang, Y. Shi, and I. Matsuda, Phys Rev B 94, 195134 (2016).

- [22] H.-J. Kim, S.-H. Kang, I. Hamada and Y.-W. Son, Phys. Rev. B 95, 180101(R) (2017).

- [23] J. Zhou, F. Liu, J. Lin, X. Huang, J. Xia, B. Zhang, Q. Zeng et. al., Advanced Materials 29, 3, 1603471 (2017).

- [24] Salvador Barraza-Lopez, Benjamin M. Fregoso, John W. Villanova, Stuart S. P. Parkin, Kai Chang, Rev. Mod. Phys., Vol. 93, No. 1, 011001-3 (2021).

- [25] Shengxue Yang, Yuan Liu, Minghui Wu, Li-Dong Zhao, Zhaoyang Lin, Hung-chieh Cheng, Yiliu Wang, Chengbao Jiang, Su-Huai Wei, Li Huang, Yu Huang, and Xiangfeng Duan, Nano Res. 11(1), 554 (2018).

- [26] E. B. Borisenko, V. A. Berezin, N. N. Kolesnikov, V. K. Gartman, D. V. Matveev, and O. F. Shakhlevich, Phys. Solid State 59, 1310 (2017).

- [27] O.O. Shvetsov, A. Kononov, A.V. Timonina, N.N. Kolesnikov, E.V. Deviatov EPL, 124, 47003 (2018), doi: 10.1209/0295-5075/124/47003.

- [28] A. Kononov, O.O. Shvetsov, S.V. Egorov, A.V. Timonina, N.N. Kolesnikov and E.V. Deviatov, EPL, 122, 27004 (2018), doi: 10.1209/0295-5075/122/27004.

- [29] N.N. Orlova, N.S. Ryshkov, A.A. Zagitova, V.I. Kulakov, A.V. Timonina, D.N. Borisenko, N.N. Kolesnikov, and E.V. Deviatov, Phys. Rev. B 101, 235316 (2020).

- [30] Physics of Ferroelectrics. Modern Perspective., Edited by K. M. Rabe, Ch. H. Ahn, J.-M. Triscone, Springer-Verlag, Berlin, Heidelberg (2007).

- [31] T. Schenk, E. Yurchuk, S. Mueller, U. Schroeder, S. Starschich, U. Boottger and T. Mikolajick, Appl. Phys. Rev., 1, 2014, 041103.

- [32] K. Adouby, C. Pérez-Vicente, J. C. Jumas, R. Fourcade, and A. Abba Touré, Crystalline materials 213, 343-349 (1998).

- [33] L.-D. Zhao, Sh.-H. Lo, Y. Zhang, H. Sun, G. Tan, C. Uher, C. Wolverton, V. P. Dravid and M. G. Kanatzidis, Nature, 508, 373, (2014).

- [34] T. Hou, Ya. Ren, Yu. Quan, J. Jung, W. Ren, and Zh. Qiao, Phys. Rev. B 101, 201403(R) (2020).