#### I. INTRODUCTION

Abstract—Traditional TCAD simulation has succeeded in predicting and optimizing the device performance; however, it still

faces a massive challenge - a high computational cost. There

have been many attempts to replace TCAD with deep learning,

Technology computer-aided design (TCAD) simulation has played a key role in predicting and optimizing semiconductor device performance. As semiconductor technologies have become more sophisticated, TCAD simulation gets more time-consuming. To reduce simulation time, there have been attempts to use some technologies [1], [2] based on multicore computing, which turned out to be insufficient. As an alternative way, researchers began introducing deep learning (DL) models. In the semiconductor field, two approaches have been mainly studied. The first one is to model the relationship between inputs and outputs using DL rather than using partial differential equations (PDE) [3]-[6]. The second one is to solve differential equation via DL, which provides the initial values for PDE [7] or regularizes itself to mimic the differential equation [8]. So far no study has been done to make DL and current TCAD model compatible with each other. In this paper, we present a novel algorithm, called Real-Time TCAD (RTT) to complement the TCAD simulation process. This proposed algorithm enables 3-D real-time TCAD simulation and allows both TCAD and DL to be compatible with each other. As a result, the new features of this algorithm would restructure the conventional TCAD system in a way that DL solves the troubles that TCAD has and vice versa.

## **II. METHODOLOGY AND ITS ASSESSMENT**

# A. Preliminary

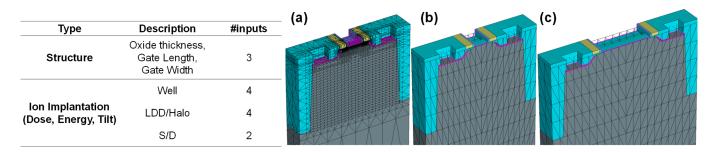

We begin with a brief explanation about TCAD simulation on a 45nm process. We use in-house process and device simulator (Polaris). There are three and ten input variables on device geometry and ion implantation (IIP) process, respectively (Fig. 1). We change the unstructured mesh into structured meshes with uniform intervals since it is difficult for DL to learn an unstructured mesh (Fig. 2). Even if the size of device varies depending on the input conditions, we change them into the predefined size (Fig. 2). Then, we generate 2.050 TCAD simulation samples by changing the input variables. 2,000 samples are used in the training phase and the remaining 50 samples are used to evaluate the performance of models.

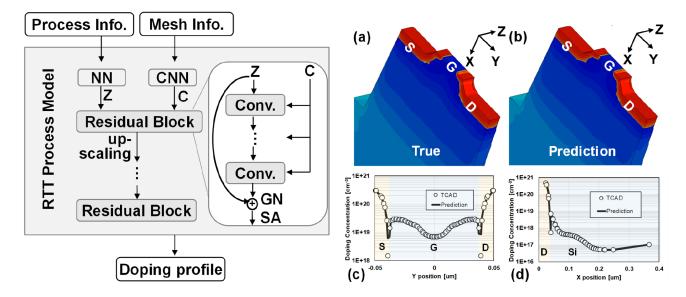

Process simulation computes doping concentration in metaloxide-semiconductor field-effect transistor (MOSFET) with respect to process condition. The process simulation consists of two steps; the first step creates MOSFET structure with meshes, and the second step solves IIP and diffusion processes using PDE. We use DL to primarily focus on predicting the doping profile since the latter step takes most of the time during process simulation. The distinctive feature of our work compared to the previous ones is that the process model learns the real value of doping of MOSFET structures, not the images. Furthermore, it allows the model to handle 3-D doping profiles. We introduce a core architecture based on convolutional neural network (CNN), up-sampling and residual block (RB) (Fig. 3). Up-sampling doubles the dimensions of input representation. RB, which contains group normalization (GN) [9] and swish activation (SA) [10], is introduced to prevent vanishing gradients [11]. GN makes the training loss landscape smoother and SA avoids a slow training time during near-zero gradients. Last but not least, putting coordinates during performing convolution operations is very crucial for model performance. The previous studies [3], [12] have put relative coordinates in each CNN operation. On the other hand, in this study, the coordinates extracted by actual meshes must be inserted because the coordinates of uniformed-sized outputs could be different. (Fig. 2 (b), (c)). We concatenate the Cartesian coordinates channel-wise to the input representation after passing the adaptive network, which consists of CNN and pooling layer. An adaptive network is designed to match the size with which each RB deals. Figure 4 compares the prediction results of the RTT process model (Fig. 4 (b)) to the ground truth (Fig. 4 (a)). To compare TCAD with the RTT model more precisely, we assess 1-D doping profiles exploited by horizontal and vertical axes (Fig. 4 (c), (d)). RTT model has achieved the average accuracy above 99% compared to TCAD.

©2021 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. DOI: 10.1109/IEDM19574.2021.9720616

# Restructuring TCAD System: Teaching Traditional TCAD New Tricks

Sanghoon Myung <sup>1</sup>, <sup>\*</sup>, Wonik Jang<sup>1</sup>, Seonghoon Jin<sup>2</sup>, Jae Myung Choe<sup>1</sup>, Changwook Jeong<sup>1,†</sup>, and Dae Sin Kim<sup>1</sup>

<sup>1</sup>Data and Information Technology Center, Samsung Electronics. <sup>2</sup>Device Lab, Samsung Semiconductor Inc.

email: {shoon.myung<sup>\*</sup>, chris.jeong<sup>†</sup>}@samsung.com

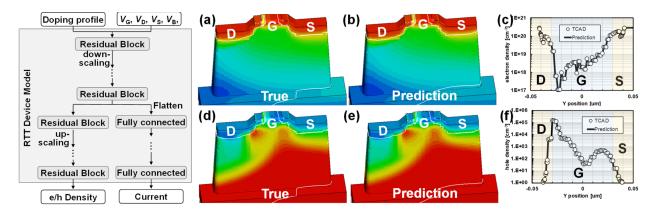

#### C. RTT Device Model

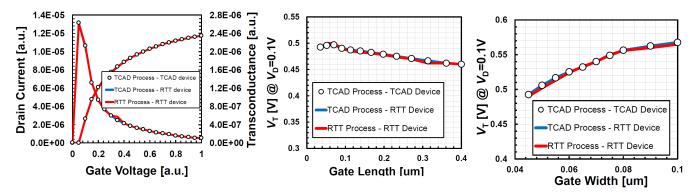

In device simulation, MOSFET structure and its doping concentration from RTT process model work as input variables. The device simulation results in the current-versus-voltage (I - V) curve and carrier profiles. We propose a multi-task learning that predicts the current and carrier profile simultaneously. Inputs to RTT device model, MOSFET structure with doping concentration and bias conditions, share RB and down-sampling until they reach the diverging point (Fig. 5). The network for career density uses RB and up-sampling for outputs to become bigger, same-sized with input dimension; the network for current only uses fully connected layers. Both electron and hole profiles predicted by RTT device model are identical with TCAD simulation by 99.5% (Fig. 6).

#### **III. ADDITIONAL FEATURES**

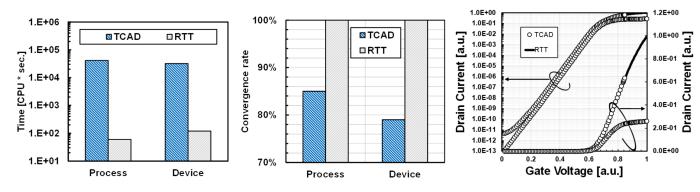

#### A. Real-time Simulation and No Convergence Error

One of the merits of RTT models, including RTT process and device model, is that it can predict TCAD simulation in real time. As described in Sec. I, TCAD simulation has trouble in predicting the device performance in real time. In contrast, RTT models can predict it in almost real time (Fig. 7). Quantitatively speaking, RTT models are 691 times faster than TCAD simulation. On top of that, TCAD simulation often suffers from errors that fail to solve PDE. The longer the TCAD tool chain, the lower the convergence rate (Fig. 8). On the other hand, RTT models present 100% convergence results. Figure 9 shows that the RTT device model is successful at predicting the I - V curve, which TCAD fails to predict.

#### B. Compatibility with TCAD simulation

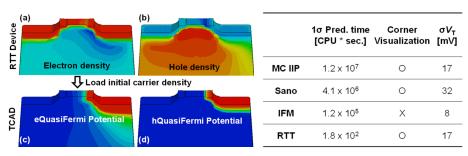

The previous studies [3]–[5] have only predicted the results. On the contrary, the proposed algorithm makes inputs and outputs of TCAD and RTT interchangeable. Figure 10 demonstrates that all results are indistinguishable even if an input of TCAD device simulation is an output of whether RTT process model or TCAD process simulation. In addition, the RTT device model infers I - V characteristics without any difference between the outputs of TCAD and those of RTT. Figure 11 and 12 demonstrate that RTT models are compatible with conventional TCAD model in various situations. Figure 13 shows an example that RTT device model can replace a part of TCAD device simulation. The TCAD device simulator selfconsistently couples the Poisson and continuity equation to obtain the unknown variables: carrier density and electrostatic potential. With our RTT device model, however, TCAD device simulator solves only Poisson equation after loading the carrier density predicted by RTT device model (Fig. 13). This method enables TCAD device simulator to use a Schottky contact model [13] while the previous work [7] cannot.

### C. Statistical Inference

The doping profile can naturally contain a variation because IIP is usually computed by Monte Carlo (MC) method. To capture the variance of MC IIP, we assume that the doping concentration of each node follows Gaussian distribution. Although discrete dopants are distributed in a device, this assumption is valid because the diffusion model is continuum model. We set the loss function of the RTT process model as negative-log likelihood (NLL) to capture a variance.

$$NLL = \frac{(y - u(x))^2}{2\sigma^2(x)} + \frac{\ln \sigma^2(x)}{2}$$

(1)

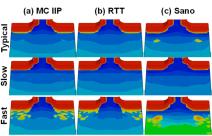

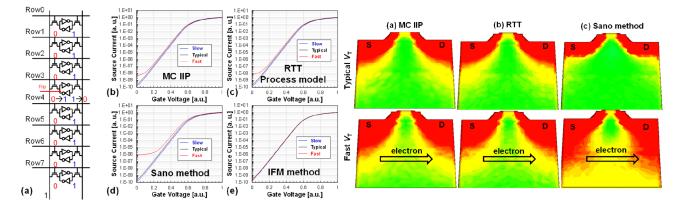

where u(x) and  $\sigma^2(x)$  are mean and variance of doping concentration that RTT process model returns. The  $\sigma^2(x)$ can represent the data noise (e.g., variance of MC IIP) if there is enough data [14]. Note that the number of MC particles for IIP is calculated from a dose of IIP and structure dimension. We evaluate whether the proposed method captures a variation of MC IIP or not. Furthermore, we compare MC IIP with two existing methods: Sano method [15] and impedance Field Method (IFM) [16]. The RTT results are compared to the various benchmark methods (Fig. 14). The  $\sigma V_T$  of RTT is consistent with that of MC IIP and is approximately an average of the  $\sigma V_T$  obtained from Sano and IFM. Also note that RTT model provides good visualization for simulation results. Figure 15 shows the process corner results from each method, but IFM cannot illustrate the process corner. RTT is consistent with MC IIP results for process corner. RTT and MC IIP results are similar to Sano results except for the fast corner. Next, to check the impact of the process variability on SRAM failure, simulations at various process corners have been performed and analyzed (Fig. 16 and Fig. 17). Figure 16 (a) illustrates a test case where a defective cell in one of SRAM arrays causes a punch-through current. Process corner simulations with different methods (RTT, Sano) are compared to MC IIP in order to examine which approach correctly describes a variation of doping profile. Except for the IFM method, the other methods (MC, Sano, and RTT) show the possibility of the leakage current (Fig. 16). It can be clearly seen in Fig. 17 that unexpected current flows on the substrate for the fast corner condition, while the typical condition suppresses the leakage current. It is important to note that RTT model is almost  $10^3 \sim 10^5$  times faster than MC and Sano when predicting  $1\sigma$  doping profile.

#### **IV. CONCLUSION**

We propose a novel approach to reinforce traditional TCAD simulation with domain-tailored DL algorithms. The proposed RTT method 1) shows the real-time prediction of 3-D TCAD simulators for the first time, 2) enables TCAD and deep learning to be compatible with each other, 3) fully resolves convergence error issues, and 4) demonstrates accurate modeling of IIP-induced process variations with  $10^3x$  reduction in simulation time. We hope this work can facilitate future studies of restructuring conventional TCAD systems.

#### REFERENCES

- Toselli, Andrea, and Olof Widlund. Domain decomposition methodsalgorithms and theory. Vol. 34. Springer Science & Business Media, 2004.

- [2] Koshimoto, Hiroo, et al. "Gummel-cycle Algebraic Multigrid Preconditioning for Large-scale Device Simulations." 2020 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD). IEEE, 2020.

- [3] Myung, Sanghoon, et al. "Real-Time TCAD: a new paradigm for TCAD in the artificial intelligence era." 2020 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD). IEEE, 2020.

- [4] Jeong, Changwook, et al. "Bridging TCAD and AI: its application to semiconductor design." IEEE Transactions on Electron Devices 68.11 (2021): 5364-5371.

- [5] Myung, Sanghoon, et al. "A novel approach for semiconductor etching process with inductive biases." arXiv preprint arXiv:2104.02468 (2021).

- [6] Kim, Yohan, et al. "Physics-augmented neural compact model for emerging device technologies." 2020 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD). IEEE, 2020.

- [7] Han, Seung-Cheol, Jonghyun Choi, and Sung-Min Hong. "Acceleration of semiconductor device simulation with approximate solutions predicted by trained neural networks." IEEE Transactions on Electron Devices 68.11 (2021): 5483-5489.

- [8] Huh, In, et al. "Time-reversal symmetric ode network." Advances in Neural Information Processing Systems 33 (2020): 19016-19027.

- [9] Wu, Yuxin, and Kaiming He. "Group normalization." Proceedings of the European conference on computer vision (ECCV). 2018.

- [10] Ramachandran, Prajit, Barret Zoph, and Quoc V. Le. "Searching for activation functions." arXiv preprint arXiv:1710.05941 (2017).

- [11] He, Kaiming, et al. "Deep residual learning for image recognition." Proceedings of the IEEE conference on computer vision and pattern recognition. 2016.

- [12] Liu, Rosanne, et al. "An intriguing failing of convolutional neural networks and the coordconv solution." Advances in neural information processing systems 31 (2018).

- [13] Varahramyan, K., and E. J. Verret. "A model for specific contact resistance applicable for titanium silicide-silicon contacts." Solid-State Electronics 39.11 (1996): 1601-1607.

- [14] Kendall, Alex, and Yarin Gal. "What uncertainties do we need in bayesian deep learning for computer vision?." Advances in neural information processing systems 30 (2017).

- [15] Sano, Nobuyuki, et al. "On discrete random dopant modeling in driftdiffusion simulations: physical meaning of atomistic 'dopants." Microelectronics Reliability 42.2 (2002): 189-199.

- [16] El Sayed, Karim, Eugeny Lyumkis, and Andreas Wettstein. "Modeling statistical variability with the impedance field method." Proc. Int. Conf. Simulation Semiconductor Process. Devices (SISPAD). 2012.

ated with ion implantation.

Fig. 1. Description of TCAD input parameters. There are Fig. 2. An example of (a) original mesh, (b) interpolated mesh that has a same structure of three variables related to structure and ten variables associ- (a) and (c) interpolated mesh that has a long gate length. To make it clearly visible, we enlarge interpolated mesh bigger than the actual scale. Regardless of structure size, the number of grids is constant while the size of the interval depends on the structure size.

Fig. 3. Illustration of proposed process model. NN denotes a neural Fig. 4. (a) A TCAD process simulation result. (b) A prediction result of RTT network, Z the latent space learned by NN, C the coordinates sampled process model. (c) 1-D doping concentration plot in the horizontal direction from mesh, GN the group normalization and SA the swish activation. Z below the gate. (d) 1-D doping concentration plot in the vertical direction and C are concatenated for every convolution.Up-sampling doubles the at the center of drain. dimensions of input representation.

Fig. 5. Illustration of RTT device model, Fig. 6. Electron density of (a) TCAD (b) RTT device model at  $V_D = V_G = V_{DD}$ . (c) 1-D electron which can predict both electron/hole den- density in the horizontal direction below the gate. Hole density of (d) TCAD (e) RTT device model at  $V_D = V_G = V_{DD}$ . (f) 1-D hole density in the horizontal direction below the gate. sity and the current.

Fig. 7. Prediction time for each simulation. RTT Fig. 8. Convergence rate of each simulation. RTT model can predict the result up to 691 times faster. model shows 100% convergence rate.

Fig. 9. An example of  $I_D - V_G$  curves. RTT device model successfully calculates  $I_D - V_G$  curves while TCAD simulation cannot.

Fig. 10.  $I_D - V_G$  curves calculated by TCAD device Fig. 11. The results of the threshold voltage simulation whose inputs are from both TCAD process roll-off by various simulations. The results can Fig. 12. The results of narrow width effect. All be indistinguishable from each other. results are consistent with each other. simulation and RTT process model.

hole estimated by TCAD after loading carrier density from RTT device results.

Fig. 13. (a) Electron and (b) hole density predicted by Fig. 14. The results of benchmark methods. RTT (c) Sano. Typical  $V_T$  denotes an average RTT. The quasi-Fermi potential of (c) electron and (d) Prediction time represents the total time to of 100 samples, Slow  $V_T(u_{donor} - 3\sigma_{donor})$  generate a hundred samples. RTT model shows  $(u_{acceptor} + 3\sigma_{acceptor})$  and Fast  $V_T(u_{donor})$ a good agreement with MC IIP results.

Fig. 15. Process corner of (a) MC IIP (b) +  $3\sigma_{donor}$ ) - ( $u_{acceptor}$  -  $3\sigma_{acceptor}$ ).

Fig. 16. (a) A schematic on failure analysis of SRAM array. At row 3, in the typical process, whereas unexpected current flows at the substrate in leakage current occurs from the drain to the source. (b-e)  $I_S - V_G$  curve the fast process. All method shows the possibility of the leakage current. of (b) MC IIP (c) RTT (d) Sano and (e) IFM for the process corner.