# A note on load balancing in DC microgrids

Shravan Mohan<sup>1</sup> and Bharath Bhikkaji<sup>2</sup> <sup>1</sup>Mantri Residency, Bannerghatta Road, Bangalore. <sup>2</sup>Indian Institute of Technology Madras, Chennai.

Abstract—A problem of load balancing in isolated DC microgrids is considered in this paper. Here, a DC load is fed by multiple heterogenous DC sources, each of which is connected to the load via a boost converter. The gains of the DCC's provide for a means to control the division of load current amongst the DC sources. The primary objective of the control scheme is to minimise the total losses in the network, while maintaining the output voltage within a desired range, serving the load current demand and adhering to VI-characteristics of the power sources. Under assumptions of concavity/monotonocity/piecewise-linearity of the VI-characteristics, the problem is solved using a convex relaxation. It is shown that the solution to the relaxed problem is tight. Thus, the resulting algorithm is guaranteed to reach global optimality in a numerically efficient manner. Simulations are provided for corroboration.

Index Terms—Convex Optimization, DC-DC power converters, Load Balancing

#### I. INTRODUCTION

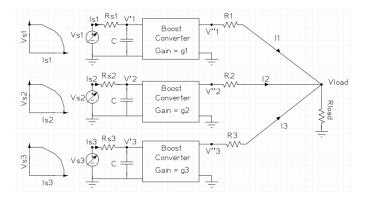

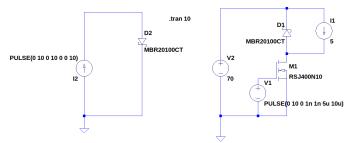

Consider the circuit shown in Figure 1. The voltage sources with the VI-characteristic curves (output voltage vs current drawn) drawn beside those represent the heterogeneous power sources. Heterogeneity here is with respect to the VI characteristics. It is further assumed that all the VI characteristic curves are positive, piece-wise linear (PWL), concave and non-increasing (A1). Such an assumption, as shall be shown, aids analysis. It is also not an impractical assumption since many power sources show such behaviour and a concave curve can be well-approximated as a piece-wise linear curve. The internal resistances of these sources,  $Rs_1$ ,  $Rs_2$ ,  $\cdots$ ,  $Rs_k$ , as also shown in Figure 1, are considered separately and are not a part of the VI-characteristics (A2). Each of these sources is connected to the load via a DC-DC converter (DCC). A large capacitive filter is placed at the input of the DCC's so as to prevent current ripple in the power sources (A3). It is assumed that the DCC's in this problem are of the boost class (A4). The output of these DCC's are connected to the load via cable wires which offer their own resistances,  $R_1, R_2, \dots, R_k$ . The load is assumed to be resistive (A5), which needs the voltage across it to be within a desired range. It is also assumed that the minimum of this range is greater than the open circuit voltages of all power sources (A6).

The DCC gains are the control inputs in this problem. It is mandated that the DCC's are operated in the Continuous Conduction Mode (CCM), by ensuring a minimum average current through the inductor (A7). The objective here is to set the gains so as to minimize the total losses in the

Fig. 1. A schematic of the DC microgrid showing three DC sources, all together feeding the load. Each one has a different VI-characteristic as shown in the schematic and a different internal resistance. The load is modelled as a resistance. Also, each source is connected to the load via a boost converter. The connecting cables from the output of the DCC's to the load offer resistances as shown. The gains of the DCC's are the control inputs for a desirable load balance.

system. The losses considered here are the resistive losses in the cables and the internal resistances, and in the DCC themselves. Note that the losses here refer to the losses at steady state; the losses during transients are not considered. In addition, while formulating an optimization problem, the fact that the DCC's do not inject any power into the system, must also be included.

Such scenarios commonly arise in systems fed by multiple renewable sources, such as solar panels, fuel cells, lithiumion/lead-acid batteries and windmills. The variations in solar power, the fuel cell state and wind direction, or the variations in manufacturing process itself, leads to variations in the VI-characteristic curves of these devices. This makes a case for the requirement of an appropriate control strategy to balance the load current and regulate the load voltage. Since such networks might involve long cables, there is also a strong need to minimize the resistive losses in them. In addition, there are the losses of the DCC's themselves, which need to be minimized in order for an efficient thermal management. The losses in the DCC's are typically divided into conduction and switching losses. It will however be assumed that the conduction losses due to the current ripple component and the losses in the capacitors are negligible (**A8**).

There has been considerable interest in this field. The authors of [1] consider a similar load balancing in an

isolated Dc microgrid and propose a metric termed as droop index, which measures the performance of the network. The performance is a function of the current difference between branches and the cable losses at the output side of the DCC's. The authors of [2] propose a decentralized control scheme to regulate the load voltage. The scheme depends only the output voltage and output current of a branch, thereby not requiring a communication overhead between the DCC's and a central controller. The authors of [3] present an optimization methodology for determining droop resistances, chosen from a discrete set of resistance, for various generation units in network so to minimize the resistive losses in the network. The focus of all the references mentioned here is to introduce a virtual resistance (called droop resistance) to improve current sharing amongst the loads, while maintaining voltage regulation. To the best of the authors' knowledge, an approach similar to the one presented for load balancing in DC-microgrids considering sources, which considers (i) varied concave non-increasing PWL VI-characteristic curves, (ii) the losses in DCC's, the internal resistances and the cables, (iii) while maintaining an output voltage within a desired range and (iv) catering to a current demand, has not been discussed in literature. [4] [5], [6], [7], [1], [2], [8]

### II. THE OPTIMIZATION PROBLEM

The following notations describe the optimization variables in a network with N branches.

- $\{Vs_1, Vs_2, \dots, Vs_N\}$  denote the average source voltages at steady state.

- $\{Is_1, Is_2, \dots, Is_N\}$  denote the average source currents at steady state, while  $\{is_1(t), is_2(t), \dots, is_N(t)\}$  represent the instantaneous source currents.

- $\{V'_1, V'_2, \cdots, V'_N\}$  denote the average DCC's' average input voltages at steady state.

- $\{V_1'', V_2'', \dots, V_N''\}$  denote the average DCC's' average output voltages at steady state.

- $\{I_1, I_2, \dots, I_N\}$  denote the average DCC's' average output currents at steady state.

- $\{id_1(t), id_2(t), \dots, id_N(t)\}$  represent the instantaneous diode currents, and  $\{im_1(t), im_2(t), \dots, im_N(t)\}$  represent the instantaneous MOSFET currents.

- $\{vd_1(t), vd_2(t), \dots, vd_N(t)\}$  represent the instantaneous voltage at the anode of the diode.

In the following analysis, the time (t) will be dropped for ease of exposition. Also, bold lettered variables will denote the optimal values. The following are known parameters of the circuit components.

- $f_k(x) = \min_{i \in [1, P_k]} \{ \beta_{k,i} x + \gamma_{k,i} \}, \ \beta_{k,i} < 0 \ \forall \ k, i \ (\text{see A1}).$

- $\{Rs_1, Rs_2, \dots, Rs_N\}$  and  $\{R_1, R_2, \dots, R_N\}$ , resistances connecting the sources to the DCC's (see A2) and the DCC's to the load, respectively.

- $R_{\text{load}}$ , the load resistance.

- { $R_{L,1}, R_{L,2}, \cdots, R_{L,N}$ }, the DC resistances of the inductors used in the DCC's.

- $[V_{L,\min}, V_{L,\max}]$ , desired average output voltage range.

- $\{I_{1,\min}, I_{2,\min}, \cdots, I_{N,\min}\}$ , minimum average output currents to ensure CCM.

- $\{g_{1,\max}, g_{2,\max}, \cdots, g_{N,\max}\}$ , upper bounds on the DCC gains. The lower bounds are assumed to be one (see A4).

- $\{\lambda_1, \lambda_2, \cdots, \lambda_N\}$  and  $\{\mu_1, \mu_2, \cdots, \mu_N\}$ , user-defined weights.

- $\{R_{M,1}, R_{M,2}, \dots, R_{M,N}\}$ , ON state drain-source resistances of the MOSFETs used in the DCC's.

- { $V_{D,1}, V_{D,2}, \cdots, V_{D,N}$ }, the forward bias voltages of diodes used in the DCC's.

- $\{R_{D,1}, R_{D,2}, \cdots, R_{D,N}\}$ , the diode resistances.

- $\{\alpha_1, \alpha_2, \cdots, \alpha_N\}$ , the multiplicative constant for deriving switching losses for the MOSFETs.

## A. The Construct

Consider the optimization problem mentioned below:

$$\min \sum_{k=1}^{N} \lambda_{k} \left\{ Is_{k}^{2} \left( Rs_{k} + R_{L,k} \right) + \left( im_{k} \right)_{\mathrm{rms}}^{2} R_{M,k} \cdots \right. \\ \left. \left. \left. + \left( id_{k} \right)_{\mathrm{rms}}^{2} R_{D,k} + V_{D,k} I_{k} + I_{k}^{2} R_{k} + \alpha_{k} \left( vd_{k} id_{k} \right)_{\mathrm{peak}} \right\} \right\}$$

(1)

subject to

$$V'_k = V s_k - I s_k R s_k, \ \forall k, \tag{2}$$

$$V_k'' = V_{\text{load}} + I_k R_k, \ \forall k, \tag{3}$$

$$\sum_{k=1}^{N} I_k = \frac{V_{\text{load}}}{R_{\text{load}}},\tag{4}$$

$$V_{\text{load},\min} \le V_{\text{load}} \le V_{l,\max},$$

(5)

$$V_k' \le V_k'' \le g_{k,\max} V_k', \ \forall k, \tag{6}$$

$$Vs_k = f_k(Is_k), \ \forall k, \tag{7}$$

$$Vs_k Is_k = \left\{ Is_k^2 \left( Rs_k + R_{L,k} \right) + \left( im_k \right)_{\rm rms}^2 R_{M,k} \cdots \right. \\ \left. \cdots + \left( id_k \right)_{\rm rms}^2 R_{D,k} + I_k^2 R_k + V_{D,k} I_k \cdots \right. \\ \left. \cdots + \alpha_k \left( vd_k id_k \right)_{\rm peak} + V_{\rm load} I_k \right\} \; \forall k.$$

$$(8)$$

$$Is_k \ge Is_{k,\min}, \quad Vs_k, Is_k, V'_k, V''_k \ge 0, \forall k.$$

(9)

Modifications to this problem, which will be discussed in the following subsections, will lead to the main algorithm of this paper shown in Figure 2.

1) The Cost Function: The objective function is the weighted sum total of losses in the cables, the internal resistances of sources and the DCC's. These weights can be regarded as the cost of the losses in a particular branch, based on the type of power source used. With large input and output capacitors (see A3) in the DCC's, the ripple in the input source current and the output current is negligible. Thus, the

resistive losses in the cables and the internal resistances of where  $s = \text{sign}(R_{M,k} - R_{D,k})$ , the  $k^{\text{th}}$  branch is

$$I_k^2 R_k + I s_k^2 R s_k. aga{10}$$

The loss in a DCC is composed of two parts: (i) the conduction losses in the inductor, the switch and the diode and (ii) the switching loss in the switch. Since the current ripple in the inductor is very low (see A8) as compared to the average value, the conduction loss in inductor of the  $k^{\text{th}}$ converter is approximately

$$Is_k^2 R_{L,k} \tag{11}$$

Now, notice that in the boost converter, the instantaneous current through the inductor is the sum total of the instantaneous switch current and diode current. Thus

$$is_k = im_k + id_k \Longrightarrow Is_k = \langle im_k \rangle + I_k,$$

(12)

where < . > denotes the time average over one time period. Also note that the instantaneous switch current and the diode current in a boost converter are orthogonal. That is,

$$im_k id_k = (is_k - id_k) id_k = 0.$$

(13)

With these observations, the conduction loss in the switch of the  $k^{\text{th}}$  converter is approximated as

$$(im_{k})_{\rm rms}^{2} R_{M,k} = \frac{1}{T} \int_{0}^{T} (is_{k} - id_{k})^{2} (t) R_{M,k} dt$$

$$= \frac{1}{T} \int_{0}^{T} (is_{k} (is_{k} - id_{k})) (t) R_{M,k} dt$$

$$\approx Is_{k} (Is_{k} - I_{k}) R_{M,k} = Is_{k}^{2} R_{M,k} - Is_{k} I_{k} R_{M,k}.$$

(14)

Using a similar logic, the conduction loss in the diode of the  $k^{\rm th}$  converter is

$$V_{D,k}I_k + (id_k)_{\rm rms}^2 R_{D,k} = V_{D,k}I_k + Is_k I_k R_{D,k}.$$

(15)

The switching loss in the MOSFET of the  $k^{\text{th}}$  converter is [9], [4]

$$\alpha_k (vd_k id_k)_{\text{peak}} = \alpha_k (vd_k)_{\text{peak}} (id_k)_{\text{peak}} = \alpha_k (V_{\text{load}} + I_k R)$$

$$\cdots V_{D,k} + Is_k R_{D,k} Is_k = \alpha_k (V_{\text{load}} + V_{D,k}) Is_k.$$

$$\cdots + \alpha_k Is_k I_k R_k + \alpha_k Is_k^2 R_{D,k}.$$

(16)

Therefore, the cost function is

$$\sum_{k=0}^{N} \lambda_{k} \left\{ Is_{k}^{2} \left( Rs_{k} + R_{L,k} + R_{M,k} + \alpha_{k}R_{D,k} \right) .. \\ \cdots + I_{k}^{2}R_{k} + Is_{k}I_{k} \left( \alpha_{k}R_{k} - \left( R_{M,k} - R_{D,k} \right) \right) \cdots \\ \cdots + \alpha_{k}V_{\text{load}}I_{k} + V_{D,k} \left( I_{k} + \alpha_{k}Is_{k} \right) \right\}.$$

(17)

The above can be modified further as

$$\sum_{k=0}^{N} \lambda_k Q_k = \sum_{k=0}^{N} \lambda_k \left\{ I s_k^2 \left( R_{\text{eff},1} - R_{\text{eff},2} \right) \cdots + \left( I_k + I s_k \alpha_k \right)^2 \frac{R_k}{2} + \left( I s_k - s I_k \right)^2 \frac{|R_{M,k} - R_{D,k}|}{2} \cdots + \alpha_k V_{\text{load}} I_k + V_{D,k} \left( I_k + \alpha_k I s_k \right) + I_k^2 R_{\text{eff},3} \right\}, \quad (18)$$

$$R_{\text{eff},1} = (Rs_k + R_{L,k} + R_{M,k} + \alpha_k R_{D,k}), \quad (19)$$

$$R_{\text{eff},2} = \left(\frac{|R_{M,k} - R_{D,k}|}{2} + \frac{\alpha_k^2 R_k}{2}\right), \qquad (20)$$

and

$$R_{\rm eff,3} = \left(\frac{R_k - |R_{M,k} - R_{D,k}|}{2}\right).$$

(21)

The expression is convex iff

$$R_{\text{eff},1} \ge R_{\text{eff},2} \text{ and } R_{\text{eff},3} \ge 0.$$

(22)

These are not an impractical conditions for the following reason. The quantity  $\alpha_k$  is approximately

$$\alpha_{\rm k} = \frac{1}{2} \left( \tau_{\rm ON} + \tau_{\rm OFF} \right) f_s, \tag{23}$$

where  $\tau_{ON}$  and  $\tau_{OFF}$  are ON and OFF transition times for a MOSFET. For typical values  $f_s = 100$  KHz, and  $\tau_{\rm ON} +$  $\tau_{\rm OFF} = 100$  ns, one obtains  $\alpha_k \approx 0.005$ . With a typical large inductor resistance of  $1\Omega$ , a source resistance of  $500m\Omega$ , MOSFET ON-state resistance of  $200m\Omega$ , diode resistance of  $30m\Omega$  and a low cable resistance of  $1\Omega$  the bounds reads

$$1.7 \ge 0.115 \text{ and } 1 \ge 0.115.$$

(24)

Thus, the two conditions are satisfied with healthy margins, thereby resulting in a convex cost function in practical cases.

There might also be an interest to add to the cost a weighted combination of the absolute values of circulating currents in the network. Circulating currents arise due to the difference between the output voltages of the different DCC's. Mathematically, the circulating currents are a linear transform of the output voltages of the DCC's, and a weighted absolute sum (by weights  $\{\mu_1, \mu_2, \cdots, \mu_N\}$ ) of these adds a convex term to the cost function. That is, the total circulating current from  $k^{\text{th}}$  converter is given as [1]

$$Ic_{k} = \sum_{j \neq k} \frac{V_{k}'' - V_{j}''}{(R_{k} + R_{j})},$$

(25)

and thus the additive cost would be

$$\sum_{k=1}^{N} \mu_k |Ic_k| = \sum_{k=1}^{N} \mu_k \left| \sum_{j \neq k} \frac{V_k'' - V_j''}{(R_k + R_j)} \right|, \qquad (26)$$

It will be shown that with this additive term in the cost function, the qualitative aspects of the solution remain unchanged.

2) The Constraints: There are in all eight sets of constraints in the optimization problem (9). The first set of constraints are the Kirchoff's Voltage Laws (KVL) applied to the input side of the DCC's. The second set is the KVL applied to the output side of the DCC's (see A5). The third constraint is the Kirchoff's Current Law applied to load node. The fourth constraint bounds the output voltage within the desired range. The fifth set of constraints bounds the gains of the DCC's within practical ranges (see A4). For example, the following expression gives a conservative upper bound on the the gain of the  $k^{\text{th}}$  boost converter (ignoring switching loss) [4],

$$\frac{\left(1 - D'\frac{V_{D,k}}{V_{in}}\right)D'(R_k + R_{\text{load}})}{(D')^2(R_k + R_{\text{load}}) + D'R_{D,k} + DR_{M,k} + R_{L,k}},$$

(27)

where D' = 1 - D. Note that gain depends on the input voltage to the DCC. Suppose now that the input voltage is constrained to be at least 20 times the forward bias of the diode. That is

$$V_k' \ge 20 * V_{D,k}.$$

(28)

Then a conservative maximum on the gain would be

$$\max_{D} \left\{ \frac{0.95D'(R_k + R_{\text{load}})}{(D')^2(R_k + R_{\text{load}}) + D'R_{D,k} + DR_{M,k} + R_{L,k}} \right\}.$$

(29)

The sixth set of constraints ensures that the VI-characteristics of the power sources are adhered to (see **A1**). The seventh set of constraints ensures that the total power input to the DCC is equal its output power plus the DCC losses [4]. This is equivalent to stating that the DCC's do not inject power into the network. To derive the functional form of the constraint, note that

$$V'_k Is_k = V''_k I_k + Q_k$$

$$\Rightarrow (Vs_k - Is_k Rs_k) Is_k = (V_{\text{load}} + I_k R_k) I_k + Q_k$$

$$\Rightarrow Vs_k Is_k = Is_k^2 Rs_k + Q_k + I_k^2 R_k + V_{\text{load}} I_k.$$

Substituting the expression for  $Q_k$ , as discussed earlier, one obtains the seventh set of constraints.

The last set of constraints, requiring the voltage and current opt-variables to be non-negative, ensures that power is only drawn from the power sources. Now suppose that the following lower bounds hold

$$Is_k \ge 5 \frac{\max\{Vs_k\}}{f_s L_k}, \ \forall k.$$

(30)

It is immediate that converters would operate only in CCM as desired, as the average current is larger than the maximum deviation that can occur (see A7). Moreover, the RMS of a waveform with an average of  $Is_k$  and a linear deviation of at most 40% is given by [4]

$$(is_k)_{\rm rms}^2 = Is_k^2 \left(1 + \frac{0.4^2}{12}\right) \approx Is_k^2,$$

(31)

so that the conduction losses in the inductors are approximated well by considering only the average current passing through those. Finally, the optimal gains can be calculated as the ratio of the optimal  $V_k''$ 's to  $V_k'$ 's, and the optimal duty ratios can be determined using [4]

$$I_{k} \approx (1 - D) Is_{k}. \tag{32}$$

It may be noted that the duty ratio corresponding to optimal gains need not be perfectly attainable in practice due to the limit on the counter frequency. In that case, it is assumed that the duty cycle in implementation will be the best approximation to the optimal duty ratio.

### B. The Convex Relaxation

The non-convexity of the optimization problem (9) is the primary challenge. In a series of steps it shall be shown that the a convex relaxation of the problem can be used to obtain the globally optimal solution. As a first step, let the load voltage  $V_{\text{load}}$  be fixed to a value  $V_{\text{load}}$  within the desired range. Let the solution set in this case be given by  $P = \{V_1, \dots, V_m, V'_1, \dots, V'_m, V''_1, \dots, V''_m, Is_1, \dots, Is_m, I_1, \dots, I_m\}$ . Let the optimal cost be C. Now, suppose for some  $\delta$  > 0,  $V_{\mathrm{load}}$  –  $\delta$  is also within the desired range. Then it is obvious that the point  $P_{\delta}$  =  $\{V_1, \cdots, V_m, V_1', \cdots, V_m', V_1'' - \delta, \cdots, V_m'' - \delta, Is_1, , \dots, Is_m, I_1, \cdots, I_m\}$  is a feasible point for the optimization problem with the load voltage set to  $V_{\text{load}} - \delta$ , the cost of which is also C. Note that the assumption A6 is necessary here to prove feasibility of  $P_{\delta}$ . Therefore, the optimal cost with the load voltage set to  $V_{\rm load} - \delta$  cannot be more than C. All these arguments also hold good with the addition cost term given in (26), since the difference between the output voltages of the DCC's in  $P_{\delta}$  remain unchanged. Thus, one can at once set the load voltage to the minimum value in the desired range. This fact shall be assumed in the analysis to follow.

For the second step, note that the sixth set of constraints consists of all non-convex constraints, as the functions  $f_k$ 's need not be affine. But, since  $f_k(.)$  are concave, a standard convex relaxation would be to replace equality with less than or equal to. That is:

$$V_k = f_k(Is_k) \quad \longmapsto \quad V_k \le f_k(Is_k) \tag{33}$$

This relaxation allows for the output voltage to be lower than what the VI-characteristic curves prescribe. Similarly, the seventh set of constraints also comprises all non-convex constraints, since those are quadratic and affine. A convex relaxation of these constraints can be achieved in the following way. With the assumption that the  $f_k(.)$  is a PWL concave decreasing function (see A1), note that

$$V_k I s_k = f_k (I s_k) I s_k = \min_{j \in [1, P_k]} \left\{ \beta_{k,j} I s_k^2 + \gamma_{k,j} I s_k \right\}.$$

(34)

1) Set  $V_{\text{load}}$  to  $V_{\text{load,min}}$ . Ensure that given circuit parameters adhere to (22).

2) Solve the following:

$$\min\sum_{k=0}^{N} \lambda_{k} \left\{ Is_{k}^{2} \left( R_{\text{eff},1} - R_{\text{eff},2} \right) + \left( I_{k} + Is_{k}\alpha_{k} \right)^{2} \frac{R_{k}}{2} + \left( Is_{k} - sI_{k} \right)^{2} \frac{|R_{M,k} - R_{D,k}|}{2} + \alpha_{k} V_{\text{load}} I_{k} + V_{D,k} I_{k} + I_{k}^{2} R_{\text{eff},3} \right\}$$

$$\begin{split} V_k' &= Vs_k - Is_k Rs_k \; \forall k, \quad V_k'' = V_{\text{load}} + I_k R_k \; \forall k, \quad \sum_{k=1}^m I_k = \frac{V_{\text{load}}}{R_{\text{load}}}, \quad V_k' \leq V_k'' \leq g_{k,\max} V_k' \; \; \forall k, \quad V_k \leq f_k \left( Is_k \right) \; \forall k, \\ \min_{j \in [1, P_k]} \left\{ \beta_{k,j} Is_k^2 + \gamma_{k,j} Is_k \right\} \geq Is_k^2 \left( R_{\text{eff},1} - R_{\text{eff},2} \right) \left( I_k + Is_k \alpha_k \right)^2 \frac{R_k}{2} + \left( Is_k - sI_k \right)^2 \frac{|R_{M,k} - R_{D,k}|}{2} \cdots \\ \cdots + \alpha_k V_{\text{load}} I_k + V_{D,k} I_k + I_k^2 R_{\text{eff},3} + V_{\text{load}} I_k \; \forall k \;, \\ I_k \geq I_{k,\min} \; \forall k, \quad V_k, Is_k, V_k', V_k'' \geq 0 \; \forall k. \end{split}$$

3) If feasible, and for some k,  $V_k < f_k(Is_k)$ , then set  $V_k$  to  $f_k(Is_k)$ , set  $V'_k$  to  $V'_k + f_k(Is_k) - V_k$ .

|      | •  | -   |      | o            |           |

|------|----|-----|------|--------------|-----------|

| Fig. | 2. | The | Main | Optimization | Algorithm |

|      |    |     |      |              |           |

| TABLE | I |

|-------|---|

| IADLL | 1 |

CASE(I): PARAMETERS FOR THE CONCAVE POWER SOURCES

| Br. No.                                                                             | $eta_1, \gamma_1$ | $eta_2, \gamma_2$ | $eta_3, \gamma_3$ | $eta_4, \gamma_4$ | $eta_5, \gamma_5$ | $eta_6, \gamma_6$ | $eta_7,\gamma_7$ | $eta_8, \gamma_8$ | $eta_9, \gamma_9$ | $eta_{10}, \gamma_{10}$ |  |  |  |

|-------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-------------------|-------------------|-------------------------|--|--|--|

| 1                                                                                   | -0.4483,          | -0.7394,          | -0.848,           | -1.2129,          | -2.0441,          | -2.8258,          | -3.4599,         | -3.806,           | -4.6268,          | -4.8629,                |  |  |  |

| 1                                                                                   | 42.2458           | 42.8602           | 43.3191           | 45.6297           | 52.6495           | 60.8998           | 68.932           | 74.0474           | 87.9088           | 92.3943                 |  |  |  |

| 2                                                                                   | -0.1616,          | -0.3842,          | -0.911,           | -1.7442,          | -1.982,           | -2.4405,          | -2.4844,         | -3.4,             | -4.2573,          | -4.9458,                |  |  |  |

| 2                                                                                   | 35.5302           | 35.9755           | 38.0826           | 43.0815           | 44.9842           | 49.5688           | 50.0966          | 62.9142           | 76.631            | 89.024                  |  |  |  |

| -0.8106, -0.8138, -0.858, -1.0573, -1.1274, -1.8309, -2.0942, -2.7073, -3.6009, -4. |                   |                   |                   |                   |                   |                   |                  |                   |                   |                         |  |  |  |

| 3                                                                                   | 28.1456           | 28.1517           | 28.3187           | 29.4479           | 29.9775           | 36.6217           | 39.6052          | 47.7127           | 61.2161           | 73.912                  |  |  |  |

|                                                                                     |                   |                   |                   |                   | TABLE II          |                   |                  |                   |                   |                         |  |  |  |

| IADLE II                                |                                                      |

|-----------------------------------------|------------------------------------------------------|

| CASE(I): OTHER CIRCUIT PARAMETERS AND R | Results, $V_{\text{load}} = 50, R_{\text{load}} = 5$ |

| Br. No. | Rs   | $R_L$ | $R_M$ | $\alpha$ | $V_D$ | $R_D$ | $I_{\min}$ | $V'_{\rm min}$ | $g_{\rm max}$ | $\lambda$ | $\mu$ | Is      | V'       | V''      | Ι       |

|---------|------|-------|-------|----------|-------|-------|------------|----------------|---------------|-----------|-------|---------|----------|----------|---------|

| 1       | 0.5  | 0.04  | 0.019 | 0.0026   | 0.6   | 0.014 | 0.6613     | 12             | 4.4755        | 1         | 1     | 6.9648, | 33.6996, | 50.8974, | 4.4870, |

| 1       | 0.5  | 0.04  | 0.019 | 0.0020   | 0.0   | 0.014 | 0.0015     | 12             | 4.4755        | 1         | 1     | 6.9561  | 33.699   | 50.894   | 4.4865  |

| 2       | 0.4  | 0.053 | 0.019 | 0.0026   | 0.6   | 0.014 | 0.3003     | 12             | 4.0702        | 1.5       | 1     | 5.5893, | 30.7549, | 50.8216, | 3.2864, |

| 2       | 0.4  | 0.055 | 0.019 | 0.0020   | 0.0   | 0.014 | 0.3003     | 12             | 4.0702        | 1.5       | 1     | 5.5905  | 30.753   | 50.818   | 3.2865  |

| 2       | 0.45 | 0.053 | 0.019 | 0.0026   | 0.6   | 0014  | 0.2012     | 12             | 4.0627        | 1         | 1     | 5.5357, | 21.0780, | 50.5120, | 2.2264, |

| 5       | 0.45 | 0.055 | 0.019 | 0.0020   | 0.0   | 0014  | 0.2012     | 12             | 4.0027        | 1         | 1     | 5.5364  | 21.077   | 50.509   | 2.2263  |

| TA | DI | E | TIT |

|----|----|---|-----|

| IА | וס |   | 111 |

Case (II, a): Circuit parameters and results (CVXPY, LTSPICE),  $V_{\text{load}} = 70$ ,  $R_{\text{load}} = 5$ ,  $V_{\text{load}}$  from LTSPICE = 71.137

| Br. No. | $V_s$ | Rs   | $R_L$ | $R_M$ | α        | $V_D$  | $R_D$  | $I_{\min}$ | $V'_{\rm min}$ | $g_{\rm max}$ | $\lambda$ | $\mu$ | Is      | V'       | V''      | Ι       |

|---------|-------|------|-------|-------|----------|--------|--------|------------|----------------|---------------|-----------|-------|---------|----------|----------|---------|

| 1       | 50    | 0.5  | 0.04  | 0.019 | 0.002143 | 0.5418 | 0.0184 | 0.6643     | 10.8366        | 4.4576        | 1         | 1     | 8.8644, | 45.5677, | 71.1108, | 5.5540, |

| 1       | 50    | 0.5  | 0.04  | 0.017 | 0.002145 | 0.5410 | 0.0104 | 0.0045     | 10.0500        | 4.4570        | 1         | 1     | 9.0461  | 45.477   | 72.251   | 5.5644  |

| 2       | 45    | 0.4  | 0.053 | 0.019 | 0.002143 | 0.5418 | 0.0184 | 0.3447     | 10.8366        | 4.0555        | 1.5       | 1     | 7.2370, | 42.1051, | 71.0471, | 4.1885, |

| 2       |       | 0.4  | 0.055 | 0.017 | 0.002145 | 0.5410 | 0.0104 | 0.5447     | 10.0500        | 4.0555        | 1.5       | 1     | 7.5524  | 41.979   | 72.209   | 4.284   |

| 3       | 40    | 0.45 | 0.053 | 0.019 | 0.002143 | 0.5418 | 0.0184 | 0.2932     | 10.8366        | 4.0481        | 1         | 1     | 8.6130, | 36.1241, | 70.9792, | 4.2574, |

| 5       | 40    | 0.45 | 0.055 | 0.019 | 0.002145 | 0.5410 | 0.0104 | 0.2932     | 10.8500        | 4.0401        | 1         | 1     | 9.0689  | 35.919   | 72.145   | 4.3792  |

TABLE IV

Case(II, a): Power loss numbers comparison

| Br. No. | MOSFET Loss<br>CVXPY | MOSFET Loss<br>LTSpice | Diode Loss<br>CVXPY | Diode Loss<br>LTSpice |

|---------|----------------------|------------------------|---------------------|-----------------------|

| 1       | 1.9218               | 2.0574                 | 3.9165              | 3.9462                |

| 2       | 1.5315               | 1.6724                 | 2.8280              | 2.9443                |

| 3       | 2.0358               | 2.2614                 | 2.9824              | 3.1069                |

following set of convex constraints

$$\min_{j \in [1, P_k]} \left\{ \beta_{k,j} I s_k^2 + \gamma_{k,j} I s_k \right\} \ge I s_k^2 \left( R_{\text{eff},1} - R_{\text{eff},2} \right) \cdots \\

\cdots + \left( I_k + I s_k \alpha_k \right)^2 \frac{R_k}{2} + \left( I s_k - s I_k \right)^2 \frac{|R_{M,k} - R_{D,k}|}{2} \cdots \\

\cdots + \alpha_k V_{\text{load}} I_k + V_{D,k} \left( I_k + \alpha_k I s_k \right) + I_k^2 R_{\text{eff},3} + V_{\text{load}} I_k \tag{35}$$

In essence, the above relaxation implies that the power generated by a power source is at least the sum total of the losses in the branch and the power delivered to the load by that branch. As mentioned earlier, the DCC's would operate in CCM if

Note that the expression above is a concave function as  $\beta_{k,j}$ 's are non-positive. Secondly, the term on the RHS of a constraint is convex as long as the conditions (22) hold. Thus, the seventh set of constraints last is replaced with the

$$Is_k \ge Is_{k,\min} \ \forall k. \tag{36}$$

|          | TABLE V                                                                                                                                       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| CASE (II | b): Circuit parameters and results (CVXPY, LTSPICE), $V_{\text{load}} = 70$ , $R_{\text{load}} = 5$ , $V_{\text{load}}$ from LTSPICE = 69.997 |

| Br. No. | $V_s$ | Rs   | $R_L$ | $R_M$ | α        | $V_D$  | $R_D$  | $I_{\min}$ | $V'_{\rm min}$ | $g_{\rm max}$ | $\lambda$ | $\mu$ | Is                | V'                 | V''                | Ι                 |

|---------|-------|------|-------|-------|----------|--------|--------|------------|----------------|---------------|-----------|-------|-------------------|--------------------|--------------------|-------------------|

| 1       | 50    | 0.5  | 0.04  | 0.019 | 0.002143 | 0.5418 | 0.0184 | 0.6643     | 10.8366        | 4.4576        | 1         | 1     | 8.8644,<br>8.8648 | 45.5677,<br>45.568 | 71.1108,<br>71.108 | 5.5540,<br>5.5536 |

| 2       | 45    | 0.4  | 0.053 | 0.019 | 0.002143 | 0.5418 | 0.0184 | 0.3447     | 10.8366        | 4.0555        | 1.5       | 1     | 7.2370,<br>7.2405 | 42.1051,<br>42.104 | 71.0471,<br>71.045 | 4.1885,<br>4.1899 |

| 3       | 40    | 0.45 | 0.053 | 0.019 | 0.002143 | 0.5418 | 0.0184 | 0.2932     | 10.8366        | 4.0481        | 1         | 1     | 8.6130,<br>8.6128 | 36.1241,<br>36.124 | 70.9792,<br>70.976 | 4.2574,<br>4.2561 |

TABLE VI

Case (III): Circuit parameters and results (CVXPY, LTSPICE),  $V_{\rm load} = 70, R_{\rm load} = 5, V_{\rm load}$  from LTSPICE = 69.997

| Br. No. | $V_s$ | Rs   | $R_L$ | $R_M$ | α      | $V_D$ | $R_D$ | Imin   | $V'_{\rm min}$ | $g_{\max}$ | $\lambda$ | $\mu$ | Is      | V'       | V''      | Ι       |

|---------|-------|------|-------|-------|--------|-------|-------|--------|----------------|------------|-----------|-------|---------|----------|----------|---------|

| 1       | 45    | 0.5  | 0.04  | 0.022 | 0.0027 | 0.7   | 0.018 | 0.5364 | 14             | 4.3648     | 1         | 1.5   | 9.1187, | 40.4407, | 71.0097, | 5.0485, |

| 1       |       | 0.5  | 0.04  | 0.022 | 0.0027 | 0.7   | 0.010 | 0.5504 | 14             | 4.5040     | 1         | 1.5   | 9.118   | 40.441   | 71.007   | 5.0469  |

| 2       | 50    | 0.4  | 0.053 | 0.025 | 0.0031 | 0.65  | 0.014 | 0.4244 | 13             | 3.9306     | 1.5       | 1     | 6.7501, | 47.3,    | 71.096,  | 4.3842, |

| 2       | 50    | 0.4  | 0.055 | 0.025 | 0.0051 | 0.05  | 0.014 | 0.4244 | 15             | 5.9500     | 1.5       | 1     | 6.7541  | 47.298   | 71.094   | 4.3867  |

| 3       | 42    | 0.45 | 0.053 | 0.019 | 0.0029 | 0.6   | 0016  | 0.3226 | 12             | 4.0561     | 1         | 1     | 8.7935, | 38.0429, | 71.0505, | 4.5674, |

| 5       | 42    | 0.45 | 0.055 | 0.019 | 0.0029 | 0.0   | 0010  | 0.3220 | 12             | 4.0501     | 1         | 1     | 8.793   | 38.043   | 71.047   | 4.5659  |

To prove tightness of the convex relaxation, the above lower bound on source current will converted into an equivalent lower bound on output current. That lower bound on output current  $I_{k,\min}$  can be obtained as the positive root of the equation

$$\min_{j \in [1, P_k]} \left\{ \beta_{k,j} I s_{k,\min}^2 + \gamma_{k,j} I s_{k,\min} \right\} = \cdots$$

...  $I s_{k,\min}^2 \left( R_{\text{eff},1} - R_{\text{eff},2} \right) + \left( I_{k,\min} + I s_{k,\min} \alpha_k \right)^2 \frac{R_k}{2} \dots$

...  $+ \left( I s_{k,\min} - s I_{k,\min} \right)^2 \frac{|R_{M,k} - R_{D,k}|}{2} + \alpha_k V_{\text{load}} I_{k,\min} \dots$

...  $+ V_{D,k} \left( I_{k,\min} + \alpha_k I s_{k,\min} \right) + I_{k,\min}^2 R_{\text{eff},3} + V_{\text{load}} I_{k,\min}.$

(37)

However, if such a root does not exist, there is no feasible solution to the optimization problem. With all the aforementioned modifications, one can see that the main optimization problem given in Figure 2 is obtained.

As the third step it will be shown that, at optimality (if it exists), the convex relaxations are tight. To begin with, consider the constraint in (35) previously mentioned. Suppose on the contrary, for some k, at the optimal point P = $\{V_1, \dots, V_m, V'_1, \dots, V'_m, V''_1, \dots, V''_m, Is_1, \dots, Is_m, I_1, \dots, I_m\},$  $\min_{j \in [1, P_k]} \{\beta_{k,j}Is_k^2 + \gamma_{k,j}Is_k\} > Is_k^2 (R_{\text{eff},1} - R_{\text{eff},2}) \cdots$  $\cdots + (I_k + Is_k\alpha_k)^2 \frac{R_k}{2} + (Is_k - sI_k)^2 \frac{|R_{M,k} - R_{D,k}|}{2} \cdots$  $\cdots + \alpha_k V_{\text{load}}I_k + V_{D,k} (I_k + \alpha_k Is_k) + I_k^2 R_{\text{eff},3} + V_{\text{load}}I_k$  (38)

Then, due to the continuity of the functions on either side of the constraint, there exists a  $\delta > 0$  such that the point  $P_{\delta} = \{V_1, \dots, V_m, \dots (V'_k + \delta R s_k) \dots, V''_1, \dots, V''_m, \dots (I s_k - \delta) \dots, I_1, \dots, I_m\}$  is a feasible point with a lower cost. The point  $P_{\delta}$  is feasible because a reduction in  $I s_k$  only increases the range for possible  $V s_k$  (see A1), and increases  $V'_k$ , thereby only requiring a reduction in gain of the  $k^{\text{th}}$  converter. However, the gain cannot go below 1 due to assumption A6. The reduction in cost can be reasoned as follows. A reduction in  $Is_k$  surely reduces all terms in the cost function, possibly except  $(Is_k - I_k)^2 \frac{R_{M,k}}{2}$ . But then, in a lossy boost converter  $Is_k > I_k$  and thus  $(Is_k - I_k)^2 \frac{R_{M,k}}{2}$  can only reduce with a reduction in  $Is_k$ . Thus, at optimality, the power constraint is tight. Since in the arguments of  $P_{\delta}$ , the DCC output voltages remain unchanged, the result holds good even with the additive cost of (26).

Lastly, note that the convex constraints pertaining to the VI-characteristics (given in (33)) need not be tight at optimality. In other words, the voltage at the output of the power sources need not be equal to the value prescribed by the VI-characteristics. Suppose, at optimality, for the  $k^{\rm th}$ converter,

$$\boldsymbol{V_k} < f_k \left( \boldsymbol{Is_k} \right). \tag{39}$$

Then, in that case,  $V_k$  can be increased to  $V_k + \delta$  where  $\delta = f_k (Is_k) - V_k$ ,  $V'_k$  to  $V'_k + \delta$  and the gain can be reduced to

$$\frac{V_{k}^{\prime\prime}}{V_{k}^{\prime}+f_{k}\left(Is_{k}\right)-V_{k}}\tag{40}$$

to maintain  $V_k''$ . Note that the gain remains greater than 1 due to A7 and all currents in the network also remain unchanged in this process. *Thus, one can find an optimal solution which adheres to the VI-characteristics.* Again, since these arguments left the DCC output voltages unchanged, the result holds good with additive cost of (26).

## III. COMPUTATIONS AND SIMULATIONS

This section presents computations in CVXPY and simulations on LTSpice. Three cases are presented: (i) the sources have non-linear VI-characteristics, (ii) the sources are constant voltage sources and the semiconductor characteristics are same across the DCCs, and (iii) the sources are constant voltage sources and the semiconductor characteristics are different across the DCCs. The optimal gains for all the cases are calculated using CVXPY and LTSpice simulations are presented. The LTSpice simulation for case (i) and (iii) consider an equivalent circuit which

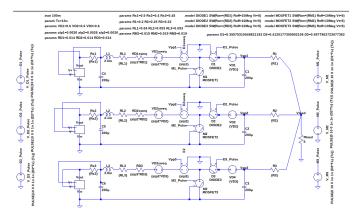

Fig. 3. Case (i): An equivalent circuit for case (i). The non-linear voltage sources is realized using the circuit shown in Figure 4.

Fig. 4. Case (i): The shown circuit realizes a concave and decreasing (w.r.t current) voltage source. With increasing current, a block of the voltage source with a resistance comes into effect, while it is bypassed until then. The increase in series voltage increases the intercept, while increase in series resistance increases the slope.

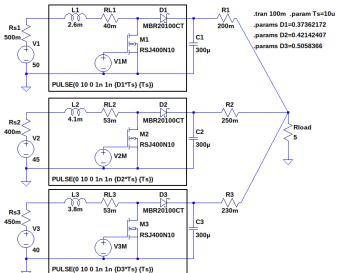

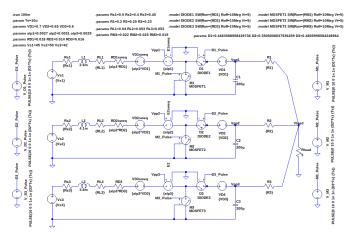

emulates the mathematical optimization model. The LTSpice simulations for case (ii) comprise two types: (a) simulation of a circuit with commercially available semiconductor components, and (b) simulation of an equivalent circuit, as mentioned earlier for other cases, which emulates the mathematical optimization model. In all the cases, the parameters of the circuit are assumed to be constant over the period of simulation. Table I present the parameters pertaining to the power sources for case (i), and Figure 3 & 4 present the circuits used for simulation on LTSpice. Table II presents the parameters pertaining to the other circuit elements and the numerical results from CVXPY & LTSpice. Table III and IV presents all the circuit parameters and results for case (ii,a). Similarly, the results for case (ii, b) are presented in Table V. The circuits for cases (ii, a) and (ii, b) are presented in Figure 5 and Figure 6, respectively. The circuit parameters and results from CVXPY for case(iii) are presented in Table VI.

For case (ii), the diode forward bias and the resistance are estimated by first subjecting the diode to a slow voltage ramp up to the rated voltage (see the circuit to the left in Figure 7). The current is recorded. The voltage and current are multiplied to get the instantaneous power consumed. The power curve is fitted with the form  $P(I) = V_D I + I^2 R_D$ using least squares, to obtain the forward bias voltage  $V_D$

Fig. 5. Case (ii, a): The LTSpice schematic shows three DCCs feeding power from three voltage sources with internal resistances to a resistive load. The semiconductor components (MOSFETs and diodes) are commercially available, and have been chosen appropriately as per the load voltage/current requirement. The simulation results for this circuit have been presented in Table III and IV.

Fig. 6. Case (ii, b): The LTSpice schematic shows equivalent circuits of three DCCs feeding power from three voltage sources with internal resistances to a resistive load. The semiconductor components (MOSFETs and diodes) are modeled as ideal switches with resistances/bias voltages, as applicable. The controlled voltage source aids in modeling the switching losses. The simulation results for this equivalent circuit have been presented in Table V.

and the resistance  $R_D$ . The multiplicative constants for deriving switching losses are estimated using the circuit shown to the right in Figure 7. The voltage source is set to

$$V_{\text{load}} + V_{D,k} + Is_{k,\min} (R_k + R_{D,k}),$$

(41)

since the voltage that would appear at the drain of the MOSFET in a DCC of the network would be at least this value. The current source is set to  $\frac{V_{\text{load}}}{3R_{\text{load}}}$ , since the exact current sharing isn't known prior to optimization. The circuit in Figure 5 is then simulated for several cycles (setting duty ratio to 0.5), and the average power dissipated in the MOS-

Fig. 7. A schematic of the test circuits used to estimate the parameters pertaining to the diode and the MOSFETs.

FET  $P_{\text{loss}}$ , and the rms-current through it  $I_{\text{rms}}$ , are recorded. Since the drain-to-source resistance of the MOSFET  $R_{M,k}$  can be read from its data-sheet, the multiplicative constant can be calculated as

$$\alpha_k = \frac{P_{\text{loss}} - 0.5 \left(\frac{V_{\text{load}}}{3R_{\text{load}}}\right)^2 R_{M,k}}{\left(V_{\text{load}} + V_{D,k} + \frac{V_{\text{load}}}{3R_{\text{load}}} \left(R_k + R_{D,k}\right)\right) \frac{V_{\text{load}}}{3R_{\text{load}}}}.$$

(42)

The equivalent circuit emulating the losses modeled in the optimization formulation is shown in Figure 4. The terms of the loss appearing with squared of the source currents appear on the primary side of the switch. The terms appearing with squared of the output currents appear on the secondary side. The switch itself is an ideal switch with a small ON resistance equal to the drain-source resistance of the MOSFET. Since an ideal switch has no switching loss, the switching loss terms require a voltage controlled voltage source to be included in the model, essentially to emulate the product term of the source current and the output current.

As expected, the quadratic convex constraints are all tight at optimality, in all cases. in addition, the voltages and currents obtained from LTSpice are also in close correspondence with the numbers obtained from CVXPY. However, for case (ii, a) the difference between the two sets of numbers (obtained from CVXPY and LTSpice) is more as compared to other cases, which can be attributed to modeling error of the semiconductor components.

## IV. FUTURE WORK

The convexity of the main optimization relies on certain conditions being satisfied by circuit parameters. Although, these conditions are often satisfied in practice, solving the otherwise non-convex problem is of considerable research interest. First is that the set of constraints given by (22), which may not be satisfied in generality. Secondly, the condition for CCM operation of DCC's is chosen as (30). However, a necessary and sufficient condition would be

$$Is_k \ge \frac{V'_k}{2L_k f_s} \left(1 - \frac{I_k}{Is_k}\right), \ \forall k.$$

(43)

However, this is a non-convex constraint and makes the optimization problem harder.

The losses considered in the paper are not comprehensive. For example, the core losses in the inductor, the loss in the diodes due to reverse recovery current, the losses in through the output capacitances of the MOSFETs have not been considered. Although these are typically small as compared to the losses considered, their inclusion makes the treatment closer to reality. This might also be an interesting direction for future research.

The stability aspects of such a interconnected system is also an important matter for consideration, which is presently out of the scope of this paper. Although, simulations are indicative of a stable system, an analytical proof is desirable. This problem (seen in the sense of average models) in cases (ii) and (iii) boils down to finding checkable conditions for the stability of the set of matrices given by  $\{u_1A_1 + u_2A_2 + \cdots + u_nA_n | 0 \le u_1, u_2, \cdots, u_n \le 1\}$ . In case (i), the problem becomes harder due to the involvement of nonlinear voltage sources.

The presented methodology requires a communication between a central controller, which measures the parameters and runs the optimization routine, and the DCC's which actuate as per the set point communicated. Thus, a study along the lines of decentralized control might be of much importance. It might also be of interest to extend the presented approach to similar load-balancing systems with other converter classes, such as buck and buck-boost. This would call for the losses in the DCC and the bounds on gains to be appropriately accounted for.

#### REFERENCES

- [1] S. Augustine, M. K. Mishra, and N. Lakshminarasamma, "Adaptive droop control strategy for load sharing and circulating current minimization in low-voltage standalone dc microgrid," *IEEE Transactions* on Sustainable Energy, vol. 6, no. 1, pp. 132–141, 2014.

- [2] P. Prabhakaran, Y. Goyal, and V. Agarwal, "Novel nonlinear droop control techniques to overcome the load sharing and voltage regulation issues in dc microgrid," *IEEE Transactions on power electronics*, vol. 33, no. 5, pp. 4477–4487, 2017.

- [3] R. A. Jabr, "Mixed-integer convex optimization for dc microgrid droop control," *IEEE Transactions on Power Systems*, 2021.

- [4] R. W. Erickson and D. Maksimovic, *Fundamentals of power electronics*. Springer Science & Business Media, 2007.

- [5] S. Boyd and L. Vandenberghe, *Convex optimization*. Cambridge university press, 2004.

- [6] N. Mohan and T. M. Undeland, Power electronics: converters, applications, and design. John Wiley & Sons, 2007.

- [7] D. G. Holmes and T. A. Lipo, Pulse width modulation for power converters: principles and practice. John Wiley & Sons, 2003, vol. 18.

- [8] S. Diamond and S. Boyd, "Cvxpy: A python-embedded modeling language for convex optimization," *The Journal of Machine Learning Research*, vol. 17, no. 1, pp. 2909–2913, 2016.

- [9] Rohm, "Efficiency of buck converter," Rohm Semiconductor Application Notes, 2016.