# arXiv:2206.00644v1 [cond-mat.mes-hall] 1 Jun 2022

# An extraction method for mobility degradation and contact resistance of graphene transistors

Anibal Pacheco-Sanchez, Nikolaos Mavredakis, Pedro C. Feijoo, David Jiménez

## Abstract

The intrinsic mobility degradation coefficient, contact resistance and the transconductance parameter of graphene field-effect transistors (GFETs) are extracted for different technologies by considering a novel transport model embracing mobility degradation effects within the charge channel control description. By considering the mobility degradation-based model, a straightforward extraction methodology, not provided before, is enabled by applying the concept of the well-known *Y*-function to the *I-V* device characteristics. The method works regardless the gate device architecture. An accurate description of experimental data of fabricated devices is achieved with the underlying transport equation by using the extracted parameters. An evaluation of the channel resistance, enabled by the extracted parameters here, has been also provided.

### **Index Terms**

graphene FET, mobility degradation, contact resistance, channel resistance, Y-function.

### I. INTRODUCTION

One of the most popular approaches for the characterization of graphene field-effect transistors (GFETs) has been the description of experimental data by a device total resistance  $R_{tot}$  model [1]. This model considers the impact of vertical fields and impurities on the carrier transport and has enabled to obtain relevant device parameters since its proposal, e.g., a low-field mobility [2]-[4]. Recently, this well-known model has been adapted in order to explicitly consider mobility degradation effects in the performance description of GFET technologies [5]. This novel approach has been motivated by experimental observations of a carrier density-dependent mobility in GFETs under different scenarios [6]-[8]. Hence, a first-order mobility model considers both, short- and long-range scattering mechanisms in graphene devices by including an intrinsic mobility degradation coefficient  $\theta_{ch}$  into the mobility description, similarly to the approach used in MOSFET theory [9]-[11]. Additionally, a potential drop at the metal-graphene interface has been considered by a contact resistance  $R_c$  in order to describe the internal transport phenomena.

From a device characterization point of view, the fitting procedure relying on an initial guess of  $R_c$  towards obtaining the other three model parameters in [5] might become an important constraint for the characterization of GFETs at a large scale due to the computational burden and challenges related to randomly finding adequate initial values. A straightforward parameter extraction methodology considering experimental data is required to expand and ease the use of this novel modeling-based characterization approach. In this work, by following a methodical treatment of experimental data based on the concept of the well-known Y-function, a parameter extraction methodology for the mobility degradation-based transport model is proposed using individual device transfer characteristics of a given GFET technology with devices of different gated-channel lengths. In contrast to the original approach [5], the extraction methodology proposed here is more robust for device characterization purposes since it yields values of three out of four of the model parameters without needing any initial random assumption. The fourth parameter, related to charge-neutrality, is extracted by appropriately adjusting the model to experiments at very low transversal electric fields.

By considering the characterization of GFET technologies including sub- $\mu$ m gate-lengths, the model-based characterization is proven here to be for general purposes and not only for long devices as shown in [5]. Further adaptations of the underlying model to include velocity saturation effects -relevant at high lateral fields- are out of the scope of this work, however, the extracted parameters here can be relevant for the extraction of velocity saturation related parameters. In contrast to previous GFET studies using *Y*-function-based methods [12]-[15], this work relies on a transport current description including a charge definition more related to GFETs physics rather than the conventional MOSFET charge equation. The extracted parameters enable an evaluation of the mobility and an accurate description of the drain current over a wide transversal electric field range including charge neutrality conditions.

This straightforward extraction methodology of contact resistance and mobility parameters of graphene technologies can be applied to any gate architecture. Hence, it is an immediate efficient alternative to test-structure-based extraction methodologies such as the transfer length method (TLM) [16], limited to global-back-gate (GBG) devices only. The latter limitation can mislead performance projections based on TLM for other device architectures in which the different electrostatics, e.g., from a top- (TG) [17] or buried-gate (BG) [18], might affect the Schottky-like potential barrier height at graphene-metal contacts

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. DOI: 10.1109/TED.2022.3176830

This work has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreements No GrapheneCore3 881603, from Ministerio de Ciencia, Innovación y Universidades under grant agreement RTI2018-097876-B-C21(MCIU/AEI/FEDER, UE) and FJC2020-046213-I. This article has been partially funded by the European Union Regional Development Fund within the framework of the ERDF Operational Program of Catalonia 2014-2020 with the support of the Department de Recerca i Universitat, with a grant of 50% of total cost eligible. GraphCAT project reference: 001-P-001702.

The authors are with the Departament d'Enginyeria Electrònica, Escola d'Enginyeria, Universitat Autònoma de Barcelona, Bellaterra 08193, Spain, e-mails: AnibalUriel.Pacheco@uab.cat, David.Jimenez@uab.cat

[19], [20], i.e., the value of  $R_c$ . Furthermore, the fabrication issues of individual TG and BG [18] graphene devices, implies a more challenging fabrication of TLM structures (including a series of individual devices) for such configurations. The TLM-related constraints are overcome by the method presented here since (i) the particular device electrostatics is considered in the underlying transport description and (ii) no fabrication of extra test structures is required.

### II. PARAMETERS EXTRACTION METHODOLOGY

The drain current  $I_D$  of GFETs given by a straightforward adaptation of a widely used *I-V* model [1] considering both an appropiate charge control description and an explicit contribution of the extrinsic mobility degradation coefficient  $\theta$  [10], [21], [22] is expressed as<sup>1</sup> [5]

$$I_{\rm D} = \beta \frac{\sqrt{V_0^2 + V_{\rm GSO}^2}}{1 + \theta \sqrt{V_0^2 + V_{\rm GSO}^2}} V_{\rm DS},\tag{1}$$

where  $\beta$  is a transconductance parameter associated to  $\mu_{app,0}C_{ox}w_g/L_g$  [22] with  $\mu_{app,0}$  as an apparent low-field mobility,  $C_{ox}$  as the gate oxide capacitance per unit area,  $w_g$  as the gate width and  $L_g$  as the gated-channel length,  $V_{GSO} = V_{GS} - V_{Dirac}$  is the extrinsic gate-to-source voltage overdrive with  $V_{GS}$  as the extrinsic gate-to-source voltage and  $V_{Dirac}(=V_{GS}|_{\min(I_D)})$  as the  $V_{GS}$  corresponding to charge neutrality conditions,  $V_0 = qn_0/C_{ox}$  the residual voltage with q as the electron charge,  $n_0$  as the residual charge carrier density at  $V_{Dirac}$  [1],  $\theta = \theta_{ch} + \beta R_c$  with  $\theta_{ch}$  as the intrinsic mobility degradation coefficient due to vertical fields [9]-[11] and the contact resistance  $R_c (= R_{cs} + R_{cd})$  embracing the phenomena at metal-channel interfaces (source and drain sides). Notice that Eq. (1) can be also obtained from the drift-diffusion transport description for graphene transistors [23] after neglecting the quantum capacitance and the local channel voltage at low  $V_{DS}$ .

Based on Eq. (1) and by considering that  $V_{\rm GSO} \gg V_0$ , the transconductance  $g_{\rm m} = \partial I_{\rm D} / \partial V_{\rm GS}$  is given by

$$g_{\rm m} \approx \beta \frac{1}{\left(1 + \theta \sqrt{V_0^2 + V_{\rm GSO}^2}\right)^2} V_{\rm DS},\tag{2}$$

while the device total resistance  $R_{\rm tot} = V_{\rm DS}/I_{\rm D}$ , considering the definition of  $\theta$ , reads

$$R_{\rm tot} = \underbrace{\left(\frac{1}{\beta\sqrt{V_0^2 + V_{\rm GSO}^2}} + \frac{\theta_{\rm ch}}{\beta}\right)}_{R_{\rm ch}} + R_{\rm c}.$$

(3)

A comparison with the general definition of  $R_{tot}$  as the sum of channel resistance  $R_{ch}$  and  $R_c$ , and by considering that  $\theta_{ch}$  is associated to channel phenomena [9]-[11], leads to relate the term inside brackets in Eq. (3) as  $R_{ch}$  in the context of this work. The latter is confirmed by considering two channel scattering mechanisms (cf. Eq. (3) in [5]) in the underlying transport model (cf. Eq. (3) in [1])<sup>2</sup>.

By applying the concept of the Y-function [22], [24], i.e.,  $Y = I_D / \sqrt{g_m}$ , with Eqs. (1) and (2), this relation yields

$$Y \approx \sqrt{\beta V_{\rm DS}} \sqrt{V_0^2 + V_{\rm GSO}^2},\tag{4}$$

while the product of Eqs. (3) and (4) corresponds to

$$R_{\rm tot}Y \approx \sqrt{\frac{V_{\rm DS}}{\beta}} + \frac{\theta}{\beta}Y.$$

(5)

The ratio  $\theta/\beta$  and the parameter  $\beta$  can be extracted from the plots of  $R_{tot}Y$  vs. Y and  $Y^2$  vs.  $V_{GSO}^2$ , respectively, for different  $L_g$  and at a fixed low  $V_{DS}$ . By following the definition of  $\theta$  given above,  $\theta_{ch}$  and  $R_c$  are extracted from the intercept at zero and slope of a  $\beta$ -dependent plot of  $\theta$ . While the extraction of  $\beta$ ,  $\theta_{ch}$  and  $R_c$  is performed at an unipolar bias region away from  $V_{Dirac}$ , the underlying model can be adjusted towards describing charge neutrality conditions. Hence, a unique value for  $V_0$  is obtained from the best adjustment of the model to experimental data at the bias region close to  $V_{Dirac}$ , upon extraction of all other parameters.

The extraction method yields a constant  $R_c$  value which can be of special interest for technology evaluation [3] as well as an initial guide for modeling purposes towards the design of specific applications at a fixed bias point, e.g., high-frequency circuits<sup>3</sup> [25], [26]. For the interested reader, a bias-dependent contact resistance model, which is out of the scope of this work, has been reported elsewhere [19]. Notice that despite Eq. (5) resembles the approach presented in [27] for silicon technologies, both the underlying transport equation and the extraction methodology are different in this work.

<sup>&</sup>lt;sup>1</sup>Notice that  $\theta$  has been called  $\theta_{\text{eff}}$  in [5].

$<sup>^{2}</sup>R_{\text{tot}} = (N_{\text{sq}}/\mu_{0})(1/qn + \theta_{\text{ch}}/C_{\text{ox}}) + R_{\text{c}} \equiv R_{\text{ch}} + R_{\text{c}}$ , with the number of squares  $N_{\text{sq}} = L_{\text{g}}/w_{\text{g}}$

<sup>&</sup>lt;sup>3</sup>In general, GFETs are fixed at  $|V_{\rm GS} - V_{\rm Dirac}| \gg 0$  in practical scenarios where a high transconductance in an unipolar region benefits the dynamic performance.

# III. CHARACTERIZATION OF GFET TECHNOLOGIES

The parameter extraction methodology described above has been applied to the experimental data of GFET technologies with different device architectures such as GBG [28], [29], BG [17], [23] and TG [30] as well as with different sub-µm- and µm-long gate lengths. Device characteristics and extracted parameters are listed in Table I.

| gate arch.<br>& ref. | $egin{array}{c} w_{ m g} \ (\mu{ m m}) \end{array}$ | $L_{ m g} \ (\mu{ m m})$                               | $\begin{array}{c} \theta_{\rm ch} \\ ({\rm V}^{-1}) \end{array}$ | $egin{array}{c} R_{ m c} \cdot w_{ m g} \ ({ m k} \Omega \cdot \mu { m m}) \end{array}$ |

|----------------------|-----------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| GBG, [28]            | 5                                                   | $\begin{array}{c} 0.120, 0.225,\\ 0.640, 2\end{array}$ | 0.025                                                            | 2.9                                                                                     |

| GBG, [29]            | 20                                                  | $5, 10, 15 \\20, 25, 30$                               | 0.034                                                            | 1.6                                                                                     |

| BG, [17]             | _                                                   | 0.250, 0.450                                           | 1.5                                                              | $0.2 \cdot w_{ m g}$                                                                    |

| BG, [23]             | 12                                                  | 0.1, 0.2, 0.3                                          | 3.1                                                              | 2.6                                                                                     |

| TG, [30]             | 3.4                                                 | $0.1, 0.3, \\ 1, 2$                                    | 0.081                                                            | 0.4                                                                                     |

TABLE I

CHARACTERISTICS AND EXTRACTED MODEL PARAMETERS OF GFETS.

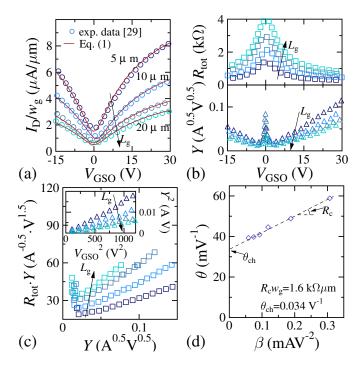

The extraction procedure is depicted in Fig. 1 with experimental data of GBG devices reported elsewhere [29]. Only the *n*-type region ( $V_{\rm GSO} > 0$ ) has been used for the extraction. From the experimental transfer characteristics of GFETs with different  $L_{\rm g}$  and at a given  $V_{\rm DS}$ , plots of  $R_{\rm tot}$  and the Y-function have been obtained (Fig. 1(b)). The product of  $R_{\rm tot}$  and Y has been ploted over Y (Fig. 1(c)) in order to obtain the ratio  $\theta/\beta$  from the slope of the linear part of each curve (at  $Y > Y|_{\min(R_{\rm tot}Y)}$ ), i.e., for each  $L_{\rm g}$ , as indicated by Eq. (5). Similarly, the slopes of the curves in the  $Y^2(V_{\rm GSO}^2)$ -plot (inset of Fig. 1(c)) yield the parameter  $\beta$ . The contact resistance and the intrinsic mobility degradation coefficient are obtained from the  $\theta(\beta)$  plot (Fig. 1(d)). In order to validate the extracted parameters, the model with the extracted parameters succesfully describes the experimental transfer characteristics, provided  $V_0$  is obtained, as shown in Fig. 1(a).

Fig. 1. Extraction methodology presented in this work applied to the GBG GFET technology presented in [29]. (a) Transfer characteristics, (b) total resistance (top) and Y-function (bottom) plots over  $V_{\text{GSO}}$ , (c)  $R_{\text{tot}}Y$  and  $Y^2$  (inset) over Y and  $V_{\text{GSO}}^2$ , respectively and (d)  $\theta$  over  $\beta$  plot showing the extracted parameters  $R_c$  and  $\theta_{ch}$ . Markers represent experimental data and solid lines represent Eq. (1) results by using the extracted parameters. Dashed lines are added as guides for the eyes in order to show the extracted parameters.  $V_{\text{DS}} = 0.05 \text{ V}$  for all plots.

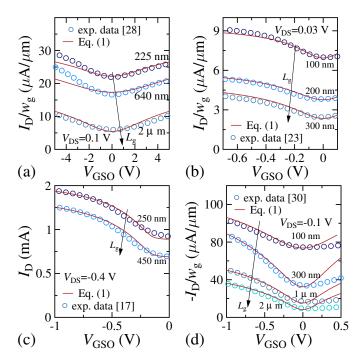

By using the corresponding extracted parameters (cf. Table I), the mobility degradation-based transport model describes the experimental transfer characteristics of the other GFET technologies studied here within the bias region where the extraction methodology has been applied in each case as shown in Fig. 2. The values of  $\mu_{app,0}$  for the shortest devices in the BG technologies presented in this work are of  $2079 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  for [17] and of  $2580 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  for [23]. These values are similar to the ones reported in the literature:  $2000 \text{ to } 2500 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  for the former one [17] and of  $3250 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , reported with Hall measurements in [32], for the latter [23].

The impact of velocity saturation, out of the scope of this modeling approach, can further improve the model adjustment. E.g., if a simple velocity saturation model for an effective mobility  $\mu_{\text{eff}}(=\mu/(1+E_x/E_c))$  is considered, where  $\mu$  includes mobility degradation effects as Eq. (1) in [5] and  $E_x$  and  $E_c$  are the horizontal and critical electric field, respectively, the related velocity saturation parameters can be extracted at high  $V_{\rm DS}$  regime provided that all the other parameters, i.e.,  $\theta$ ,  $R_c$  and  $\beta$  have been estimated from a lower  $V_{\rm DS}$  region with the extraction method presented here. A similar approach for the estimation of velocity saturation effects has been presented elsewhere [4].

Fig. 2. Transfer characteristics of GFET technologies with different architectures: (a) GBG [28], (b) BG [23], (c) BG [17] and (d) TG [30]. Markers represent experimental data and solid lines represent modeling results by using the extracted parameters in Eq. (1).

The pronounced asymmetry in experimental transfer characteristics (cf. Figs. 2(a) and (d)) due to different mobility and contact properties observed in the devices of [28] and [30] is not captured by the model. Hence, slight discrepancies are observed in the unipolar region where the extraction has not been performed, i.e., *p*-type in [28] and *n*-type region in [30]. In this case, a new parameter set obtained by applying the extraction method at the bias conditions of interest can be used to overcome the disagreement due to asymmetric device features. For the GBG (TG) device in [28] ([30]), the extraction methodology applied for the *p*-type (*n*-type) region yields values of  $R_c \cdot w_g$  equal to  $0.8 \text{ k}\Omega \cdot \mu\text{m}$  (0.65 k $\Omega \cdot \mu\text{m}$ ) and of  $\theta_{ch}$  equal to  $0.04 \text{ V}^{-1}$  (0.29 V<sup>-1</sup>). The different current levels in each part of the transfer curves (Fig. 2(a) and (d)) of the device in [28] ([30]) are associated to the lower (higher)  $R_c \cdot w_g$  extracted value for the *p*-type (*n*-type) region in contrast to the one obtained for the *n*-type (*p*-type) region (cf. Table I). Additionally, the weaker gate control over the channel observed for the TG device [30] at  $V_{GSO} > 0$  V than at  $V_{GSO} < 0$  V is quantified by an extracted  $\theta_{ch}$  value which is ~ 3.6 higher than the one extracted for the *n*-type region.

Regarding the extracted  $R_c$  values, for the GBG technology with relaxed dimensions, the extracted value of  $R_c$  (cf. Fig. 1(b)) is in good agreement with the one obtained by TLM in [29] considering the bias region where the methods have been applied, i.e.,  $9 V < V_{GSO} < 37 V$ . In the case of the BG GFET reported in [23], the slight difference ( $\sim 30 \Omega$ ) between the extracted  $R_c$  value here and the one obtained by the adjustment of a compact model is related to different underlying transport equations. The extraction of  $R_c$  with this methodology for all kind of device architectures overcomes the challenging fabrication of TLM test structures which are generally limited to GBG devices [16], specially in graphene technologies [12], [29]. Values of  $\theta_{ch}$  for GFETs have been rarely reported in the literature with other methods [14]. Regarding the GFETs analyzed here, GBG devices have the lower  $\theta_{ch}$  owing to the full-gated channels in contrast to BG and TG devices, and hence, a better overall gate control over the channel is obtained with the former device architecture. It is worth to notice that in the device technologies studied here,  $\theta_{ch}$  is not negligible for the definition of  $\theta$  as suggested elsewhere for 2D-based devices [31]. The latter is of key importance to determine whether the device performance is dominated by channel or contact phenomena [14].

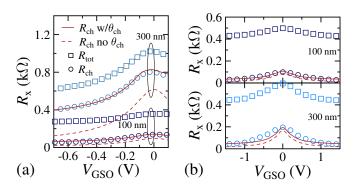

The experimental device channel resistance BG GFET technology reported in [23], obtained upon extraction of  $R_c$ , is well described by the modeling approach followed here, i.e., considering  $\theta_{ch}$  into its description (c.f. Eq. (3)), as shown in Fig. 3(a). The experimental  $R_{tot}$  curves have been included in the plot for comparison purposes. Modeling results of  $R_{ch}$  without including  $\theta_{ch}$  fail to describe the experimental data: the maximum (minimum) error between model without  $\theta_{ch}$  is of ~ 60% (~ 25%) in contrast to the ~ 15% (~ 0.5%) maximum (minimum) relative error for the  $R_{ch}$  model considering  $\theta_{ch}$ , all values for the region where the parameter extraction has been performed for these devices, i.e., for  $V_{GSO} < 0$  V.

Numerical device simulations (NDS) have been performed in order to further explore the channel resistance description. The simulated GFETs under study have gated-channels (of lengths of 100 nm and 300 nm and a width of  $1 \mu \text{m}$ ) encapsulated in a hexagonal-boron nitride dielectric. Mobility degradation due to vertical fields has been considered. The contact resistance value is set to  $400 \Omega$ . The model used in simulations consists in the self-consistent solution of the Poisson's equation together

Fig. 3. Resistances of (a) fabricated ( $V_{\rm DS} = 0.03 \,\mathrm{V}$ ) [23] and (b) simulated ( $V_{\rm DS} = 0.1 \,\mathrm{V}$ ) GFETs with different  $L_{\rm g}$ . Solid (dashed) lines are modeling results of  $R_{\rm ch}$  considering (not considering)  $\theta_{\rm ch}$ . Legend in (a) applies to (b).

with the current continuity equation, where the properties of carrier transport have been previously extracted from Monte Carlo simulations [13], [33]. Simulation results, shown in Fig. 3(b), reveal that the devices total resistance is mainly due to the injection mechanisms ( $R_c > R_{ch}$ ). The extraction method has been applied to the NDS data yielding an  $R_c$  value of 397  $\Omega$  and a  $\theta_{ch}$  of  $1 \text{ V}^{-1}$ . The channel resistance obtained from the simulation data by  $R_{ch} = R_{tot} - 400 \Omega$  has been better described by an  $R_{ch}$  model considering  $\theta_{ch}$  (maximum/minimum error of  $\sim 30\%/3\%$  at the region used for extraction) in contrast to the approaches suggested elsewhere [5], [31] where  $\theta_{ch}$  has been neglected as a channel transport parameter (maximum/minimum error of  $\sim 55\%/30\%$  at the region used for extraction).

Hence, in addition to the conceptual relation of  $\theta_{ch}$  to channel phenomena (and corresponding parameters) and the discussion provided above, the results presented here suggest that the term including  $\theta_{ch}$  should be accounted for an accurate description of  $R_{ch}$ . The  $L_g$  independence of  $R_c$ , implied with the latter approach, has been also confirmed with experimentally calibrated physics-based contact models of GFETs [19], [20]. In other words, in contrast to a previous proposal where the  $R_c$  value varies with  $L_g$ , the effect of a gate electrostatics-dependent effective length of the potential step (in the transport direction) at metal-graphene interfaces [19], [34] has been associated in this approach to the transport within the channel rather than to contact effects.

## IV. CONCLUSION

A parameter extraction methodology of a novel model considering mobility degradation effects in GFETs has been provided. The underlying transport model using the extracted parameters, namely  $R_c$ ,  $\theta_{ch}$  and  $\beta$ , describes accurately the experimental data of various short- and long-gate GFET technologies at different bias conditions regardless the gate architecture. The latter is of relevance for leveraging the challenging fabrication of test structures for parameter extraction. The engineering approach proposed with this extraction method relies entirely on a mathematical treatment of the experimental transfer characteristic enabled by a mobility degradation-based modeling proposal, i.e., no initial fitting parameters are required. The mobility degradation description enabled by the extracted parameters can be useful for technology evaluation and modeling purposes as shown in this work. A modeling approach including  $\theta_{ch}$  in the description of the channel resistance has been proven to yield more accurate results than the case where  $\theta_{ch}$  is not considered into  $R_{ch}$ . The extracted parameters can be included in compact models. The extracted constant value of  $R_c$  can be exploited in practical small-signal GFET modeling approaches where devices are biased at a certain operation regime.

### REFERENCES

- S. Kim, J. Nah, I. Jo, D. Shahrjerdi, L. Colombo, Z. Yao, E. Tutuc, S. K. Banerjee, "Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric", *Applied Physics Letters*, vol. 94, no. 9, Feb. 2009. DOI: 10.1063/1.3077021

L. Liao, J. Bai, Y. Qu, Y. Lin, Y. Li, Y. Huang, X. Duan, "High-k oxide nanoribbons as gate dielectrics for high mobility top-gated graphene

- [2] L. Liao, J. Bai, Y. Qu, Y. Lin, Y. Li, Y. Huang, X. Duan, "High-k oxide nanoribbons as gate dielectrics for high mobility top-gated graphene transistors", *Proceedings of the National Academy of Sciences of the United States of America*, vol. 107, no. 15, pp. 6711-6715, Apr. 2010. DOI: 10.1073/pnas.0914117107

- [3] Y.-H. Wu, P.-Y. Tseng, P.-Y. Hsieh, H.-T. Chou, N.-H. Tai, "High Mobility of Graphene-Based Flexible Transparent Field Effect Transistors Doped with TiO2 and Nitrogen-Doped TiO2", ACS Applied Materials & Interfaces, vol. 7, no. 18, pp. 9453-9461, Apr. 2015. DOI: 10.1021/am508996r

- [4] N. Mavredakis, W. Wei, E. Pallecchi, D. Vignaud, H. Happy, R. G. Cortadella, N. Schaefer, A. B. Calia, J. A. Garrido, D. Jimenez, "Low-Frequency Noise Parameter Extraction Method for Single-Layer Graphene FETs", *IEEE Transactions on Electron Devices*, vol. 67, no. 5, pp. 2093-2099, May 2020. DOI: 10.1109/TED.2020.2978215

- [5] K. Jeppson, M. Asad, J. Stake, "Mobility Degradation and Series Resistance in Graphene Field-Effect Transistors", *IEEE Transactions on Electron Devices*, vol. 68, no. 6, pp. 3091-3095, Jun. 2021. DOI: 10.1109/TED.2021.3074479

- [6] W. Zhu, V. Perebeinos, M. Freitag, and P. Avouris, "Carrier scattering, mobilities, and electrostatic potential in monolayer, bilayer, and trilayer graphene", *Physical Review B*, vol. 80, no. 23, 235402, Dec. 2009. DOI: 10.1103/PhysRevB.80.235402.

- [7] V. E. Dorgan, M.-H. Bae, E. Pop, "Mobility and saturation velocity in graphene on SiO2", Applied Physics Letters, vol. 97, no. 8, Art. no. 082112, Aug. 2010. DOI: 10.1063/1.3483130.

- [8] H. Zhong, Z. Zhang, H. Xu, C. Qiu, and L.-M. Peng, "Comparison of mobility extraction methods based on field-effect measurements for graphene", *AIP Advances*, vol. 5, no. 5, Art. no. 057136, May 2015. DOI: 10.1063/1.4921400.

- [9] G. Merckel, J. Borel, N. Z. Cupcea, "An accurate large-signal MOS transistor model for use in computer-aided design", *IEEE Transactions on Electron Devices*, vol. 19, no. 5, pp. 681–690, 1972. DOI: 10.1109/T-ED.1972.17474

- [10] L. Risch, "Electron mobility in short-channel MOSFET's with series resistances", IEEE Transactions on Electron Devices, vol. 30, no. 8, pp. 959-961, Aug. 1983. DOI: 10.1109/T-ED.1983.21246.

- [11] C. C. Enz, E. A. Vittoz, "Charge-based MOS Transistor Modeling", John Wiley & Sons, 2006.

- [12] F. Urban, G. Lupina, A. Grillo, N. Martucciello, A. Di Bartolomeo, "Contact resistance and mobility in back-gate graphene transistors", *Nano Express*, vol. 1, no. 1, 010001, Mar. 2020. DOI: 10.1088/2632-959X/ab7055

- [13] A. Pacheco-Sanchez, P. C. Feijoo, D. Jiménez, "Contact resistance extraction of graphene FET technologies based on individual device characterization", Solid-State Electronics, vol. 172, 107882, Oct., 2020. DOI: 10.1016/j.sse.2020.107882

- [14] A. Pacheco-Sanchez, D. Jiménez, "Accuracy of Y-function methods for parameters extraction of two-dimensional FETs across different technologies", *Electronics Letters*, vol. 56, no. 18, pp. 942-945, Sep. 2020. DOI: 10.1049/el.2020.1502

- [15] A. Pacheco-Sanchez, D. Jiménez, "A contact resistance extraction method of 2D-FET technologies without test structures", in Proc. IEEE Spanish Conference on Electron Devices (CDE), pp. 19-22, 2021. DOI: 10.1109/CDE52135.2021.9455755

- [16] D. Schroder, "Semiconductor material and device characterization", Wiley-IEEE Press, 2006.

- [17] S.-J. Han, S. Oida, K. A. Jenkins, D. Lu, Y. Zhu, "Multifinger Embedded T-Shaped Gate Graphene RF Transistors With High fMAX/fT Ratio", IEEE Electron Device Letters, vol. 34, no. 10, pp. 1340-1342, Oct. 2013. DOI: 10.1109/LED.2013.2276038

- [18] S. K. Lee, Y. J. Kim, S. Heo, W. Park, T. J. Yoo, C. Cho, H. J. Hwang, B. H. Lee, "Advantages of a buried-gate structure for graphene field-effect transistor", Semiconductor Science and Technology, vol. 34, 055010, Apr. 2019. DOI: 10.1088/2053-1583/aba449

- [19] F. A. Chaves, D. Jiménez, A. A. Sagade, W. Kim, J. Riikonen, H. Lipsanen, D. Neumaier, "A physics-based model of gate-tunable metal-graphene contact resistance benchmarked against experimental data", 2D Materials, vol. 2, no. 2, 025006, May 2015. DOI: 10.1088/2053-1583/2/2/025006

- [20] B. Wang, M. W. Malik, Y. Yan, V. Kilchytska, Y. Zeng, D. Flandre, J.-P. Raskin, "A Physical Model of Contact Resistance in Ti-Contacted Graphene-Based Field Effect Transistors", *IEEE Transactions on Electron Devices*, vol. 68, no. 2, pp. 892-898, Feb. 2021. DOI: 10.1109/TED.2020.3046166

- [21] C. Hao, B. Cabon-Till, S. Cristoloveanu, G. Ghibaudo, "Experimental determination of short-channel MOSFET parameters", Solid-State Electronics, vol. 28, no. 10, pp. 1025-1030, 1985. DOI: 10.1016/0038-1101(85)90034-6

- [22] G. Ghibaudo, "New method for the extraction of MOSFET parameters", *Electronics Letters*, vol. 24, no. 9, pp. 543-545, 1988. DOI: 10.1049/el:19880369

[23] N. Mavredakis, W. Wei, E. Pallecchi, D. Vignaud, H. Happy, R. G. Cortadella, A. B. Calia, J. A. Garrido, D. Jiménez, "Velocity Saturation Effect on Low Frequency Noise in Short Channel Single Layer Graphene Field Effect Transistors", *ACS Applied Electronic Materials*, vol. 1, pp. 2626-2636, 2019. DOI: 10.1021/acsaelm.9b00604

- [24] S. Jain, "Measurement of threshold voltage and channel length of submicron MOSFETs", *IEE Proceedings I (Solid-State and Electron Devices)*, vol. 135, no. 6, pp. 162–164, 1988. DOI: 10.1049/ip-i-1.1988.0029

- [25] A. Pacheco-Sanchez, J. N. Ramos-Silva, E. Ramírez-García, D. Jiménez "A Small-Signal GFET Equivalent Circuit Considering an Explicit Contribution of Contact Resistances", *IEEE Microwave and Wireless Components Letters*, vol. 31, no. 1, pp. 29-32, Jan. 2021. DOI: 10.1109/LMWC.2020.3036845

- [26] A. Hamed, M. Asad, M. -D. Wei, A. Vorobiev, J. Stake, R. Negra, "Integrated 10-GHz Graphene FET Amplifier", *IEEE Journal of Microwaves*, Jun. 2021. DOI: 10.1109/JMW.2021.3089356.

- [27] R. Trevisoli, R. Trevisoli Doria, M. de Souza, S. Barraud, M. Vinet, M. Cassé, G. Reimbold, O. Faynot, G. Ghibaudo, M. A. Pavanello, "A New Method for Series Resistance Extraction of Nanometer MOSFETs", *IEEE Transactions on Electron Devices*, vol. 64, no. 7, pp. 2797-2803, Jul. 2017. DOI: 10.1109/TED.2017.2704928

- [28] S.-J. Han, Z. Chen, A. A. Bol, Y. Sun, "Channel-Length-Dependent Transport Behaviors of Graphene Field-Effect Transistors", IEEE Electron Device Letters, vol. 32, no. 6, pp. 812-814, Jun. 2011. DOI: 10.1109/LED.2011.2131113

- [29] A. Gahoi, S. Kataria, F. Driussi, S. Venica, H. Pandey, D. Esseni, L. Selmi, M. C. Lemme, "Dependable Contact Related Parameter Extraction in Graphene-Metal Junctions", *Advanced Electronic Materials*, vol. 6, 2000386, Sep. 2020. DOI: 10.1002/aelm.202000386

[30] J. Bai, L. Liao, H. Zhou, R. Cheng, L. Liu, Y. Huang, X. Duan, "Top-Gated Chemical Vapor Deposition Grown Graphene Transistors with Current

- [30] J. Bai, L. Liao, H. Zhou, R. Cheng, L. Liu, Y. Huang, X. Duan, "Top-Gated Chemical Vapor Deposition Grown Graphene Transistors with Current Saturation", *Nano Letters*, vol. 11, pp. 2555-2559, May 2011. DOI: 10.1021/nl201331x

- [31] H.-Y. Chang, W. Zhu, D. Akinwande, "On the mobility and contact resistance evaluation for transistors based on MoS2 or two dimensional semiconducting atomic crystals", Applied Physics Letters, vol. 104, p. 113504, 2014. DOI: 10.1063/1.4868536

- [32] W. Wei, X. Zhou, G. Deokar, H. Kim, M. M. Belhaj, E. Galopin, E. Pallecchi, D. Vignaud, H. Happy, "Graphene FETs With Aluminum Bottom-Gate Electrodes and Its Natural Oxide as Dielectrics", *IEEE Transactions on Electron Devices*, vol. 62, no. 9, pp. 2769-2773, Aug. 2015. DOI: 10.1109/TED.2015.2459657

- [33] P. C. Feijoo, F. Pasadas, J. M. Iglesias, E. M. Hamham, R. Rengel, D. Jiménez, "Radio Frequency Performance Projection and Stability Tradeoff of h-BN Encapsulated Graphene Field-Effect Transistors", *IEEE Transactions on Electron Devices*, vol. 66, no. 3, pp. 1567-1573, Mar. 2019. DOI: 10.1109/TED.2018.2890192

- [34] F. Xia, V. Perebeinos, Ym. Lin, Y. Wu, P. Avouris, "The origins and limits of metal-graphene junction resistance", Nature Nanotechnology, vol. 6, pp. 179–184, Feb. 2011. DOI: 10.1038/nnano.2011.6