# Overcoming High Frequency Limitations of Current-Mode Control Using a Control Conditioning Approach — Part II: Implementation and Hardware

Xiaofan Cui, Student Member, IEEE, and Al-Thaddeus Avestruz, Senior Member, IEEE

Abstract—This article is the second part of a paper series about interference in extremum (i.e., peak or valley) current-mode control, which applies to both fixed and variable switching frequency power converters. Specifically, this part presents three control conditioning methods that mitigate the adverse effect of interference. These methods are new ways to use: (i) slope compensation; (ii) low-pass filtering; and (iii) the phenomenon of comparator-overdrive-delay, for control conditioning. The stability criterion, closed-loop dynamics, and transient performance are derived with mathematical rigor for each method. The design tradeoffs are illustrated, discussed, and compared. The effectiveness of all three methods are demonstrated and validated in hardware using a power converter operating at multi-MHz switching frequencies.

Index Terms—peak current-mode control, valley current-mode control, digital control, nonlinear control, Lure system, parasitics, ringing, large-signal stability, robustness, comparator overdrive propagation delay, switching-synchronized sampled-state space, voltage regulator modules (VRMs), slope compensation, subharmonics, subharmonic oscillations

## I. INTRODUCTION

EALIZING the ultimate potential of current-mode con-**K** trol to be faster, more flexible, reliable, and safer is fundamentally curtailed by unwanted signals on the current sensor. A prominent class of current-mode controller prescribes the extremum (i.e., peak or valley) of the inductor current trajectory at every switching cycle. Both fixed frequency [1], [2] and variable frequency (i.e., constant off-time [3] and constant on-time [3], [4]) varieties are employed, enabling cycle-by-cycle control of the inductor current. The sensing of the current extremum requires a single-point measurement, which is especially vulnerable when the switching frequency approaches the frequency band of the interference. Interference can lead to instabilities including those that manifest as subharmonics of the equilibrium switching frequency [5]. The modeling of this interference within a control conditioning framework and the effect on the dynamics were logically delineated and rigorously derived in theory in Part I of this paper.

Control conditioning approaches the repair of corruption from interference in the model of the current control loop. The model of the current control loop consists of the static and dynamic mappings; the control conditioning methods described in this part of this paper repairs one or both of these mappings. The goals of the control conditioning methods are to: (i) guarantee stability; (ii) optimize control performance; (iii) ease hardware implementation; (iv) enable circuit integration; (v) ease controller design; and (vi) provide provable guarantees.

Among the control conditioning methods: (i) first-event-triggering with latching, (ii) slope compensation, (iii) low-pass filter conditioning, and (iv) comparatoroverdrive-delay conditioning have been investigated and can be deployed. The principles and example design of (i) are illustrated in the Part I article. In this article, the principle and design of (ii)-(iv) will be elaborated.

In repairing the dynamic mapping, (ii)-(iv) contribute additional dynamics to the current control loop. We rigorously derive the stability criterion, closed-loop dynamics, and transient performance of the current control loop for each. The closedloop dynamics (e.g., poles and zeros) are needed particularly when the current controller is enclosed by an outer loop such as a voltage control loop. The transient performance consists of settling and overshoot; these two metrics are most often used to compare different types of controllers, and in the context of this paper, control conditioning methods.

Additionally, we illustrate the design tradeoffs of each of these methods through mathematically proven stability criteria and analytical expressions for transient performance. We examine a unified framework for fairly comparing and optimally selecting among the conditioning methods to maximize the control performance for the practicing engineer. Each control conditioning method (ii)-(iv) together with hardware demonstration and validation using a dc-dc converter switching at multi-megahertz frequencies is provided. Straightforward hardware design was possible with a hybrid digital/analog strategy.

In the the Part I article, we develop the foundations for the mathematical modeling of interference as an uncertainty in the model of the plant for the current control loop and the theoretical framework for control conditioning as a mitigation of the deleterious effects. The important concepts of static and dynamic mappings of the current control loop are discussed and how the corruption of these mappings by interference leads to subharmonic instabilities, which make the output ripple hard to filter reliably.

In this Part II article, a thorough discussion of the theory and hardware results are presented for each of the (ii)-(iv) control conditioning methods. In Section II, the large-signal stability

The authors are with the Department of Electrical and Computer Engineering, University of Michigan, Ann Arbor, MI, 48109 USA (e-mail: cuixf@umich.edu; avestruz@umich.edu).

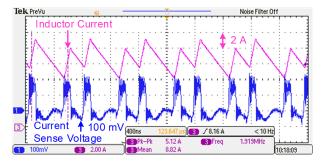

Fig. 1: Current sense voltage of a current-mode buck converter using constant on-time (10 m $\Omega$  current sense resistor). The current sensor output is largely distorted by interference, and the measurement error can be as much as 40%. The interference comes from the parasitic ringing and power ground resonance. Subharmonics on the inductor current waveform manifest because the interference severely destabilizes the current control loop.

criteria, settling, and overshoot are theoretically derived in closed-form for each of the methods, with proofs provided in papers [6], [7]. In addition, intuitive graphical and textual descriptions of the dynamics are included. For each method, the hybrid analog/digital hardware implementation is carefully described in Section III. In Section IV, a summary of the results and contributions of this paper are summarized.

### II. DESIGN OF CONTROL CONDITIONING METHODS

Control conditioning changes both the static and dynamical mappings of the current control loop to flatten nonlinearities, stabilize, and improve transient performance from what had been degraded by interference. For the static mapping, control conditioning transforms the interference to reduce the degree of nonlinearity. One unintended consequence of this interference transformation is the transformation of the ideal static mapping. In the best case, the ideal static mapping remains a line, but may be offset or changed in slope; however, this transformation can additionally introduce nonlinearities to this ideal mapping. The best-fit line to this transformed ideal mapping can be considered the "new ideal mapping", which becomes the baseline for the analysis of deviations discussed in Section II of the Part I article [8]. From this analysis, the deviation results from (a) the unintended nonlinearity from control conditioning and (b) the nonlinearity from interference.

For dynamical mapping, control conditioning transforms the interference to reduce the worst-case model gains that cause instability, slow settling, and large overshoot. One unintended consequence of this interference transformation may be the introduction of additional destabilizing gains, poles, zeros, or a delay, which degrades the stability margin. Designing the control conditioning involves balancing two competing mechanisms: the reduction of the deleterious effects of interference and the unintended dynamics introduced by control conditioning.

We discuss four new control conditioning methods to confront interference. First-event triggering with latching is the precursor to the following three. The multivalued static mapping can be resolved by first-event triggering with latching. However, this triggering criterion can cause discontinuities in the static mapping. These discontinuities along with other

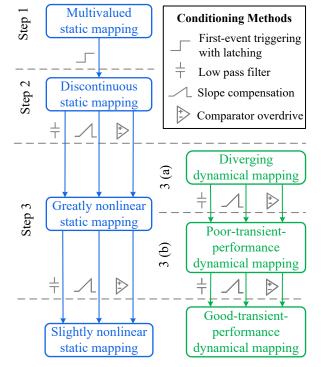

**Fig. 2:** 3-steps design procedure of control conditioning. Four conditioning methods — first-event triggering with latching, low-pass filtering, slope compensation and comparator overdrive are applied to repair the defective static mapping and dynamical mapping step-by-step.

nonlinearities can be repaired by the following three methods: slope compensation, low-pass filtering, and comparator overdrive delay. These methods also affect the dynamical mapping whose impact to stability must be considered, leading to different tradeoffs in the transient performance. Our theoretical results enable the guarantee of *global asymptotic stability* of the dynamical mapping and hence the current control loop, while optimizing the transient performance. The low-pass filter, although the most often-used method for alleviating interference, is typically selected in an ad-hoc manner. The filter is the most straightforward to implement in hardware; however, guarantees of stability are theoretically involved and usually result in worse transient performance than the other two methods, and are often infeasible when the band of interference is lower or near the switching frequency.

The other two methods come from two familiar constituents of power converters, but are used in an entirely new way. Slope compensation is the most straightforward to understand as a control conditioning method. Although traditionally used to stabilize a different phenomenon [9], using this wellknown method to alleviate interference leads to a surprising result. The overdrive delay in a comparator as a means for control conditioning is original. This method can readily be implemented as part of an integrated circuit controller and the delay can easily be made tunable.

In this section, we outline and rigorously prove a 3-step design procedure to precisely design the control conditioning of interference in current-mode control. We offer quantitative comparisons in choosing slope compensation, low pass filtering, and comparator overdrive.

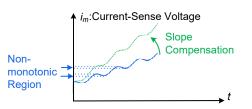

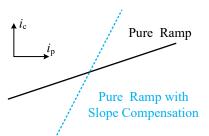

**Fig. 3:** Time domain explanation of how slope compensation conditions the interference. Slope compensation guarantees the continuity of the static current mapping by rotating the current sensor signal until it becomes monotonic and re-scaling the deviation from the interference.

- 1) In step 1, we use first-event triggering with latching to resolve the problem of the multivalued static mapping.

- 2) In step 2, we use one of three conditioning methods including slope compensation, low-pass filtering, and comparator overdrive delay to condition the discontinuous static mapping. Each of these can independently solve the problem. We prove the condition for each method to make the static mapping continuous.

- 3) In step 3, we carefully design these three methods to condition the degraded dynamical mapping. We prove the criterion for each method to make the dynamical mapping stable. we analyze the design trade-off for each method to optimize the settling and overshoot of the dynamical mapping. The design procedure is summarized in Fig. 2.

### A. Slope Compensation

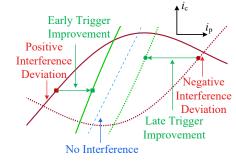

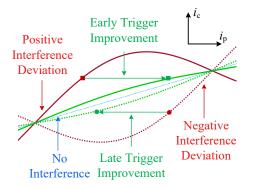

Slope compensation is a well-recognized control conditioning method that stabilizes the fixed-frequency current-mode control loop when the duty cycle crosses 50%. What had been previously unknown is that slope compensation can also be used for the control conditioning of interference. Slope compensation can repair both discontinuities and the ensuing smooth nonlinearities in the static mapping, as well as improve the transient performance of the dynamical mapping. Slope compensation decreases the degree of nonlinearity by effectively flattening the interference in the time domain waveform as shown in Fig. 3. This has the consequence of flattening the static mapping by contracting the points in the interference that correspond to early triggering (negative deviation from transformed ideal line of the current mapping) and late triggering (positive deviation from the transformed ideal line) as illustrated in Fig. 3. For an ideal static mapping, slope compensation does not introduce nonlinearities, but rather introduces a slope (gain) error in the mapping, as shown in Fig. 5. As previously mentioned, this gain error is outside of the current control loop and is subsequently corrected in the design of the outer voltage loop.

We start with constant off-time current-mode control as an example. By adding slope compensation, we replace  $i_c$ , which is constant within every switching cycle, with  $i_c - m_s t$ , which is a decreasing ramp for  $m_s > 0$ . A state-space form of the current control loop is

$$i_p[n] = i_p[n-1] - m_2 T_{\text{off}} + m_1 t_{\text{on}}[n],$$

$$i_c[n] = i_p[n] + w(t_{\text{on}}[n]) + m_s t_{\text{on}}[n].$$

(1)

Fig. 4: Slope compensation weakens the nonlinearity of the static current mapping by contracting the deviation from the ideal triggering.

Fig. 5: Slope compensation does not affect the nonlinearity of the static current mapping but causes a gain error on the mapping.

Proposition 1 in the Part I article [8] states that if the current sensor output is not monotonic, then the static current mapping is discontinuous. A discontinuous static mapping can make the current control loop unstable. Corollary 1 below states that if a slope compensation  $m_s$  is added, the discontinuity can be eliminated as had been discussed for Fig. 3. We show that an appropriately designed slope compensation can make the time-domain function of the current sensor output monotonic; from Proposition 1 in the Part I article [8], the static mapping is also made continuous.

**Corollary 1.**  $\mathcal{T}$  is a strictly monotonically increasing and continuous static mapping if and only if  $(m_1 + m_s) t + w(t)$  is strictly monotonically increasing and continuous within a switching cycle.

In this section, we show that adding an extra slope transforms both the interference and the ideal current ramp, which allows the dynamical mapping to be stabilized even if the original interference violates the stability bound in Theorem 1 of the Part I article [8]. From Theorem 1 of the Part I article [8] and having satisfied its condition of continuous static mapping, the stability of the dynamical mapping depends on the upper bound of the Lipschitz constant  $\Lambda_{ub}$  of the interference. For a larger  $\Lambda_{ub}$ , an accordingly larger  $m_s$  is needed to make the current control loop globally asymptotically stable.

This slope compensation method does not impose any restrictions on the amplitude and frequency of the interference, which means it can be an often-used and robust large-signal method to stabilize the current control loop. One proviso is that a larger compensation  $m_s$  corresponds to a higher loop gain, hence moving the pole on the z-domain root locus as we explain below; when it is too high, it slows down the closed-loop response of the current control loop, which is the

opposite of what happens in the *s*-domain when the loop gain becomes higher.

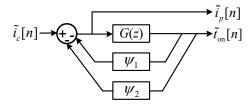

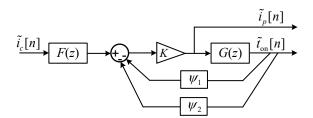

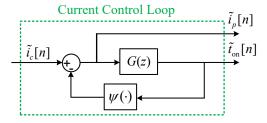

We approach the stability analysis by applying the z-transform to system (1). The current control loop can be represented as the Lure system in Fig. 6 with

$$G(z) = \frac{1 - z^{-1}}{m_1}.$$

(2)

The interference is embedded in the static nonlinearity  $\psi_1$  in the feedback path

$$\psi_1 = w(\tilde{t}_{\rm on}[n] + T_{\rm on}[n]) - w(T_{\rm on}[n]).$$

(3)

The slope compensation is embedded as a gain  $\psi_2$  also in the feedback path

$$\psi_2 = m_s. \tag{4}$$

If the function  $w(\cdot)$  is monotonically decreasing, the feedback path  $\psi_1$  is a positive feedback path and might cause instability. Typically the compensation slope  $m_s$  is chosen to be positive, which makes  $\psi_2$  a negative feedback path, which can be used to correct the destabilizing effect of  $\psi_1$ .

As a Lure system, we can apply the circle criterion similarly to the Part I article; the large-signal stability criterion for the dynamical mapping can be proven.

**Corollary 2.** The current control loop represented by the Lure system in Fig. 6 is *globally asymptotically stable* if  $\Lambda_{ub} < m_1/2 + m_s$ .

Fig. 6: Large-signal block diagram of the constant off-time/fixed-frequency peak current control loop with slope compensation. The interference is embedded in  $\psi_1$  and the slope compensation is embedded in  $\psi_2$ .

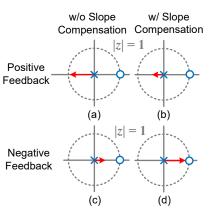

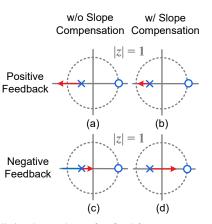

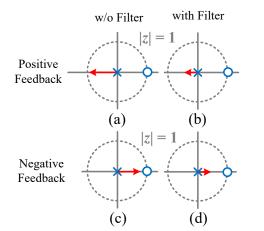

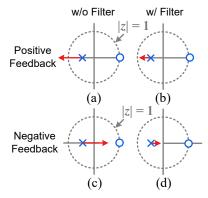

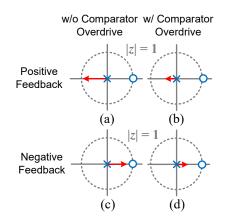

We can obtain an intuition for stability by examining the linearized system of (1). The root locus for this linearized system is illustrated in Fig. 7 and helps to visualize how slope compensation improves stability and affects the transient response. We observe that slope compensation for positive feedback in Figs. 7 (a) and (b) moves the location of the worst-case closed-loop pole further to the right, hence improving stability margin. Likewise, for negative feedback in Figs. 7 (c) and (d), adding the slope compensation right-translates the closed-loop pole towards z = 1 and increases the worst-case settling.

We use the settling and overshoot metrics in (28) and (29), respectively, to quantitatively illustrate the relationship between these metrics and the pole locations. With interference, the pole *a* cannot be located exactly, but rather within a range  $[a_{\min}, a_{\max}]$ , where

$$a_{\min} = \frac{m_s - \Lambda_{ub}}{(m_1 + m_s - \Lambda_{ub})}, \ a_{\max} = \frac{m_s + \Lambda_{ub}}{(m_1 + m_s + \Lambda_{ub})}.$$

(5)

Fig. 7: Small-signal root locus of the constant off(on)-time current control loop with the slope compensation. The sign of the feedback is determined by the interference. In positive feedback, slope compensation decreases the loop gain to increase the stability margin. In negative feedback, the converter is always stable, but results in a slower transient performance. In practice, the polarity of the feedback cannot be determined a-priori and the compensation slope is chosen so that the converter is stable in positive feedback.

The worst-case for settling and overshoot can be obtained from (28) and (29), respectively. It is worth noting that  $a_{\min}$  and  $a_{\max}$  are not usually symmetric about the origin.

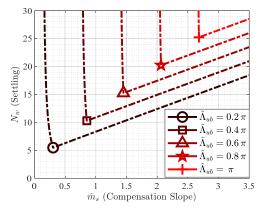

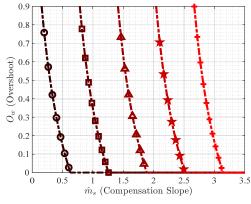

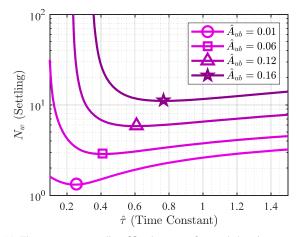

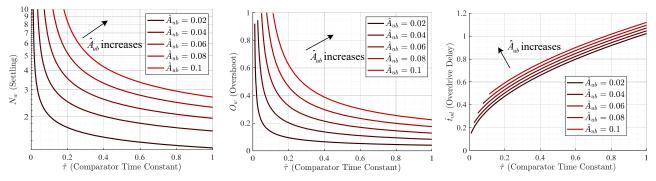

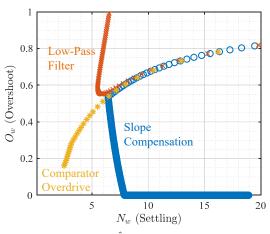

The transient performance of the current control loop varies with the compensation slope, as shown in Fig. 8(a) and Fig. 8(b). The transient performance is related to the *normalized* compensation slope  $\hat{m}_s$  and *normalized* Lipschitz constant of interference  $\hat{\Lambda}_{ub}$

$$\hat{m}_s \triangleq \frac{m_s}{m_1}, \qquad \hat{\Lambda}_{ub} \triangleq \frac{\Lambda_{ub}}{m_1}.$$

(6)

The curves from Fig. 8(a) are convex with points of minimum settling, which are marked by symbol points on each of the curves. The worst-case overshoot decreases monotonically with the compensation slope as shown in Fig. 8(b). These show a tradeoff between settling and overshoot. The range of pole locations can be expressed as

$$a_{\min} = \frac{\hat{m}_s - \hat{\Lambda}_{ub}}{(1 + \hat{m}_s - \hat{\Lambda}_{ub})}, \ a_{\max} = \frac{\hat{m}_s + \hat{\Lambda}_{ub}}{(1 + \hat{m}_s + \hat{\Lambda}_{ub})}.$$

(7)

By observing that the bounds  $a_{\min}$  and  $a_{\max}$  monotonically move to the right in the root locus with increasing  $\hat{m}_s$ , the criterion for minimum worst-case settling is then  $a_{\min} = -a_{\max}$ , from which the corresponding  $\hat{m}_s^*$  can be solved

$$\hat{m}_s^* = \sqrt{\frac{1}{4} + \hat{\Lambda}_{ub}^2 - \frac{1}{2}}.$$

(8)

The corresponding minimum worst-case settling is

$$N_w^* = \left| \frac{4}{\ln \left| 1 - (1 + \sqrt{\frac{1}{4} + \hat{\Lambda}_{ub}^2} + \hat{\Lambda}_{ub})^{-1} \right|} \right|.$$

(9)

These results can be extended to other types of current control loops. The continuity theorem, stability theorem, and the performance analysis for constant on-time control can be

(a) The worst-case settling  $N_w$  decreases first and then increases with the compensation slope  $\hat{m}_s$ .

(b) The worst-case overshoot  $O_w$  decreases with the compensation slope  $\hat{m}_s$ .

Fig. 8: The control conditioning diagram for compensation slopes given different interference levels  $\hat{\Lambda}_{ub}$ . For a given interference, there is a minimum settling  $N_w$  required. Beyond a certain compensation slope, the overshoot is always zero, but the penalty in  $N_w$  keeps increasing.

derived by replacing G(z) by

$$G(z) = \frac{(z^{-1} - 1)}{m_2}.$$

(10)

The result for fixed-frequency control can be derived by replacing G(z) by

$$G(z) = \frac{1 - z^{-1}}{m_1 + m_2 z^{-1}}.$$

(11)

The effect of slope compensation on the root locus for fixedfrequency control is shown in Fig. 9.

### B. Low-Pass Filter Conditioning

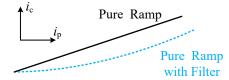

Traditionally, the low-pass filter is used for signal conditioning to reduce the amplitude of the interference signal when the interference frequency is well above the switching frequency. In this way, the cut-off frequency of the low-pass filter can be above the switching frequency hence attenuating the amplitude of the interference without affecting the inductor current ramp. When the time scale of the interference is near or below the switching frequency, the cut-off frequency will also be near or below the switching frequency; through control conditioning, the introduction of a now significant and undesirable smooth

Fig. 9: Small-signal root locus for fixed-frequency current control loop with slope compensation. The sign of the feedback is determined by the interference. In positive feedback, slope compensation decreases the loop gain to increase the stability margin. In negative feedback, the converter is always stable, but results in a slower transient performance. In practice, the polarity of the feedback cannot be determined a-priori and the compensation slope is chosen so that the converter is stable in both positive and negative feedback.

nonlinearity is considered. In doing so, stability and good transient performance can be guaranteed.

Low-pass filtering can repair both the discontinuity and nonlinearity problem in the static mapping. Despite the introduction of an unwanted nonlinearity, the filter repairs discontinuities in the static mapping, and can actually improve the interference-degraded transient performance of the dynamical mapping by reducing the interference amplitude.

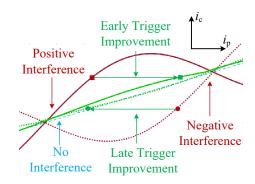

The filter decreases the degree of nonlinearity in the static mapping, as shown in Fig. 10. The early trigger, which is caused by a positive interference deviation, is delayed by the filter. The late trigger, which is caused by a negative interference deviation, is advanced by the filter. The filter makes an ideal static mapping nonlinear as shown in Fig. 11, while also able to make a larger nonlinearity from interference smaller. Therefore, there exists an optimal filter to perform the control conditioning.

The current control loop using constant off-time can be modeled as

$$i_p[n] = i_p[n-1] - m_2 T_{\text{off}} + m_1 t_{\text{on}}[n], \qquad (12a)$$

$$i_c[n] = h_0(t_{\text{on}}[n])h_0(T_{\text{off}})i_c[n-1]$$

$$+\left(i_m(t)u(t)*h(t)\right)\Big|_{t=t_{\rm on}[n]},\qquad(12b)$$

where \* is the convolution operator, h(t) is the impulse response of the low-pass filter,  $h_0(t)$  is the zero input response of the filter, and u(t) is the unit step function.  $i_m(t)$  can be expressed as the additive summation of the inductor current during the on time and the interference,

$$i_m(t) = i_p[n-1] - m_2 T_{\text{off}} + m_1 t + w(t).$$

(13)

A first-order low-pass filter has the impulse response  $h(t) = u(t) e^{-t/\tau}/\tau$  and  $h_0(t) = e^{-t/\tau}$  where  $\tau$  is the time constant. As mentioned previously, a continuous static mapping is a prerequisite for stability. Theorem 1 provides a suf-

Fig. 10: Filter shows a weakening effect on the nonlinearity of the static current mapping because it attenuates the interference signal.

Fig. 11: Filter shows an enhancing effect on the nonlinearity of the static current mapping because it warps the ramp signal.

Fig. 12: Small-signal block diagram of the constant on-time/fixed-frequency peak current control loop with the filter.

Fig. 13: Small-signal root locus of the constant off(on)-time current control loop with the low-pass filter. The sign of the feedback is determined by the interference. In positive feedback, low-pass filter decreases the loop gain to increase the stability margin. In negative feedback, the closed-loop pole is moved further to the left by the filter.

ficient condition for the filter to guarantee a continuous static mapping. As long as the time constant satisfies Theorem 1, the static mapping is continuous. We denote the lower bound of the frequency of interference by  $\omega_l$ .

**Theorem 1.** A current control loop using constant off-time has minimum on time  $T_{on}^{min}$  and off time  $T_{off}$ . The time constant of the first-order low-pass filter is  $\tau$ . The interference w(t)satisfy Definition 2 in the Part I article [8]. The condition for  $\tau$  to guarantee the *continuous* static mapping is

$$\frac{\hat{A}_{ub}}{(1-d)\hat{\tau}} \left( 1 + \frac{d}{\sqrt{1 + (2\pi\hat{\omega}_l\hat{\tau})^2}} \right) + \frac{b\hat{I}_{\max}}{(1-d)\hat{\tau}} < 1, \quad (14)$$

where

$$\hat{T}^{\min} = \hat{T}_{\text{on}}^{\min} + 1, \quad b = e^{-\frac{\hat{T}^{\min}}{\hat{\tau}}}, \quad d = e^{-\frac{\hat{T}^{\min}}{\hat{\tau}}}, \quad \hat{\tau} = \frac{\tau}{T_{\text{on}}},$$

$$\hat{A}_{ub} = \frac{A_{ub}}{m_1 T_{\text{on}}}, \quad \hat{I}_{\max} = \frac{I_{\max}}{m_1 T_{\text{on}}}, \quad \hat{\omega}_l = \frac{\omega_l T_{\text{on}}}{2\pi}.$$

(15)

The proof can be found in [7].  $\hat{\tau}$  can be interpreted as the *normalized time constant*.  $\hat{T}^{\min}$ ,  $\hat{T}^{\min}_{on}$ ,  $\hat{A}_{ub}$ ,  $\hat{I}_{\max}$ , and  $\hat{\omega}_l$  can be interpreted as the normalized minimum switching period, minimum on time, interference amplitude, maximum inductor current, and lower bound on the interference, respectively.

Theorem 2 provides a sufficient condition for stability. If  $\tau$  satisfies this condition, global asymptotic stability is guaranteed. This bound on  $\tau$  depends on the maximum inductor current  $I_{\text{max}}$ , minimum on time  $T_{\text{on}}^{\min}$ , and the interference amplitude and frequency bounds.

**Theorem 2.** A current control loop using constant off-time has a minimum on time  $T_{on}^{min}$  and fixed off time  $T_{off}$ . The time constant of the first-order, low-pass filter is  $\tau$ . The interference w(t) satisfies Definition 2 in the Part I article [8]. The bounds on  $\tau$  to guarantee the global asymptotic stability of the current control loop is

$k_0 \frac{1}{\hat{\tau}} + k_1 \frac{\hat{A}_{ub}}{\hat{\tau}} + k_2 \frac{\hat{A}_{ub}}{\hat{\tau}\sqrt{1 + (2\pi\hat{\omega}_l\hat{\tau})^2}} < \frac{1}{2},$

and

$$k_3 \frac{\hat{I}_{\max}}{\hat{\tau}} + \frac{\hat{A}_{ub}}{\hat{\tau}} + \frac{\hat{A}_{ub}}{\hat{\tau}\sqrt{1 + (2\pi\hat{\omega}_l\hat{\tau})^2}} < \frac{1}{2}, \qquad (17)$$

where

$$k_{0} = \frac{d(T_{\text{on}}^{\min} + \hat{\tau}d - \hat{\tau})}{(1 - d)^{2}}, \quad k_{1} = \frac{1}{(1 - d)}, \quad \hat{T}^{\min} = \hat{T}_{\text{on}}^{\min} + 1,$$

$$b = e^{-\frac{\hat{T}_{\tau}^{\min}}{\hat{\tau}}}, \quad d = e^{-\frac{\hat{T}_{\text{on}}^{\min}}{\hat{\tau}}}, \quad \hat{\tau} = \frac{\tau}{T_{\text{on}}}, \quad \hat{A}_{ub} = \frac{A_{ub}}{m_{1}T_{\text{on}}},$$

$$k_{2} = 1 + \frac{(1 + d)d}{(1 - d)^{2}}, \quad k_{3} = \frac{d - b}{(1 - d)^{2}}, \quad \hat{I}_{\max} = \frac{I_{\max}}{m_{1}T_{\text{on}}},$$

$$\hat{\omega}_{l} = \frac{\omega_{l}T_{\text{on}}}{2\pi}.$$

(18)

The proof can be found in [7]. Although these guarantees are large-signal, we accrue intuition on the stability through linearization. At the operating point determined by the peak inductor current command  $I_c$ , the actual peak inductor current  $I_p$ , the actual valley inductor current  $I_v$ , at on time  $T_{on}$ , we

(16)

$$\tilde{i}_{p}[n] = \tilde{i}_{p}[n-1] + m_{1} \tilde{t}_{on}[n],

\tilde{i}_{c}[n] = q(T_{on})q(T_{off}) \tilde{i}_{c}[n-1] + c_{1} \tilde{i}_{p}[n] + c_{2} \tilde{t}_{on}[n],$$

(19)

where

$$c_{1} = u(t) * h(t) \Big|_{t=T_{on}},$$

$$c_{2} = -\frac{d q(t)}{d t} \Big|_{t=T_{on}} q(T_{off}) I_{c} + h(T_{on}) I_{v} + \frac{d w(t) u(t) * h(t)}{d t} \Big|_{t=T_{on}}.$$

(20)

System (19) is represented in the block diagram in Fig. 12, with the plant

$$G(z) = \frac{1 - z^{-1}}{m_1}.$$

(21)

Compared to the standard Lure representation in Fig. 14(b) of the Part I article [8], there is an additional gain block

$$K = \frac{1}{1 - e^{-\frac{T_{\text{on}}}{\tau}}}.$$

(22)

There also an additional pole-zero pair

$$F(z) = 1 - e^{-\frac{T}{\tau}} z^{-1}.$$

(23)

The effect of interference is shown in the feedback path  $\psi_1$  in Fig. 13

$$\psi_1 = \int_{-\infty}^{+\infty} \frac{j\omega W(\omega) e^{j\omega T_{\text{on}}}}{1+j\omega\tau} \, d\omega - \frac{e^{-\frac{T_{\text{on}}}{\tau}}}{\tau} \int_{-\infty}^{+\infty} \frac{W(\omega)}{1+j\omega\tau} \, d\omega.$$

(24)

Negative  $\psi_1$  can result in positive feedback and might destabilize the current control loop. As the filter time constant  $\tau$ is increased, the filter better attenuates the interference. We observe there is an another feedback path  $\psi_2$  in Fig. 13, which is derived from the static mapping

$$\psi_2 = -\frac{e^{-\frac{T}{\tau}}}{\tau}I_c + \frac{e^{-\frac{T_{\text{on}}}{\tau}}}{\tau}I_v.$$

(25)

This feedback path is a function of the actual current  $I_p$  and inductor current ripple  $m_2 T_{\text{off}}$ . A large  $I_p$  or small  $m_2 T_{\text{off}}$  can result in positive  $\psi_2$ . Positive  $\psi_2$  means a negative feedback path, which can partially cancel the positive feedback path of  $\psi_1$ . It is worth noting that  $\psi_2$  is the result of the trapezoidal shape of the current sensor waveform.

We visualize the effect of the filter on the stability of the current control loop through the root locus. P(z) in Fig. 12 is outside of the loop, hence is not included in the root locus. We collapse  $\psi_1$  and  $\psi_2$  in the root locus as a single gain. The root locus of the current control loop is shown in Fig. 13. We observe that the low-pass filter for positive feedback in Figs. 13 (a) and (b) move the location of the worst-case closed-loop pole further to the right, hence improving stability margin. Likewise, for negative feedback in Figs. 13 (c) and (d), the closed-loop pole moves further to the left. In this way, the filter guarantees the closed-loop poles to always stay inside the unit disk. Therefore stability is guaranteed.

We next show the quantitative relationship between the interference and the location of the closed-loop pole. From (19), the closed-loop transfer function is

$$C_2(z) = \frac{\beta(1 - bz^{-1})}{1 - az^{-1}},$$

(26)

where

$$a = 1 - \frac{m_1}{m_1 + \frac{\psi_1 + \psi_2}{1 - d}}, \quad b = e^{-\frac{T}{\tau}}, \quad d = e^{-\frac{T_{\text{on}}}{\tau}},$$

$$\psi_1 = \int_{-\infty}^{+\infty} \frac{j\omega W(\omega) e^{j\omega T_{\text{on}}}}{1 + j\omega\tau} d\omega - \frac{e^{-\frac{T_{\text{on}}}{\tau}}}{\tau} \int_{-\infty}^{+\infty} \frac{W(\omega)}{1 + j\omega\tau} d\omega,$$

$$\psi_2 = -\frac{e^{-\frac{T}{\tau}}}{\tau} I_c + \frac{e^{-\frac{T_{\text{on}}}{\tau}}}{\tau} I_v. \tag{27}$$

We use the settling and overshoot metrics in (28) and (29) respectively from [8], to quantitatively illustrate the relationship between these metrics and the pole locations. The settling cycles

$$N_w = \max\left\{ \left| \frac{4}{\ln(|a_{\min}|)} \right|, \left| \frac{4}{\ln(|a_{\max}|)} \right| \right\}.$$

(28)

The worst-case overshoot

$$O_w = \max\{-a_{\min}, 0\},\tag{29}$$

where  $O_w$  is expressed in percentage form in this paper.

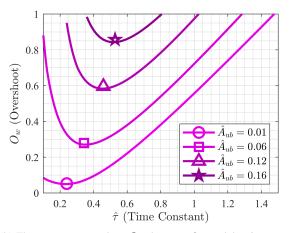

For different operating points, the pole *a* is within the range  $[a_{\min}, a_{\max}]$ . We observe that a small  $\tau$  does not provide enough attenuation on the interference whereas a too-high  $\tau$  distorts the original current ramp. Another observation is that a big  $\tau$  slows down the zero in (26). A slow zero causes a long-tail settling and overshoot problem in the transient response. Figure 14(a) and Fig. 14(b) show how the settling and overshoot change with the time constant. We fix the interference frequency at twice the switching frequency <sup>1</sup> and vary the interference amplitude. The theoretical relationships are represented by the dotted line and the simulated relationships are represented by the solid line. We observe that the theoretical curves perfectly match the simulation curves.

The settling first decreases with the time constant  $\hat{\tau}$  because the filter attenuates the interference. However, the filter also distorts the original current ramp. With the increase of  $\hat{\tau}$ , this distortion effect becomes more severe, hence the settling starts to increase with  $\hat{\tau}$ . Similarly, the overshoot decreases first with  $\hat{\tau}$  because the interference is suppressed. However, the filter also introduces a zero in the transfer function (26). This zero becomes slower and causes large overshoot as  $\hat{\tau}$  increases.

In conclusion, the important take-away messages for designers are: (i) there exists the optimal  $\hat{\tau}$  to minimize overshoot and settling; (ii) the optimal  $\hat{\tau}$  increases as the amplitude of interference increases, which is supported by our design diagram.

To extend the analysis to the constant on-time current

<sup>&</sup>lt;sup>1</sup>For the constant on(off)-time operation, this means the reciprocal of on(off) time, i.e. the fastest switching frequency.

(a) The worst-case settling  $N_w$  decreases first and then increases with the time constant  $\hat{\tau}$  of the filter. The interference frequency  $\hat{\omega} = 2$ .

(b) The worst-case overshoot  $O_w$  decreases first and then increases with the time constant  $\hat{\tau}$  of the filter. The interference frequency  $\hat{\omega} = 2$ .

Fig. 14: The design diagram for filter given different interference levels. The theoretical curves which are represented by the dotted line matches the simulated curves, which are represented by the solid line.

control loop, G(z) is transformed to

$$G(z) = \frac{1 - z^{-1}}{m_2},\tag{30}$$

and  $\psi_2$  becomes

$$\psi_2 = -\frac{d}{\tau}I_p - \frac{b}{\tau}I_c. \tag{31}$$

Note that  $\psi_2 < 0$ , hence the feedback path  $\psi_2$  is a pure positive feedback and it always shrinks the stability margin. Therefore, the filter helps more on the constant off-time control than the constant on-time control. For designers who use the filter in constant on-time control, the author suggests that it is better to choose the time constant of the filter to be faster than the switching period to avoid the harmful effect of the  $\psi_2$  feedback path. The simplified root locus of the current control loop is identical to Fig. 13.

The analysis method can be extended to fixed-frequency

**Fig. 15:** Small-signal root locus of the fixed-frequency current control loop with the low-pass filter. The sign of the feedback is determined by the interference. In positive feedback, low-pass filter decreases the loop gain to increase the stability margin. In negative feedback, the closed-loop pole is moved further to the left by filter.

peak current-mode control with a G(z) given by

$$G(z) = \frac{1 - z^{-1}}{m_1 + m_2 z^{-1}},$$

(32)

$$\psi(x) = w(x + DT) - w(DT). \tag{33}$$

and  $\psi_2$  in the feedback loop given by

$$\psi_2 = \frac{d}{\tau} I_v - \frac{b}{\tau} I_c (1 - z^{-1}).$$

(34)

We observe that in constant on(off)-time control,  $\psi_2$  is a pure gain; however, in fixed-frequency control,  $\psi_2$  introduces a pole at z = 0 and a zero. The simplified root locus of the current control loop is shown in Fig. 15.

We have shown a rigorous analytical way to design a filter for control conditioning. In the traditional way of designing for signal conditioning, low-pass filters are commonly chosen to cut off after the switching frequency, but far before the higher frequency interference band. This makes the filters unable to effectively suppress interference whose spectrum is near or below the switching frequency. The cut-off frequency of the filter can be well-below the switching frequency yet still result in stability and good transient performance. Even when the bandwidth of the filter is particularly low that the ramp is significantly distorted, the stability of the current control loop can still be guaranteed.

### C. Comparator-Overdrive-Delay Conditioning

In this section, we introduce a new idea using the comparator overdrive delay in real implementations of comparators to condition for interference; it is a dual-use of the comparator. Comparator overdrive delay is a propagation delay that is dependent on the input voltage difference. In an integrated circuit, comparator overdrive delay can be made to be realtime programmable.

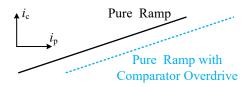

Like other control conditioning methods, using the comparator overdrive delay can repair both the discontinuity and nonlinearity problems in the static mapping along with improving the transient performance of dynamical mapping. Comparator overdrive decreases the degree of nonlinearity in the defective static mapping shown in Fig. 17. For an ideal

Fig. 16: A schematic of a simple three-stage comparator.

current sensor output ramp, using comparator overdrive delay does not create a nonlinearity, but instead introduces an offset in the static mapping, as shown in Fig. 18. This offset error does not affect the stability and transient performance of the current control loop. Rather, it can be separated so that it is outside of the current control loop and thus becomes a disturbance for the outer voltage control loop, which is often addressed by an integrator in the controller. In practice, the lower bound on the interference frequency  $\omega_l$  can be chosen as within the bandwidth of the outer loop.

For an ideal current sensor output ramp, comparator overdrive delay conditioning introduces a fixed delay in the dynamical mapping. For fixed-frequency power converters, this overdrive delay, together with other significant delays, which are caused by the blanking, subthreshold and signal propagation, should not exceed the duty ratio limits. Variable frequency power converters do not have this limitation.

In real voltage comparator implementations, the output of the comparator does not change instantaneously when the input difference crosses the voltage threshold, hence causing a delay. The *input overdrive* is defined as this voltage difference after the threshold is crossed, but before the output changes state. The input overdrive can be positive or negative, depending on whether the signal is positive-going or negative-going. For example, for peak current detection, input overdrive is when the current sensor voltage is above the voltage threshold set by the current command; for valley current detection, it is when the sensor voltage is below.

The delay time depends on the input overdrive in what is known as *comparator overdrive delay*, which is typically shown in datasheets.<sup>2</sup> In the rest of this section, we present comparator overdrive conditioning, without loss of generality, in the context of current control loops that use peak current sensing, which are positive-going input signals.

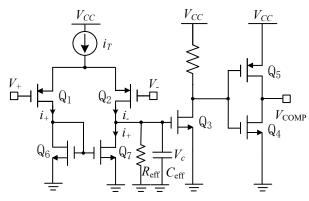

To illustrate our model for comparator overdrive, we examine a simple three-stage comparator shown in Fig. 16. It contains a differential-pair front end (Stage I), a common-source amplifier (Stage II), and a logic inverter output (Stage III).

Fig. 17: Comparator overdrive decreases the degree of nonlinearity in the static current mapping.

Fig. 18: Comparator overdrive does not affect the nonlinearity of the static current mapping and only causes an offset error.

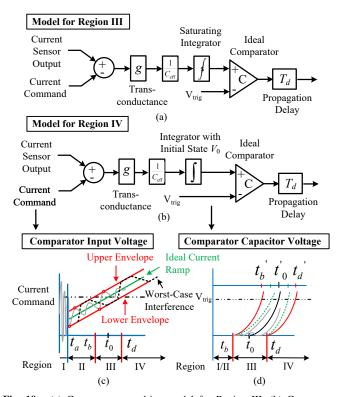

**Fig. 19:** (a) Comparator overdrive model for Region III. (b) Comparator overdrive model for Region IV. (c) Comparator input voltage. The four regions are divided by the time instants  $t_a$ ,  $t_b$ , and  $t_d$ . The blanking ends at  $t_a$ . The upper envelope and lower envelope crosses the current command at  $t_b$  and  $t_d$ , respectively. (d) Comparator capacitor voltage. The capacitor voltage trajectory of the upper envelope, ideal current ramp, and lower envelope cross the threshold  $V_{\text{trig}}$  at  $t'_b$ ,  $t'_0$ , and  $t'_d$ , respectively. The capacitor voltage trajectory given the worst-case interference is bounded between the green dashed line. Hence the comparator output can not trigger earlier than  $t'_d$ .

$<sup>^{2}</sup>$ The comparator overdrive delays that are indicated in datasheets often refer to the delays from step changes in the input. Other types of inputs can be inferred from the datasheet delays.

### DRAFT PREPRINT

We denote the equivalent capacitance at the output of Stage I by  $C_{\rm eff}$ . The comparator output toggles only if the voltage difference  $V_+ - V_-$  lasts long enough so that  $C_{\rm eff}$  is charged or discharged to cross the voltage threshold of Stage II. The current at the output of Stage I is  $i_{-} - i_{+}$ , which can also be expressed as  $g(V_{-} - V_{+})$ , where g is a nonlinear transconductance [10]. Because of  $R_{\text{eff}}$ , which is the effective resistance at the output of Stage I, the charging current for  $C_{\text{eff}}$  is always smaller than  $i_{-} - i_{+}$ .  $R_{\text{eff}}$  effectively decreases the transconductance. For the analysis, we choose a constant G, which is the largest small-signal transconductance in the range of g. Choosing the largest transconductance results in the lowest comparator overdrive delay and hence a conservative design for stability. Because g is determined by  $i_T$ , overdrive delay can be programmed by changing this tail current  $i_T$ , for example in an integrated circuit design.

We formulate a model class based on practical current sensor waveforms from power electronics, for example in Fig. 1. This class elicits a model that is straightforward in guaranteeing global stability.

This model class is characterized by four regions, which can be observed in Fig. 19(c). Region I is the "blanking" region, where large and very fast but quickly decaying switching transients dominate the current sensor output. It is worth noting that in the many instances that this region is blanked, the blanking occurs after the output of the comparator to defer the peak current event detection. Region II is the "subthreshold" region where the worst-case current sensor waveform is below the current command. Region III is the "threshold" region where the current sensor waveforms are neither unambiguously below nor above the current-command threshold; in this region, the waveform can cross the threshold multiple times. Region IV is the "overdrive" region where the current sensor waveform is always above the current command. The qualifying restriction on Region II, III, and IV for this model class is that waveform is never below the minimum current command.

In Regions I and II, we consider the comparator capacitor remaining in reset or equivalently, negatively saturated. In Regions III and IV, the capacitor integrates the current that is representative of the difference between the current command and the current sensor output; the mathematical formalization requires two different types of integrators to describe each region, as shown in Fig. 19(a) and (b). The integrator resets every switching cycle for the usual case that the overdrive delay of the comparator is smaller than the minimum off time.

The ideal current sensor output (without interference) is a ramp, which crosses the current command threshold at  $t_0$ . After  $t_0$ ,  $C_{\text{eff}}$  begins integrating; for the ideal current ramp, the capacitor voltage is a quadratic. When the capacitor voltage crosses the trigger voltage  $V_{\text{trig}}$  at  $t_0$ , which results from a combination of the gains and MOSFET thresholds (for example in Fig. 16 for  $Q_3$ ), the comparator output changes state at  $t'_0$ . The overdrive delay is from  $t_0$  to  $t'_0$ .

The current sensor output with interference in our model class can be bounded from above by an *upper envelope* and from below by a *lower envelope* in Regions II and III. The upper envelope crosses the current command earlier than the ideal current ramp by  $\Delta t_b = t_0 - t_b$ . The lower envelope crosses the current command later than the ideal current ramp by  $\Delta t_d = t_d - t_0$ . The upper and lower envelope have the same comparator overdrive delay as the ideal current ramp because these envelopes have the same slope as the ideal current ramp given the bounded amplitude assumption,

$$t_{0}^{'} - t_{0} = t_{b}^{'} - t_{b} = t_{d}^{'} - t_{d}.$$

(35)

Although the overdrive delays are identical, the upper envelope triggers earlier than that of the ideal current ramp by  $\Delta t'_b = t'_0 - t'_b$  and the lower envelope triggers later by  $\Delta t'_d = t'_d - t'_0$ .

The worst-case interference waveform that can be contained by the upper and lower envelopes is a trapezoidal signal [11]. The lower bound  $\omega_l$  of the interference frequency is the fundamental of the trapezoidal signal. The largest slew rate of the trapezoidal signal is the upper bound of the Lipschitz constant  $\Lambda_{ub}$ .

Comparator overdrive conditioning decreases the trigger time deviation from the ideal ramp for waveforms within the envelope bounds. In Region III, the time deviation of the crossing event of the worst-case interference from that of the ideal current ramp can range from  $\Delta t_{b}^{'}$  earlier to  $\Delta t_{d}^{'}$ later. In Region IV, the capacitor voltage trajectory given the worst-case interference input is strictly bounded between the quadratic trajectories of the upper and lower envelope inputs. This is a strict bound because the integral of the worst-case trapezoid is bounded from above by  $\pi A_{ub}/\omega_l$ ; hence, the comparator output cannot trigger earlier than  $\Delta t_b^{'}$  nor later than  $\Delta t'_{d}$ . The tradeoff of this control conditioning method is that longer overdrive delay becomes commensurate with smaller trigger time deviation. This overdrive delay manifests as a limitation to an outer control loop, which might for example, control output voltage.

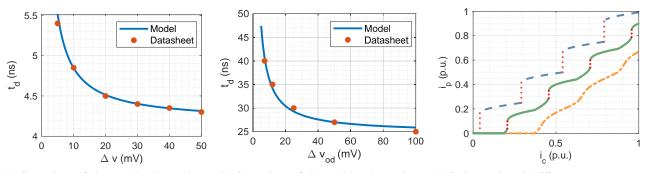

Delay and nonlinearity are the pertinent effects that determine stability and transient performance. Region I (blanking), Region II (subthreshold), and Region III (threshold) are modeled as pure delays in Fig. 19(c).  $T_d$  is a constant that encapsulates the circuit delays that are independent of the comparator input. This model for comparator overdrive delay agrees well with the real-world data [12] shown in Fig. 20(a) and Fig. 20(b).

The model for Region III (threshold) is shown in Fig. 19(a). The salient feature of this model is the saturating integrator, whose state and hence output is bounded both from above and below, but behaves like a linear integrator between these bounds. An implementation of a comparator with this behavior is illustrated in Fig. 16, where  $V_c$  is always above ground. It is worth noting that the comparator circuit actually possesses this behavior in all four of the the model regions. Stability guarantees can be proven by partitioning the comparator behavior into these regions and restricting the saturating integrator behavior to Region III.

This saturating integrator behavior is mathematically important in that the saturating integrator is a sublinear function, which enables the proof of continuity in the static mapping

(a) Comparison of the model and experimen- (b) Comparison of the model and experimen- (c) Static mapping with different comparator overtal data on the overdrive delay of comparator tal data on the overdrive delay of comparator drive delay. --- is for the comparator with zero LT1711.  $\Delta v$  represents the input overdrive and AD8469.  $\Delta v$  represents the input overdrive and overdrive delay. — is for the comparator with  $t_d$  represents the delay. The fitted trigger voltage  $t_d$  represents the delay. The fitted trigger voltage medium overdrive delay. The jump discontinuity — time constant product  $V_{\text{trig}}\tau = 6.102 \text{ ns}\cdot\text{mV}$ , — time constant product  $V_{\text{trig}}\tau = 113.3 \text{ ns}\cdot\text{mV}$ , points are represented by … . — is for the and  $T_d = 4.198 \text{ ns}$ .

Fig. 20: Comparison of the model and experimental data on the overdrive delay.

[6]. STOP The behavior in Region III be represented by

$$V(t) = \frac{1}{C_{\text{eff}}} \oint_{t_b}^{t_d} G\left(i_v[n] + m_1 t + w(t) - i_c[n]\right) dt.$$

(36)

We define  $t_{fi}$  as the last instant in Region III when the output of the integrator V(t) is zero.<sup>3</sup>

$$t_{fi} \triangleq \{t' \mid V(t') = 0 \text{ and } V(t) > 0 \quad \forall t > t'\}.$$

(37)

After  $t_{fi}$ , the behavior in Region III is a linear integrator with a voltage output  $V_0$  at the end of Region III

$$V_0 = \frac{1}{C_{\text{eff}}} \int_{t_{fi}}^{t_d} G\left(i_v[n] + m_1 t + w(t) - i_c[n]\right) \, dt.$$

(38)

The model for Region IV (overdrive), which represents a strictly positive integrator output is modeled in Fig. 19(b). The initial output  $V_0$  of the integrator embeds the saturating integrator behavior in Region III.  $V_0$  is bounded from above by  $\frac{1}{2}m_1(t_b - t_d)^2$ , which is induced by the upper envelope of the current sensor output.  $V_0$  is bounded from below by the lower bound of the saturating integrator.

The comparator overdrive in Region IV can be represented by

$$V_0 + \frac{1}{C_{\text{eff}}} \int_{t_d}^{t_{\text{on}}[n]} G\left(i_v[n] + m_1 t + w(t) - i_c[n]\right) dt = V_{\text{trig}}.$$

(39)

In (39),  $i_v[n] + m_1 t + w(t) - i_c[n]$  represents the error between the current sensor output and the current command.

By substituting (38) into (39), the comparator overdrive can

be represented as

$$\frac{1}{C_{\rm eff}} \int_{t_{fi}}^{t_{\rm on}[n]} G\left(i_v[n] + m_1 t + w(t) - i_c[n]\right) dt = V_{\rm trig}.$$

(40)

Together with the dynamics of the constant off-time current control loop, the system using the comparator overdrive can be represented as

$$\int_{t_{fi}}^{t_{on}[n]} \left( i_v[n] + m_1 t + w(t) - i_c[n] \right) dt = V_{\text{trig}}\tau, \quad (41a)$$

$$i_p[n] = i_p[n-1] - m_2 T_{\text{off}} + m_1 t_{\text{on}}[n],$$

(41b)

where the comparator time constant  $\tau = C_{\text{eff}}/G$  is the *design* variable for comparator-overdrive-delay conditioning. Equation (41a) describes the feedback path and (41b) describes the forward path.

Proposition 1 in the Part I of the paper [8] states that if the current sensor output is not monotonic, then the static current mapping is discontinuous. A discontinuous static mapping can make the current control loop unstable. We use  $\tau$  as the metric for the comparator overdrive delay. Theorem 3 below states that an appropriately designed comparator overdrive delay can make the static mapping continuous. Figure 20(c) demonstrates Theorem 3 by plotting three static mappings with different comparator overdrive delays. We observe that given small  $\tau$ , the static mapping is discontinuous. As we increase  $\tau$ , the degree of discontinuity of the static mapping decreases. The static mapping becomes continuous if  $\tau$  is large enough. Mathematically, the degree of discontinuity can be defined as the Lebesgue measure on the set of unreachable points.

**Theorem 3.** Given a constant off-time current control loop with comparator overdrive delay, if the input is a ramp with slope  $m_1$  and interference function w(t), the condition to guarantee the continuous static current mapping is

$$V_{\text{trig}}\tau \ge m_1 K_3 \left(\frac{|W(\omega)|}{m_1}\right). \tag{42}$$

The definition of the  $K_3(\cdot)$  function as well as the proof of Theorem 3 can be found in [6].

<sup>&</sup>lt;sup>3</sup>We provide a short proof for this statement: the saturating integrator always has positive or zero state at any threshold crossing instants. We start from the last instant and backwards check the integrator states at each threshold crossing instants. We stop at the instant at which the integrator state is zero. This algorithm is guaranteed to stop because the integrator state must be zero at the first threshold crossing instant. Therefore, the stop instant is the  $t_{fi}$  we want.

### DRAFT PREPRINT

Having satisfied the condition of continuous static mapping, we next show that the comparator overdrive delay allows the dynamical mapping to be stabilized. Comparator overdrive conditioning attenuates the effect of interference by averaging, hence its performance improves with increasing interference frequency. The averaging time interval is determined by  $\tau$ ; smaller  $\tau$  results in longer averaging time and hence a better interference attenuation. Smaller  $\tau$  contributes to a bigger delay, which means that interference attenuation trades off with transient performance. Theorem 4 describes the stability constraint on the design of  $\tau$ ; Theorem 5 describes the constraint from the hardware limits on minimum on time.

Theorem 4 shows there exists a minimum comparator time constant, above which the current control loop is guaranteed to be globally asymptotically stable. The stability of the dynamical mapping depends on the upper bound of the interference amplitude  $A_{ub}$  and the lower bound of the interference frequency  $\omega_l$ . Only a short overdrive delay is needed to stabilize the current control for small  $A_{ub}$  and large  $\omega_l$ . This is consistent with the behavior we described in Fig. 19.

**Theorem 4.** Given a constant off-time current control loop with comparator overdrive delay, if the input is a ramp with slope  $m_1$  and interference function w(t), the condition to guarantee a globally asymptotically stable dynamical mapping is

$V_{\text{trig}}\tau \ge \frac{4A_{ub}^2}{m_1} + B,$

where

$$au = \frac{C_{\text{eff}}}{G}, \quad B = \int_{-\infty}^{+\infty} \left| \frac{W(\omega)}{\omega} \right| d\omega.$$

The proof of this Theorem is based on the observation that (41a) is an implicit nonlinear function from  $t_{on}[n]$  to the deviation of peak current  $i_c[n] - i_p[n]$ . Therefore, the current-control loop can be represented as a Lure system. Equation (41b) describes the linear forward path and G(z) can be found in (21). (41a) describes the nonlinear feedback path and  $\psi(\tilde{t}_{on})$  is sector-bounded. The detailed proof can be found in [6]. Equation (43) shows that a current control loop with large interference amplitude can be stabilized by a comparator with a large time constant  $\tau$ .

However, having a time constant  $\tau$  that is too large results in an overdrive delay that may be too long. Long overdrive delay increases the minimum on time  $T_{on}^{min}$  of the current control loop, hence slowing down transient response. Theorem 5 shows a rigorous upper bound on the overdrive delay.

**Theorem 5.** Given a constant off-time current control loop with comparator overdrive delay, if the input is a ramp with slope  $m_1$  and interference function w(t), the maximum comparator overdrive delay  $t_{ad}^{\max}$  is

$$t_{od}^{\max} = \frac{A_{ub}}{m_1} + \sqrt{\left(\frac{A_{ub}}{m_1}\right)^2 + \frac{2}{m_1}\left(V_{\rm th}\tau + B\right)}, \qquad (44)$$

Fig. 21: The Lure system representation of current control loop with comparator overdrive for large-signal analysis. The interference is embedded in  $\psi(x)$ .

where

(43)

$$au = rac{C_{

m eff}}{G}, \quad B = \int_{-\infty}^{+\infty} \left| rac{W(\omega)}{\omega} \right| d\omega$$

The maximum comparator overdrive delay  $t_{od}^{\max}$  depends on the interference, hardware parameters, and design variable  $\tau$ . The proof can be found in [6].

The large-signal transient performance of the power converter is determined by the inductor current slew rate, which in turn is determined by the minimum on time  $T_{on}^{min}$ .  $T_{on}^{min}$  is a *design objective* for comparator-overdrive-delay conditioning. We design the comparator so that  $T_{on}^{min}$  is as small as possible while maintaining stability. Therefore, a judicious choice is to design the longest overdrive delay to equal the minimum on time

$$T_{\rm on}^{\rm min} = t_{od}^{\rm max}.$$

(45)

We define the normalized interference frequency as

$$\hat{\omega} \triangleq \frac{\omega_{lb}}{\omega_b}, \quad \omega_b \triangleq \frac{2\pi}{T_{\text{on}}},$$

(46)

the normalized interference amplitude as

$$\hat{A} \triangleq \frac{A_{ub}}{A_b}, \quad A_b \triangleq \frac{A_{ub}}{m_1 T_{\text{on}}},$$

(47)

the normalized comparator time constant as

$$\hat{\tau} \triangleq \frac{\tau}{\tau_b}, \quad \tau_b \triangleq \frac{m_1 T_{\text{on}}^2}{2V_{\text{trig}}},$$

(48)

and the normalized minimum on time as

$$\hat{T}_{\rm on}^{\rm min} \triangleq \frac{T_{\rm on}^{\rm min}}{T_{\rm on}}.$$

(49)

The base value for the normalization were chosen to be the operating points in the steady state. For example,  $T_{on}$ represents the on time of the current control loop in the steady state.

We can acquire more intuition on the stability of the current control loop with comparator-overdrive-delay conditioning through linearization. The linearized model can be expressed as a block diagram in Fig. 21 with the linear feedback gain

$$\psi = \frac{f(T_{\rm on}) - f(T_{fi})}{T_{\rm on} - T_{fi}},$$

(50)

where  $T_{fi}$  is the steady-state value of (37) and  $T_{on}$  is the on time in the steady state.

Fig. 22: Small-signal root locus of the constant off(on)-time current control loop with the comparator overdrive delay. The sign of the feedback is determined by the interference. In positive feedback, comparator overdrive delay decreases the loop gain to increase the stability margin. In negative feedback, the closed-loop pole is moved further to the left by filter.

Interference manifests in the feedback gain  $\psi$ . Negative  $\psi$  results in positive feedback and may destabilize the current control loop. Larger comparator time constant  $\tau$  results in longer delay from  $T_{fi}$  to  $T_{on}$ . From (50), larger  $T_{on} - T_{fi}$  can decrease the amplitude of  $\psi$  and stabilize the current control loop. However, either positive or negative feedback can result in stable control loop.

We can visualize the stabilizing effect of comparator-overdrive-delay conditioning through the root locus, which is shown in Fig. 22. We observe that comparator-overdrive-delay for positive feedback in Figs. 22 (a) and (b) move the location of the worst-case closed-loop pole further to the right, hence improving stability margin. Likewise, for negative feedback in Figs. 22 (c) and (d), the closed-loop pole moves further to the left. In this way, comparator-overdrive-delay conditioning can guarantee that the closed-loop poles stay inside the unit disk, hence guaranteeing stability.

We next show the quantitative relationship between interference and the location of closed-loop pole. From (19), the closed-loop transfer function is

$$C_2(z) = \frac{\beta}{1 - az^{-1}},$$

(51)

where

$$\beta = \frac{m_1}{m_1 + \psi}, \quad a = \frac{\psi}{m_1 + \psi}; \tag{52}$$

$\psi$  is defined in (50). Given an interference with amplitude upper bound  $A_{ub}$  and frequency lower bound  $\omega_l$ ,  $\psi$  is bounded within the range  $[\psi_{\min}, \psi_{\max}]$  where

$$\psi_{\min} = \frac{-2m_1}{1 + \sqrt{1 + \frac{1}{\hat{A}^2}(\hat{\tau} - \frac{\hat{A}}{\hat{\omega}})}},$$

$$\psi_{\max} = \frac{2m_1}{-1 + \sqrt{1 + \frac{1}{\hat{A}^2}(\hat{\tau} - \frac{\hat{A}}{\hat{\omega}})}}.$$

(53)

The detailed derivations can be found in [6]. For different operating points, the pole a is always real and within the range

$[a_{\min}, a_{\max}]$  where

$$a_{\min} = \frac{\psi_{\min}}{(m_1 + \psi_{\min})}, \quad a_{\max} = \frac{\psi_{\max}}{(m_1 + \psi_{\max})}.$$

(54)

The condition for small-signal stability is

$$|a_{\min}| < 1, |a_{\max}| < 1.$$

(55)

The worst-case settling and overshoot can be obtained from (28) and (29), respectively. Figures 23(a), 23(b), and 23(c) show how the settling, overshoot and overdrive delay change with the comparator time constant. We observe that both the settling and overshoot decrease as comparator time constant  $\hat{\tau}$  increases; also, overdrive delay increases as  $\hat{\tau}$  increases. These observations match our intuition because the increase in the comparator time constant results in a corresponding increase in the ability of the comparator to attenuate interference; hence, overshoot and settling is smaller. However, with this increase in comparator time constant, overdrive delay is longer, in consequence sacrificing large-signal speed.

The analysis in this section can be used for control conditioning fixed-frequency peak current-mode control by substituting G(z) in (21) by (56).

$$G(z) = \frac{1 - z^{-1}}{m_1 + m_2 z^{-1}},$$

(56)

$$\psi(x) = w(x + DT) - w(DT).$$

(57)

To extend the analysis to the constant on-time control or the fixed-frequency valley current-mode control, we need to substitute  $m_1$  by  $m_2$  and  $T_{on}$  by  $T_{off}$  in (46) and (47).

In summary, comparator-overdrive-delay conditioning can be a powerful control conditioning approach that can be easily implemented. The analog comparator, which is commonly used in peak current-mode control, can directly have a dual-use as an interference attenuator without extra complexity. Within an integrated circuit, the level of attenuation can be easily chosen by adjusting the tail current.

### **III. HARDWARE RESULTS**

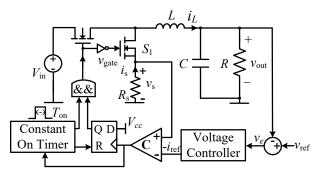

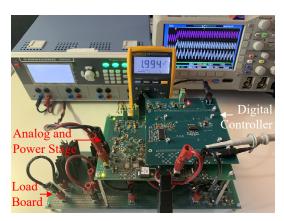

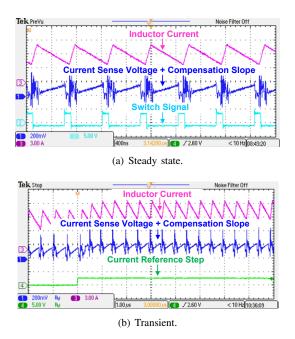

We use a multi-megahertz buck converter prototype as a working hardware example to demonstrate the effectiveness of control conditioning for current control loops with interference dysfunction. For this prototype, we selected constant on-time current-mode control, which is frequently used in high-speed converters for microprocessors. The schematic is shown in Fig. 24.

## A. DC-DC Converter Hardware Prototype Platform

The conditioning methods in this paper apply for alleviating the effect of interference that occurs in all types of current sensors. We employ the ground-referenced shunt-resistor current sensor as a widely-used exemplar because of its simplicity and wide measurement bandwidth. A 5 MHz buck converter demonstrating cycle-by-cycle control is specified in Table I. This constant on-time current mode converter delivers 2 V at 30 Watts from a 12 V input.

The control algorithms were implemented in a low cost Xilinx Artix-7 FPGA together with a 15 MHz high-speed ADC

tor. The frequency of the interference is  $\hat{\omega} = 2$ .

(a) The relationship between the worst-case set- (b) The relationship between the worst-case (c) The relationship between the maximum comtling  $N_w$  and the time constant  $\hat{\tau}$  of the compara- overshoot  $O_w$  and the time constant  $\hat{\tau}$  of the parator overdrive delay  $t_{max}^{oad}$  and the time constant comparator. The frequency of the interference is  $\hat{\tau}$  of the comparator. The frequency of the inter- $\hat{\omega}=2.$ ference is  $\hat{\omega} = 2$ .

Fig. 23: The design diagram for comparator overdrive given different interference levels.

Fig. 24: Schematic diagram of a digitally-controlled current-mode constant-on time buck converter.

TABLE I: Design Parameters of the Constant On-Time Current-Mode Buck Converter

| Parameters  | Values        | Parameters        | Values               |

|-------------|---------------|-------------------|----------------------|

| $V_{ m in}$ | 12 V          | L                 | 240 nH               |

| Vout        | 2 V           | $R_{\text{load}}$ | $0.2\Omega$          |

| Iout        | 8 A           | $R_s$             | $10\mathrm{m}\Omega$ |

| $T_{ m on}$ | 100 ns        | $f_{lb}$          | 5 MHz                |

| C           | $100 \ \mu F$ | $v_I$             | 4 mV                 |

and a 40 MHz DAC are used in the digital system. The FPGA communicates with the ADC through a 100 MHz LVDS highspeed interface. We implemented a hybrid digital and analog controller for current-mode control with commercial off-theshelf comparators. The hardware is shown in Fig. 25.

## B. Comparing the Three Control Conditioning Methods

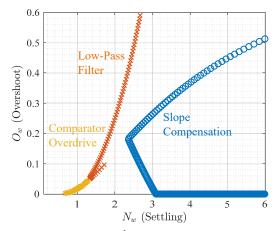

Slope compensation, low-pass filtering, and comparator-overdrive-delay conditioning repair corrupted static and dynamical mappings. From a unified framework, we compare these three control conditioning methods. All three methods decrease the degree of nonlinearity in the static mapping, but introduce other non-idealities that must be addressed. Low-pass filtering repairs the nonlinearity caused by the

Fig. 25: A 30 W, 5 MHz current-mode buck converter using constant on-time cycle-by-cycle digital control [5]. The digital controller is implemented in Xilinx Artix-7 FPGA.

interference, but introduces its own nonlinearity in the current sensor output; these two nonlinearities must be balanced to minimize the overall nonlinearity. Slope compensation adds a gain error while comparator-overdrive-delay conditioning causes an offset error in the static mapping. All three methods ensure stability and improve transient response of the current control loops. To compare control-conditioning methods, we use overshoot and settling as performance metrics.

It is inadequate to compare either the settling or overshoot in isolation because each method allows designers to trade-off between these two performance metrics through design parameters. Instead, we compare among the tradeoff spaces and construct two-dimensional performance spaces as shown in Figs. 26(a) and 26(b). By varying the key design parameter for each method, e.g. compensation slope, filter time constant, or comparator time constant, we plot the point set for each of the three methods in this space. One observes that the points closer to the origin have a better performance tradeoff in overshoot and settling. These curves depend on the interference parameters  $(A_{ub}, \omega_I)$ , with all methods performing worse with higher interference amplitude. We define  $\omega_I$  as the *interference* frequency band, which means the set of frequencies within which the interference frequency is contained. In this paper,

(a) Normalized amplitude  $\hat{A}_{ub} = 0.01$ , Normalized frequency  $\hat{\omega}_I = 3$ .

(b) Normalized amplitude  $\hat{A}_{ub} = 0.12$ , Normalized frequency  $\hat{\omega}_I = 1$ .

Fig. 26: Overshoot-settling cycle performance tradeoff. Three interference conditioning methods are compared on a current-mode converter using constant off-time control. The  $\hat{A}_{ub}$  and  $\hat{\omega}_I$ , which will be defined in Section III-E, are the normalized amplitude and frequency of interference.

the *interference frequency* refers to the interference frequency band.

Fig. 26(a) illustrates that if switching frequency is much lower than the interference frequency (e.g.,  $\omega_{sw} = \omega_I/3$ ), both the comparator-overdrive-delay conditioning and low-pass filter achieve a smaller overshoot and shorter settling than slope compensation. Fig. 26(b) illustrates that if the switching frequency is comparable to the interference frequency (e.g.,  $\omega_{sw} \approx \omega_I$ ), comparator overdrive-delay-conditioning and slope compensation result in a smaller overshoot and shorter settling than the low-pass filter. For comparator-overdrive-delay conditioning, both the overshoot and settling monotonically increase together. However, because the reduction of overshoot and settling is effected by increasing the comparator overdrive delay, the minimum on time is also increased. It is worth noting that this is so because the minimum on time is equal to comparator overdrive delay, i.e. the decision to turn the switch off cannot be made before the comparator can output its comparison. This minimum on time saturation has consequences in the large signal design of the overall power converter control loop. A qualitative comparison of the three conditioning methods is summarized in Table II.

The transient performance of the filter is the best when the switching frequency is well below the interference frequency. When the switching frequency is within the range of the interference, both slope compensation and comparator-overdrive-delay conditioning perform well. However, comparator-overdrive-delay conditioning incurs a higher complexity when implemented discretely, but is much more straightforward within an integrated circuit; additionally, as mentioned above, the dependence on minimum on time adds an additional constraint. Adaptive tuning is straightforward for both slope compensation and comparator-overdrive-delay compensation.

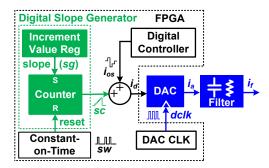

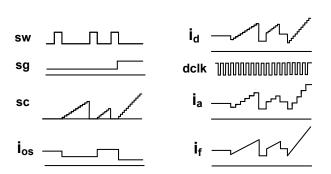

### C. Control Conditioning Using Slope Compensation

We exhibit a digital slope generator with programmable slope in Fig. 27. The slope is programmed by the increment value register sg. The output of the digital controller  $i_{os}$ determines the offset value of the valley current. The counter sc is triggered and reset every cycle. The constant-on-time modulator sw resets the counter to 0 at each rising edge and freezes the counter during the entire on time. The counter starts at the falling edge of the constant-on-time modulator sw and counts upwards.  $i_d$  represents the summation of the valley current offset  $i_{os}$  and slope  $sc. i_d$  is converted into an analog signal by the DAC. The output of the DAC  $i_a$ is updated at the rising edge of the DAC clock. The filter smooths the stepped  $i_a$  so that it is nearly an ideal ramp. The digital slope generator and controller are implemented in the FPGA, and the DAC and filter are implemented in discrete hardware. This all-digital slope generator can be reconfigured in real-time to optimize for transient and stability at different operating points, in which gain scheduling is an example. All the critical waveforms can be found in Fig. 28.

Fig. 27: Schematic of the programmable digital slope generator, which allows for re-programmability and adaptability.

The output of the slope generator can function correctly both in steady state and in transition as shown in Figs. 29(a) and 29(b). The slope generator output is shown in Channel 1 (dark blue). The inductor current is shown in channel 3 (pink) and the switching signal is shown in channel 2 (light blue). There is a propagation delay from the switching signal to the inductor current. We observe that the slope generator output is highly contaminated by the switch-on transient, but the slope compensation still functions correctly because we only need

| Method               | Less<br>Complexity | <b>Transient Performance</b><br>@ $\omega_s \ll \omega_I$ | <b>Transient Performance</b><br>@ $\omega_s \approx \omega_I$ |

|----------------------|--------------------|-----------------------------------------------------------|---------------------------------------------------------------|

| Filter               | +++                | ++                                                        | +                                                             |

| Slope Compensation   | ++                 | +                                                         | ++                                                            |

| Comparator Overdrive | +                  | +++                                                       | +++                                                           |

TABLE II: Comparison of Three Conditioning Methods

Fig. 28: Waveform of the programmable digital slope generator shows straightforward implementation of digital functions.

to compensate the current sensor slope during the off time, which means the switch-off transition does not induce heavy interference on the slope generator output.

Fig. 29: Experimental waveforms of digital slope generator with slope =  $10 \text{ A}/\mu \text{s}$  shows stable power converter operation despite a current controller corrupted by interference.

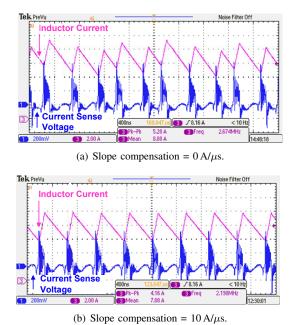

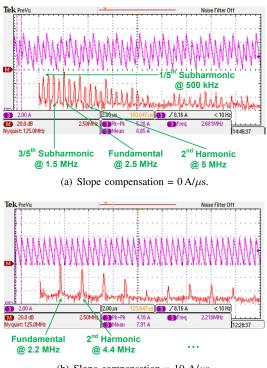

Without slope compensation, the inductor current is not stable because of the contaminated current sense voltage as illustrated in Fig. 30(a). The subharmonic frequencies of one-fifth to fourth-fifths of the fundamental frequency appear in Fig. 31(a). With slope compensation of  $10 \text{ A}/\mu\text{s}$ , the inductor current is stabilized despite the severe contamination on the current sensor voltage as shown in Fig. 30(b). The

only remaining harmonics are positive integer multiples of the fundamental frequency as validated by the Fourier spectrum in Fig. 31(b).

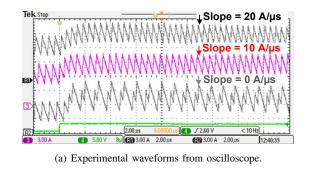

The slope compensation results in a second-order response to the current control loop as illustrated in Fig. 32(a). The greater the compensation slope, the slower the transient response as shown in Fig. 32(b). The current control loop is unstable in hardware when the compensation slope is  $0 \text{ A}/\mu \text{s}$ . When the slope is increased to  $10 \text{ A}/\mu \text{s}$ , the current controller settles quickly to a stable equilibrium within several cycles. The ringing disappears when the slope is further increased to  $20 \text{ A}/\mu \text{s}$ . However, the current transient takes longer to settle.

Inductor current and current-sense voltage of a current contr

# Fig. 30: Inductor current and current-sense voltage of a current control loop corrupted by interference shows instability without slope compensation and stability.

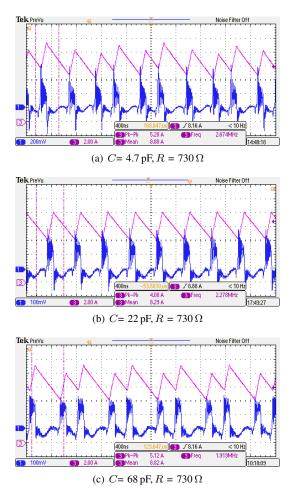

## D. Control Conditioning Using Low-Pass Filter

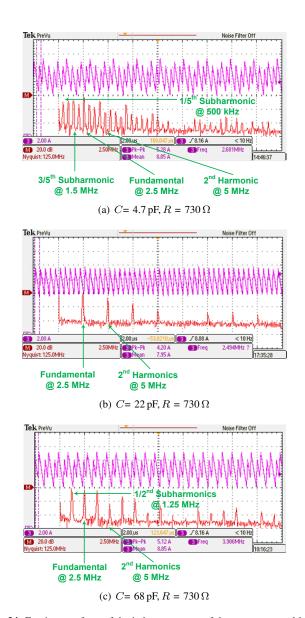

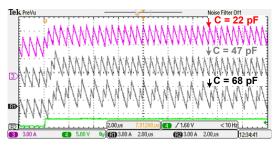

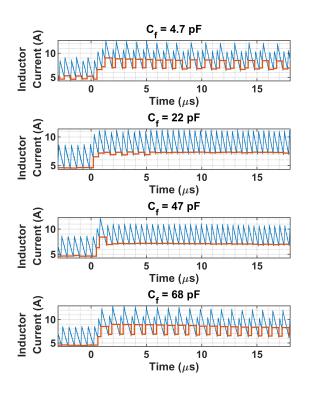

We use the first-order low-pass filter for illustration. The design of the low-pass filter includes the design of time constant  $\tau$ . The constant on-time buck prototype is used as a hardware design example. Figures 33(a), 33(b), and 33(c) show the experimental waveforms of the current-mode buck converter with different conditioning filters. We vary the capacitor value to change the time constant of the first-order low-pass filter. The inductor current is shown in Channel 3 (pink) and the current sensor output is shown in Channel 1

(b) Slope compensation = 10 A/ $\mu$ s.

Fig. 31: Fourier transform of the inductor current of the current controllers that corrupted by interference show subharmonics without slope compensation, but stable harmonics with appropriate compensation slope.

(dark blue), which is highly contaminated by interference. Note that the filter capacitor  $C = 4.7 \,\mathrm{pF}$  is always placed at the comparator input, not only for low-pass filter conditioning, but also for slope compensation and comparator-overdrive-delay conditioning because it can condition the voltage spike during switching transients, in other words, limit the bandwidth of the current-sense output. This design not only protects the comparator from being overdriven, but also makes the assumption that the bandwidth limit holds in Definition 2 in the Part I of this paper [8].

If only the bandwidth limiting filter is used without proper design, the converter cannot function properly because inductor current exhibits a complicated subharmonic behavior as shown in Fig. 33(a). From the Fourier transform of inductor current in Fig. 34(a), we observe that in addition to the switching frequency component, the  $1/5^{\text{th}}$ ,  $2/5^{\text{th}}$ ,  $3/5^{\text{th}}$ , and  $4/5^{\text{th}}$ -order subharmonics are also commingled because of the interference. We increase the time constant of low-pass filter by increasing the capacitance to 22 pF. As shown in Fig. 33(b), the inductor current goes back to stable periodic steady state; Fig. 34(b), a longer-horizon view, further confirms our observation. The Fourier transform of inductor current only contains switching-frequency and higher-order harmonics. A further step to increase the capacitance to 68 pF destabilizes the inductor current as shown in Fig. 33(c). Figure 34(c) shows that unlike Fig. 33(a), the unstable inductor current in Fig. 33(c)only contains the  $1/2^{\text{th}}$  order subharmonics. Experimentally, the steady state of the current control loop matches the theory. A fast filter cannot condition the interference and hence cannot

(b) Experimental waveforms with the inductor current valleys marked as discrete time samples.

Fig. 32: Experimental step-up response of the current control loop with different slope compensations shows instability with no slope compensation, stability with appropriate compensation, and slow transient response with over-compensation.

decrease the nonlinearity of the static current mapping; a slow filter can distort the linear ramp and increase the nonlinearity.