# INTERPLAY: An Intelligent Model for Predicting Performance Degradation due to Multi-cache Way-disabling

Panagiota Nikolaou\*<sup>†</sup>, Yiannakis Sazeides<sup>†</sup>, Maria K. Michael\*<sup>†</sup>

\*Department of Electrical and Computer Engineering and KIOS Centre of Excellence, <sup>†</sup>University of Cyprus

Abstract—Modern and future processors need to remain functionally correct in the presence of permanent faults to sustain scaling benefits and limit field returns. This paper presents a combined analytical and microarchitectural simulation-based framework called INTERPLAY, that can rapidly predict, at design-time, the performance degradation expected from a processor employing way-disabling to handle permanent faults in caches while in-the-field. The proposed model can predict a program's performance with an accuracy of up to 98.40% for a processor with a two-level cache hierarchy, when multiple caches suffer from faults and need to disable one or more of their ways. INTERPLAY is 9.2x faster than an exhaustive simulation approach since it only needs the training simulation runs for the single-cache way-disabling configurations to predict the performance for any multi-cache way-disabling configuration.

Index Terms—permanent faults, multi-cache way-disabling, graceful performance degradation, analytical predictive model

#### I. INTRODUCTION

Continued device miniaturization has enabled the integration of many cores and larger caches in processors. A modern processor contains multiple caches that take a large fraction of the total chip area (40%-60%) [1]. However, the scaling benefits for caches are confronted with reliability challenges caused by dynamic variations, e.g., aging [2], [3], and operation at low voltage levels [4]. To ensure reliable cache operation one can use spares to replace unreliable cache parts [5], however, this incurs high area costs [6].

One way industry limits spare overheads is with in-the-field mechanisms for disabling cache segments that are detected to suffer from permanent (frequently repeating) faults [7]–[10]. However, this can degrade performance due to the extra misses caused by the smaller cache capacity [11]. Therefore, it has become essential to assess the performance degradation caused by different cache-disabling configurations.

Such analysis can be done at design-time using simulation to determine field return policies (e.g., which cache-way disabling configurations should flag a field return), so that customers do not suffer from large or unknown performance degradation in-the-field. Thus, there is a need to quantify at design-time the performance impact when operating with different cache-disabling configurations to develop field return policies and to inform customers of the expected performance penalty when way-disabling is used.

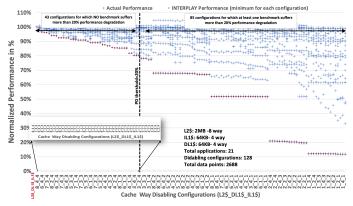

Cache-disabling can be applied at different granularities, by disabling the line or the entire cache-way that contains a fault [7]–[10], [12]. Figure 1 shows a performance analysis of cache way-disabling for a processor with a two-level cache hierarchy, for 21 different applications and all possible cache-

**Fig. 1:** Performance Impact for each cache way-disabling configuration (x-axis does not show all points to be legible, inset shows x-axis for configurations for which no benchmark incurs more than 20% performance degradation).

way disabling configurations. The processor has a 4-way IL1\$ cache, a 4-way DL1\$ and an 8-way L2\$. Thus, the total number of way-disabling cache configurations of the processor are 4 \* 4 \* 8 = 128 (assuming there is at least one operational way in each cache) and are shown on the x-axis (denoted by L2\$\_DL1\$\_IL1\$). Configuration 8\_4\_4 is the baseline configuration with no disabling in any of the caches. Each configuration is evaluated for each of the 21 workloads (i.e., total 128 \* 21 = 2688 data points, the methodology details are given in Section IV). The x-axis is sorted according the degradation suffered by any benchmark for a given way-disabling configuration.

It can be seen from Figure 1 that for 85 out of 128 (or 66.4%) of the configurations there is at least one benchmark that exceeds a hypothetical threshold of performance degradation of 20% (set by the manufacturer based on user requirements). When these way-disabling configurations occur in the field the processor can raise a flag for replacement [7], [9], [10]. One way to determine at design-time the performance degradation due to cache way-disabling, is to exhaustively evaluate, using micro-architectural simulators, all the possible combinations of way-disabling in one or more caches. However, this is, in general, non-practical as the time complexity grows as a product of the number of ways in the cache hierarchy. For example, for a processor with an 8-way IL1\$, 8-way DL1\$, 16-way L2\$ and 20-way L3\$, 20480 simulations are needed per application to cover all cache way-disabling configurations (8 \* 8 \* 16 \* 20). An alternative way, is to use analytical methods, in addition to simulation, to predict the performance degradation due to

cache disabling. Unfortunately, most existing works predict performance degradation due to disabling in only a single cache [13]–[16]. Another related work [17], attempts to reduce power, given a performance constraint, using multi-cache waypower-gating. The work in [17] uses a greedy method to determine the best power-gating configuration. However, the method is only applicable during operation, it is heuristicbased and can suffer from a large performance degradation which needs to be detected and remedied on-line. In contrast to prior work, our paper aims to predict the performance degradation of all multi-cache way-disabling configurations at design-time in an accurate manner which requires, as we show later, to account for the interplay between caches at different levels.

This work proposes INTERPLAY, the first to our knowledge, efficient, design-time, framework capable of predicting in-the-field processor performance degradation due to multicache way-disabling. In particular, our main contributions are:

- The INTERPLAY framework that predicts the performance of any multi-cache way-disabling configuration based on a new performance-degradation analytical model that uses microarchitectural statistics from the simulation of single-cache way-disabling training runs. The number of simulations needed for each benchmark by INTERPLAY is proportional to the sum of the number of ways in the various caches instead of their product that is required by the exhaustive simulation approach.

- We validate INTERPLAY for a specific processor using 14 single-cache way-disabling combinations for training to predict the performance degradation of 114 multicache way-disabling configurations, for 21 benchmarks. The results show an average performance degradation prediction error of just 1.4% with more than 9x reduction in simulation time as compared to the exhaustive simulation approach.

The rest of the paper is organized as follows: Section II describes the INTERPLAY framework. Section III presents the proposed analytical prediction model. Section IV describes the evaluation setup, and Section V presents and discusses the results. Finally, Section VI concludes this paper and discusses some future directions.

# II. INTERPLAY HIGH LEVEL FLOW AND USE

INTERPLAY combines simulation and an analytical model to quickly assess the performance of any multi-cache waydisabling configuration of a processor. It is based on an intelligent selection of a small subset of cache way-disabling configurations that are simulated for an application and used as training dataset to derive the values for the microarchitectural parameters (e.g., cache misses) which are then used by an analytical model to predict the performance of the application for any of the remaining possible way-disabling configurations. Thus, this approach can reduce drastically the number of time-consuming simulations.

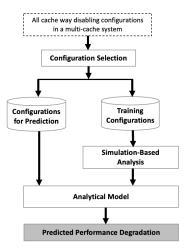

An overview of the proposed framework is given in Figure 2. A selection step divides the configurations into, i) those

**Fig. 2:** INTERPLAY framework for performance degradation prediction due to multi-cache way-disabling

to will be simulated and used as training dataset to feed the analytical model, and ii) those to be predicted using the analytical model. The training configurations are simulated to collect different micro-architectural statistics that feed into the analytical-model which determines the performance impact for the remaining way-disabling configurations (predicted configurations). The computational benefits of INTERPLAY depend on the size of its training set. As we show next, it can be quite small which helps to drastically reduce the time spent on simulations.

At design-time, a designer can use INTERPLAY to quickly produce a similar analysis to that in Figure 1, to determine which way-disabling configurations can cause unacceptable large performance degradation (PD) and should flag a field return. The PD threshold can be defined by the designer, based on the application and its requirements. The effectiveness of INTERPLAY is shown in Figure 1 with red points that indicate the largest degradation predicted by INTERPLAY per way-disabling configuration: it is virtually an exact match with the actual simulation results. Below we explain the workings of INTERPLAY.

### III. ANALYTICAL MODEL FOR PERFORMANCE DEGRADATION PREDICTION

This Section describes the models used by INTERPLAY to predict the performance degradation due to multi-cache way-disabling. An example cache hierarchy used to describe INTERPLAY's models is shown in Figure 3(a). We use this example as a point of reference to present the proposed model, which can be generalized for other configurations and types of caches. In this specific case, the hierarchy has two-levels, the level-one or high-level caches consisting of a 4-way instruction cache (IL1\$) and a 4-way data cache (DL1\$), and the low-level cache, in this case, an 8-way unified cache (L2\$). All caches are connected with their representative Miss Status Handling Register (mshr) to track outstanding cache misses.

# A. Training Configurations Selection

One of the main contributions of this paper is the appropriate selection of the training configurations. We keep

**Fig. 3:** Example of cache hierarchy for (a) baseline configuration (no cache disabling), (b) training configurations with single-way cache-disabling, (c) predicted configuration with multi-way cache-disabling

the set of training configurations small, to reduce the time complexity, but yet sufficient to predict accurately the performance degradation for all the remaining configurations. We select for training the baseline configuration (i.e., without any fault and disabled ways) and all the single-cache waydisabling configurations (i.e., with fault(s) in a single cache). All the remaining multi-cache way-disabling configurations can be predicted by our model. To illustrate, consider the processor in Figure 3(a) and assume we want to predict the performance of a multi-cache way-disabling configuration with 3-way IL1\$, 2-way DL1\$ and 7-way L2\$ shown in Figure 3(c). Our model will use statistics from the baseline simulation (Figure 3(a)) plus the three corresponding single-cache waydisabling simulations (Figure 3(b)), each having the same number of ways disabled as in the multi-cache way-disabling configuration but for a single-cache at a time i.e., (i) 4-way IL1\$, 4-way DL1\$ and 7-way L2\$, (ii) 3-way IL1\$, 4-way DL1\$ and 8-way L2\$ and (iii) 4-way IL1\$, 2-way DL1\$ and 8-way L2\$.

As the example shows, INTERPLAY attempts to predict the performance of a multi-cache way-disabling in three caches. using the baseline configuration plus the three single-cache way-disabling configurations with the corresponding disabled ways for each individual cache. Consequently, the total number of training configurations that are needed to predict ANY multi-cache way-disabling configuration is equal to 1 + $\sum (\#ways \ in \ cache_i - 1), \forall \ cache_i$ . Here, we assume that a functional processor needs to have at least one-way operational per cache. In an exhaustive simulation approach, the number of cache disabling configurations needed to be simulated in a multi-cache is equal to  $\prod (\#ways \ in \ cache_i), \forall \ cache_i$ . Hence, our proposed framework can drastically reduce the simulation time. Note that, the exact location of disabled way(s) in a cache is irrelevant, only the # of ways disabled needs to be considered.

TABLE I: Parameters used in Performance Degradation Model

| Parameters                              | Description                                                                                 |  |  |  |

|-----------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|

| $CPI_P$                                 | Predicted CPI                                                                               |  |  |  |

| $CPI_L$                                 | CPI linear model                                                                            |  |  |  |

| $CPI_{EM}$                              | CPI model for extra misses in lower-level caches                                            |  |  |  |

| $C_L$                                   | Cycles for linear model                                                                     |  |  |  |

| $C_j$                                   | Cycles for a configuration j, where j is:                                                   |  |  |  |

|                                         | B: Baseline configuration (without disabling)                                               |  |  |  |

|                                         | DT: DL1\$ Training configuration                                                            |  |  |  |

|                                         | IT: IL1\$ Training configuration                                                            |  |  |  |

|                                         | L2T: L2\$ Training configuration                                                            |  |  |  |

| $EM_i$                                  | Extra misses for cache <i>i</i> , where <i>i</i> is:                                        |  |  |  |

|                                         | D: Data cache (DL1\$)                                                                       |  |  |  |

|                                         | I\$: Instruction cache (IL1\$)                                                              |  |  |  |

|                                         | L2\$: L2 cache (L2\$)                                                                       |  |  |  |

| $M_i$                                   | Misses for cache $i$ (D\$, I\$, L2\$)                                                       |  |  |  |

| $M_{i,j}$                               | Misses for cache $i$ (D\$, I\$, L2\$) in configuration $j$ (B, DT, IT,                      |  |  |  |

|                                         | L2T)                                                                                        |  |  |  |

| $M_{i \rightarrow m}$                   | Misses for cache $i$ (D\$, I\$, L2\$) derived from cache $m$ (D\$, I\$,                     |  |  |  |

|                                         | L2\$) accesses                                                                              |  |  |  |

| $M_{i \to m, j}$                        | Misses for cache $i$ ( $D$ \$, $I$ \$, $L2$ \$) derived from cache $m$ ( $D$ \$, $I$ \$,    |  |  |  |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | L2\$) for configuration $j$ ((B, DT, IT, L2T))                                              |  |  |  |

| $TM_i$                                  | Total Misses for cache $i$ ( $D$ \$, $I$ \$, $L2$ \$)                                       |  |  |  |

| $MR_{i \rightarrow m}$                  | Miss Rate for cache $i$ ( $D$ \$, $I$ \$, $L2$ \$) derived from cache $m$ ( $D$ \$, $I$ \$, |  |  |  |

|                                         | L2\$) accesses                                                                              |  |  |  |

| $Penalty_i$                             | Per miss penalty in cycles for cache $i$ ( $D$ \$, $I$ \$, $L2$ \$)                         |  |  |  |

B. Analytical Prediction Model

The selected training configurations are simulated for each benchmark to provide various micro-architectural statistics, such as cycles per instruction (CPI), cache misses and cache accesses, all used as input to the analytical model. Specifically, to formulate the CPI for each predicted configuration (multicache way-disabling configuration), we gather and use the statistics from their corresponding single-cache way-disabling training configurations and the baseline configuration. To determine the predicted CPI we combine, i) a linear CPI model  $(CPI_L)$  that sums the performance degradation, due to the extra cache misses, from all single-cache way-disabling configurations and ii) a CPI model  $(CPI_{EM})$  that captures the degradation due to the extra cache misses in the lower-level cache (e.g L2\$) as a result of the interplay between lower and higher level caches. We define the predicted CPI  $(CPI_P)$  for a multi-cache way-disabling configuration as:

$$CPI_P = CPI_L + CPI_{EM} \tag{1}$$

All the parameters used in the formulation throughout this Section are defined in Table I. Moreover, for simplicity, when we refer to misses or extra misses, we mean mshr–misses or extra mshr–misses, respectively.

**Linear CPI model** ( $CPI_L$ ): The first objective, is to estimate  $CPI_L$ . Since the number of committed instructions of a benchmark run is the same for all the configurations, we replace CPI with cycles C. Hence, we use:

$$C_L = (C_{DT} - C_B) + (C_{IT} - C_B) + (C_{L2T} - C_B) + C_B$$

(2)

This equation sums the extra cycles contributed from the three single-cache way-disabling training configurations  $(C_{DT}, C_{IT}$  and  $C_{L2T})$ . To this end, we subtract from each training configuration cycles the cycles of the baseline configuration  $(C_B)$ . At the end, we add to these differences the cycles of the baseline configuration to estimate the total cycles. For example, if we want to predict the CPI for a disabled

L2\$ with 1 remaining way, a DL1\$ with 2 remaining ways and an IL1\$ with 3 remaining ways, assuming a baseline configuration of L2\$=8 ways, DL1\$=4 ways and IL1\$=4 ways, then equation(2) becomes:

$$C_L = (C_{8\_2\_4} - C_{8\_4\_4}) + (C_{8\_4\_3} - C_{8\_4\_4}) + (C_{1\_4\_4} - C_{8\_4\_4}) + C_{8\_4\_4}$$

(3)

where  $8\_4\_4$  is the baseline configuration,  $8\_2\_4$  is the DL1 training configuration,  $8\_4\_3$  is the IL1 training configuration and  $1\_4\_4$  is the L2 training configuration.

**CPI model due to extra cache misses in lower-level caches**  $(CPI_{EM})$ : The most challenging aspect of the problem we solve is capturing the interplay between the different caches in a multi-cache way-disabling configuration. Particularly, extra misses can occur in a multi-cache way-disabling configuration that do not occur either in the baseline or in the training single-cache way-disabling configurations. This is caused by the interactions between the higher-level and low-level caches. For example, this happens when an L2\$ hit in a single-cache multi-cache way-disabling configuration. Such interplay is not captured by the  $CPI_L$  model. Thus, we use  $CPI_{EM}$  to encapsulate this behavior defined as follows:

$$C_{EM} = EM_{L2\$} * Penalty_{L2\$} \tag{4}$$

,where  $EM_{L2\$}$  are the extra misses in L2\$ and  $Penalty_{L2\$}$  is the cycle penalty per L2\$ miss.  $EM_{L2\$}$  can be estimated using the following:

$$EM_{L2\$} = TM_{L2\$} - M_{L2\$} \tag{5}$$

,where the extra misses of L2\$ is the difference between the total expected L2\$ misses  $(TM_{L2\$})$  and the L2\$ misses from the training configurations for L2\$  $(M_{L2\$})$ . More specifically,  $TM_{L2\$}$  is estimated by:

$$TM_{L2\$} = M_{L2\$ \to D\$} + M_{L2\$ \to I\$} \tag{6}$$

Equation (6), aims to capture the total number of L2\$ misses of predicted configuration that mainly stem from two sources: 1) L2\$ misses caused by DL1\$ cache misses that access L2\$ (L2\$ $\rightarrow D$ \$) and 2) L2\$ misses caused from IL1\$ cache misses that access L2\$ (L2\$ $\rightarrow D$ \$) and 2) L2\$ misses caused from IL1\$ cache misses that access L2\$ (L2\$ $\rightarrow I$ \$). To do so,  $M_{L2$ \$ $\rightarrow D$ \$ and  $M_{L2$ \$ $\rightarrow I$ \$ are calculated as follows:

$$M_{L2\$\to D\$} = M_{D\$} * MR_{L2\$\to D\$}$$

(7)

,where  $M_{D\$}$  are the total misses from DL1\$ and,  $MR_{L2\$ \rightarrow D\$}$  is the miss rate of the DL1\$ accesses in L2\$.

$$M_{L2\$ \to I\$} = M_{I\$} * MR_{L2\$ \to I\$}$$

(8)

where  $M_{I\$}$  are the total misses from IL1\$, and  $MR_{L2\$ \rightarrow I\$}$  is the miss rate of the IL1\$ accesses in L2\$.

The L2\$ miss rates of the predicted configurations are determined from the training data provided by the simulated single-cache configuration as the ratio of the number of L2\$ accesses, due to higher-level cache misses, that cause miss

TABLE II: Processor Configuration

| Parameter description        | Setting                                     |  |

|------------------------------|---------------------------------------------|--|

| Pipeline depth               | 15 stages                                   |  |

| Fetch/Decode/Issue/Commit    | Up to 4/4/6/4 instructions per cycle        |  |

| Line Predictor               | 4096 entries                                |  |

| RAS                          | 16 entries                                  |  |

| Indirect Jump Predictor      | 512 entries                                 |  |

| Branch Predictor             | 8 KB gshare                                 |  |

| Branch Resolution            | In-order                                    |  |

| Prefetching                  | Disabled                                    |  |

| Issue Queue/Reorder buffer   | 40 INT entries, 20 FP entries / 128 entries |  |

| L1 instruction cache (IL1\$) | 4-way, 64 B blocks, LRU                     |  |

| L1 data cache (DL1\$)        | 4-way, 64 B blocks, LRU                     |  |

| L2 unified cache (L2\$)      | 8-way, 64 B blocks, LRU                     |  |

**TABLE III:** Execution time in hours for the exhaustive simulationbased and INTERPLAY approaches

| Benchmark  | Simulation-Based Approach | INTERPLAY |

|------------|---------------------------|-----------|

| astar      | 52.60                     | 5.75      |

| bwaves     | 16.00                     | 1.75      |

| bzip2      | 16.28                     | 1.78      |

| cactusADM  | 13.25                     | 1.45      |

| gamess     | 31.30                     | 3.42      |

| gcc        | 44.93                     | 4.91      |

| GemsFDTD   | 27.02                     | 2.95      |

| gobmk      | 43.55                     | 4.76      |

| gromacs    | 16.02                     | 1.75      |

| lbm        | 18.33                     | 2.01      |

| leslie3d   | 12.50                     | 1.37      |

| libquantum | 26.48                     | 2.89      |

| mcf        | 37.80                     | 4.13      |

| milc       | 25.67                     | 2.81      |

| namd       | 47.52                     | 5.19      |

| omnetpp    | 44.78                     | 4.89      |

| perlbench  | 33.12                     | 3.62      |

| sjeng      | 25.23                     | 2.76      |

| soplex     | 47.95                     | 5.24      |

| sphinx3    | 54.53                     | 5.96      |

| zeusmp     | 19.98                     | 2.19      |

| Total      | 654.85                    | 71.62     |

in L2\$, over the total number of L2\$ cache accesses due to the higher-level cache misses. Thus, the two miss rates are calculated using the following:

$$MR_{L2\$ \to D\$} = \begin{cases} M_{L2\$ \to D\$, L2T} / M_{D\$, L2T} &, (i) \\ M_{L2\$ \to D\$, DT} / M_{D\$, DT} &, (ii) \end{cases}$$

(9)

where (i)  $M_{L2\$ \to D\$, L2T} \ge M_{L2\$ \to D\$, DT}$  and (ii)  $M_{L2\$ \to D\$, L2T} < M_{L2\$ \to D\$, DT}$ .

$$MR_{L2\$ \to I\$} = \begin{cases} M_{L2\$ \to I\$, L2T} / M_{I\$, L2T} &, (iii) \\ M_{L2\$ \to I\$, IT} / M_{I\$, IT} &, (iv) \end{cases}$$

(10)

where (iii)  $M_{L2\$ \to I\$, L2T} \ge M_{L2\$ \to I\$, IT}$  and (iv)  $M_{L2\$ \to I\$, L2T} < M_{L2\$ \to D\$, IT}$ .

Conditions (*i*)-(*iv*) help determine the training configuration statistics that will be selected to compute the predicted misses.

The  $TM_{L2\$}$  includes the additional misses that are already captured by the linear model  $(CPI_L)$  so we need to subtract them. These misses correspond to  $M_{L2\$}$  which is computed based on the misses from the training configurations (DT, IT and L2T) as follows:

$$M_{L2\$} = (M_{L2\$,DT} - M_{L2\$,B}) + (M_{L2\$,IT} - M_{L2\$,B}) + (M_{L2\$,L2T} - M_{L2\$,B})$$

(11)

Finally, to estimate the miss penalty in cycles per L2\$ cache miss, needed in eq (4), we use the following:

$$Penalty_{L2} = (C_{L2T} - C_B)/M_{L2\$, L2T}$$

(12)

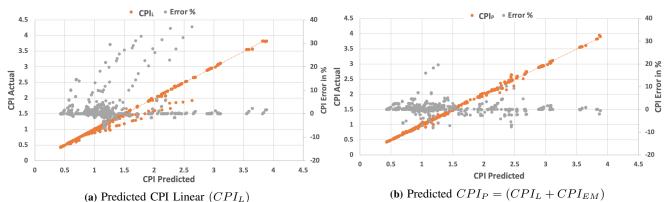

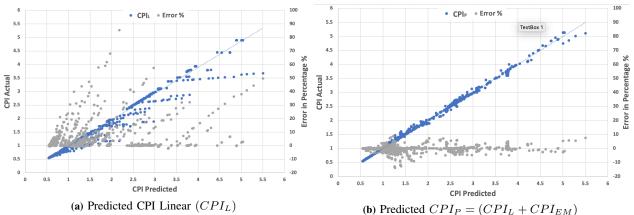

(a) Frederic CFT Linear (CFTT<sub>L</sub>) Fig. 4: Cycles per Instruction (CPI) for model-based prediction for (a)  $CPI_L$  and (b)  $CPI_P$ , for a 2MB L2\$ cache

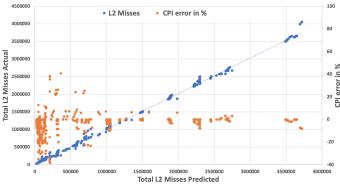

Fig. 5: Predicted L2\$ Misses using  $TM_{L2}$ \$

,which determines the per miss cycles in the L2\$ and represents the difference in clock cycles between the baseline and L2\$ training configurations, divided by the misses in L2\$ in the training configuration L2T.

### IV. EXPERIMENTAL SETUP

The simulation experiments in this work were performed using the cycle accurate simulator sim-alpha for ALPHA processor [18]. The simulator is extended to support all the combinations of way disabling for all the cache levels (DL1\$, IL1\$, L2\$) leaving at least one operational way in each cache, and to monitor all the related performance statistics. The key parameters of the simulated processor configuration are summarized in Table II. The experiments are conducted for 100M committed instructions of 21 SPEC CPU2006 benchmarks. An in-house SimPoint [19]-like tool is used to select the regions to simulate.

Two types of experimental results are reported: simulation and analytical based. The exhaustive simulation-based results are used to validate the accuracy of the proposed model. The validation compares the values obtained by simulations against the values predicted by the proposed model. The first set of results are for a processor with a 2MB L2 cache. To analyze further the model's accuracy and further highlight its generality, we have also experimented with a smaller L2 cache size of 256KB L2 that is still 8-way. For the training dataset we use a set of 14 single-cache way-disabling configurations per benchmark and for the prediction dataset we use the set of all possible 114 multi-cache way-disabling configurations.

# A. Execution time comparison of naive exhaustive simulationbased versus INTERPLAY

V. RESULTS

We first analyze the execution time for all 21 benchmarks for the two approaches, exhaustive simulation vs combined simulation and model based approach (INTERPLAY). The results are obtained when running the simulations on a Xeon server and are presented in Table III for each benchmark. The second and third column represent the execution time in hours for simulation-based approach and INTERPLAY approach, respectively. As it can be seen in Table III, INTERPLAY approach is around 9.2 times faster than the simulation approach. It is useful to note that this value matches the ratio 128/14 which corresponds to the total number of multi-cache way-disabling configurations over the INTERPLAY training configurations.

# B. Model-Based Approach Accuracy Results

We evaluate the accuracy of the proposed predicting model for  $CPI_P$ , that includes both  $CPI_L$  and  $CPI_{EM}$ . We also present results for  $CPI_L$  alone, to highlight the need for both models. For these results we use CPI and we present the accuracy of the model in terms of percentage error. The error quantifies the difference of the proposed model with the actual exhaustive simulation results. Figures 4(a)-(b) show the CPI predicted (x-axis) versus the actual CPI (y-axis), as well as, the error in percentage (secondary y-axis) for  $CPI_L$  and  $CPI_P$ , respectively, per benchmark and cache way-disabling configuration. In order to quantify the accuracy of our model we set-up a 5% threshold as a maximum permissible error. Thus, error values that are above +5% or below -5% are considered as failed predictions. Consequently, the accuracy of  $CPI_L$  is 96.42% with an average error of 10% and a maximum error of 37%. On the other hand, considering the  $CPI_P$  model, as shown in Figure 4(b), we can see a prediction error decrease, giving an accuracy of 98.40% with an average error of 3% and a maximum error of 19%.

The accuracy of the performance prediction is correlated with the accuracy that L2\$ misses are predicted, depicted in Figure 5 which shows the predicted L2\$ misses (x-axis) estimated using eq. 7, the actual L2\$ misses (y-axis) and the error on the secondary y-axis. Figure 5 clearly demonstrates that in

Fig. 6: Cycles per Instruction (CPI) for model-based prediction for (a) CPI<sub>L</sub> and (b) CPI<sub>P</sub>, for a 256KB L2\$ cache

most of the cases where we experience a larger prediction error, the actual number of L2\$ misses is relatively small (see 0-100K misses in Figure 5), which means that the overall impact on performance will be negligible. Furthermore, we investigated the prediction accuracy using different thresholds and the results show an accuracy of 92.96% with 2% error threshold and 88.09% with 1% error threshold for the  $CPI_P$ model versus 89.88% with 2% error threshold and 81.13% with 1% error threshold for the  $CPI_L$  model. This clearly demonstrates the need for the  $CPI_P$  model, which considers the interplay between lower-level and higher-level caches.

To further demonstrate the effectiveness of the model we also analyze INTERPLAY with smaller L2\$ cache which can cause a higher number of L2\$ misses. Figures 6(a)-(b) show the CPI prediction with a 256KB L2\$ for the  $CPI_L$  model and the  $CPI_P$  models, respectively. As it can be seen in Figure 6(a), the prediction error in model  $CPI_L$  increases considerably in the case of the smaller cache (compared with Figure 4(a)). However, when model  $CPI_P$  is used (Figure 6(b)), the prediction error remains small, similar to that in the larger cache (Figure 4(b)). In particular,  $CPI_P$  for the smaller cache provides an accuracy of 96.8%.

Finally, we investigated all the cases that have a prediction error above |5%| and we determined that the  $CPI_P$  fails when extra L2\$ misses cause other misses. We call these secondary misses, and by analyzing them a bit further, we found out that when a benchmark has high reusesness on specific cache blocks and these cache blocks are replaced regularly by other blocks due to the small capacity of the cache (due to cacheway disabling), then this can result in secondary misses on the frequently accessed blocks, that our current approach cannot predict.

#### VI. CONCLUSIONS AND FUTURE WORK

This paper proposes INTERPLAY framework that uses a small set of single-cache way-disabling simulations as training configurations for an analytical model to predict the performance of multi-cache way-disabling configurations. Some key novelty of the work is the intelligent selection of the training configurations that consist of single-cache way disabling configurations and a model that predicts the extra misses caused by the interaction of higher and lower level caches

when both caches, have some ways disabled. The framework has several uses. One of them is to use it at design time to help designers leverage trade-offs between performance degradation and number of field returns. Future work will consider three-level cache hierarchy and multicore processors. Finally, it would be also interesting to apply and validate the proposed model at the cache disabling granularity of a cache line.

#### REFERENCES

- S. Aga, S. Jeloka, A. Subramaniyan, S. Narayanasamy, D. Blaauw, and R. Das, "Compute caches," in *IEEE HPCA*, 2017, pp. 481–492.

K. Bowman, J. Tschanz, C. Wilkerson, S.-L. Lu, T. Karnik, V. De, and S. Borkar, "Circuit techniques for dynamic variation tolerance," in *IEEE* Development of the second DAC, 2009.

- DAC, 2009.

M. Ottavi, S. Pontarelli, D. Gizopoulos, C. Bolchini, M. K. Michael, L. Anghel, M. Tahoori, A. Paschalis, P. Reviriego, O. Bringmann et al., "Dependable multicore architectures at nanoscale: The view from europe," *IEEE Design & Test*, vol. 32, no. 2, pp. 17–28, 2014.

C. Wilkerson, H. Gao, A. R. Alameldeen, Z. Chishti, M. Khellah, and S.-L. Lu, "Trading off cache capacity for reliability to enable low voltage operation," *ACM SIGARCH*, vol. 36, no. 3, pp. 203–214, 2008.

L. Koren and C. M. Krishna. *Exatt telarant systems*, 2020.

- I. Koren and C. M. Krishna, Fault-tolerant systems, 2020.

I. Koren and C. M. Krishna, Fault-tolerant systems, 2020.

P. Nikolaou, Y. Sazeides, L. Ndreu, and M. Kleanthous, "Modeling the implications of dram failures and protection techniques on datacenter tco," in *IEEE MICRO*, 2015, pp. 572–584.

Intel, Intel Itanium Processor 9700 Series Mission Critical Computing. [6]

- [8]

- J. Chang, M. Huang, J. Shoemaker, J. Benoit, S.-L. Chen, W. Chen, S. Chiu, R. Ganesan, G. Leong, V. Lukka *et al.*, "The 65-nm 16-mb shared on-die 13 cache for the dual-core intel xeon processor 7100 series," *IEEE Journal of Solid-State Circuits*, 2007. [9] IBM, Cache Protection Mechanisms - IBM Power 595 Technical

- Overview And Introduction.

- [10]

- Fujitsu, Hot Chips 30 conference; Fujitsu briefing, 2018. N. Foutris, D. Gizopoulos, J. Kalamatianos, and V. Sridharan, "Measur-[11] [11] N. I outperformance impact of permanent faults in modern microprocessor architectures," in *IOLTS*, 2013, pp. 181–184.

[12] D. A. Patterson, P. Garrison, M. Hill, D. Lioupis, C. Nyberg, T. Sippel,

- and K. V. Dyke, "Architecture of a vlsi instruction cache for a risc," ACM SIGARCH, vol. 11, no. 3, pp. 108-116, 1983.

- and Y. Sazeides, "The performance [13] D. Hardy, I. Sideris, N. Ladas, vulnerability of architectural and non-architectural arrays to permanent faults," in *IEEE MICRO*, 2012, pp. 48–59. D. Hardy and I. Puaut, "Static probabilistic worst case execution time

- [14] estimation for architectures with faulty instruction caches," Real-Time Systems, pp. 128–152, 2015.

[15] J. Abella, A. González, X. Vera, and M. F. O'Boyle, "Iatac: a smart predictor to turn-off 12 cache lines," *TACO*, vol. 2, pp. 55–77, 2005.

[16] S.-H. Yang, M. D. Powell, B. Falsafi, and T. Vijaykumar, "Exploiting

- [16] S.-H. Yang, M. D. Powell, B. Falsah, and I. Vijaykumar, "Exploiting choice in resizable cache design to optimize deep-submicron processor energy-delay," in *IEEE HPCA*, 2002, pp. 151–161.

[17] I. S. Choi and D. Yeung, "Multi-cache resizing via greedy coordinate descent," *The Journal of Supercomputing*, 2017.

[18] R. Desikan, D. Burger, S. W. Keckler, and T. Austin, "Sim-alpha: a validated execution driven alpha 21264 simulator," Technical Report TR-01.22, Technical Rep. 2001.

- Validated execution and en applied similator, reclinical Report Re-01-23, Tech. Rep., 2001.

T. Sherwood, E. Perelman, G. Hamerly, and B. Calder, "Automatically characterizing large scale program behavior," *ACM SIGPLAN*, vol. 37, no. 10, pp. 45–57, 2002. [19]