# On implementing SWMR registers from SWSR registers in systems with Byzantine failures

Xing Hu Sam Toueg

Department of Computer Science, University of Toronto, Canada

#### — Abstract

The implementation of registers from (potentially) weaker registers is a classical problem in the theory of distributed computing. Since Lamport's pioneering work [13], this problem has been extensively studied in the context of asynchronous processes with crash failures. In this paper, we investigate this problem in the context of Byzantine process failures, with and without process signatures.

We first prove that, without signatures, there is no wait-free linearizable implementation of a 1-writer *n*-reader register from atomic 1-writer 1-reader registers. In fact, we show a stronger result, namely, even under the assumption that the writer can only crash and at most one reader can be malicious, there is no linearizable implementation of a 1-writer *n*-reader register from atomic 1-writer (n-1)-reader registers that ensures that every correct process eventually completes its operations. In light of this impossibility result, we give two implementations of a 1-writer *n*-reader register from atomic 1-writer inter 1-reader registers that work under different assumptions. The first implementation is linearizable (under any combination of process failures), but it guarantees that every correct process eventually completes its operations only under the assumption that the writer is correct or no reader is malicious — thus matching the impossibility result. The second implementation assumes process signatures; it is bounded wait-free and linearizable under any combination of process failures.

Finally, we show that without process signatures, even if we assume that the writer is correct and at most one of the readers can be malicious, it is impossible to guarantee that every correct reader completes each read operation in a *bounded* number of steps.

**2012 ACM Subject Classification** Theory of computation  $\rightarrow$  Distributed computing models; Theory of computation  $\rightarrow$  Distributed algorithms

Keywords and phrases distributed computing, concurrency, linearizability, shared registers

# 1 Introduction

We consider the basic problem of implementing a single-writer *multi*-reader register from atomic single-writer *single*-reader registers in a system where processes are subject to *Byzantine failures*. In particular, (1) we give an implementation that works under some failure assumptions, and (2) we prove a matching impossibility result for the case when these assumptions do not hold. We also consider systems where processes can use unforgeable signatures, and give an implementation that works for any number of faulty processes. We now describe our motivation and results in detail.

# 1.1 Motivation

Implementing shared registers from weaker primitives is a fundamental problem that has been thoroughly studied in distributed computing [2, 3, 4, 8, 12, 13, 15, 16, 17, 18, 19, 20, 21]. In particular, it is well-known that in systems where processes are subject to *crash* failures, it is possible to implement a *m*-writer *n*-reader register (henceforth denoted [m, n]-register) from atomic 1-writer 1-reader registers (denoted [1, 1]-registers).

In this paper, we consider the problem of implementing *multi*-reader registers from *single*-reader registers in systems where processes are subject to *Byzantine* failures. In particular,

#### 50:2 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

we consider the following basic questions:

- Is it possible to implement a [1, n]-register from atomic [1, 1]-registers in systems with Byzantine processes?

- If so, under which assumption(s) such an implementation exist?

The above questions are also motivated by the growing interest in shared-memory or hybrid systems where processes are subject to Byzantine failures. For example, Cohen and Keidar [5] give *f*-resilient implementations of several objects (namely, *reliable broadcast, atomic snapshot*, and *asset transfer* objects) using atomic [1, n]-registers in systems with Byzantine failures where at most f < n/2 processes are faulty. As another example, Aguilera *et al.* use atomic [1, n]-registers to solve some agreement problems in hybrid systems with Byzantine process failures [1]. Moreover, Mostéfaoui *et al.* [14] prove that, in *message-passing* systems with Byzantine process failures, there is a *f*-resilient implementation of a [1, n]-register if and only if at most f < n/3 processes are faulty.

#### **1.2** Description of the results

In this section, when we write "implementation", we mean an implementation that is both: (a) "safe", i.e., it is linearizable [5, 10, 14], and (b) "live", i.e., it ensures that every correct process eventually completes its operations (possibly under some failure assumptions).

To simplify the exposition of our results, we first state them in terms of two process groups: *correct* processes that do not fail and *faulty* ones. We show that in a system with Byzantine failures the following matching impossibility and possibility results hold. For all  $n \ge 3$ :

- (A) If the writer and some readers (even if only one reader) can be faulty, then there is no implementation of a [1, n]-register from atomic [1, n 1]-registers.

- (B) If the writer or some readers (any number of readers), but not both, can be faulty, then there is an implementation of a [1, n]-register from atomic [1, 1]-registers.

Note that result (A) implies that there is no *wait-free* implementation of a [1, n]-register from atomic [1, n - 1]-registers.<sup>1</sup>

This simple version of the results, however, leaves some questions open. One reason is because these results do not distinguish between the different types of faulty processes (recall that Byzantine failures encompass all the possible failure behaviours, from simple crash to "malicious" behaviour). For example we may ask: what happens if we can assume that some processes (say the writer) are subject to crash failures *only*, while some other processes (say the readers) can fail in "malicious" ways? Is an implementation of a [1, n]-register from atomic [1, 1]-registers now possible?

To answer this and similar questions, we partition processes into *three* separate groups:

(a) those that do not fail, called *correct* processes, (b) those that fail *only* by crashing, and

(c) those that fail in any other way, called *malicious* processes. In systems with a mix of such process failures, we prove the following:

(1) For all  $n \ge 3$ , there is no implementation  $\mathcal{I}_n$  of a [1, n]-register from atomic [1, n - 1]-registers, even if we assume that the writer can only crash and at most one of the readers can be malicious.

In fact, we show that this impossibility result holds even if *every* reader is given atomic [1, n]-registers that it can write and *all* processes can read, and the writer is the only process that does not have atomic [1, n]-registers.

Note that the above results consider safety and liveness as an *indivisible* requirement of a register implementation. But it could be useful to consider each requirement separately. For example, what happens if we want to implement a [1, n]-register with the following properties: (a) it is *always* safe (i.e., linearizable) and (b) it may lose its liveness (i.e., it may

<sup>&</sup>lt;sup>1</sup> Recall that a wait-free implementation guarantees that every correct process eventually completes its operations, regardless of the execution speeds or failures of the other processes [9].

block some read or write operations) *only if* some specific "pattern/types" of failures occur? We prove that in systems with a mix of process failures:

- (2) For all  $n \ge 3$ , there is an implementation  $\mathcal{I}_n$  of a [1, n]-register from atomic [1, 1]-registers such that:

- $\mathcal{I}_n$  is linearizable, and

- In every run of  $\mathcal{I}_n$  where the writer is correct or no reader is malicious, every correct process completes all its operations.

So this register implementation is linearizable regardless of which processes fail and how they fail, i.e., it is always "safe". But it guarantees "liveness" only if the writer is correct or no reader is malicious. If the writer is correct, it tolerates any number of malicious readers.

Note that (1) and (2) are matching impossibility and possibility results. They imply the simpler results (A) and (B) that we stated earlier for processes that are coarsely characterized as either correct or faulty.

If we assume that the writer is correct, the linearizable implementation of result (2) above ensures that every correct reader completes each read in a *finite* number of steps. This raises the question of whether, if we assume that the writer is correct, there is a linearizable implementation such that every reader completes each read in a *bounded* number of steps. We prove that the answer is "No". More precisely:

(3) For all  $n \ge 3$ , even if we assume that the writer is correct and at most one reader can be malicious, there is *no* linearizable implementation of a [1, n]-register from atomic [1, n-1]-registers that ensures that every correct reader completes every read in a *bounded* number of steps.

The above results are for the case that the implemented register has at least n = 3 readers. For the special case that n = 2, we give a simple implementation of a [1, 2]-register from atomic [1, 1]-registers that is *bounded wait-free*: all correct processes are guaranteed to complete their operations in a bounded number of steps regardless of which processes fail and how they fail.

We also consider the problem of implementing a [1, n]-register from atomic [1, 1]-registers in systems where processes are subject to Byzantine failures, but they can use *unforgeable signatures*. In sharp contrast to the impossibility result (1), we show that with signatures for all  $n \ge 2$ , there is an implementation of [1, n]-register from atomic [1, 1]-registers that is bounded wait-free.

We conclude the paper with a result about implementations from *regular* registers [13]. Recall that, in contrast to atomic registers, regular registers allow "new-old" inversions in the values that processes read. It is well-known that in systems with crash failures, it is easy to implement a *wait-free* linearizable [1, n]-register from regular [1, n]-registers. Here we show that in systems with Byzantine failures, such an implementation is impossible: for  $n \geq 3$ , even if we assume that the writer can only crash and at most one reader can be malicious, there is *no* linearizable implementation of a [1, n]-register from regular [1, n]-registers<sup>2</sup> that ensures that every correct process eventually completes its operations.

# 2 Result techniques

The techniques that we used to obtain our main possibility and impossibility results are also a significant contribution of this paper.

To prove the impossibility result (1), one cannot use a standard partitioning argument: all the processes except the writer are given atomic [1, n]-registers that all processes can read, and the writer is given a [1, n - 1]-register that all the readers except one can read; thus it is clear that the system cannot be partitioned.

$<sup>^{2}</sup>$  So all processes, *including the writer*, are given regular registers that all the *n* readers can read.

#### 50:4 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

So to prove this result we use an interesting reductio ad absurdum technique. Starting from an alleged implementation of [1, n]-register from [1, n - 1]-registers, we consider a run where the implemented register is initialized to 0, the writer completes a write of 1, and then a reader reads 1. By leveraging the facts that: (1) in each step the writer can read or write only [1, n - 1]-registers, (2) the writer may crash, (3) one of the readers may be malicious, and (4) there are at least 3 readers, we are able to successively remove every read or write step of the writer (one by one, starting from its last step) in a way that maintains the property that some correct reader reads 1 and at most one reader in the run is malicious. As we successively remove the steps of the writer, the identity of the reader that reads 1, and the identity of the reader that may be malicious, keep changing. By continuing this process, we end up with a run in which the writer takes no steps, and yet a correct reader reads 1.

Note that this proof is reminiscent of the impossibility proof for the "Two generals' Problem" in message-passing systems [7]. In that proof, one leverages the possibility of message losses to successively remove one message at a time. The proof given here is much more elaborate because it leverages the subtle interaction between crash *and* malicious failures that may occur at different processes.

For the matching possibility result (2), we solve the problem of implementing a [1, n]-register from [1, 1]-registers with a *recursive* algorithm: intuitively, we first give an algorithm to implement a [1, n]-register using [1, n - 1]-registers, rather than only [1, 1]-registers, and then recurse till n = 2. We do so because the recursive step of implementing a [1, n]-register using [1, n - 1]-registers is significantly easier than implementing a [1, n]-register using only [1, 1]-registers. This is explained in more detail in Section 5.1.

# 3 Model Sketch

We consider systems with asynchronous processes that communicate via single-writer registers and are subject to Byzantine failures. Recall that a single-writer *n*-reader register is denoted as a [1, n]-register; the *n* readers are distinct from the writer.

# 3.1 Process failures

A process that is subject to Byzantine failures can behave arbitrarily. In particular, it may deviate from the algorithm it is supposed to execute, or just stop this execution prematurely, i.e., crash. To distinguish between these two types of failures, we partition processes as follows:

- Processes that do not fail, i.e., *correct* processes.

- Processes that fail, i.e., *faulty* processes. Faulty processes are divided into two groups:

- processes that just *crash*, and

- $\_$  the remaining processes, which we call malicious.

# 3.2 Atomic and implemented registers

A register is *atomic* if its read and write operations are *instantaneous* (i.e., indivisible); each read must return the value of the last write that precedes it, or the initial value of the register if no such write exists.

Roughly speaking, the *implementation* of a register from a set of "base" registers is given by read/write procedures that each process can execute to read/write the implemented register; these procedures can access the given base registers (which, intuitively, may be less "powerful" than the implemented register). So each operation on an implemented register *spans an interval* that starts with an *invocation* (a procedure call) and completes with a corresponding *response* (a value returned by the procedure). Note that a process executes steps of a register implementation only when it executes its *own* operations on the register, i.e., only within

#### X. Hu and S. Toueg

the intervals of these operations.

# 3.3 Implementation liveness properties

All the register implementations that we consider satisfy the following liveness property:

▶ Definition 1 (Termination). Every correct process completes every operation in a finite number of its own steps.

As we will see, termination may rely on some failure assumptions. For example, the register implementation that we give in Section 5.4 (Algorithm 1, Theorem 48) satisfies the Termination property under the assumption that either the writer is correct or no reader is malicious. In contrast to the Termination property, *wait-freedom* and *bounded wait-freedom* are liveness properties that do not rely on any failure assumptions [9]:

▶ Definition 2 (Wait-freedom). Every correct process completes every operation in a finite number of its own steps, regardless of the execution speeds or failures of the other processes.<sup>3</sup>

▶ **Definition 3** (Bounded wait-freedom). Every correct process completes every operation in a bounded number of its own steps, regardless of the execution speeds or failures of the other processes.

# 3.4 Linearizability of register implementations

Roughly speaking, linearizability requires that every operation on an implemented object appears as if it took effect instantaneously at some point (the "linearization point") in its execution interval [10].<sup>4</sup> As noted by [5, 14], however, the precise definition of linearizability depends on whether we assume that processes can only crash (as it was assumed in [10]), or they can also fail in a "Byzantine way". We now explain this for the special case of *register* implementations.

In systems with only crash failures. It is well-known that a *single-writer multi-reader* register implementation is linearizable if and only if it satisfies two simple properties: intuitively, (1) every read operation reads the value written by a concurrent or immediately preceding write operation, and (2) there are no "new-old" inversions in the values read. To define these properties precisely, we first define what it means for two operations to be concurrent or for one to precede the other.

▶ **Definition 4.** Let o and o' be any two operations.

- $\blacksquare$  o precedes o' if the response of o occurs before the invocation of o'.

- $\bullet$  o is concurrent with o' if neither precedes the other.

We say that a write operation W *immediately precedes* a read operation R if W precedes R, and there is no write operation W' such that W precedes W' and W' precedes R.

Let  $v_0$  be the *initial value* of the implemented register, and  $v_k$  be the value written by the k-th write operation of the writer w of the implemented register (this is well-defined because each process, including the writer, applies its operations sequentially).

▶ **Definition 5** (Register Linearizability). In a system with crash failures, an implementation of a [1, n]-register is linearizable if and only if it satisfies the following two properties:

<sup>&</sup>lt;sup>3</sup> In a preliminary version of this paper [11], an implementation that satisfies the Termination property (under some failure assumption) was said to be wait-free (under this failure assumption). In particular, the register implementation given in Section 5.4 was said to be wait-free under the assumption that the writer is correct or no reader is malicious. But this use of the term "wait-free" is not conventional and can be misleading. Here we reserve the term "wait-free" for implementations that satisfy the Termination property unconditionnally, as in [9].

<sup>&</sup>lt;sup>4</sup> Linearizable (implementations of) registers, however, are *not* equivalent to atomic registers. In fact, Golab, Higham and Woelfel have shown that with a strong adversary, some randomized algorithms that "work correctly" under the assumption that processes use atomic registers, do not work if they use linearizable register implementations instead of atomic registers [6].

## 50:6 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

- Property 1 [Reading a "current" value] If a read operation R returns the value v then:

there is a write v operation that immediately precedes R or is concurrent with R, or

- $v = v_0$  and no write operation precedes R.

- **Property 2** [No "new-old" inversion] If two read operations R and R' return values  $v_k$  and  $v_{k'}$ , respectively, and R precedes R', then  $k \leq k'$ .

In systems with Byzantine failures. The above definitions do not quite work for systems with Byzantine failures. For example, it is not clear what it means for a writer w of an implemented register to "write a value v" if w is malicious, i.e., if w deviates from the write procedure that it is supposed to execute; similarly, if a reader r is malicious it is not clear what it means for r to "read a value v". The definition of linearizability for systems with Byzantine failures avoids the above issues by restricting the linearization requirements to processes that are *not* malicious. More precisely:

**Definition 6** (Register Linearizability). In a system with Byzantine process failures, an implementation of a [1, n]-register is linearizable if and only if the following holds. If the writer is not malicious, then:

- Property 1 [Reading a "current" value] If a read operation R by a process that is not malicious returns the value v then:

- = there is a write v operation that immediately precedes R or is concurrent with R, or =  $v = v_0$  and no write operation precedes R.

- **Property 2** [No "new-old" inversion] If two read operations R and R' by processes that are not malicious return values  $v_k$  and  $v_{k'}$ , respectively, and R precedes R', then  $k \leq k'$ .

Note that if the writer is correct or only crashes, then readers that are correct or only crash are required to read "current" values and also avoid "new-old" inversions. So in systems where faulty processes can only crash, Definition 6 reduces to Definition 5.

Cohen and Keidar were the first to define linearizability for *arbitrary* objects in systems with Byzantine failures [5], and their definition generalizes the definition of *register* linearizability in such systems given by Mostéfaoui *et al.* in [14]. Definition 6 above (which is also for register linearizability) is consistent with both.<sup>5</sup>

# 4 Impossibility result

We now prove that there is no wait-free linearizable implementation of a [1, n]-register from atomic [1, n - 1]-registers. In fact, we show a stronger result: even under the assumption that the writer can only crash and at most one reader can be malicious, there is no linearizable implementation of a [1, n]-register from atomic [1, n - 1]-registers that ensures that every correct process eventually completes its operations.

▶ **Theorem 7.** For all  $n \ge 3$ , in a system with n+1 processes that are subject to Byzantine failures, there is no linearizable implementation of a [1, n]-register from atomic [1, n - 1]-registers that satisfies the Termination property, even if we assume that the writer of the implemented [1, n]-register can only crash and at most one reader can be malicious.

**Proof.** Let  $n \geq 3$ . Suppose, for contradiction, that there is an implementation  $\mathcal{I}$  of a [1, n]-register  $\mathbf{R}$  from atomic [1, n - 1]-registers that is linearizable (i.e., it satisfies the Register Linearizability property) and ensures that all correct processes complete their operations (i.e., it satisfies the Termination property), under the assumption that the writer w of  $\mathbf{R}$  can only crash and at most one of the n readers of  $\mathbf{R}$  can be malicious.

<sup>&</sup>lt;sup>5</sup> In [5, 14], however, processes that are subject to Byzantine failures are partitioned into only two groups, namely, correct processes and faulty processes. Thus the reader of a register that just crashes is, by definition, faulty. So, as with all other faulty processes, by the linearizability definitions in [5, 14] it is exempt from any requirement, e.g., it is allowed to read a stale value. Definition 3 avoids this by leveraging our subdivision of faulty processes into those that only crash and those that are malicious.

**Figure 11** Run A<sub>0</sub>

#### 50:8 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

We now construct a sequence of runs of  $\mathcal{I}$  that leads to a contradiction. In all these runs, the initial value of the implemented **R** is 0, the writer w invokes only one operation into **R**, namely a write of 1, and each reader reads **R** at most once (i.e., **R** is only a "one-shot" binary register). Moreover, in each of these runs the writer crashes (but it is not malicious) and there is at most one malicious reader; the other n - 1 readers are correct. Thus, these runs of  $\mathcal{I}$  must satisfy the linearizability Properties 1 and 2 of Register Linearizability (Definition 6), and every correct reader must complete any read operation that it invokes.

▶ **Definition 8.** Let s be any step that the writer w takes when executing the implementation  $\mathcal{I}$  of  $\mathbf{R}$ . Step s is invisible to a reader p if s is either a local step of w, or the reading or the writing of an atomic [1, n - 1]-register that is not readable by p.

Since there are n readers, and the registers that w can write are atomic [1, n - 1]-registers, every write by w into one of these registers is invisible to one of the readers. So:

▶ Observation 9. Let s be any step that the writer w takes when executing the implementation  $\mathcal{I}$  of **R**. Step s is invisible to at least one of the n readers.

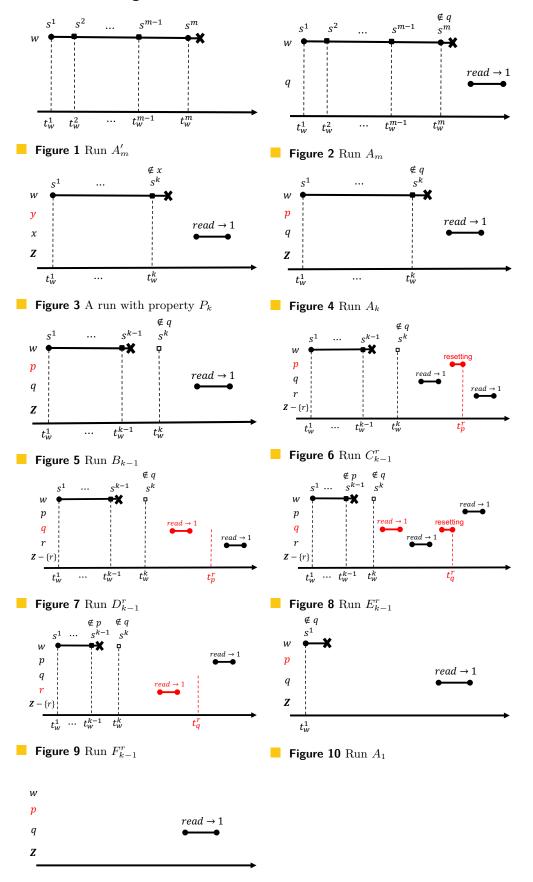

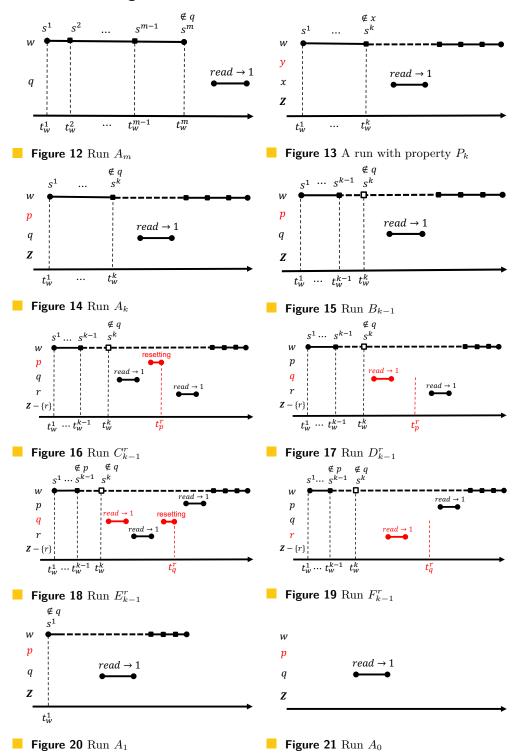

Let  $A'_m$  be the following run of  $\mathcal{I}$  (see Figure 1):

- The readers do not invoke any read operations, and so they take no steps.

- The writer w invokes an operation to write 1 on R. By the Termination property of the implementation, it completes this operation in a finite number of steps.

During this write operation, w takes a sequence of steps s<sup>1</sup>,...,s<sup>m</sup> such that each s<sup>i</sup> is either a local step, or the reading or the writing of an atomic [1, n 1]-register (s<sup>0</sup> is the

- invocation step of the write operation, and  $s^m$  is the response step of this operation). Let  $t_w^i$  be the time when step  $s^i$  occurs.

- After the time  $t_w^m$  when w completes its write operation, w crashes.

- From the run  $A'_m$  of  $\mathcal{I}$ , it is clear that the following run is also a run of  $\mathcal{I}$  (see Figure 2):

• RUN  $A_m$ :

- The writer w behaves exactly as in  $A'_m$ .

- All the readers are correct.

- Let q be a reader such that step  $s^m$  is invisible to q (by Observation 9, this reader exists). After the writer w crashes at time  $t_w^m$ , q invokes a read operation on **R**. By the Termination property of the implementation, q completes its read operation. By the linearizability properties of  $\mathcal{I}$ , this read operation on **R** returns 1.

- All the other readers do not invoke any read operations, and so they take no steps.

▶ Definition 10. For every  $k, 1 \le k \le m$ , a run of  $\mathcal{I}$  has property  $P_k$  if the following holds:

- 1. Up to and including time  $t_w^k$ , all processes behave exactly as in  $A_m$ , that is:

- $\blacksquare$  w takes steps  $s^0, s^1, \dots, s^k$

- All the readers take no steps.

- **2.** After taking step  $s^k$  at time  $t^k_w$ , w crashes before taking further steps.

- **3.** There is a reader x that is correct such that step  $s^k$  is invisible to x. After time  $t_w^k$ , reader x starts and completes a read operation on **R** that returns 1.

- 4. There is a reader  $y \neq x$  that may be correct or malicious. After time  $t_w^k$ , reader y may or may not take steps.

- 5. There is a set Z of n-2 distinct readers other than x and y that are correct and take no steps.

Note that since  $n \ge 3$ , the set Z contains at least one reader. Furthermore, all the readers that take steps do so after time  $t_w^k$ .

A run of  $\mathcal{I}$  with property  $P_k$  is shown in Figure 3. In this figure and all the subsequent ones, correct readers are in black font, while the reader that may be malicious is colored red (this reader may have taken some steps after time  $t_w^k$ , but these are *not* shown in the figure). The " $\notin x$ " on top of a step  $s^i$  means that  $s^i$  is invisible to the reader x. The symbol \* indicates where the crash of the writer w occurs.

Note that the run  $A_m$  of  $\mathcal{I}$  satisfies property  $P_m$ : the reader denoted x in property  $P_m$  is the reader q of run  $A_m$ , the reader y of  $P_m$  is an arbitrary reader other than q in  $A_m$ , and the set Z of  $P_m$  is the set of the remaining n-2 readers in  $A_m$ . So we have:

▶ Observation 11. Run  $A_m$  of  $\mathcal{I}$  has property  $P_m$ .

$\triangleright$  Claim 12. For every  $k, 1 \leq k \leq m$ , there is a run of  $\mathcal{I}$  that has property  $P_k$ .

**Proof.** We prove the claim by a backward induction on k, starting from k = m.

**Base Case:** k = m. This follows directly from Observation 11.

**Induction Step**: Let k be such that  $1 < k \le m$ .

• RUN  $A_k$ . Suppose there is a run  $A_k$  of  $\mathcal{I}$  that has property  $P_k$  (this is the induction hypothesis). We now show that there is a run  $A_{k-1}$  of  $\mathcal{I}$  that has property  $P_{k-1}$ .

Since run  $A_k$  of  $\mathcal{I}$  satisfies  $P_k$ , the following holds in  $A_k$  (see Figure 4):

- Up to and including time  $t_w^k$ , all processes behave exactly as in  $A_m$ .

- After taking step  $s^k$  at time  $t^k_w$ , w crashes before taking further steps.

- There is a reader q that is correct such that step  $s^k$  is invisible to q. After time  $t_w^k$ , reader q starts and completes a read operation on **R** that returns 1.

- There is a reader  $p \neq q$  that may be correct or malicious. After time  $t_w^k$ , reader p may or may not take steps.<sup>6</sup>

- There is a set Z of n-2 distinct readers other than p and q that are correct and take no steps.

• RUN  $B_{k-1}$ . From the run  $A_k$  of  $\mathcal{I}$  we construct the following run  $B_{k-1}$  of  $\mathcal{I}$  (Figure 5). Intuitively,  $B_{k-1}$  is exactly like  $A_k$  except that w crashes just before taking step  $s^k$  (so  $B_{k-1}$  is just  $A_k$  with the step  $s^k$  "removed"). Run  $B_{k-1}$  is possible because: (1) even though p may have "noticed" the removal of step  $s^k$ , p may be malicious (all the other readers are correct in this run), and p behaves exactly as in  $A_k$ , and (2) q cannot distinguish between  $A_k$  and  $B_{k-1}$  because  $s^k$  is invisible to q, and p and all the readers in Z behave as in  $A_k$ ; so q behaves as in  $A_k$ , and in particular q reads 1 in  $B_{k-1}$  as in  $A_k$ .

More precisely in  $B_{k-1}$ :

- All processes behave exactly as in  $A_k$  up to and including time  $t_w^{k-1}$ .

- After taking step  $s^{k-1}$  at time  $t_w^{k-1}$ , the writer w crashes before taking step  $s^k$ .

- $\blacksquare$  All the readers in Z are correct and take no steps, exactly as in  $A_k$ .

- **p** behaves exactly as in  $A_k$ . This is possible because even though p may have "noticed" the removal of step  $s^k$ , p may be malicious (all the other readers are correct in this run).

- q behaves exactly as in  $A_k$ . In particular, after time  $t_w^k$ , q starts and completes a read operation on **R** that returns 1. This is possible because q cannot distinguish between  $A_k$  and  $B_{k-1}$ :  $s^k$  is invisible to q, and p and all the readers in Z behave exactly as in  $A_k$ .

Note that in  $B_{k-1}$  all processes behave exactly as in  $A_m$  up to and including time  $t_w^{k-1}$ . There are two cases:

**Case 1:**  $s^{k-1}$  is invisible to q. Then  $B_{k-1}$  is a run of  $\mathcal{I}$  that has the property  $P_{k-1}$ , as we wanted to show.

**Case 2:**  $s^{k-1}$  is visible to q. Then, by Observation 9,  $s^{k-1}$  is invisible to p or to some  $r' \in Z$ . • RUN  $C_{k-1}^r$ . Let r be any reader in Z. From the run  $B_{k-1}$  of  $\mathcal{I}$  we construct the following run  $C_{k-1}^r$  of  $\mathcal{I}$  (Figure 6).  $C_{k-1}^r$  is a continuation of  $B_{k-1}$  where, after the correct reader q reads 1, malicious p wipes out any trace of the write steps that it may have taken so far, and then correct reader  $r \in Z$  reads 1 (this is the only value that r can read, since correct q previously read 1). More precisely:

$C_{k-1}^r$  is an extension of  $B_{k-1}$ : all processes behave exactly as in  $B_{k-1}$  up to and including the time when q completes its read operation on **R**.

$<sup>^{6}</sup>$  These steps are not shown in Figure 4.

#### 50:10 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

- All the readers in  $Z \{r\}$  are correct and take no steps<sup>7</sup>.

- After the correct reader q completes its read operation on  $\mathbf{R}$ :

- = q takes no steps.

- = p resets all the atomic registers that it can write to their initial values. Process p can do so because it may be malicious (all the other readers are correct in this run). Let  $t_p^r$  be the time when p completes all the register resettings.

- Correct reader r starts a read operation on **R** after time  $t_p^r$ . It takes no steps before this read. By the Termination property of the implementation, r completes its read operation. Since w is not malicious, and the read operation by correct q precedes the read operation by r and returns 1, by the linearizability of  $\mathcal{I}$ , the read operation by correct reader r also returns 1.

Note that in  $C_{k-1}^r$  all processes behave exactly as in  $A_m$  up to and including time  $t_w^{k-1}$ .

• RUN  $D_{k-1}^r$ . We can now construct the following run  $D_{k-1}^r$  of  $\mathcal{I}$  (Figure 7). Intuitively, we obtain  $D_{k-1}^r$  from  $C_{k-1}^r$  by removing all the steps of p. So reader p (which was malicious in  $C_{k-1}^r$ ) is now a correct process that takes no steps. Despite this removal, q behaves exactly as in  $C_{k-1}^r$  because q (which was correct in  $C_{k-1}^r$ ) may now be malicious. The writer w also behaves exactly as in  $C_{k-1}^r$  because it cannot see the removal of p's steps: they all occur after time  $t_w^{k-1}$ . Correct reader r behaves exactly as in  $C_{k-1}^r$  because it also cannot see the removal of p's steps: in both  $C_{k-1}^r$  and  $D_{k-1}^r$ , r does not "see" any steps of p. So r reads 1 in  $D_{k-1}^r$  as in  $C_{k-1}^r$ .

More precisely in  $D_{k-1}^r$ :

- w behaves exactly as in  $C_{k-1}^r$ .

- All the readers in  $Z \{r\}$  are correct and take no steps, as in  $C_{k-1}^r$ .

- p is correct and it takes no steps. So all the atomic registers that it can write retain their initial values.

- q behaves exactly as in  $C_{k-1}^r$ . This is possible because even though q may have "noticed" the removal of p's steps, q may be malicious (all the other readers are correct in this run).

- r behaves exactly as in  $C_{k-1}^r$ . In particular, after time  $t_p^r$  reader r starts and completes a read operation on **R** that returns 1. This is possible because r cannot distinguish between  $C_{k-1}^r$  and  $D_{k-1}^r$ : r cannot see the removal of p's steps, and q and all the readers in  $Z - \{r\}$  behave exactly as in  $C_{k-1}^r$ .

Note that in  $D_{k-1}^r$  all processes behave exactly as in S up to and including time  $t_w^{k-1}$ .

If  $s^{k-1}$  is invisible to reader r, it is clear that the run  $D_{k-1}^r$  of  $\mathcal{I}$  has property  $P_{k-1}$ .

Recall that (1) the reader r above is an *arbitrary* reader in Z, and (2)  $s^{k-1}$  is invisible to p or to some reader  $r' \in Z$ . So there are two cases:

**Subcase 2a:**  $s^{k-1}$  is invisible to some reader  $r' \in \mathbb{Z}$ . In the above we proved that the run  $D_{k-1}^{r'}$  of  $\mathcal{I}$  has property  $P_{k-1}$ , as we wanted to show.

Subcase 2b:  $s^{k-1}$  is invisible to p.

• RUN  $E_{k-1}^r$ . We construct the continuation  $E_{k-1}^r$  of  $D_{k-1}^r$  shown in Figure 8: after r reads 1, malicious process q wipes out any trace of the write steps that it has taken so far, and then correct reader p starts a read operation on **R**. By the Termination property of the implementation, this read operation by p must complete. Since correct r previously read 1, by the linearizability of  $\mathcal{I}$ , p must also read 1.

More precisely in  $E_{k-1}^r$ :

- $= E_{k-1}^r$  is an extension of the run  $D_{k-1}^r$ : all processes behave exactly as in  $D_{k-1}^r$  up to and including the time when r completes its read operation on **R**.

- All the readers in  $Z \{r\}$  are correct and take no steps, as in  $D_{k-1}^r$ .

- After the correct reader r completes its read operation on  $\mathbf{R}$ :

- r takes no steps.

<sup>&</sup>lt;sup>7</sup> If n = 3, then the set  $Z - \{r\}$  is empty.

#### X. Hu and S. Toueg

- = q resets all the atomic registers that it can write to their initial values. Process q can do so because it may be malicious (all the other readers are correct in this run). Let  $t_a^r$  be the time when q completes all the register resettings.

- Correct reader p starts a read operation on  $\mathbf{R}$  after time  $t_q^r$ . It takes no steps before this read. By the Termination property of the implementation, p completes its read operation. Since w is not malicious, and the read operation by correct r precedes the read operation by p and returns 1, by the linearizability of  $\mathcal{I}$ , the read operation by correct reader p also returns 1.

Note that in  $E_{k-1}^r$  all processes behave exactly as in  $A_m$  up to and including time  $t_w^{k-1}$ .

• Run  $F_{k-1}^r$ . Finally, we construct the run  $F_{k-1}^r$  of  $\mathcal{I}$  by removing all the steps of q from  $E_{k-1}^r$  (see Figure 9); so q (which was malicious in  $E_{k-1}^r$ ) is now a correct process that takes no steps. Despite this removal, r behaves exactly as in  $E_{k-1}^r$  because r (which was correct in  $E_{k-1}^r$ ) may now be malicious. The writer w also behaves exactly as in  $E_{k-1}^r$  because it cannot see the removal of q's steps: they all occur after time  $t_w^{k-1}$ . Finally, correct p behaves exactly as in  $E_{k-1}^r$  because it also cannot see the removal of q's steps: in both  $E_{k-1}^r$  and  $F_{k-1}^r$ , p does not "see" any steps of q. So p reads 1 in  $F_{k-1}^r$  as in  $E_{k-1}^r$ .

More precisely in  $F_{k-1}^r$ :

- $\blacksquare$  w behaves exactly as in  $E_{k-1}^r$ .

- All the readers in  $Z \{r\}$  are correct and take no steps, as in  $E_{k-1}^r$ .

- q is correct and it takes no steps. So all the atomic registers that it can write retain their initial values.

- r behaves exactly as in  $E_{k-1}^r$ . This is possible because even though r may have "noticed" the removal of q's steps, r may be malicious (all the other readers are correct in this run).

- p behaves exactly as in  $E_{k-1}^r$ . In particular, after time  $t_q^r$  reader p starts and completes a read operation on **R** that returns 1. This is possible because p cannot distinguish between  $E_{k-1}^r$  and  $F_{k-1}^r$ : p cannot see the removal of q's steps, and r and all the readers in  $Z - \{r\}$  behave exactly as in  $E_{k-1}^r$ .

Note that in  $F_{k-1}^r$  all processes behave exactly as in  $A_m$  up to and including time  $t_w^{k-1}$ .

Since  $s^{k-1}$  is invisible to p, it is clear that the run  $F_{k-1}^r$  of  $\mathcal{I}$  has property  $P_{k-1}$ .

The above concludes the proof of the Induction Step of Claim 12: we proved that, in all possible cases, there is a run of  $\mathcal{I}$  that has property  $P_{k-1}$ , as we needed to show.

By the Claim 12 that we just proved, the implementation  $\mathcal{I}$  of **R** has a run  $A_1$  with property  $P_1$ . By this property, the following holds in  $A_1$  (see Figure 10):

- Up to and including time  $t_w^1$ , all processes behave exactly as in  $A_m$ .

- After taking step  $s^1$  at time  $t^1_w$ , w crashes before taking further steps.

- There is a reader q that is correct such that step  $s^1$  is invisible to q. After time  $t_w^1$ , reader q starts and completes a read operation on **R** that returns 1.

- There is a reader  $p \neq q$  that may be correct or malicious. After time  $t_w^1$ , reader p may or may not take steps.

- There is a set Z of n-2 distinct readers other than p and q that are correct and take no steps.

From the run  $A_1$  of  $\mathcal{I}$  we construct the following run  $A_0$  of  $\mathcal{I}$  (Figure 11). Intuitively,  $A_0$  is the same as  $A_1$  except that the writer is correct and does not take any steps (i.e., w does not invoke a write 1 operation on  $\mathbf{R}$ ), but all the readers behave the same as in  $A_1$  and so q still reads 1. This run of  $\mathcal{I}$  is possible because: (1) even though p may have "noticed" that w does not take the step  $s^1$ , p may be malicious (all the other readers are correct in this run), and p behaves exactly as in  $A_1$ , and (2) q cannot distinguish between  $A_1$  and  $A_0$  because  $s^1$  is invisible to q, and p and all the readers in Z behave as in  $A_1$ . So q reads 1 from  $\mathbf{R}$  in  $A_0$  exactly as in  $A_1$ . Since the initial value of the implemented register  $\mathbf{R}$  is 0, run  $A_0$  of the implementation  $\mathcal{I}$  of  $\mathbf{R}$  violates the linearizability of  $\mathcal{I}$  — a contradiction that concludes the proof of Theorem 7.

#### 50:12 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

It is easy to verify that the above proof holds (without any change) even if every reader is given atomic [1, n]-registers that it can write and *all* other processes can read, and the writer is the only process that does not have an atomic [1, n]-register. Thus:

▶ **Theorem 13.** For all  $n \ge 3$ , in a system with n+1 processes that are subject to Byzantine failures, there is no linearizable implementation of a [1, n]-register that satisfies Termination, even under the assumption that:

- the writer w of the implemented [1, n]-register can only crash and at most one reader can be malicious, and

- $\bullet$  w has atomic [1, n-1]-registers, and every reader has atomic [1, n]-registers.

# 5 Register implementation algorithm

We now give an implemention of a [1, n]-register from atomic [1, 1]-registers in systems with Byzantine process failures; this implementation is linearizable, and it satisfies the Termination property provided the writer of the register *or* any number of the readers, *but not both*, can be faulty. More precisely, it is a *valid* implementation, as we define below.

- ▶ **Definition 14.** A register implementation is valid if the following holds:

- It is linearizable.

- If the writer is correct or no reader is malicious, it satisfies the Termination property.

Note that, when executed in a system where processes can only crash, a valid register implementation is linearizable and "terminating" (unconditionally).

#### 5.1 Some difficulties to overcome

Note that in a system with Byzantine process failures, implementing a [1, n]-register from [1, 1]-registers is non-trivial, even if the writer can only crash. To see this, we now illustrate some of the issues that arise. First note that with [1, 1]-registers the writer cannot *simultaneously* inform all the readers about a new write. So different readers may have different views of whether there is a write in progress: some readers may not see it, some readers may see it as still in progress, while other readers may see it as having completed. Thus readers must communicate with each other to avoid "new-old" inversions in the values they read. With non-Byzantine failures, readers can easily coordinate their reads because they can trust the information they pass to each other. With Byzantine failures, however, readers cannot blindly trust what other readers tell them.

For example, suppose a reader q is aware that a write v operation is in progress (say because the writer w directly "told" q about it via the register that they share). To avoid a "new-old" inversion, q checks whether any other reader q' has already read v (because it is possible that from q''s point of view, the write of v already completed). Suppose some q' "warns" q that it has already read the new value v, and so q also reads v. But what if q' is malicious and "lied" to q (and only to q) about having read v? Note that q may be the *only* correct reader currently aware that the write of v is in progress (say because w is slow). Now suppose that a reader q'' that is *not* aware of the write of v also wants to read: if q'' reads the old value of the register this creates a "new-old" inversion with the newer value v that q previously read; but if q'' reads v because q warns q'' that it had read v, then q'' may be reading a value v*that was never written by the correct writer* w: q itself could be malicious and could have "lied" about reading v!

The above is only one of many possible scenarios illustrating why it is not easy to implement a [1, n]-register from [1, 1]-registers when some readers can be malicious, even if the writer itself is not malicious.

To simplify this task, we do not *directly* implement a [1, n]-register using *only* [1, 1]-registers. Instead, we first give an implementation  $I_n$  of a [1, n]-register that uses some [1, n - 1]-registers together with some [1, 1]-registers. Then, by replacing the [1, n - 1]-registers with  $I_{n-1}$  implementations, we get an implementation of the [1, n]-register that uses some [1, n - 2]-registers and some [1, 1]-registers. By recursing down to n = 2, this gives an implementation of the [1, n]-register that uses only [1, 1]-registers. In other words, we can implement a [1, n]-register from [1, 1]-registers with a *recursive* construction that gradually reduces the number of readers of the base registers that it uses (all the way down to 1). We now describe this recursive implementation and prove its correctness.

# **5.3** Implementing a [1, n]-register from [1, n-1]-registers

Algorithm 1 is an implementation  $I_n$  of a [1, n]-register that is writable by a process w and readable by every process in  $\{p\} \cup Q$ , where p is an arbitrary reader and all remaining n-1readers are in Q. We distinguish p from the other readers in Q because p and  $q \in Q$  use different procedures for reading the implemented [1, n]-register.  $I_n$  uses two kinds of registers: *atomic* [1, 1]-registers and *implemented* [1, n-1]-registers. We will show that  $I_n$  is *valid* under the assumption that the [1, n-1]-register implementations that it uses are also *valid*. **Notation.** Recall that if R is an atomic register, all operations applied to R are instantaneous, whereas if R is an implemented register, each operation spans an interval of time, from an invocation to a response. However, since we assume that the [1, n-1]-register implementations that  $I_n$  uses are valid and therefore *linearizable*, we can think of each operation on an implemented [1, n-1]-register as being atomic, i.e., as if it takes effect instantaneously at some point during its execution interval [10]. Thus to read or write a register R we use the same notation, irrespective of whether R is atomic or implemented. In particular, in our implementation algorithm (shown in Figure 1) we use the following notation:

= " $R \leftarrow v$ " denotes the operation that writes v into R.

**"if** R = val then ..." means "read register R and if the value read is equal to val then ..." The shared registers used by the implementation are as follows:

$R_{ss'}$  is an atomic [1,1]-register writable by process s and readable by process s'.<sup>8</sup>

$\blacksquare$   $R_{wQ}$  is an implemented [1, n-1]-register writable by w and readable by every  $q \in Q$ .

$\blacksquare$   $R_{pQ}$  is an implemented [1, n-1]-register writable by p and readable by every  $q \in Q$ .

Algorithm description. The implementation  $I_n$  of a [1, n]-register from [1, n - 1]-registers consists of two procedures, namely WRITE() for the writer w, and READ() for each reader rin  $\{p\} \cup Q$ . To write a value u, the writer w executes WRITE(u). If u is the k-th value written by w, WRITE(u) first forms the unique tuple  $\langle k, u \rangle$  and then it calls the lower-level write procedure W( $\langle k, u \rangle$ ) to write this tuple. Intuitively, WRITE() tags the values that it writes with a counter value to make them unique and to indicate in which order they are written. To read a value, a reader  $r \in \{p\} \cup Q$  calls READ(), and this in turn calls a lower-level read procedure  $\mathbb{R}_r()$  that reads tuples written by W(). There are two version of the procedure  $\mathbb{R}_r()$ : one used when r = p and one used when  $r \in Q$ . If  $\mathbb{R}_r()$  returns a tuple of the form  $\langle j, v \rangle$ , then READ() strips the counter j from the tuple and returns the value v as the value read (otherwise READ() returns  $\perp$  to indicate a read failure).

Thus the lower-level procedures W(),  $R_p()$ , and  $R_q()$  for each  $q \in Q$ , are executed to write and read unique tuples of the form  $\langle k, u \rangle$ . We now describe how these procedures work.

• To execute  $W(\langle k, u \rangle)$ , process w first writes (PREPARE, *last\_written*,  $\langle k, u \rangle$ ) in the  $R_{wp}$  register that p can read, and then in the  $R_{wQ}$  register that every process in Q can read;

<sup>&</sup>lt;sup>8</sup> If s = s', this "shared register" is actually just a local register of process s.

# 50:14 On implementing SWMR registers from SWSR registers in systems with Byzantine failures

**Algorithm 1** Implementation  $I_n$  of a [1, n]-register writable by (an arbitrary) process w and readable by the n processes in  $\{p\} \cup Q$ , for  $n \ge 2$ . It uses two [1, n-1]-registers and some [1, 1]-registers.

| ATOMIC REGIS<br>$B \cdot \begin{bmatrix} 1 & 1 \end{bmatrix}_{-1}$                                                                                        |                                                                                                                                                                                                     | LOCAL VARIABLES<br>c: variable of $w$ ; initially 0<br>$last\_written$ : variable of $w$ ; initially $\langle 0, u_0 \rangle$<br>$previous\_k$ : variable of $p$ ; initially 0 |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| For all proc                                                                                                                                              | register; initially (COMMIT, $\langle 0, u_0 \rangle$ )<br>esses $q$ and $q'$ in $Q$ :<br>[1, 1]-register; initially $\langle 0, u_0 \rangle$                                                       |                                                                                                                                                                                |  |  |  |

| Implemented                                                                                                                                               | Registers                                                                                                                                                                                           |                                                                                                                                                                                |  |  |  |

| $R_{wQ}$ : $[1, n - 1]$ -register; initially (COMMIT, $\langle 0, u_0 \rangle$ )<br>$R_{pQ}$ : $[1, n - 1]$ -register; initially $\langle 0, u_0 \rangle$ |                                                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

| WRITE $(u)$ :                                                                                                                                             |                                                                                                                                                                                                     | $\operatorname{READ}(): \ \triangleright \text{ executed by any reader } r \text{ in } \{p\} \cup Q$                                                                           |  |  |  |

| 1: $c \leftarrow c +$<br>2: <b>call</b> W(                                                                                                                |                                                                                                                                                                                                     | 4: <b>call</b> $R_r()$<br>5: <b>if</b> this call returns some tuple $\langle k, u \rangle$ <b>then</b>                                                                         |  |  |  |

| 2: call w(<br>3: return                                                                                                                                   |                                                                                                                                                                                                     | 6: return $u$                                                                                                                                                                  |  |  |  |

|                                                                                                                                                           |                                                                                                                                                                                                     | 7: else return $\perp$                                                                                                                                                         |  |  |  |

| $W(\langle k, u \rangle)$ :                                                                                                                               |                                                                                                                                                                                                     | $\triangleright$ executed by $w$ to do its $k$ -th write                                                                                                                       |  |  |  |

|                                                                                                                                                           | $(PREPARE, last_written, \langle k, u \rangle)$                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | $(\text{PREPARE}, last\_written, \langle k, u \rangle) \\ (\text{COMMIT}, \langle k, u \rangle)$                                                                                                    |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | $(\text{COMMIT}, \langle k, u \rangle)$                                                                                                                                                             |                                                                                                                                                                                |  |  |  |

| 12: $last\_w$                                                                                                                                             | $ritten \leftarrow \langle k, u \rangle$                                                                                                                                                            |                                                                                                                                                                                |  |  |  |

| 13: return                                                                                                                                                | done                                                                                                                                                                                                |                                                                                                                                                                                |  |  |  |

| $R_p()$ :                                                                                                                                                 |                                                                                                                                                                                                     | $\triangleright$ executed by reader $p$                                                                                                                                        |  |  |  |

| 14: <b>if</b> $R_{wp}$                                                                                                                                    | = (COMMIT, $\langle k, u \rangle$ ) for some $\langle k, u \rangle$ y                                                                                                                               | with $k \ge previous\_k$ then                                                                                                                                                  |  |  |  |

|                                                                                                                                                           | $R_{pQ} \leftarrow \langle k, u \rangle$                                                                                                                                                            |                                                                                                                                                                                |  |  |  |

| 1                                                                                                                                                         | $\frac{previous_k \leftarrow k}{pature}$                                                                                                                                                            |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | return $\langle k, u \rangle$                                                                                                                                                                       |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | elseif $R_{wp} = (\text{PREPARE}, last\_written, -)$ for some $last\_written$ then<br>return $last\_written$                                                                                        |                                                                                                                                                                                |  |  |  |

| 20: else re                                                                                                                                               |                                                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

| P ():                                                                                                                                                     |                                                                                                                                                                                                     | $\land$ executed by any reader $a$ in $O$                                                                                                                                      |  |  |  |

|                                                                                                                                                           | $R_q(): \qquad \qquad \triangleright \text{ executed by any reader } q \text{ in } \zeta$ 1: <b>if</b> $R_{wQ} = (\text{COMMIT}, \langle k, u \rangle)$ for some $\langle k, u \rangle$ <b>then</b> |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           |                                                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           |                                                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

| 24: <b>cob</b>                                                                                                                                            |                                                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | repeat forever                                                                                                                                                                                      |                                                                                                                                                                                |  |  |  |

| 26:                                                                                                                                                       | if $R_{wQ} = (\text{COMMIT}, \langle k', - \rangle)$ for s                                                                                                                                          | some $k' \ge k$ then                                                                                                                                                           |  |  |  |

| 27:                                                                                                                                                       | return $\langle k, u \rangle$                                                                                                                                                                       |                                                                                                                                                                                |  |  |  |

| 28:                                                                                                                                                       | if $R_{wQ} = (\text{PREPARE}, -, \langle k', - \rangle)$ for some $k' > k$ then                                                                                                                     |                                                                                                                                                                                |  |  |  |

| 29:                                                                                                                                                       | $\mathbf{return}\left\langle k,u\right\rangle$                                                                                                                                                      |                                                                                                                                                                                |  |  |  |

| 11                                                                                                                                                        | THREAD 2                                                                                                                                                                                            |                                                                                                                                                                                |  |  |  |

| 30: i                                                                                                                                                     | if $R_{pQ} = \langle k', - \rangle$ for some $k' \ge k$ then                                                                                                                                        |                                                                                                                                                                                |  |  |  |

| 31:                                                                                                                                                       | for every process $q' \in Q$ do $R_q$                                                                                                                                                               | $_{q'} \leftarrow \langle k, u \rangle$                                                                                                                                        |  |  |  |

| 32:                                                                                                                                                       | return $\langle k, u \rangle$                                                                                                                                                                       |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | elseif $R_{q'q} = \langle k', - \rangle$ for some $q' \in Q$ and some $k' \ge k$ then                                                                                                               |                                                                                                                                                                                |  |  |  |

| 34:<br>25.                                                                                                                                                | if $R_{pQ} = \langle k', - \rangle$ for some $k' \ge k$                                                                                                                                             |                                                                                                                                                                                |  |  |  |

| 35:<br>36:                                                                                                                                                | for every process $q' \in Q$ do $R_{qq'} \leftarrow \langle k, u \rangle$<br>return $\langle k, u \rangle$                                                                                          |                                                                                                                                                                                |  |  |  |

| 37:                                                                                                                                                       | else exit Thread 2                                                                                                                                                                                  |                                                                                                                                                                                |  |  |  |

|                                                                                                                                                           | else return last_written                                                                                                                                                                            |                                                                                                                                                                                |  |  |  |

| 38: 6                                                                                                                                                     | eise return <i>iusi_written</i>                                                                                                                                                                     |                                                                                                                                                                                |  |  |  |

| 38:     6       39:     coe       40:     else re                                                                                                         | nd                                                                                                                                                                                                  |                                                                                                                                                                                |  |  |  |

*last\_written* is the *last* tuple written by w before  $\langle k, u \rangle$  (so *last\_written* =  $\langle k - 1, u' \rangle$  for some u'). Then, w writes (COMMIT,  $\langle k, u \rangle$ ) into  $R_{wp}$  and then into  $R_{wQ}$ .

#### X. Hu and S. Toueg

• To execute  $R_p()$ , process p reads  $R_{wp}$  (line 14). If p reads (COMMIT,  $\langle k, u \rangle$ ) with a k at least as big as those it saw before, it returns  $\langle k, u \rangle$  as the tuple read (line 17); just before doing so, however, it writes  $\langle k, u \rangle$  in the  $R_{pQ}$  register that every process  $q \in Q$  can read (line 15): intuitively, this is to "warn" them that p read a "new" tuple, to help avoid "new-old" inversions in the tuples read.

If p reads (PREPARE,  $last\_written, -$ ) (line 18), then it returns  $last\_written$  as the tuple read (without giving any "warning" about this to processes in Q).

If p reads anything else from  $R_{wp}$ , then it returns  $\perp$  (the writer is surely malicious).

• To execute  $R_q()$ , process  $q \in Q$  reads  $R_{wQ}$ . If q reads (COMMIT,  $\langle k, u \rangle$ ) (line 21), it just returns  $\langle k, u \rangle$  as the tuple read in line 22 (without "warning" other processes).

If q reads (PREPARE, last\_written,  $\langle k, u \rangle$ ) (line 23), then q cannot simply return last\_written as the tuple read: this is because p could have already read (COMMIT,  $\langle k, u \rangle$ ) from  $R_{wp}$  and so p could have already read the "newer" tuple  $\langle k, u \rangle$  with  $R_p()$ . So q must determine whether to return last\_written or  $\langle k, u \rangle$ . To do so, q forks two threads and executes them in parallel (we will explain why below).

If q does not read values of the form (PREPARE, *last\_written*,  $\langle k, u \rangle$ ) or (COMMIT,  $\langle k, u \rangle$ ) from  $R_{wQ}$ , then q just returns  $\perp$  in line 40 (w is surely malicious).

In THREAD 1, process q keeps reading  $R_{wQ}$ : if it ever reads (COMMIT,  $\langle k', - \rangle$ ) with  $k' \ge k$ , or (PREPARE,  $-, \langle k', - \rangle$ ) with k' > k, it simply returns  $\langle k, u \rangle$  as the tuple read. Note that if the writer w is correct, then q cannot spin forever in this thread without returning  $\langle k, u \rangle$ .

In THREAD 2, process q first reads the register  $R_{pQ}$  to see whether p "warned" processes in Q that it read a tuple at least as "new" as  $\langle k, u \rangle$ .

- If q sees that  $R_{pQ}$  contains a tuple at least as "new" as  $\langle k, u \rangle$  (line 30), then q returns  $\langle k, u \rangle$  as the tuple read (line 32); but before doing so, q successively writes  $\langle k, u \rangle$  in each register  $R_{qq'}$  such that  $q' \in Q$  (line 31): intuitively, this is to "warn" each process in Q that q read this "new" tuple.

- Otherwise, q reads every  $R_{q'q}$  register to avoid a new-old inversion with any tuple read by any process  $q' \in Q$ : if q sees that some  $R_{q'q}$  contains a tuple at least as "new" as  $\langle k, u \rangle$ (line 33), then q reads  $R_{pQ}$  again (line 34) (so q does not simply "trust" q' and return  $\langle k, u \rangle$ !). If q sees that  $R_{pQ}$  contains a tuple at least as "new" as  $\langle k, u \rangle$  (line 34), then q successively writes  $\langle k, u \rangle$  to every register  $R_{qq'}$  such that  $q' \in Q$  (line 35), and it returns  $\langle k, u \rangle$  as the tuple read (line 36); else q exits THREAD 2 (so in this case only THREAD 1 remains).

- Finally, if q does not see that  $R_{pQ}$  or any  $R_{qq'}$  contains a tuple at least as "new" as  $\langle k, u \rangle$  (in lines 30 and 33), then q returns *last\_written* (line 38).

Why two parallel threads? In a nutshell, this is to guarantee the Termination property of  $I_n$  in runs where the writer is correct or no reader is malicious (this property is required for the implementation to be valid). It turns out that:

- (A) if only THREAD 1 is executed, then a faulty writer can block correct readers even if no reader is malicious, and

- (B) if only THREAD 2 is executed, then malicious readers can block correct readers from returning any value in this thread even if the writer is correct.

But if the writer is correct or no reader is malicious, we can show that every read operation by a correct reader is guaranteed to complete with a return value *in one of the two threads*. It is easy to see why a faulty writer (even one that just crashes) may block a correct reader in THREAD 1. We now explain how malicious readers may impede correct readers in THREAD 2. In THREAD 2 readers must read  $R_{pQ}$  at least once (in line 30). Recall that (a)  $R_{pQ}$  is an *implemented* [1, n - 1]-register, and (b) we are only assuming that this implementation is valid. In particular, if the writer p of  $R_{pQ}$  crashes and some readers of  $R_{pQ}$  are malicious, the implementation of  $R_{pQ}$  does not guarantee that correct readers complete their operations. In other words, if p crashes and some readers of  $R_{pQ}$  are malicious, a correct reader q may block while trying to read  $R_{pQ}$ !

#### 50:16 On implementing SWMR registers from SWSR registers in systems with Byzantine failures