# Electrical Gating of the Charge-Density-Wave Phases in Quasi-2D h-BN/1T-TaS<sub>2</sub> Devices

Maedeh Taheri<sup>1</sup>, Jonas Brown<sup>1</sup>, Adil Rehman<sup>2</sup>, Nicholas R. Sesing<sup>3</sup>, Fariborz Kargar<sup>1,4</sup>, Tina T. Salguero<sup>3</sup>, Sergey Rumyantsev<sup>2</sup>, and Alexander A. Balandin<sup>1,4\*</sup>

<sup>1</sup>Nano-Device Laboratory, Department of Electrical and Computer Engineering, Bourns College of Engineering, University of California, Riverside, California 92521 U.S.A.

<sup>2</sup>CENTERA Laboratories, Institute of High-Pressure Physics, Polish Academy of Sciences, Warsaw 01-142 Poland

<sup>3</sup>Department of Chemistry, University of Georgia, Athens, Georgia 30602 U.S.A.

<sup>4</sup>Phonon Optimized Engineered Materials Center, Materials Science and Engineering Program, Bourns College of Engineering, University of California, Riverside, California 92521 U.S.A.

<sup>\*</sup> Corresponding author (A.A.B.): <u>balandin@ece.ucr.edu</u>; web-site: <u>http://balandingroup.ucr.edu/</u>

### **Abstract**

We report on electrical gating of the charge-density-wave phases and current in *h*-BN capped three-terminal 1T-TaS<sub>2</sub> heterostructure devices. It is demonstrated that the application of a gate bias can shift the source-drain current-voltage hysteresis associated with the transition between the nearly commensurate and incommensurate charge-density wave phases. The evolution of the hysteresis and the presence of abrupt spikes in the current while sweeping the gate voltage suggest that the effect is electrical rather than self-heating. We attribute the gating to an electric-field effect on the commensurate charge-density-wave domains in the atomic planes near the gate dielectric. The transition between the nearly commensurate and incommensurate charge-density-wave phases can be induced by both the source-drain current and the electrostatic gate. Since the charge-density-wave phases are persistent in 1T-TaS<sub>2</sub> at room temperature, one can envision memory applications of such devices when scaled down to the dimensions of individual commensurate domains and few-atomic plane thicknesses.

**Keywords:** charge-density-waves; de-pinning; gating; 2D van der Waals materials; TaS<sub>2</sub>

The charge-density-wave (CDW) phase is a macroscopic quantum state consisting of a periodic modulation of the electronic charge density accompanied by a periodic distortion of the atomic lattice <sup>1-3</sup>. The early work on CDW effects, performed with bulk samples of the quasi-one-dimensional (1D) metallic crystals, revealed many spectacular phenomena — nonlinear electron transport, oscillating electric current for constant voltages, giant dielectric response, and multistable conducting states <sup>1-4</sup>. Recent years witnessed a rebirth of the field of CDW materials and devices, partially driven by an interest in layered quasi-2D van der Waals materials where CDW phases can manifest themselves at room temperature (RT) and above <sup>5-21</sup>. The size and geometry of quasi-2D CDW films provide new opportunities for device fabrication. The first reports of depinning of CDWs in quasi-2D materials have emerged suggesting common features among CDW phenomena in quasi-1D and quasi-2D systems <sup>22-23</sup>. However, there is also an understanding of differences in physics governing CDW phases in material systems of different dimensionalities and crystal structures <sup>24-25</sup>.

The 1T polymorph of TaS<sub>2</sub> is one of the prominent members of the quasi-2D van der Waals materials of the transition-metal dichalcogenide group that reveals several CDW phases and transitions between them, in the form of resistivity changes and hysteresis <sup>10, 14-15, 18-21</sup>. Two of the phase transitions in 1T-TaS2 are above RT. These transitions can be induced by temperature, electric current, light, and other stimuli. It was noted in the prior works that 1T-TaS<sub>2</sub> CDW devices have the potential for application in oscillators, detectors, and radiation-hard electronics <sup>21, 26-28</sup>. The devices reported to date, were two-terminal, with the resistive state and hysteresis controlled by the source-drain current via the voltage-controlled resistor connected in series <sup>21, 27</sup>. These CDW devices utilized the hysteresis window and negative feedback for their operation rather than the on-off ratio in the resistance change. There have been reports that described CDW transitions in 1T-TaS<sub>2</sub> induced by visible light or electromagnetic radiation in MHz – GHz frequency range <sup>29-31</sup>. The question of the role of local heating in CDW devices, as a result of passing current, remains open. It likely depends on the specific device design and the speed of switching 18, 21, 32-<sup>34</sup>. Despite numerous attempts, the electrical gating of the CDW phase remains elusive. Apart from the demonstrated possibility of modulating 1T-TaS<sub>2</sub> properties via ion intercalation in chemical field-effect transistors <sup>15</sup>, we are not aware of any successful demonstration of changing the source-drain current and the current hysteresis by the application of a gate bias. Gating of CDW phases, particularly near RT, would substantially enhance the functionality of the CDW devices and open novel application domains, *e.g.* in non-volatile memory. Electrical gating is also important for answering a fundamental science question: "Can one achieve an electrical switching of CDW phase *via* the pure field effect, without any local Joule heating involved?"

The main difficulty of electrical gating of the CDW phases and currents in 2D van der Waals materials is associated with the fact that different phases still have a rather high concentration of charge carriers. Below 550 K, 1T-TaS<sub>2</sub> is in the metallic-like incommensurate CDW (IC-CDW) phase. The nearly commensurate phase (NC-CDW) appears below 350 K and persists approximately until 180 K. Below this temperature, 1T-TaS<sub>2</sub> enters the commensurate CDW (C-CDW) phase. In the NC-CDW phase, the hexagonal-shaped C-CDW clusters are separated by the incommensurate regions. As the temperature increases to 350 K, the domains melt, and the material falls into the IC-CDW state. The transition from the NC-CDW phase to the IC-CDW phase reveals itself as a change in the resistivity of the device channel accompanied by hysteresis. The carrier concentrations in these two CDW states are high:  $10^{21}$  cm<sup>-3</sup> and  $10^{22}$  cm<sup>-3</sup> for the higher resistive NC-CDW and lower resistive IC-CDW phases, respectively <sup>15, 35</sup>. The high concentration of charge carriers, N, results in a small relative change of the carrier concentration,  $\delta N/N$ , due to the large N and strong screening of the gate potential. Reducing the thickness of 1T-TaS<sub>2</sub> thin film for a stronger gating effect is not necessarily a viable approach because at small thicknesses the CDW phases can be locked and some phase transitions disappear <sup>15, 36-37</sup>. It is known that the NC-CDW – C-CDW transition disappears when the 1T-TaS<sub>2</sub> channel thickness decreases below ~9 nm <sup>15, 37</sup>. On the other side, the incommensurate regions, also referred to as the discommensurate network, may be rather narrow in the NC-CDW phase. The latter may reduce the screening of the electrical field created by the gate, allowing for its deeper penetration to the channel layer. The above considerations can be relevant to other quasi-2D CDW van der Waals materials.

In this Communication, we report the first successful demonstration of the electrostatic gating of the current in the NC-CDW phase near RT, and the electric field switching of the CDW phases in quasi-2D CDW van der Waals materials. It is demonstrated that the hysteresis in the source-drain current-voltage (I-V) characteristics that accompany the transition between the NC-CDW

and IC-CDW phases can be shifted by applying a gate bias. The effect is electrical rather than self-heating. We also show that the transition between the NC-CDW and IC-CDW can be induced both by the source-drain current and the electrostatic gate.

# **Results**

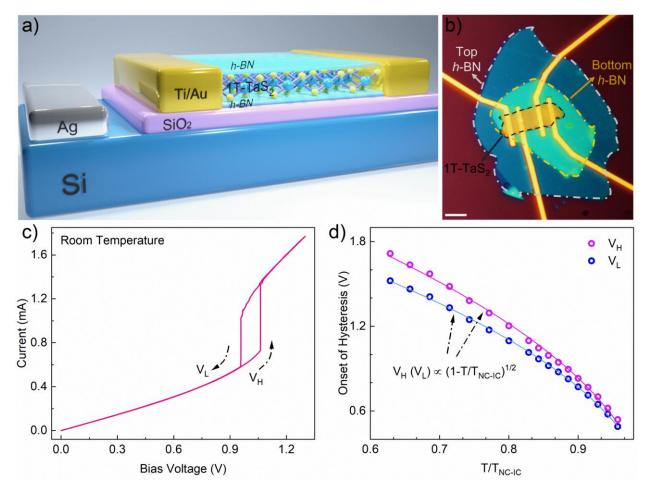

**Device fabrication and testing.** The bulk 1T-TaS<sub>2</sub> crystals for this study were grown by the chemical vapor transport (CVT) method <sup>16, 18, 38-41</sup>; structure and composition were confirmed by X-ray diffraction and energy dispersive spectroscopy, respectively. The thin films of the material were mechanically exfoliated from the small 1T-TaS<sub>2</sub> crystals and transferred onto Si/SiO<sub>2</sub> substrates. For fabricating the device channels, we selected thin films with thicknesses ranging from ~15 nm to ~35 nm. The layers of 1T-TaS<sub>2</sub> were capped with electrically insulating thin films of h-BN with a few nm thicknesses for protection from environmental exposure and degradation <sup>21, 37, 42</sup>. This design also improves heat dissipation from the 1T-TaS<sub>2</sub> channel owing to the high thermal conductivity of h-BN. For comparison, the bulk thermal conductivity of  $1T-TaS_2$  in the NC-CDW state is ~ 4 W/mK to 6 W/mK while that of a few-layer h-BN is ~ 360 W/mK  $^{18, 43-44}$ . We have also experimented with a more sophisticated design where two layers of h-BN were used so that the 1T-TaS<sub>2</sub> channel is completely encapsulated with h-BN. Figure 1a shows the schematic of h-BN-encapsulated 1T-TaS<sub>2</sub> devices. The performance of h-BN capped and h-BN encapsulated devices was similar and discussed jointly in the text below. The source-drain contacts were patterned with the electron beam lithography followed by the atomic layer etching step to remove the h-BN layer underneath the contacts. The evaporation of Ti / Au with 10 nm / 100 nm thicknesses was used to fabricate device structures with the lateral dimensions of 1  $\mu$ m – 3  $\mu$ m by  $1 \mu m - 3.5 \mu m$ . The back gate consisted of a silver contact deposited on the highly doped Si substrate. The 300-nm thick layer of SiO<sub>2</sub> acted as the gate dielectric. An optical microscopy image of a representative h-BN/1T-TaS<sub>2</sub>/h-BN device structure is presented in Figure 1b.

Figure 1: Device structure and current-voltage characteristics. (a) Schematic of 1T-TaS<sub>2</sub> heterostructure devices encapsulated in h-BN layers. For some devices, only the top h-BN capping layer was used. In 1T-TaS<sub>2</sub> crystal, the Ta atoms are depicted in blue while sulfurs are in yellow colors. (b) Optical image of the fabricated device with the channel thicknesses of ~35 nm. The scale bar is 5  $\mu$ m. (c) I-V characteristics of 1T-TaS<sub>2</sub> device at room temperature. The arrows indicate the direction of source-drain bias sweep. (d) Dependency of the hysteresis onset voltages,  $V_H$  and  $V_L$ , on temperature. The theory fitting  $(1-T/T_{NC-IC})^{1/2}$  is shown with the purple and blue curves for  $V_H$  and  $V_L$ , respectively. The measured  $T_{NC-IC}$  for this device is 350 K.

We have tested about 20 different h-BN/1T-TaS<sub>2</sub> devices with varying channel thickness, H < 35nm, and source-drain separation, L. Typical I-Vs with the signature hysteresis, measured at RT for a device with a channel thickness of ~ 15 nm, can be seen in Figure 1c. The voltage sweep direction is indicated by arrows. The hysteresis is due to the NC-CDW to IC-CDW phase transition. Measured as a function of temperature at small electric biases, i.e., near-equilibrium conditions, this transition occurs at 350 K. In our measurements, the ambient temperature was kept constant, and the transition was triggered by applying the source-drain voltage and passing a current through the channel. Our prior studies for 1T-TaS<sub>2</sub> devices on Si/SiO<sub>2</sub> substrates, without h-BN capping, indicated that the local Joule heating produced by the current is essential for inducing the phase transition  $^{18, 32}$ . The temperature dependence of the threshold voltages,  $V_H$  and  $V_L$ , follows the relation  $(1-T/T_{NC-IC})^{1/2}$  (see Figure 1d). This temperature dependence agrees with prior studies and is explained by the theories of the CDW order parameter <sup>21</sup>. The hysteresis part of the I-V provides functionality for CDW devices such as voltage-controlled oscillators that can operate at RT <sup>21, 29</sup>. A possibility of affecting the hysteresis with the electrostatic gate or changing the electrical current with the gate voltage in the linear part of the I-Vs would substantially increase the functionality of CDW devices.

Electrical gating of CDW phases and current. First, we attempted to change the I-Vs by applying the gate bias,  $V_g$ , in the range from -20 V to 40 V. The values of the gate bias are rather large due to the back-gate design and thick layers of SiO<sub>2</sub> dielectric. As mentioned above, it is unlikely that one can change the total current substantially, owing to the high carrier concentration and the large thickness of the samples. The collective CDW current in 2D materials is also small <sup>45</sup>. There is no well-defined de-pinning and sliding of CDW in 2D materials similar to that in metals with quasi-1D crystal structure, which would result in a strong increase in the total current and emergence of the AC component, termed "narrow-band noise" <sup>1</sup>. The latter is likely due to the domain structure of the NC-CDW phase in 2D materials. In the NC-CDW phase, the domains or islands of the C-CDW phase, which consist of atoms arranged in the "David-star" formation, are separated by the metallic IC-CDW phase, *i.e.* discommensurate regions. The C-CDW phase of 1T-TaS<sub>2</sub> has a band gap of about 100 meV to 200 meV <sup>46-47</sup>. How the size of the islands affects the bang-gap is not well understood. The IC-CDW phase surrounding the C-CDW islands has an

electrical conductivity of at least an order of magnitude higher <sup>37</sup>. It is possible that the electric field applied perpendicular to the channel can produce some effect on the C-CDW domain structure in a few 1T-TaS<sub>2</sub> atomic planes, closest to the gate, thus altering the channel current. If the discommensurate regions have narrow width compared to the size of the C-CDW islands, it is possible that the screening is not effective, and the electric field of the gate penetrates deeper into the channel.

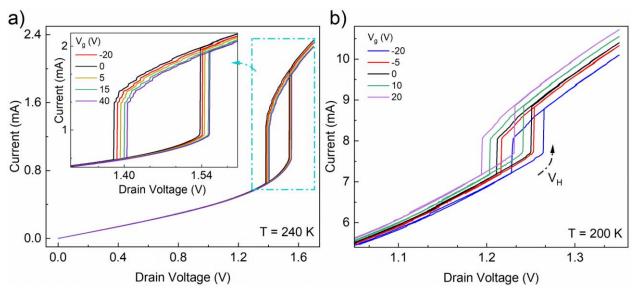

Figure 2a and 2b show the I-V characteristics near the hysteresis window for two different devices at the temperatures of 240 K and 200 K, respectively. These temperatures were selected somewhat above the C-CDW transition and below RT to ensure that the devices are in the NC-CDW phase. The data in Figure 2a are for the thinner channel ( $H \sim 15$  nm) while the data in Figure 2b are for the thicker channel ( $H \sim 35$  nm) device. One can see that we succeeded in shifting the hysteresis region by the applied gate bias. The changes in the hysteresis, characterized by the on-set voltages,  $V_L$  and  $V_H$ , are non-monotonic with the gate bias,  $V_g$ . The changes are only partially reversible. This suggests that the electric field of the gate produces some changes to the C-CDW domains or their ordering. The semiconducting domains can be charged with the electrons from the surrounding IC-CDW phase or shifted or, possibly, merged with other domains when the field is strong enough. These mechanisms can produce permanent changes so that the hysteresis I-Vs do not return to the same positions when a reverse gate bias is applied. In measuring these I-Vs under different gate biases, we wanted to exclude or minimize the local heating effects. For fixed gate biases, we swept the source-drain voltage with an interval of ~ 10 min to avoid heat accumulation in the device structure. One can see in both Figures 2a and 2b that the area of the hysteresis remains unchanged at different gate biases. This is an indication that the shift of the hysteresis with the gate bias, i.e.,  $V_H(V_g)$  and  $V_L(V_g)$ , is not due to the heating but rather due to the direct electric field effect. The hysteresis changes due to local heating are accompanied by the decreasing hysteresis size <sup>21</sup>. The hysteresis is large at low temperatures, and it collapses at  $T \sim 350$  K, which is the NC-CDW – IC-CDW phase transition temperature near equilibrium, *i.e.*, measured at small biases.

Figure 2: Electrical gating of the charge-density-wave hysteresis. (a) Drain-source I-V characteristics of the h-BN capped 1T-TaS<sub>2</sub> device ( $H \sim 15$  nm) under the fixed gate biases  $V_g$ , at T = 240 K. Note that the linear region and the size of hysteresis remain unchanged under the gate bias. The inset shows the enlarged hysteresis, depicting a non-monotonic shift in the values of the threshold voltages,  $V_H$  and  $V_L$ , which define the boundaries of the hysteresis, as the gate bias,  $V_g$ , varies from -20 V to 40 V. (b) Drain-source I-V characteristics of another device ( $H \sim 35$  nm), demonstrating the shift in the threshold voltages  $V_H$ , as the  $V_g$  takes values from -20 V to 20 V at T = 200 K. The drain bias sweeps have been performed with sufficient time intervals to avoid heat accumulation.

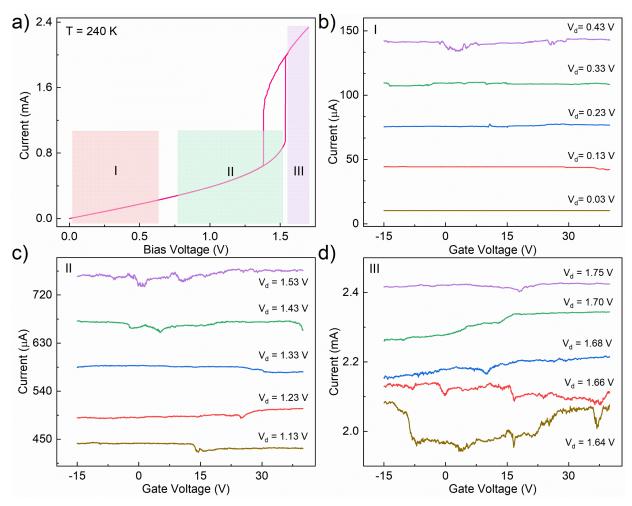

To better understand the mechanism of gating the CDW phases and currents, we measured the current while sweeping the gate voltage,  $I_d(V_g)$ , at T = 240 K. The temperature was intentionally selected in the middle of the NC-CDW phase. For these measurements, we fixed the source-drain voltage,  $V_d$ , and swept the gate voltage with the constant speed of 500 mV/s. We waited for a sufficient time between the voltage sweeps to avoid charge or heat accumulation. To analyze the data, we divided the I-V characteristics into three distinctive regions (see Figure 3a). Region I is the linear segment of I-Vs; region II is where the I-Vs become super-linear and evolve into the NC-CDW – IC-CDW phase transition; and region III is in the vicinity of  $V_H$  and further away into the metallic IC-CDW phase. At low drain bias, the CDW domains are pinned, and electrical conduction is mostly carried through the IC-CDW metallic regions surrounding the CDW islands.

In this transport regime, the application of the gate bias does not produce much change (Figure 3b). At the lowest drain voltages  $V_d = 0.03$  V and  $V_d = 0.13$  V, one cannot observe any change in  $I_d(V_g)$  at all. As  $V_d$  increases, one can start noticing small spikes in the current at certain gate biases, which likely correspond to de-pinning or other changes in the C-CDW domains. The C-CDW domains can be viewed as semiconducting owing to the band gap opening  $^{15, 37, 48}$ .

Figure 3c shows current traces while sweeping the gate voltage in region II where the source-drain I-Vs become super-linear. This is the transport regime, where domains de-pin and can be changed by the electrical gate more efficiently. The variations in the current level become close to  $\sim 15~\mu A$  in the super-linear transport regime, *i.e.*, region II, as compared to  $\sim 5~\mu A$  in the linear regime, *i.e.*, region I. In Figure 3d, one can see a much stronger effect of the gate near the NC-CDW – IC-CDW phase transition region. The fluctuation in the source-drain current reaches the level of  $\sim 2~\mu A$  mA, which is on the order of the change in current when the system transitions between the NC-CDW and the IC-CDW phases. At  $V_d = 1.64~V$  the 1T-TaS<sub>2</sub> channel is entering the IC-CDW phase, but it is still unstable near the transition point,  $V_H$ . The sweeping of the gate bias produces the strongest effect here. At the gate bias in the vicinity of the NC-CDW – IC-CDW phase transition, there is local heating owing to the source-drain current. However, the abrupt variations in the current are due to the application of the gate voltage which changes the domain structure in the channel. As the drain bias increases further,  $V_d \ge 1.75~V$ , the channel becomes fully metallic in the IC-CDW phase, and the gate action stops. In this phase, the high concentration of charge carriers leads to strong screening and small  $\delta UI \sim \delta N/N$  variation.

Figure 3: Changing the charge-density-wave current with the gate. (a) Measured I-V characteristics of the h-BN/1T-TaS<sub>2</sub> heterostructure device, without applied gate bias, at 240 K. The shaded regions I, II and III represent linear, super-linear and near- $V_H$  IC-CDW regions, respectively. The current traces measured with the gate sweep rate of 500 mV/S for fixed  $V_d$  values for three regions are shown in (b), (c) and (d) panels, respectively. The current variations are negligible in region I as seen in (b). The current spikes grow in region II (c), and achieve maximum in region III (d).

While the trend described above is clear and consistent for the tested devices, one may notice a small offset between the hysteresis  $V_L$  and  $V_H$  values (see Figure 3a) and the changes in the transfer characteristics (see Figure 3d). For example, the strongest change in the transfer characteristics happens at  $V_d = 1.64$  V while this value is already slightly larger than  $V_H$ , *i.e.* it is outside of the hysteresis in Figure 3a. This is because the I-V characteristics are taken at zero gate bias and in one sweep. However, the characteristics presented in Figure 3 (b-d) are taken at a fixed source-

drain bias and an additional field produced by the gate. The latter explains why the hysteresis window, defined by  $V_L$  and  $V_H$ , during the transfer characteristic measurements can be somewhat shifted from that presented in Figure 3a at  $V_g = 0$  V. One can also argue that the C-CDW domains are not fully melted at  $V_d$  slightly above  $V_H$ , and current variations can still be observed. These points are addressed in more detail in the discussion below.

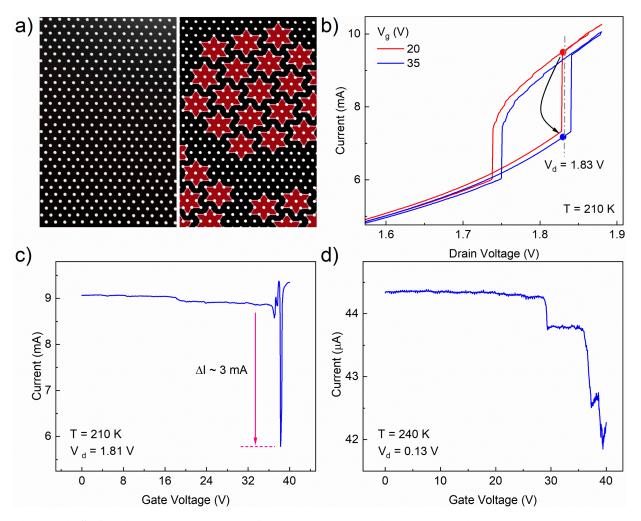

We now consider in more detail the possibility of switching the system between the NC-CDW and IC-CDW phases, illustrated in Figure 4a, by application of a gate bias. Figure 4b shows the drainsource I-V characteristics of another device for two fixed gate voltages,  $V_g$ . The measurements were performed at the temperature of 210 K to ensure that the system is in the NC-CDW phase. As the  $V_g$  switches from 20 V to 35 V, the hysteresis threshold voltage,  $V_H$ , shifts to a higher value. For a selected  $V_d$  near 1.8 V ( $V_d = 1.83$  V in Figure 4b), the channel is in the vicinity of the phase transition point and the suitable  $V_g$  bias can switch the channel between the NC-CDW and IC-CDW phases. To confirm this scenario, we biased the channel with  $V_d$  close to 1.8 V ( $V_d = 1.81$  V in Figure 4c) and allowed the current to pass the channel for six minutes without applying the gate bias. After reaching the steady-state conditions, we swept the gate voltage and monitored the drain current changes. Interestingly, near  $V_g = 38 \text{ V}$ , the current experiences an abrupt and large decrease for about ~ 3 mA, and then goes back to the original level. This change in current is clearly related to the system switching between the IC-CDW and NC-CDW phases. The amount of current drop in Figure 4c is similar to that in Figure 4b. The 1T-TaS<sub>2</sub> channel was driven to the IC-CDW phase by the source-drain current at  $V_d = 1.81$  V and then switched to the NC-CDW phase by the application of the gate bias of  $V_g = 38$  V. The data presented in Figures 4b and 4c proves the possibility of inducing the IC-CDW – NC-CDW phase transition by the gate bias. This is an important capability that was never reported before. In Figure 4d, we show how the source-drain current can be switched by the gate voltage at a small  $V_d$  bias, corresponding to the region I of the I-Vs. The changes in the current are due to the effect produced by the gate electric field on C-CDW domains near the gate dielectric. The system remains in the NC-CDW phase during this measurement.

Figure 4: Switching the charge-density-wave phases with the electrical gate. (a) Illustration of the IC-CDW and NC-CDW phases. (b) Current as a function of the source-drain voltage at two fixed gate biases, measured at T = 210 K. In this device the transition from IC-CDW to NC-CDW phase, depicted with the red and blue dots, occurs at the voltage close to  $V_d = 1.83$  V. (c) Current as the function of the gate bias at the fixed source-drain voltage  $V_d = 1.83$  V. The current change of  $\Delta I \sim 3$  mA, induced by the gate, corresponds to the 1T-TaS<sub>2</sub> channel switching between IC-CDW and NC-CDW phases. (d) Current switching by the gate within the same NC-CDW phase for small, fixed bias of  $V_d = 0.13$  V.

# **Discussion**

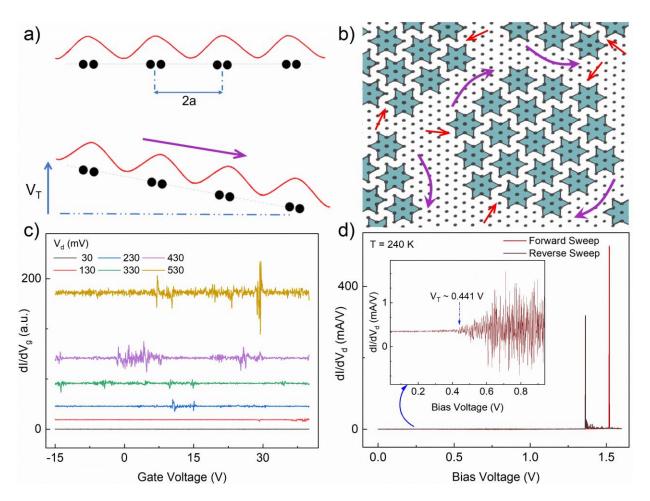

CDW de-pinning in quasi-1D and quasi-2D systems. In the above description of the results, we use the terminology of "de-pinning" of the C-CDW domains to describe the effect of the electric gate on the CDW channel conductance. One should be careful here to understand the difference between the domain de-pinning in quasi-2D materials such as 1T-TaS<sub>2</sub> and CDW de-pinning and sliding in "traditional" bulk CDW materials with quasi-1D crystal structures such as NbS<sub>3</sub> <sup>2,49</sup>. In quasi-1D crystals, the entire CDW, i.e., periodic modulation of the charge density, can de-pin and start sliding, resulting in an abrupt increase in current and the appearance of an AC current component <sup>2, 49</sup> (see Figure 5a). In quasi-2D materials, the NC-CDW phase, which separates the IC-CDW and C-CDW phases, consists of the C-CDW islands separated by the metallic IC-CDW phase. The CDW de-pinning in 1T-TaS2 can be understood more like the C-CDW domains becoming softer, loose, start rotating, and changing in size 34, 45, 50-51 (see Figure 5b). The latter contributes to the current fluctuations, observed in the derivative I-Vs or the low-frequency noise spectra <sup>23, 45</sup>. This process does not result in a large increase in the current – the domains start to fluctuate rather than move together <sup>45</sup>. As we established in this work, it also makes the C-CDW domains more susceptible to the gate bias, i.e., electric field. We now use the derivative current characteristics to illustrate the observed gate effects further.

Figure 5c depicts the differential of the drain current with respect to the gate voltage,  $dI/dV_g$ , as a function of gate bias,  $V_g$ , at a series of fixed  $V_d$  biases. The range of  $V_d$  is selected near the on-set of the I-V super-linearity, where the de-pinning of C-CDW domains is expected. The data were obtained at T = 240 K. It can be seen that at  $V_d$  = 30 mV and  $V_d$  = 130 mV, there are no pronounced changes in  $dI/dV_g$ . However, increasing the fixed drain biases introduces more fluctuations in the derivative current characteristics. The spikes in the  $dI/dV_g$  values shift with increasing  $V_d$  and their amplitude increases. We now turn to the differential current characteristic with respect to the source-drain voltage,  $dI/dV_d$ , as a function of the source-drain voltage  $V_d$ . Figure 5d, shows one large peak in  $dI/dV_d$  around  $V_d$  = 1.5 V, which corresponds to  $V_H$  and the system transition from NC-CDW to IC-CDW phase in the forward bias sweep. The other peak at  $V_d$  = 1.36 V signifies the  $V_L$  in the reverse bias sweep. A close look at the small bias region (see inset of Figure 5d), indicates the start of the derivative characteristics at the domain de-pinning threshold voltage  $V_T$  =

0.441 V. If we look back at Figure 5c, we notice that the gate derivative characteristics at  $V_d = 430$  mV, which is close to  $V_T = 0.441$  V, also reveal substantially increased spikes at certain gate biases. At  $V_d = 530$  mV, which is above the extracted  $V_T$ , one observes not only spikes but also increased background fluctuations in  $dI/dV_g$ . These considerations further confirm that the C-CDW domains in the NC-CDW phase can be affected by both the source-drain bias and the gate voltage.

From the fluctuations, i.e., spikes in the current under the actions of the electric gate we can roughly estimate the physical size of the fluctuator. We assume that the observed changes in the current are associated with some changes in the C-CDW domains that make up the NC-CDW phase  $^{23,52}$ . In this case, the change in current,  $\Delta I$ , is related to the change in the conducting volume,  $\Delta V$ , i.e.,  $\Delta I/I = \Delta V/V$ . The volume is defined as  $V = A \times t \times N$ , where A is the channel area, t is the thickness of one atomic plane, and N is the number of the atomic planes in the channel. Taking the smallest and largest normalized change in the current, ( $\Delta I/I$ ) to be ~ 8.9×10<sup>-5</sup> - 4.14×10<sup>-3</sup>, assuming N to be 25, we obtain the upper and lower bounds of the fluctuator size to be  $(\Delta A)^{1/2} = (AN\Delta I/I)^{1/2}$  $\sim$  67 nm - 455 nm. In the linear region (Figure 3a, region I), the average fluctuator size is  $\sim$  160 nm. Naturally, there is ambiguity in the N value since the conduction may not be uniform through the thickness. However, it is clear that we get a reasonable estimate for the fluctuator in the 100 nm order of magnitude. This is consistent with the size of the C-CDW domains in the NC-CDW phase measured by the scanning tunneling microscopy and other methods <sup>10, 37, 53</sup>. These considerations confirm our hypothesis that the gate electric field affects the C-CDW island, and thus induces the spikes in the current, affects the hysteresis and can switch the system between the IC-CDW and NC-CDW phases. The demonstrated electric gating and switching of the CDW phases by electrical field not only contribute to a better understanding of CDW phenomena in quasi-2D material systems but also indicate a path to future technological developments. The demonstrated switching can be potentially utilized in non-volatile memory applications, particularly if the channel area and thickness are downscaled to the 100-nm-scale or below, allowing for control of individual C-CDW domains that exist up to T ~ 350 K.

Figure 5: De-pinning and differential current-voltage characteristics. Panels (a) and (b) illustrate the difference in the CDW de-pinning in quasi-1D CDW materials and domain "depinning" in 2D CDW materials. In quasi-1D chain of atoms, the bias voltage above the threshold voltage,  $V_T$ , induces the de-pinning and sliding of the whole coherent CDW. In 2D materials the "de-pinning" indicates the onset of the fluctuations, rotation, and movements of the C-CDW domains. (c) Differential current characteristic,  $dI/dV_g$ , with respect to the gate voltage for fixed  $V_d$  values in the linear region I, measured at T = 240 K. (d) Differential current characteristic,  $dI/dV_d$ , with respect to drain voltages,  $V = V_d$ . The large spikes at ~1.52 V (red curve) and at ~1.36 V (brown curve) are associated with the onset of the hysteresis ( $V_H$  and  $V_L$ ) in the forward and reverse sweeps, respectively. The inset depicts the onset of the fluctuations at ~ 0.44 V, within the linear region I. Comparing data in panels (c) and (d), one can see, in both cases, the increase in the fluctuations at drain biases close to the  $V_d = 0.44$  V. This fluctuation behavior at the low drain bias indicates the point of de-pinning for the C-CDW domains.

In conclusion, we reported on electrostatic gating of the current and CDW phases in *h*-BN capped 1T-TaS<sub>2</sub> heterostructure devices. It is demonstrated that the hysteresis in the source-drain I-V characteristics that accompanies the transition between the NC-CDW and IC-CDW phases can be shifted by applying a gate bias. The gate bias affects the domains of the C-CDW phase as observed from the abrupt changes in the drain current. The transition between the NC-CDW and IC-CDW phases can be induced by both the source-drain current and the electrostatic gate. Since the CDW phases are persistent in 1T-TaS<sub>2</sub> at room temperature, one can envision memory applications of such devices when scaled down to the dimensions of individual commensurate domains.

# **METHODS**

**CDW device fabrication and testing:** High-quality crystals of 1T-TaS<sub>2</sub> have been mechanically exfoliated on top of polydimethylsiloxane (PDMS) layers in a dry environment (with relative humidity of < 19%). Thin films of 1T-TaS<sub>2</sub> were then transferred onto pre-selected h-BN layers on Si/SiO<sub>2</sub> substrate through the all-dry transfer method. This step is immediately followed by capping the 1T-TaS<sub>2</sub> with another few-layer aligned h-BN film. The devices being capped/encapsulated with h-BN will preserve the CDW state longer and give better protection from oxidation and environmental degradation. The patterning of electrodes was performed through electron-beam lithography. The h-BN layers covering the electrode contacts were removed with high precision using the atomic layer etching technique. For contact metal deposition, we used electron-beam evaporation and deposited 10/100 nm of Ti/Au metals. The fabricated devices had dimensions of 1 to 3  $\mu$ m channel length and 1 to 3.5  $\mu$ m channel width. The gate measurements at various temperatures were conducted in the Lakeshore cryogenic probe station TTPX and further analyzed with a semiconductor analyzer Agilent B1500.

# Acknowledgments

The work at UC Riverside was supported, in part, by the U.S. Department of Energy Office of Basic Energy Sciences under contract No. DE-SC0021020 "Physical Mechanisms and Electric-Bias Control of Phase Transitions in Quasi-2D Charge-Density-Wave Quantum Materials". A.A.B. was supported by the Vannevar Bush Faculty Fellowship from the Office of Secretary of Defense (OSD), under the Office of Naval Research (ONR) contract N00014-21-1-2947. A.R. and S.R. work was partially supported by the "International Research Agendas" program of the Foundation for Polish Science co-financed by the European Union under the European Regional Development Fund No. MAB/2018/9.

## **Author Contributions**

A.A.B. and S.R. conceived the idea. A.A.B coordinated the project and led the experimental data analysis and manuscript preparation. A.R., S.R., and F.K. contributed to the data analysis. N.S. synthesized and characterized bulk crystals of 1T-TaS<sub>2</sub>, supervised by T.T.S. M.T. fabricated devices, conducted measurements, and contributed to the data analysis. J.B. assisted with device fabrication and contributed to data analysis. A.A.B. and M.T. wrote the manuscript. All authors contributed to the manuscript editing.

# **Supplemental Information**

The supplemental information is available on the journal website for free of charge.

# The Data Availability Statement

The data that support the findings of this study are available from the corresponding author upon reasonable request.

# **REFERENCES**

- (1) Grüner, G. The Dynamics of Spin-Density Waves. Rev. Mod. Phys. 1994, 66, 1.

- (2) Zaitsev-Zotov, S. V. Finite-Size Effects in Quasi-One-Dimensional Conductors with a Charge-Density Wave. *Phys.-Usp.* **2004**, 47, 533.

- (3) Monceau, P. Electronic Crystals: An Experimental Overview. Adv. Phys. 2012, 61, 325-581.

- (4) Zybtsev, S. G.; Pokrovskii, V. Ya.; Zaitsev-Zotov, S. V. 'Quantized' States of the Charge-Density Wave in Microcrystals of K<sub>0.3</sub>MoO<sub>3</sub>. *Nature Commun.* **2010**, 1, 1087.

- (5) Balandin, A. A.; Zaitsev-Zotov, S. V.; Grüner, G. Charge-Density-Wave Quantum Materials and Devices-New Developments and Future Prospects. *Appl. Phys. Lett.* **2021,** 119, 170401.

- (6) Baraghani, S.; Barani, Z.; Ghafouri, Y.; Mohammadzadeh, A.; Salguero, T. T.; Kargar, F.; Balandin, A. A. Charge-Density-Wave Thin-Film Devices Printed with Chemically Exfoliated 1T-TaS<sub>2</sub> Ink. *ACS Nano* **2022**, 16, 6325-6333.

- (7) Boix-Constant, C.; Mañas-Valero, S.; Córdoba, R.; Baldoví, J. J.; Rubio, Á.; Coronado, E. Out-of-Plane Transport of 1T-TaS<sub>2</sub>/Graphene-Based van der Waals Heterostructures. *ACS Nano* **2021,** 15, 11898-11907.

- (8) Latt, K. Z.; Schlueter, J. A.; Darancet, P.; Hla, S. Two-Dimensional Molecular Charge Density Waves in Single-Layer-Thick Islands of a Dirac Fermion System. *ACS Nano* **2020**, 14, 8887-8893.

- (9) Hall, J.; Ehlen, N.; Berges, J.; Loon, E. V.; Efferen, C. V.; Murray, C.; Rösner, M.; Li, J.; Senkovskiy, B. V.; Hell, M.; Rolf, M.; Heider, T.; Asensio, M. C.; Avila, J.; Plucinski, L.;

- Wehling, T.; Grüneis, A.; Michely, T. Environmental Control of Charge Density Wave Order in Monolayer 2H-TaS<sub>2</sub>. *ACS Nano* **2019**, 13, 10210-10220.

- (10) Ma, L.; Ye, C.; Yu, Y.; Lu, X. F.; Niu, X.; Kim, S.; Feng, D.; Tománek, D.; Son, Y.; Chen, X. H.; Zhang, Y. A Metallic Mosaic Phase and the Origin of Mott-Insulating State in 1T-TaS<sub>2</sub>. *Nature Commun.* **2016,** 7, 10956.

- (11) Fu, W.; Qiao, J.; Zhao, X.; Chen, Y.; Fu, D.; Yu, W.; Leng, K.; Song, P.; Chen, Z.; Yu, T.; Pennycook, S. J.; Quek, S. Y.; Loh, K. P. Room Temperature Commensurate Charge Density Wave on Epitaxially Grown Bilayer 2H-Tantalum Sulfide on Hexagonal Boron Nitride. *ACS Nano* **2020**, 14, 3917-3926.

- (12) Yang, H.; Zhang, T.; Huang, Z.; Chen, Y.; Song, X.; Hao, X.; Yang, H.; Wu, X.; Zhang, Y.; Liu, L.; Gao, H.; Wang, Y. Visualization of Charge-Density-Wave Reconstruction and Electronic Superstructure at the Edge of Correlated Insulator 1T-NbSe<sub>2</sub>. *ACS Nano* **2022**, 16, 1332-1338.

- (13) Porer, M.; Leierseder, U.; Ménard, J.-M.; Dachraoui, H.; Mouchliadis, L.; Perakis, I. E.; Heinzmann, U.; Demsar, J.; Rossnagel, K.; Huber, R. Non-Thermal Separation of Electronic and Structural Orders in a Persisting Charge Density Wave. *Nature Mater.* **2014**, 13, 857-861.

- (14) Stojchevska, L.; Vaskivskyi, I.; Mertelj, T.; Kusar, P.; Svetin, D.; Brazovskii, S.; Mihailovic, D. Ultrafast Switching to a Stable Hidden Quantum State in an Electronic Crystal. *Science* **2014**, 344, 177-180.

- (15) Yu, Y.; Yang, F.; Lu, X. F.; Yan, Y. J.; Cho, Y.; Ma, L.; Niu, X.; Kim, S.; Son, Y.; Feng, D.; Li, S.; Cheong, S.; Chen, X. H.; Zhang, Y. Gate-Tunable Phase Transitions in Thin Flakes of 1T-TaS<sub>2</sub>. *Nature Nanotech.* **2015**, 10, 270-276.

- (16) Samnakay, R.; Wickramaratne, D.; Pope, T. R.; Lake, R. K.; Salguero, T. T.; Balandin, A. A. Zone-Folded Phonons and the Commensurate-Incommensurate Charge-Density-Wave Transition in 1T-TaSe<sub>2</sub> Thin Films. *Nano Lett.* **2015**, 15, 2965-2973.

- (17) Xi, X.; Zhao, L.; Wang, Z.; Berger, H.; Forró, L.; Shan, J.; Mak, K. F. Strongly Enhanced Charge-Density-Wave Order in Monolayer NbSe<sub>2</sub>. *Nature Nanotech.* **2015**, 10, 765-769.

- (18) Geremew, A. K.; Rumyantsev, S.; Kargar, F.; Debnath, B.; Nosek, A.; Bloodgood, M. A.; Bockrath, M.; Salguero, T. T.; Lake, R. K.; Balandin, A. A. Bias-Voltage Driven Switching of the Charge-Density-Wave and Normal Metallic Phases in 1T-TaS<sub>2</sub> Thin-Film Devices. *ACS Nano* **2019**, 13, 7231-7240.

- (19) Vogelgesang, S.; Storeck, G.; Horstmann, J. G.; Diekmann, T.; Sivis, M.; Schramm, S.; Rossnagel, K.; Schäfer, S.; Ropers, C. Phase Ordering of Charge Density Waves Traced by Ultrafast Low-Energy Electron Diffraction. *Nature Phys.* **2018**, 14, 184-190.

- (20) Jakhar, A.; Kumar, P.; Husain, S.; Dhyani, V.; Das, S. Integration of Nanometer-Thick 1T-TaS<sub>2</sub> Films with Silicon for an Optically Driven Wide-Band Terahertz Modulator. *ACS Appl. Nano Mater.* **2020,** 3, 10767-10777.

- (21) Liu, G.; Debnath, B.; Pope, T. R.; Salguero, T. T.; Lake, R. K.; Balandin, A. A. A Charge-Density-Wave Oscillator Based on an Integrated Tantalum Disulfide-Boron Nitride-Graphene Device Operating at Room Temperature. *Nature Nanotech.* **2016**, 11, 845-850.

- (22) Sinchenko, A. A.; Lejay, P.; Monceau, P. Sliding Charge-Density Wave in Two-Dimensional Rare-Earth Tellurides. *Phys. Rev. B* **2012**, 85, 241104R.

- (23) Liu, G.; Rumyantsev, S.; Bloodgood, M. A.; Salguero, T. T.; Balandin, A. A. Low-Frequency Current Fluctuations and Sliding of the Charge Density Waves in Two-Dimensional Materials. *Nano Lett.* **2018**, 18, 3630-3636.

- (24) Zhu, X.; Guo, J.; Zhang, J.; Plummer, E. W. Misconceptions Associated with the Origin of Charge Density Waves. *Adv. Phys.: X* **2017,** 2, 622-640.

- (25) Geremew, A. K.; Rumyantsev, S.; Debnath, B.; Lake, R. K.; Balandin, A. A. High-Frequency Current Oscillations in Charge-Density-Wave 1T-TaS<sub>2</sub> Devices: Revisiting the "Narrow Band Noise" Concept. *Appl. Phys. Lett.* **2020**, 116, 163101.

- (26) Liu, G.; Zhang, E. X.; Liang, C. D.; Bloodgood, M. A.; Salguero, T. T.; Fleetwood, D. M.; Balandin, A. A. Total-Ionizing-Dose Effects on Threshold Switching in 1T-TaS<sub>2</sub> Charge Density Wave Devices. *IEEE Electron Device Lett.* **2017**, 38, 1724-1727.

- (27) Khitun, A.; Liu, G.; Balandin, A. A. Two-Dimensional Oscillatory Neural Network Based on Room-Temperature Charge-Density-Wave Devices. *IEEE Trans. Nanotechnol.* **2017**, 16, 860-867.

- (28) Khitun, A. G.; Geremew, A. K.; Balandin, A. A. Transistor-Less Logic Circuits Implemented with 2-D Charge Density Wave Devices. *IEEE Electron Device Lett.* **2018,** 39, 1449-1452.

- (29) Zhu, C.; Chen, Y.; Liu, F.; Zheng, S.; Li, X.; Chaturvedi, A.; Zhou, J.; Fu, Q.; He, Y.; Zeng, Q.; Fan, H. J.; Zhang, H.; Liu, W.; Yu, T.; Liu, Z. Light-Tunable 1T-TaS<sub>2</sub> Charge-Density-Wave Oscillators. *ACS Nano* **2018**, 12, 11203-11210.

- (30) Dang, C.; Guan, M.; Hussain, S.; Wen, W.; Zhu, Y.; Jiao, L.; Meng, S.; Xie, L. Phase Transition Photodetection in Charge Density Wave Tantalum Disulfide. *Nano Lett.* **2020**, 20, 6725-6731.

- (31) Gerasimenko, Y. A.; Vaskivskyi, I.; Litskevich, M.; Ravnik, J.; Vodeb, J.; Diego, M.; Kabanov, V.; Mihailovic, D. Quantum Jamming Transition to a Correlated Electron Glass in 1T-TaS<sub>2</sub>. *Nature Mater.* **2019**, 18, 1078-1083.

- (32) Mohammadzadeh, A.; Baraghani, S.; Yin, S.; Kargar, F.; Bird, J. P.; Balandin, A. A. Evidence for a Thermally Driven Charge-Density-Wave Transition in 1T-TaS<sub>2</sub> Thin Film Devices: Prospects for GHz Switching Speed. *Appl. Phys. Lett.* **2021**, 118, 093102.

- (33) Yoshida, M.; Gokuden, T.; Suzuki, R.; Nakano, M.; Iwasa, Y. Current Switching of Electronic Structures in Two-Dimensional 1T-TaS<sub>2</sub> Crystals. *Phys. Rev. B* **2017**, 95, 121405R.

- (34) Mihailovic, D.; Svetin, D.; Vaskivskyi, I.; Venturini, R.; Lipovšek, B.; Mraz, A. Ultrafast Non-Thermal and Thermal Switching in Charge Configuration Memory Devices Based on 1T-TaS<sub>2</sub>. *Appl. Phys. Lett.* **2021**, 119, 013106.

- (35) Inada, R.; Ōnuki, Y.; Tanuma, S. Hall Effect of 1T-TaS<sub>2</sub> and 1T-TaSe<sub>2</sub>. *Physica B+C* **1980**, 99, 188-192.

- (36) Yoshida, M.; Zhang, Y.; Ye, J.; Suzuki, R.; Imai, Y.; Kimura, S.; Fujiwara, A.; Iwasa, Y. Controlling Charge-Density-Wave States in Nano-Thick Crystals of 1T-TaS<sub>2</sub>. *Sci. Rep.* **2014**, 4, 7302.

- (37) Tsen, A. W.; Hovden, R.; Wang, D.; Kim, Y. D.; Okamoto, J.; Spoth, K. A.; Liu, Y.; Lu, W.; Sun, Y.; Hone, J. C.; Kourkoutis, L. F.; Kim, P.; Pasupathy, A. N. Structure and Control of Charge Density Waves in Two-Dimensional 1T-TaS<sub>2</sub>. *PNAS* **2015**, 112, 15054-15059.

- (38) Revelli, J. F.; Phillips, W. A. Studies of the System TaS<sub>2-x</sub>Se<sub>x</sub>. *J. Solid State Chem.* **1974,** 9, 176-186.

- (39) Binnewies, M.; Glaum, R.; Schmidt, M.; Schmidt, P. Chemical Vapor Transport Reactions-A Historical Review. *Z. Anorg. Allg. Chem.* **2013**, 639, 219-229.

- (40) Yan, Z.; Jiang, C.; Pope, T. R.; Tsang, C. F.; Stickney, J. L.; Goli, P.; Renteria, J.; Salguero, T. T.; Balandin, A. A. Phonon and Thermal Properties of Exfoliated TaSe<sub>2</sub> Thin Films. *J. Appl. Phys.* **2013**, 114, 204301.

- (41) Renteria, J.; Samnakay, R.; Jiang, C.; Pope, T. R.; Goli, P.; Yan, Z.; Wickramaratne, D.; Salguero, T. T.; Khitun, A. G.; Lake, R. K.; Balandin, A. A. All-Metallic Electrically Gated 2H-TaSe<sub>2</sub> Thin-Film Switches and Logic Circuits. *J. Appl. Phys.* **2014**, 115, 034305.

- (42) Rhodes, D.; Chae, S. H.; Ribeiro-Palau, R.; Hone, J. Disorder in van Der Waals Heterostructures of 2D Materials. *Nature Mater.* **2019**, 18, 541-549.

- (43) Núñez-Regueiro, M. D.; Lopez-Castillo, J. M.; Ayache, C. Thermal Conductivity of 1T-TaS<sub>2</sub> and 2H-TaSe<sub>2</sub>. *Phys. Rev. Lett.* **1985**, 55, 1931-1934.

- (44) Jo, I.; Pettes, M. T.; Kim, J.; Watanabe, K.; Taniguchi, T.; Yao, Z.; Shi, L. Thermal Conductivity and Phonon Transport in Suspended Few-Layer Hexagonal Boron Nitride. *Nano Lett.* **2013,** 13, 550-554.

- (45) Mohammadzadeh, A.; Rehman, A.; Kargar, F.; Rumyantsev, S.; Smulko, J. M.; Knap, W.; Lake, R. K.; Balandin, A. A. Room Temperature De-pinning of the Charge-Density Waves in Quasi-Two-Dimensional 1T-TaS<sub>2</sub> Devices. *Appl. Phys. Lett.* **2021**, 118, 223101.

- (46) Manzke, R.; Anderson, O.; Skibowski, M. The Electronic Structure of 1T-TaS<sub>2</sub> at Room Temperature and 120 K. *J. Phys. C: Solid State Phys.* **1988**, 21, 2399-2411.

- (47) Claessen, R.; Burandt, B.; Carstensen, H.; Skibowski, M. Conduction-Band Structure and Charge-Density Waves in 1T-TaS<sub>2</sub>. *Phys. Rev. B* **1990**, 41, 8270-8277.

- (48) Park, J. W.; Lee, J.; Yeom, H. W. Zoology of Domain Walls in Quasi-2D Correlated Charge Density Wave of 1T-TaS<sub>2</sub>. *npj Quantum Mater*. **2021**, 6, 32.

- (49) Grüner, G. The Dynamics of Charge-Density Waves. Rev. Mod. Phys. 1988, 60, 1129-1181.

- (50) Gerasimenko, Y. A.; Karpov, P.; Vaskivskyi, I.; Brazovskii, S.; Mihailovic, D. Intertwined Chiral Charge Orders and Topological Stabilization of the Light-Induced State of a Prototypical Transition Metal Dichalcogenide. *npj Quantum Mater.* **2019**, 4, 32.

- (51) Vaskivskyi, I.; Mihailovic, I. A.; Brazovskii, S.; Gospodaric, J.; Mertelj, T.; Svetin, D.; Sutar, P.; Mihailovic, D. Fast Electronic Resistance Switching Involving Hidden Charge Density Wave States. *Nature Commun.* **2016**, 7, 11442.

- (52) Bloom, I.; Marley, A. C.; Weissman, M. B. Nonequilibrium Dynamics of Discrete Fluctuators in Charge-Density Waves in NbSe<sub>3</sub>. *Phys. Rev. Lett.* **1993**, 71, 4385-4388.

- (53) Wu, X. L.; Lieber, C. M. Direct Observation of Growth and Melting of the Hexagonal-Domain Charge-Density-Wave Phase in 1T-TaS<sub>2</sub> by Scanning Tunneling Microscopy. *Phys. Rev. Lett.* **1990**, 64, 1150-1153.