### Cryogenic in-memory computing using tunable chiral edge states

Yuting Liu<sup>1,2\*</sup>, Albert Lee<sup>3\*</sup>, Kun Qian<sup>1,4</sup>, Peng Zhang<sup>3</sup>, Haoran He<sup>3</sup>, Zheyu Ren<sup>1,4</sup>, Shun Kong Cheung<sup>1</sup>, Yaoyin Li<sup>2</sup>, Xu Zhang<sup>1</sup>, Zichao Ma<sup>1</sup>, Zhihua Xiao<sup>1,10</sup>, Guoqiang Yu<sup>7</sup>, Xin Wang<sup>8</sup>, Junwei Liu<sup>4,6</sup>, Zhongrui Wang<sup>5</sup>, Kang L. Wang<sup>3</sup>, & Qiming Shao<sup>1,4,6,9,10†</sup>

<sup>1</sup>Department of Electronic and Computer Engineering, The Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong SAR 999077, China

<sup>2</sup>School of Material Science and Engineering, Harbin Institute of Technology, Shenzhen 518055, People's Republic of China.

<sup>3</sup>Device Research Laboratory, Department of Electrical and Computer Engineering, University of California, Los Angeles, California 90095, USA.

<sup>4</sup>IAS Center for Quantum Technologies, The Hong Kong University of Science and Technology, Hong Kong, China

<sup>5</sup>Department of Electrical and Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong SAR 999077, China

<sup>6</sup>Department of Physics, The Hong Kong University of Science and Technology, Clear Water Bay, Kowloon, Hong Kong SAR 999077, China

<sup>7</sup>Beijing National Laboratory for Condensed Matter Physics, Institute of Physics, University of Chinese Academy of Sciences, Chinese Academy of Sciences, Beijing, 100190 China

<sup>8</sup>Department of Physics, The City University of Hong Kong, Hong Kong SAR 999077, China

<sup>9</sup>Guangdong-Hong Kong-Macao Joint Laboratory for Intelligent Micro-Nano Optoelectronic Technology, The Hong Kong University of Science and Technology, Hong Kong, China

<sup>10</sup>ACCESS – AI Chip Center for Emerging Smart Systems, InnoHK Centers, Hong Kong Science Park, Hong Kong, China

\*Equal contribution

†Email: eeqshao@ust.hk

Cryogenic electronics have become essential in reducing the number of input/output ports to the quantum chips and generating multiplexed reading and control pulses for scalable quantum computation <sup>1-5</sup>. A demanding request for cryogenic electronics is to support efficient machine learning algorithms, which have been proven effective for essential quantum computation tasks such as quantum error correction and quantum control <sup>6,7</sup>. However, current digital cryogenic electronics suffer from the von Neumann bottleneck, where the physical separation of computation and memory units causes a huge amount of energy and delay when processing data-intensive programs. Energyefficient hardware implementation of machine learning algorithms for quantum computation requires nonvolatile and electrically-programmable devices, memristors, working at cryogenic temperatures that enable in-memory computing <sup>8,9</sup>. Magnetic topological insulators are promising candidates due to their tunable magnetic order by electrical currents with high energy efficiency <sup>10-</sup> <sup>15</sup>. Here, we utilize magnetic topological insulators as memristors (termed magnetic topological memristors) and introduce a chiral edge state-based cryogenic in-memory computing scheme. On the one hand, the chiral edge state can be tuned from left-handed to right-handed chirality through spinmomentum locked topological surface current injection. On the other hand, the chiral edge state exhibits giant and bipolar anomalous Hall resistance, which facilitates the electrical readout. The memristive switching and reading of the chiral edge state exhibit high energy efficiency, high stability, and low stochasticity. We achieve high accuracy in a proof-of-concept classification task using four magnetic topological memristors. Furthermore, our algorithm-level and circuit-level simulations of large-scale neural networks based on magnetic topological memristors demonstrate a software-level accuracy and lower energy consumption for image recognition and quantum state preparation compared with existing memristor technologies. Our results may inspire further topological quantum physics-based novel computing schemes.

Quantum bit (qubit) can be abstracted into a two-level system, for which the physical implementation can be based on superconducting circuits, semiconductor dots, ion traps, optical photons, and others <sup>16</sup>. An alternative promising solution is topological qubits that can be constructed by hybridizing chiral edge states and superconducting orders <sup>17</sup>. Oubits can be controlled and read out by tailored short pulses so that processing quantum information is possible. At this moment, tens of superconducting qubits can be integrated into a single chip to demonstrate quantum advantages, which already requires 205 microwave cable <sup>18</sup>. As the number of controllable qubits increases, the number of input-output ports will increase dramatically, which demands a clear plan for scalability. Inspired by the complementary metal-oxidesemiconductors (CMOS) technology that integrates billions of transistors, multiple inputs and outputs can be combined using multiplexers and demultiplexers to reduce the number of input/output ports. This kind of peripheral circuit needs to sit beside the quantum chip and thus works at deep cryogenic temperatures. While cryogenic CMOS technology works well for traditional tasks at this temperature <sup>2–5</sup>, it does not work well for handling machine learning algorithms, which have been shown to provide advantages to support quantum algorithms, such as performing quantum error correction <sup>6</sup> and quantum control <sup>7</sup>. In particular, the performance and efficiency of cryogenic CMOS are limited by their physically separated memory and processing units, the so-called von Neumann bottleneck, which incurs large time and energy overheads when running machine learning tasks. To address this challenge, bio-inspired neuromorphic hardware with co-location of memory and processing units has been proposed. These architectures are often based upon nonvolatile and electrically-programmable devices, which are also referred to as memristors <sup>8,9</sup>. They act as artificial synapses in neural networks and their crossbar arrays physically embody weight matrices. Such a design allows them to compute entire matrix-vector multiplications in a single cycle, which is the essential computation step for artificial neural networks used in deep learning and overcomes the von Neumann bottleneck in traditional computing architectures <sup>19</sup>.

Several implementations of memristive crossbars have been developed based on different devices at room temperature, including (redox- or conductive bridge-based) resistive devices <sup>20,21</sup>, phase change devices <sup>22</sup>, ferroelectric devices <sup>23,24</sup>, and magnetic devices <sup>25</sup>. The cryogenic memristor array remains to be experimentally explored. Magnetic devices can work at cryogenic temperatures as a binary and nonvolatile memory <sup>26,27</sup>. However, the energy efficiency of the cryogenic magnetic device is comparable with its room temperature counterpart since the spin current generation is based on conventional spin-transfer torque or spin Hall effect, which is rather temperature-insensitive. Due to the limited cooling power at deep cryogenic temperatures <sup>2</sup>, a more energy-efficient analog magnetic memristor is needed. In this work, we introduce chiral edge state-based magnetic topological memristors (MTMs) by using magnetic topological insulator Hall bar devices. We demonstrate the analog memristive switching behavior in MTMs and a proof-of-concept classification system using four MTMs. The algorithm-level and circuit-level simulations of hybrid MTM-CMOS-based neural networks indicate a software-level accuracy and lower energy consumption compared with existing memristor technologies.

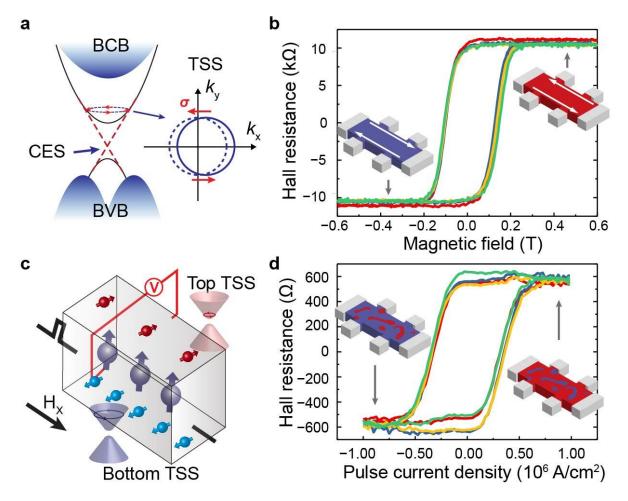

Our memristor is based on a magnetic topological insulator (MTI). We prepare MTIs, Cr-doped (Cr<sub>0.15</sub>Bi<sub>0.26</sub>Sb<sub>0.59</sub>)<sub>2</sub>Te<sub>3</sub> (Cr-BST), using molecular beam epitaxy and fabricate them into Hall bar devices (see Methods 'Device fabrication and characterization'). Due to topologically nontrivial band structures, these MTIs host chiral edge states (Fig. 1a). While the chiral edge states are dominant in the electronic transport. MTIs exhibit giant anomalous Hall resistance. In our experiment at 2 K, the saturated anomalous Hall resistivity is 11 k $\Omega$  (0.42  $h/e^2$ ) for an excitation current of 10<sup>4</sup> A/cm<sup>2</sup> (Fig. 1b), where e is the electron charge and h is Planck's constant. The anomalous Hall resistance becomes 14 k $\Omega$  (0.55  $h/e^2$ ) for an excitation current of 10 A/cm<sup>2</sup> (see Methods 'Current and temperature dependence'), significantly larger than those of the topologically trivial magnetic materials, indicating a large contribution from the chiral edge sate <sup>14,15</sup>. Since the MTI is not in the quantum anomalous Hall insulator state, there is still finite contribution from the topological surface state (Fig. 1a), which has a unique feature of spin-momentum locking. The spin-polarized topological surface current has been demonstrated to generate giant spin-orbit torque and manipulate the magnetic order of MTIs efficiently 10-12. More importantly, the spin-orbit torque from the spin-momentum locking is orders of magnitude larger at cryogenic temperature than that at room temperature <sup>13</sup>, which is different from spin-transfer torque or spin Hall effect-induced spin-orbit torque. We apply a series of pulsed charge currents into the MTI Hall bar device and then measure the corresponding Hall resistance (Fig. 1c). Fig. 1d shows the current-induced magnetization switching in four MTI Hall bar devices through the spin-orbit torque effect (see Methods 'Mechanism of SOT switching in MTIs'). The anomalous Hall resistance is tunable and ranges between -600  $\Omega$  and 600  $\Omega$ . The large reduction of the current switching range from the field switching range is attributed to the Joule heating effect, which breaks down the MTI into a multi-domain state <sup>28</sup>. Nevertheless, the large anomalous Hall resistance of about 600  $\Omega$  is still very large, indicating that chiral edge states play an important role in transport.

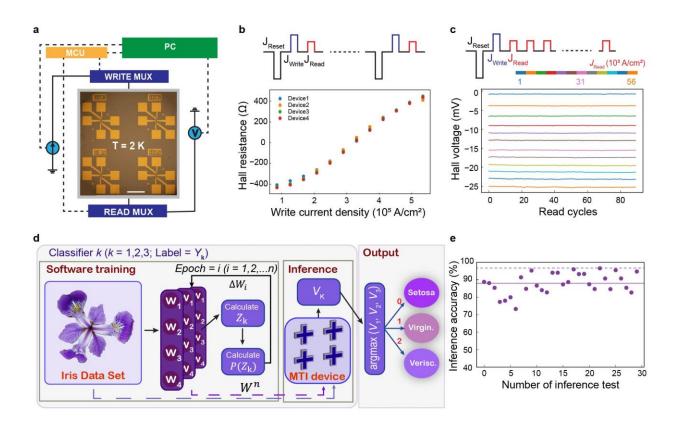

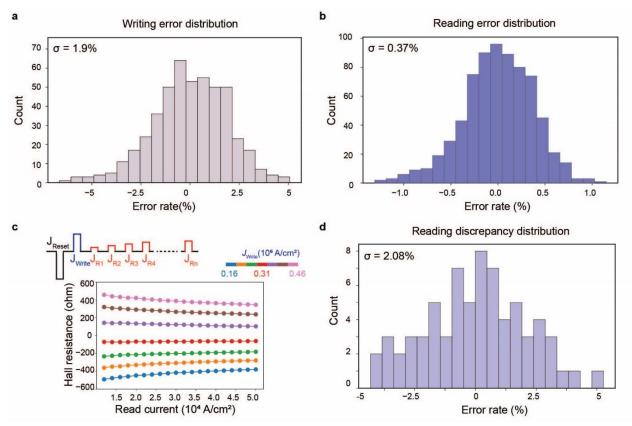

To utilize MTI as a memristor, we need to characterize its write and read capability from an application point of view. For better memristor-based technology, the number of available states for an MTM should be as large as possible and these states should be stable. We build a platform to experimentally test multiple devices at cryogenic temperature (**Fig. 2a**), which allows us to apply arbitrary pulse sequences. We have 50 trials of write tests for 12 different levels and they exhibit very low write stochasticity of 1.9% (**Fig. 2b**) (see Methods 'Memristive switching behaviors in MTIs'), which is significantly lower than other nonvolatile memory technologies and beneficial for neural network implementation <sup>9</sup>. The current density

used to reset the magnetization state can be as low as  $7 \times 10^{5}$  A/cm<sup>2</sup>, which indicates the high efficiency of spin-orbit torque and is consistent with the previous reports <sup>10–12</sup>. Also, the switching is almost analog and thus the number of available states is much larger than 12 (**Fig. 1d**). We have 90 trails for reading tests for the same 12 levels by using the fixed read pulse magnitude and they exhibit even lower read stochasticity of 0.37% (**Fig. 2c**) (see Methods 'Memristive switching behaviors in MTIs'). The high energy efficiency and low stochasticity of write and read suggest that the MTI is a good choice for memristors.

A crossbar of memristors leverages Ohm's law and Kirchoff's current law to achieve analog multiplyaccumulate operation, which is part of vector-matrix multiplication and the most frequent operation for neural network-based deep learning <sup>29</sup>. We demonstrate a proof-of-concept experiment of chiral edge statebased cryogenic in-memory computing by classifying the type of Iris flowers using four MTMs. In our experiment, the input is encoded in the input current and the output is encoded in the anomalous Hall voltage, where the anomalous Hall resistance is the weight of the matrix in the vector-matrix multiplication (**Fig. 2d**) (see Methods 'Implementation of Iris pattern classification'). We utilize three single-layer perceptrons and a softmax to classify three types of Iris flowers. We obtain the 12 software-trained weight parameters and then apply the corresponding currents to tune the anomalous Hall resistance. For each perceptron, we experimentally determine the classification accuracy 30 times. **Fig. 2e** shows that the accuracy fluctuates around 88% and can reach 96%, matching the software level accuracy. The variation in accuracy across trials is due to the read current-induced thermal noise disturbance (see Methods 'Implementation of Iris pattern classification').

To show the feasibility of using MTMs for practical deep learning, we use the extracted device properties to perform larger-scale neural network simulation tasks, including Modified National Institute of Standards and Technology (MNIST) handwritten digit recognition and reinforcement learning for quantum state preparation. One unique feature of a chiral edge state-based memristor is its straightforward representation of both positive and negative weights, which is not available for traditional resistance-based memristors. The necessary condition of this anomalous Hall effect-based in-memory computing is that the anomalous Hall resistance needs to be sufficiently large to be read out effectively (see Methods 'Design challenges for Hall effect-based neural network').

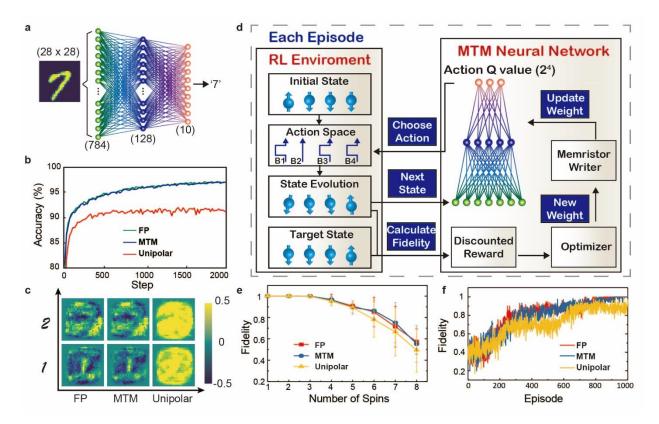

We first use the extracted MTM model to form a  $784 \times 128 \times 10$  neural network for recognizing MNIST digits (**Fig. 3a**). We compare the performance of three neural networks built upon different weight constraints: bipolar weights (e.g., the MTM), unipolar weights (e.g., traditional resistance-based memristors), and floating-point weights (e.g., software; see Methods 'MNIST dataset simulation'). We observe a similar performance between floating-point weights and MTM neural network, whereas the unipolar weight neural network exhibits significantly lower accuracy (**Fig. 3b**). We visualize the final normalized weight matrix of three neural networks (**Fig. 3c**). MTM and floating-point neural networks exhibit similar weight matrix patterns. In contrast, the limitation of positive weights in the unipolar weight neural network is insufficient to achieve the optimized weight matrix.

To show the relevance of cryogenic in-memory computing for quantum computing, we then investigate the performance of MTM-based reinforcement learning for quantum state preparation (see Methods 'Qubit preparation with policy gradient' for details). The task aims to control the state of N serially coupled spins via a magnetic flux pulse sequence and drive it from an initial state to a target state (**Fig. 3d**). A policy gradient learning environment is prepared, and we again compare the neural networks with the aforementioned weight constraints. The MTM network is on par with the floating-point network (**Fig. 3e**). In contrast, the traditional memristor network performs worse due to limitations in its weight representation. In terms of the training time cost, the MTM network also outperforms the unipolar memristor network and achieves similar performance to the floating-point network (**Fig. 3f**).

High-quality MTIs have been grown at wafer-scale on both crystalline and amorphous substrates using molecular beam epitaxy <sup>30</sup> and magnetron sputtering <sup>31</sup>, making MTI a scalable and CMOS-compatible material system for cryogenic in-memory computing. We consider the task of designing the scalable circuit and system for MTM-based in-memory computing. This task is highly nontrivial since there has yet to be a hardware realization of anomalous Hall resistance-neural networks. Prior efforts have overlooked that the chiral edge state-based memristor is essentially a four-terminal device, where the sneak path doesn't allow for the simple parallel or series summation of two-terminal memristors <sup>9,29</sup> (see Methods "Design challenges for Hall effect-based neural network'). We design a hybrid MTM-CMOS system to realize the in-memory computing functionalities and successfully demonstrate the functionalities using a foundry-provided CMOS process design kit (See Methods 'MTM neural network design' and 'Circuit simulation').

We also consider the application of our proposal using other promising material systems, such as intrinsic antiferromagnetic insulators and Moiré heterostructures such as  $MnBi_2Te_4$ <sup>32</sup> and twisted bilayer graphene <sup>33,34</sup>. These material systems can exhibit a quantized anomalous Hall effect of 25.8 k $\Omega$  ( $h/e^2$ ) like our MTI <sup>30,35</sup> but at a higher temperature, which is beneficial for easy readout. In particular, current-induced magnetization switching with an ultralow current density <sup>33,34</sup> and electric field control of magnetic order <sup>36</sup> have been demonstrated in twisted bilayer graphene systems. To apply these systems for cryogenic inmemory computing, a systematic study of their memristive behaviors and scalable methods of fabricating a device array need to be studied like this work.

In summary, our work serves as a proof-of-concept demonstration of a cryogenic in-memory computing scheme based on chiral edge states. In light of the dissipationless nature of chiral edge states in the quantum anomalous Hall insulator state, pushing our MTI device to the quantized Hall resistance regime can be potentially beneficial <sup>37</sup>. So far, the current-induced magnetization switching in the quantum anomalous Hall state remains to be experimentally demonstrated. Besides, there is a large family of quantum material systems that host chiral edge states and other tunable collective orders. We envision that many of these material systems can be utilized for cryogenic in-memory computing.

**Figure and captions**

**Fig. 1. Basic properties of the MTI device. a**, The sketch of the band structure of the MTI, where BCB, BVB, TSS, and CES represent the bulk conduction band, the bulk valence band, the topological surface state, and the chiral edge state. The red arrows represent the spin direction on the TSS. The inset shows the mechanism of the TSS-induced spin current generation. **b**, The out-of-plane magnetic field switching of the four MTI devices used in this work. The left and right insets illustrate the expected magnetic domain state and chiral edge conduction when the magnetization is fully switched down and up, respectively. **c**, The mechanism of the current induced SOT switching of MTI. The red and light blue arrows indicate the spin accumulation generated by the top and bottom TSS, and the blue arrow indicates the local magnetic moment. **d**, The pulse write current-induced switching of the four MTI devices. The left and right insets illustrate the expected magnetic moment. **d** are obtained using pulse measurements and the amplitude of the reading current is  $10^4 \text{ A/cm}^2$ . There is a 30 mT magnetic field along the x-direction for all current-induced SOT experiments.

**Fig. 2.** Memristive behavior of the MTI and Iris flower classification. **a**, The experimental setup for conducting the inference test with four MTI. PC, MCU, and MUX are short for personal computers, microcontrollers, and multiplexers/demultiplexers, respectively. The inset in the middle is the optical image of the four MTI with a channel width of 20  $\mu$ m, and length of 40  $\mu$ m. The scale bar is 300  $\mu$ m. **b**, The writing curve of 4 MTIs. The upper inset shows the scheme of the writing test, where a reset pulse (-10<sup>6</sup> A/cm<sup>2</sup>), a writing pulse, and a reading pulse (3x10<sup>4</sup> A/cm<sup>2</sup>) are applied in sequence. The Hall resistance is averaged from the reading pulse after 50 trials and the error bar is the standard deviation (see Methods 'Memristive switching behaviors in MTIs' for details). **c**, The reading test of the MTI. The upper inset shows the test scheme, where a reset pulse (-10<sup>6</sup> A/cm<sup>2</sup>), a writing pulse, and 90 reading pulses with an amplitude ranging from 1×10<sup>3</sup> A/cm<sup>2</sup> to 5.6 × 10<sup>4</sup> A/cm<sup>2</sup> are applied in sequence. **d**, The diagram of the multi-class cross-entropy algorithm and device inference. **e**, Classification accuracies of 30 inference tests. The dashed and solid horizontal lines indicate maximum and average accuracies of 96% and 88%, respectively.

**Fig. 3. Image recognition and quantum state preparation with MTM neural network**. **a**, The structure of the neural network for the MNIST image recognition. **b**, The image recognition accuracy of floating-point, MTM, and unipolar neural networks in 2000 steps. **c**, The weight distribution of three kinds of neural networks after training for 1000 steps. **d**, The diagram of the policy gradient algorithm for qubit quantum state preparation (see Methods 'Qubit preparation with policy gradient' for details). **e**, The dependence of average fidelity on the number of spins for different types of neural networks. The error bar is the standard deviation. **f**, The dependence of average fidelity on the training epoch for different types of neural networks in the case of 3 spins.

#### References

- 1. Patra, B. *et al.* Cryo-CMOS Circuits and Systems for Quantum Computing Applications. *IEEE J. Solid-State Circuits* **53**, 309–321 (2018).

- 2. Gonzalez-Zalba, M. F. *et al.* Scaling silicon-based quantum computing using CMOS technology. *Nat. Electron.* **4**, 872–884 (2021).

- 3. Xue, X. *et al.* CMOS-based cryogenic control of silicon quantum circuits. *Nature* **593**, 205–210 (2021).

- 4. Pauka, S. J. *et al.* A cryogenic CMOS chip for generating control signals for multiple qubits. *Nat. Electron.* **4**, 64–70 (2021).

- 5. Ruffino, A. *et al.* A cryo-CMOS chip that integrates silicon quantum dots and multiplexed dispersive readout electronics. *Nat. Electron.* (2021) doi:10.1038/s41928-021-00687-6.

- Wang, P. *et al.* Cryogenic benchmarks of embedded memory technologies for recurrent neural network based quantum error correction. *Tech. Dig. - Int. Electron Devices Meet. IEDM* 38.5.1-38.5.4 (2020) doi:10.1109/IEDM13553.2020.9371912.

- 7. Zhang, X.-M., Wei, Z., Asad, R., Yang, X.-C. & Wang, X. When does reinforcement learning stand out in quantum control? A comparative study on state preparation. *npj Quantum Inf.* **5**, 85 (2019).

- 8. Ielmini, D. & Wong, H.-S. P. In-memory computing with resistive switching devices. *Nat. Electron.* **1**, 333–343 (2018).

- 9. Wang, Z. *et al.* Resistive switching materials for information processing. *Nat. Rev. Mater.* **5**, 173–195 (2020).

- 10. Fan, Y. *et al.* Magnetization switching through giant spin-orbit torque in a magnetically doped topological insulator heterostructure. *Nat Mater* **13**, 699–704 (2014).

- 11. Fan, Y. *et al.* Electric-field control of spin-orbit torque in a magnetically doped topological insulator. *Nat Nanotechnol* **11**, 352–359 (2016).

- 12. Yasuda, K. *et al.* Current-Nonlinear Hall Effect and Spin-Orbit Torque Magnetization Switching in a Magnetic Topological Insulator. *Phys Rev Lett* **119**, 137204 (2017).

- 13. Che, X. *et al.* Strongly Surface State Carrier-Dependent Spin-Orbit Torque in Magnetic Topological Insulators. *Adv Mater* **32**, e1907661 (2020).

- 14. He, Q. L., Hughes, T. L., Armitage, N. P., Tokura, Y. & Wang, K. L. Topological spintronics and magnetoelectronics. *Nat. Mater.* **21**, 15–23 (2022).

- 15. Tokura, Y., Yasuda, K. & Tsukazaki, A. Magnetic topological insulators. *Nat. Rev. Phys.* **1**, 126–143 (2019).

- 16. Ladd, T. D. et al. Quantum computers. Nature 464, 45–53 (2010).

- 17. Lian, B., Sun, X. Q., Vaezi, A., Qi, X. L. & Zhang, S. C. Topological quantum computation based on chiral Majorana fermions. *Proc Natl Acad Sci U S A* **115**, 10938–10942 (2018).

- 18. Arute, F. *et al.* Quantum supremacy using a programmable superconducting processor. *Nature* **574**, 505–510 (2019).

- 19. Wong, H.-S. P. S. & Salahuddin, S. Memory leads the way to better computing. *Nat. Nanotechnol.*

**10**, 191 (2015).

- 20. Yao, P. *et al.* Fully hardware-implemented memristor convolutional neural network. *Nature* **577**, 641–646 (2020).

- 21. Wang, Z. *et al.* Reinforcement learning with analogue memristor arrays. *Nat. Electron.* **2**, 115–124 (2019).

- 22. Ambrogio, S. *et al.* Equivalent-accuracy accelerated neural-network training using analogue memory. *Nature* **558**, 60–67 (2018).

- 23. Chanthbouala, A. et al. A ferroelectric memristor. Nat. Mater. 11, 860–864 (2012).

- 24. Ni, K. *et al.* Ferroelectric ternary content-addressable memory for one-shot learning. *Nat. Electron.* **2**, 521–529 (2019).

- 25. Jung, S. *et al.* A crossbar array of magnetoresistive memory devices for in-memory computing. *Nature* **601**, 211–216 (2022).

- 26. Rowlands, G. E. *et al.* A cryogenic spin-torque memory element with precessional magnetization dynamics. *Sci. Rep.* **9**, 803 (2019).

- 27. Nguyen, M. H. *et al.* Cryogenic Memory Architecture Integrating Spin Hall Effect based Magnetic Memory and Superconductive Cryotron Devices. *Sci Rep* **10**, 248 (2020).

- 28. Lachman, E. O. *et al.* Visualization of superparamagnetic dynamics in magnetic topological insulators. *Sci Adv* **1**, e1500740 (2015).

- 29. Xia, Q. & Yang, J. J. Memristive crossbar arrays for brain-inspired computing. *Nat Mater* **18**, 309–323 (2019).

- 30. Kou, X. *et al.* Scale-invariant quantum anomalous Hall effect in magnetic topological insulators beyond the two-dimensional limit. *Phys Rev Lett* **113**, 137201 (2014).

- 31. Guo, Q. *et al.* Electrically Tunable Wafer-Sized Three-Dimensional Topological Insulator Thin Films Grown by Magnetron Sputtering\*. *Chinese Phys. Lett.* **37**, 057301 (2020).

- 32. Deng, Y. *et al.* Quantum anomalous Hall effect in intrinsic magnetic topological insulator MnBi 2 Te 4. *Science (80-. ).* **367**, 895–900 (2020).

- 33. Sharpe, A. L. *et al.* Emergent ferromagnetism near three-quarters filling in twisted bilayer graphene. *Science* (80-. ). **365**, 605–608 (2019).

- 34. Serlin, M. *et al.* Intrinsic quantized anomalous Hall effect in a moiré heterostructure. *Science* (80-.). **367**, 900–903 (2020).

- 35. Kou, X. *et al.* Metal-to-insulator switching in quantum anomalous Hall states. *Nat. Commun.* **6**, 8474 (2015).

- 36. Polshyn, H. *et al.* Electrical switching of magnetic order in an orbital Chern insulator. *Nature* **588**, 66–70 (2020).

- 37. Alam, S., Islam, M. M., Hossain, M. S., Jaiswal, A. & Aziz, A. CryoCiM: Cryogenic compute-inmemory based on the quantum anomalous Hall effect. *Appl. Phys. Lett.* **120**, 144102 (2022).

- Liu, L. *et al.* Spin-torque switching with the giant spin Hall effect of tantalum. *Science* (80-. ).

336, 555–558 (2012).

- 39. Yu, G. *et al.* Switching of perpendicular magnetization by spin–orbit torques in the absence of external magnetic fields. *Nat. Nanotechnol.* **9**, 548 (2014).

- 40. Lan, X. *et al.* Gradient Descent on Multilevel Spin–Orbit Synapses with Tunable Variations. *Adv. Intell. Syst.* **3**, 2000182 (2021).

- 41. Yang, S. *et al.* Integrated neuromorphic computing networks by artificial spin synapses and spin neurons. *NPG Asia Mater.* **13**, 11 (2021).

- 42. Shih, Y.-C. *et al.* A Reflow-capable, Embedded 8Mb STT-MRAM Macro with 9nS Read Access Time in 16nm FinFET Logic CMOS Process. in *2020 IEEE International Electron Devices Meeting (IEDM)* 11.4.1-11.4.4 (IEEE, 2020). doi:10.1109/IEDM13553.2020.9372115.

- 43. Chou, C.-C. *et al.* A 22nm 96KX144 RRAM Macro with a Self-Tracking Reference and a Low Ripple Charge Pump to Achieve a Configurable Read Window and a Wide Operating Voltage Range. in 2020 IEEE Symposium on VLSI Circuits 1–2 (IEEE, 2020). doi:10.1109/VLSICircuits18222.2020.9163014.

- 44. Murmann, B. 'ADC Performance Survey 1997-2021,' [Online]. Available: http://web.stanford.edu/~murmann/adcsurvey.html.

# Methods

# Device fabrication and characterization

High-quality single-crystalline Cr-BST films were grown on semi-insulating GaAs (111) substrates in an ultra-high vacuum Perkin-Elmer MBE system. Before the growth, the substrates were annealed to 580 degrees to remove the native oxide, under Te rich environment. The growth temperature is 200 degrees, and the epitaxial growth was monitored by an in-situ reflection high-energy electron diffraction (RHEED) technique. After the film growth, a 2 nm Al was evaporated to passivate the surface at room temperature.

The Hall bar device is fabricated by the following steps: 1. Photolithography to define the Hall bar pattern; 2. ion-beam etching to form the Hall bar structure; 3. photolithography to define the gold electrode pattern; 4. evaporation and lift-off to form gold electrodes. **Fig. 1a** illustrates the schematic of the device. The MTI Hall bar device has a channel width of 20  $\mu$ m, length of 40  $\mu$ m, and thickness of 5 nm.

The sample is placed in a cryogenic system from CryogenicLtd for low temperature measurements; The current pulse is applied by a Keithley 6221 current source; The Hall voltage is measured by a Keithley 2182a nanovolt meter; The controlling program is written by Python, and PyVisa package is used for device communication. All experiments in this paper are conducted at 2 K unless specified. We first characterize the device by applying sequential writing and reading pulses of 2 ms in the x-direction and collecting the Hall voltage in the y-direction. During the writing phase, a 30 mT symmetry-breaking magnetic field is applied along the x-direction.

# **Current and temperature dependence**

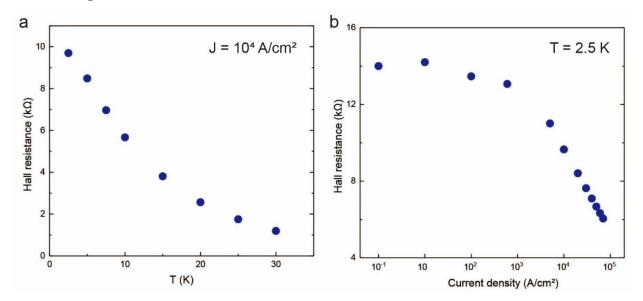

In the ultralow temperature where the surface states and bulk states freeze out, our Cr-BST exhibits quantized anomalous Hall resistance (AHR),  $h/e^2 \approx 25.8 \text{ k}\Omega$ , due to the transport of pure chiral edge states <sup>30,35</sup>. Meanwhile, at the slightly elevated temperature, while the chiral edge state (CES) still exists, the AHR is not quantized due to the electron conduction from surface states and bulk states (**Fig. 1a**).

The dependences of AHR on the temperature and reading current are shown in **Extended Data Fig. 1a** and **1b**. AHR decreases from 9.7 k $\Omega$  to 1.2 k $\Omega$  from 2.5 K to 30 K with a reading current of 10<sup>4</sup> A/cm<sup>2</sup>. Meanwhile, AHR can reach 14 k $\Omega$  (~ 0.55 *h/e<sup>2</sup>*) if the reading current is at the level of 10 A/cm<sup>2</sup>. Such a high value suggests CES transport plays an important role in our MTI device.

# Mechanism of SOT switching in MTIs

In the past experiments, we have shown that the Cr-BST/BST gives rise to a giant spin-orbit torque and the origin of the large spin-orbit torque efficiency is due to the spin-momentum locking of topological surface states by tuning the relative ratio between surface states and bulk states in a single Cr-BST layer using a gate voltage <sup>10,11</sup>. Note that while the Cr-BST is nominally uniformly doped, the different dielectric environment on the top (AlO<sub>x</sub> capping layer) and bottom (GaAs substrate) produces a net spin current from the top and bottom surface states. As a result, we show that the magnetic order and its associated CES in the Cr-BST can be switched by the in-film plane current injection (**Fig. 1b**). Note that to break symmetry for switching magnetization along the out-of-film plane direction, we apply a small assistance field of 30 mT. Due to the multi-domain nature of magnetic topological insulators <sup>28</sup>, the current-switchable AHR range is already two orders of magnitude larger than that of a technology-relevant ferromagnet, CoFeB (around several Ohms) <sup>38,39</sup>, which makes the readout using AHR feasible.

# Memristive switching behaviors in MTIs

**Fig. 2a** illustrates the measurement setup. Four devices are characterized which will be used for the classification of the IRIS dataset. Each device can be independently addressed via multiplexers and demultiplexers commanded by a microcontroller unit (MCU). The field-induced switching of the four MTI devices is shown in **Fig. 1b** and the current-induced SOT switching in **Fig. 1d**. The devices show uniform and consistent field-induced and current-induced switching properties. For the field switching, all devices have a giant AHR of about 11 kΩ and a coercivity of 100 mT. For current-induced switching, all devices can be switched by a current of 0.5 mA (current density of  $5 \times 10^5$ A/cm<sup>2</sup>) and have an AHR of -600 Ω to 600 Ω. Compared with normal HM/FM structures, the switching current density is more than one order of magnitude lower, and the AHR is more than two orders of magnitude higher.

We then characterize the switching curve (e.g., write current vs. AHR) of the device. In this experiment, we reset the resistance of the memristor via a -1 mA (-10<sup>6</sup> A/cm<sup>2</sup>) pulse before each write pulse, followed by applying a read pulse of 30  $\mu$ A (3×10<sup>4</sup> A/cm<sup>2</sup>) to readout the Hall resistance. The switching curves acquired from 50 trials are shown in **Fig. 2b**. It should be noted that although 12 resistance levels are shown, all AHR values within the AHR range can be achieved. **Extended Data Fig. 2a** shows the write distribution of the MTI devices, presented as the difference between the written AHR and the mean written AHR of 50 trials for each of the 12 resistance levels above. The maximum write variation is less than 25  $\Omega$  and the standard deviation error is 7.6  $\Omega$ , which corresponds to about 1.9% of the writing AHR range (-200  $\Omega$  to 200  $\Omega$ ). This write variation is substantially smaller than other memristor devices that operate on the stochastic formation and rupture of conducting channels.

The reading distribution of the MTI device is characterized by first applying a write pulse followed by 90 consecutive read pulses. We first test whether the AHR is stable or not across different read pulse amplitudes from 1  $\mu$ A (1 × 10<sup>3</sup> A/cm<sup>2</sup>) to 56  $\mu$ A (5.6 × 10<sup>4</sup> A/cm<sup>2</sup>), which is necessary for analog multiplication using the AHR neural network. It can be observed in **Fig. 2c** that the measured Hall voltage is very stable over repeated reading attempts, suggesting a small read noise of the device and low disturbance. The distribution of reading noise, defined as the difference between the measured AHR and the mean measured AHR of the 90 read operations, is shown in **Extended Data Fig. 2b**. We observe a maximum reading noise of 1.5 % and a standard deviation as small as 0.37%.

In addition to the above noises, the thermal effect on CES introduces a reading discrepancy as AHR reduces when the reading current increases (see **Extended Data Fig. 1**), which creates a nonlinearity during inference that potentially impacts the vector-matrix multiplication (VMM) operation. **Extended Data Fig. 2c** shows AHR as a function of reading current at different magnetization states. The Hall resistance for the same magnetization state changes dramatically when the reading current density is below  $1 \times 10^3$  A/cm<sup>2</sup>, while it remains relatively stable when the reading current density is above  $1 \times 10^4$  A/cm<sup>2</sup>. Hence, the AHR measurement presented in the main manuscript is measured by a reading current density of  $1 \times 10^4$ A/cm<sup>2</sup>. Meanwhile, to evaluate the impact of reading discrepancy on the inference test, the data from  $2 \times 10^4$  A/cm<sup>2</sup> to  $4 \times 10^4$  A/cm<sup>2</sup> are collected for making the statistics of reading discrepancy noise. The Hall resistance measured by  $3 \times 10^4$  A/cm<sup>2</sup> pulses is set as the reference, and the reading error is defined as the difference between the reference value and the resistance measured by other pulse amplitude. As shown in **Extended Data Fig. 2d**, there is at most a 5% reading discrepancy to the reference resistance value in the interesting range and the standard deviation error is about 2%.

### Implementation of Iris pattern classification

The procedure of the Iris pattern classification is shown in **Fig. 2d**. We build three binary classifiers corresponding to the 3 types of flowers (Setosa, Versicolor, and Virginica) in the Iris dataset. The classifiers are identical, training on the same input data *S* with a dimension of  $[4 \times 150]$ , but with the label *Y* binarized

to each flower (e.g., for the Setosa classifier, Setosa samples are labeled as "1" while other samples are labeled as "0"). Each classifier, therefore, has a [1×4] weight matrix W, and the output is generated by multiplying the input data with the weight matrix to obtain the prediction Z=WS, then converted to a probability P(Z) via a sigmoid function:

$$P(Z) = \frac{1}{1 + e^{-Z}} \tag{1}$$

We adopt the cross-entropy cost function and gradient descent for the optimizer, which corresponds to the weight update rule given by:

$$\Delta W = \frac{\gamma \cdot (P(Z) - Y) \cdot S^T}{N}$$

(2)

where  $\gamma$  is the learning rate and N is the number of input samples. At epoch n + 1,  $W^{n+1} = W^n - \Delta W$ . The final prediction result (PR) is obtained by comparing P(Z) of each classifier:

$$PR = \operatorname{argmax}(P(Z_{\text{Setosa}}), P(Z_{\text{Versicolor}}), P(Z_{\text{Virginica}})).$$

(3)

PR can take values of 0, 1, and 2 which correspond to Setosa, Versicolor, and Virginica, respectively. The PR is then compared with the original label of the sample to obtain accuracy.

We then demonstrate the classification of the Iris dataset using the MTI devices. The Iris dataset contains 150 samples, each with the measurements of 4 features of the flower: sepal length, sepal width, petal length, and petal width. We train the network depicted in **Fig. 2d** on the entire Iris dataset using the above logistic regression algorithm. The final accuracy is 96%, as shown in **Extended Data Fig. 3a**. The weight matrices for each flower are:

Classifier 1: W<sub>setosa</sub> = [2.03, 10.02, -11.24, -1.93],

Classifier 2: W<sub>versicolor</sub> = [2.02, -2.94, 0.63, -0.68],

Classifier 3:  $W_{\text{virginica}} = [-6.63, -12, 13.75, 4.93].$

We then map the weights to the AHR of the MTM such that its AHR is within the range between -200  $\Omega$  and 200  $\Omega$  (the writing current has a linear relationship with the AHR), and the input currents to the AHRs are in the range of from 20  $\mu$ A to 40  $\mu$ A (the reading current in this range will only bring 2% noise) is:

Classifier 1:  $W'_{setosa} = [30.45\Omega, 150.3\Omega, -168.6\Omega, -28.95\Omega],$

Classifier 2:  $W'_{versicolor} = [30.3\Omega, -44.1\Omega, 9.45\Omega, -10.2\Omega],$

Classifier 3:  $W'_{virginica} = [-99.45\Omega, -180\Omega, 206.25\Omega, 73.95\Omega].$

The inference is conducted in the following steps. Step 1: the AHR of 4 memristors is programmed to  $W'_{Setosa}$  to hardware implement classifier 1. Step 2:  $I_m$  is sent to the memristor array row by row and the Hall voltages of 4 memristors are measured and summed together. The total Hall voltage of the 4 memristors is the output of classifier 1 (denoted as V<sub>1</sub>). Step 3: Steps 1-2 are repeated for Classifiers 2 and 3 (V<sub>2</sub> and V<sub>3</sub>). Finally, we apply an argmax function on V<sub>1</sub>, V<sub>2</sub>, and V<sub>3</sub> to obtain the final classification result (FCR). We compare this with the ideal classification accuracy as well as the simulated accuracy in **Extended Data Fig. 3b**. Simulation across 100 trials results show that when the AHR should achieve an average of 88.6% accuracy. Experimentally, the network achieves an average accuracy of 87.8% across 30 inference tests (**Fig. 2e**).

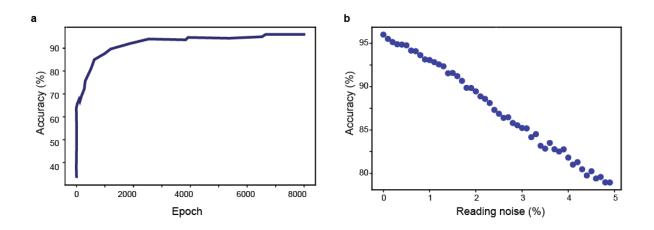

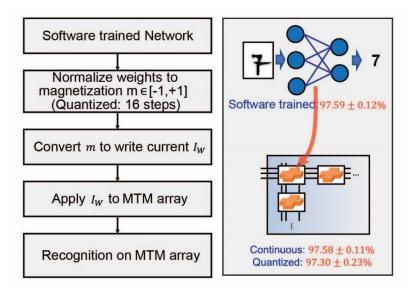

#### **MNIST** dataset simulation

To further evaluate the MTI device and show the importance of bipolar weights, we demonstrate image recognition simulation on a larger neural network and the MNIST dataset. The neural network has two layers, the first hidden layer with 128 neurons and the second classification layer with 10 neurons as shown in Fig. 3a. The algorithm is depicted in Extended Data Fig. 4. The network is trained by the stochastic gradient descent for 2000 steps with a batch size of 128, using the Adam optimizer and a cross-entropy loss function. An 12 weight loss of  $10^{-4}$  to encourage the weight distribution to be close to 0. The softwaretrained neural network achieves an accuracy of 97.59%±0.12%. We compare the performance of the neural network with different device models (floating-point neural network, MTM neural network, and unipolar neural network). Memristance of the floating-point neural network can take any real values without limitation, while that of the MTM neural network is bounded to be -800  $\Omega$  to 800  $\Omega$  and subject to a 4% (2% for writing and 2% for reading) Gaussian noise. The memristance of the unipolar neural network only takes positive resistance values from 1000  $\Omega$  to 3000  $\Omega$ . Fig. 3c presents the normalized weight of each neural network after training for 1000 steps. The weight patterns of different synapses of MTM neural network almost replicate the result of the floating-point neural network indicating the in-situ training of our MTM with bipolar weights parallels that of the software. For the unipolar neural network, however, the performance is bounded by the limited range of weights, such as in classifying characters "1" and "2", owing to lacking negative resistances. As shown in Fig. 3b, the floating-point neural network and MTM neural network both achieve a final accuracy of 97.59%±0.12%, in contrast to the unipolar neural network achieving a final accuracy of  $91.57 \pm 0.12$  %. Meanwhile, we consider a more practical case in which MTM states are quantized. For this design, AHRs are quantized to the nearest value of 16 steps between [-1, +1 (normalized) before calculating the write current. The quantized network shows a less than 1%accuracy drop to 97.30% ±0.23% (Extended Data Fig. 4). This result confirms the superior performance of MTI and the crucial role of bipolar weights in implementing deep learning models.

### Qubit preparation with policy gradient

We adopt the quantum-state preparation task described in Zhang et al. <sup>7</sup> (Fig. 3d). The task aims to control the state of *K* serially coupled spins from an initial state to the target state via a magnetic field *B*. The initial state is the leftmost spin in the  $|1\rangle$  state and all others in the  $|0\rangle$  state. The target state has the rightmost spin in the  $|1\rangle$  state and all others in the  $|0\rangle$  state. A policy gradient system is adopted for the task. The system composes an environment with state *S*, an agent that produces an action *A*, and the reward of the action *R*.

The environment represents the evolution of the K serially coupled spins. S represents the state of the spins, and is a complex vector of length K. The evolution of S is determined by the Hamiltonian H, which can be computed as

$$H(t) = C \sum_{k=1}^{K-1} \left( S_x^k S_x^{k+1} + S_y^k S_y^{k+1} \right) + \sum_{k=1}^{K} 2B_k(t) S_z^k$$

(4)

Where C=2 is the coupling strength between adjacent spins and  $B_k(t)$  is the control magnetic field at timestep t. The evolution of the state follows the Hamiltonian mechanics, e.g.,

$$S(t+dt) = S(t)e^{-iH(t)dt}$$

<sup>(5)</sup>

Where d*t* is the length of the timestep.

The agent is a network that produces the control magnetic field *B*. It is a two-layer fully-connected neural network, with an input feature of size 2K (e.g. the real and imaginary components of the *K* spins), a number of neurons of N=16, and an output of size  $2^{K}$ . (e.g., all possible actions;  $B_{ctrl} = \pm 40$  for each of the *K* spins; for example, for K=2, the possible configurations are  $[-B_{ctrl}, -B_{ctrl}]$ ,  $[-B_{ctrl}, +B_{ctrl}]$ ,  $[+B_{ctrl}, -B_{ctrl}]$ , and  $[+B_{ctrl}, +B_{ctrl}]$ ). The agent selects an action with a probability based on the softmax of the neural network output.

The reward is computed based upon a fidelity function f, which is the absolute distance between the environment state S and the target state  $S_t$ , e.g.,

$$f = |\langle S|S_t \rangle|^2 \tag{6}$$

The reward R(t) at timestep t is equal to  $R_{max} = 2500$  when f is within  $\varepsilon$  ( $\varepsilon = 0.01$ ) of its maximum value of 1, indicating that the current state is already in the target state, and  $10^*f$  otherwise.

In each trial, the network is trained for  $N_{ep}$ =1000 episodes. During each episode, the environment and agent interact for  $N_s$ =20 steps. In each step, the agent generates the control magnetic field, the state of the environment evolves, and a reward is computed. At the end of each episode, the episode reward  $R_{ep}$  is obtained via a discounted reward function, e.g.,

$$R_{ep} = \sum_{n}^{N_S} r^t R(t) \tag{7}$$

where r = 0.99 is the discount rate. This reward is the loss used to update the neural network in each episode. When the trial is complete, the network is determined to be trained. We report the maximum  $f_{ep}$  among the last 10 episodes as the fidelity of the trial  $f_{trial}$ .

For the floating-point network, we directly train upon a software-based neural network with weights that can take on any value. For our bipolar MTM network, the trained weights in each episode are converted to the resistances of the MTM via the following steps: (a) clipping the weights to the range of [-1, 1], (b) mapping it to the resistance range of [-600, 600], (c) finding the corresponding currents, and (d) applying them to an array of device models with a write error of 2%. The unipolar network follows the same process with the weights clipped to the range of [0,1] and mapped to the resistance range [1000, 3000] instead.

We run the three networks for different configurations involving the number of spins *K* to control. For each configuration, we execute at least 12 trials and report the average  $f_{trial}$  in **Fig. 3e** and the average fidelity of each episode in **Fig. 3f**.

#### Design challenges for Hall effect-based neural network

Constructing a practical AHR neural network confronts huge challenges in both materials and network designs. From the material perspective, the AHR of normal heavy metal (HM) and ferromagnetic transition metal (FM) structures is less than 5  $\Omega$ <sup>38,39</sup>. For an HM/FM Hall bar device with a channel width of 100 nm and a thickness of 5 nm, the required current density for generating reliable readout signals (e.g., to surpass the thermal and coupling noise of transistors, which is in the range of millivolts) is more than  $10^{12}$  A/m<sup>2</sup>. This current is an order of magnitude higher than the switching current and leads to disturbance in the device state. Meanwhile, the SOT efficiency in these structures also needs improvement, being capped at 1. In this context, MTI possesses incomparable advantages owing to its 2-3 orders higher AHR and SOT efficiency. MTM based neural network is thus expected to exhibit much lower power consumption.

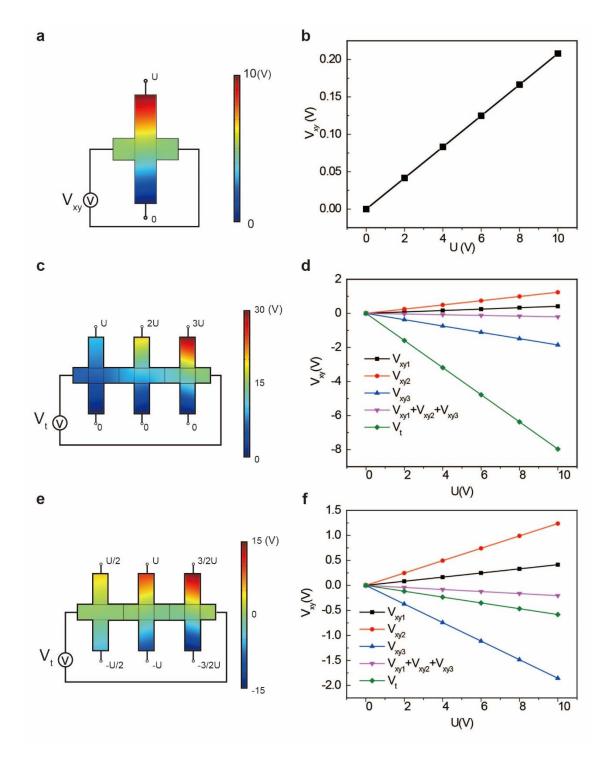

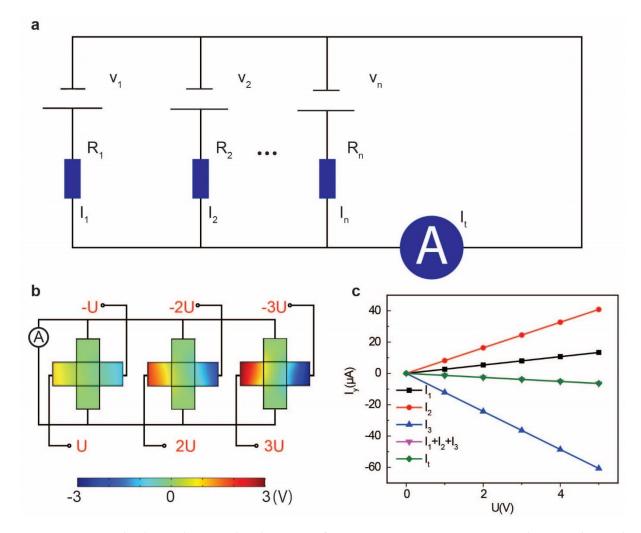

From the network perspective, a direct connection of any of the four terminals of a Hall bar could lead to leakage/sneak current paths that not only cause large energy consumption but degrade the readout signal. Since the Hall bar device is a 4-terminal device in which every terminal is conductive, there are many paths where leakage current can flow. However, this issue has yet to be considered and investigated. Recently, Lan et al. has proposed to connect the Hall bar devices in series to sum Hall voltages <sup>40</sup>. Below, we show that this design will be problematic and fail to sum AHE voltages correctly using COMSOL simulation.

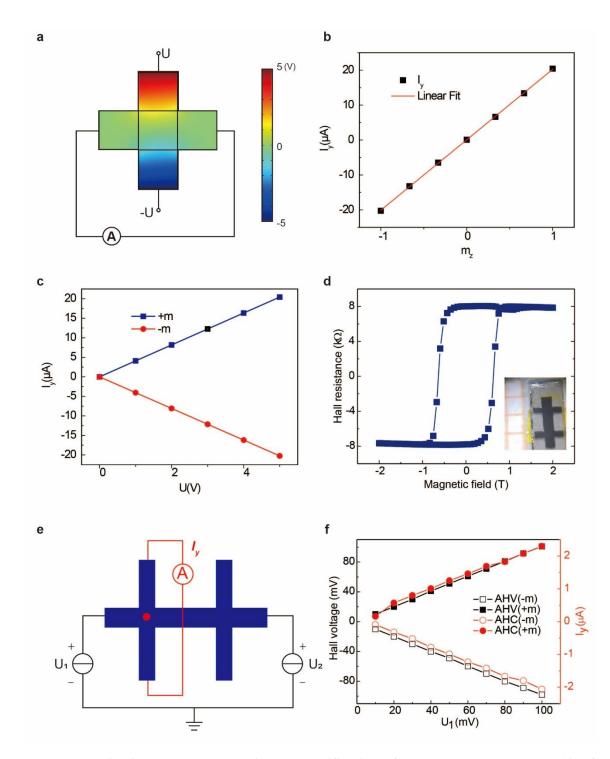

The AHE voltage of a single Hall bar device is shown in **Extended Data Fig. 5a** and **b**. The conductivity of the magnetic material and the connecting wires are  $\sigma_{mag} = \begin{pmatrix} 10^4 & 10^3 \\ -10^3 & 10^4 \end{pmatrix}$  S/m and  $\sigma_{metal} = \begin{pmatrix} 10^9 & 0 \\ 0 & 10^9 \end{pmatrix}$  S/m, respectively. The color on the contour plot represents the electric potential of the device when a 10 V voltage is applied. **Extended Data Fig. 5b** shows the dependence of Anomalous Hall voltage (AHV) on the applied voltage. As expected, the AHV is proportional to the AHR and the input voltage.

We then simulate 3 Hall bar devices with their Hall channels in series as shown in **Extended Data Fig. 5c**. The devices have different AHRs translating to different diagonal conductivities in the simulation, as,

$$\sigma_{\text{mag1}} = \begin{pmatrix} 10^4 & 2 \times 10^3 \\ -2 \times 10^3 & 10^4 \end{pmatrix} \text{ S/m};$$

$$\sigma_{\text{mag2}} = \begin{pmatrix} 10^4 & 3 \times 10^3 \\ -3 \times 10^3 & 10^4 \end{pmatrix} \text{ S/m};$$

$$\sigma_{\text{mag3}} = \begin{pmatrix} 10^4 & -3 \times 10^3 \\ 3 \times 10^3 & 10^4 \end{pmatrix} \text{ S/m}.$$

The input voltages are U, 2U, and 3U, respectively. We compare the AHV of each of the devices individually, then compare their sum with the voltage of 3 Hall bars in series (**Extended Data Fig. 5d**). It is clear that  $V_t \neq V_{xy1}+V_{xy2}+V_{xy3}$ .

This simulation result suggests that a simple connection of Hall bar devices fails to sum Hall voltages. Now we discuss why it happens. The electric potential contour plot is shown in **Extended Data Fig. 5c**. Considering only the vertical biases, the potential in the center of each Hall bar should be 0.5U, U, and 1.5U. Considering only the lateral biases, the center potential of each Hall bar should be the center of the adjacent Hall bar plus half the AHV of the two to enable summation. The disagreement in the potential difference in the vertical and horizontal paths can be viewed as a leakage path between the two paths that impact the summation of the AHVs, therefore, rendering the summation problematic.

As shown in **Extended Data Fig. 5e**, we also consider applying antisymmetric voltages across the Hall bar device so that the center potential between each device is smaller. The input voltages for each Hall bar device are 0.5U and -0.5U, U and -U, 1.5U and -1.5U, respectively. The conductivity of the magnetic material and the wires is the same as the previous simulation. As shown in **Extended Data Fig. 5f**, the AHV of 3 Hall bars in series is still not equal to the summation of the individual AHV of each Hall bar, although the difference is much smaller than in the previous case. It is worth mentioning that this leakage path also impacts the write operation as the designated current density passing through the channel is changed. Therefore, making sure that each device operates the same when they are independent and when they are in series is crucial to correct neural network operation.

### MTM neural network design

To leverage the efficiency advantage of computing with a large-scale MTM neural network hardware, we design a novel circuitry to overcome the challenges mentioned in the previous section (Methods 'Design challenges for Hall effect-based neural network'). To solve the issue that the Hall signals don't sum correctly, we read anomalous Hall current (AHC) instead of AHV for Hall signal summation. The Hall bar devices are connected in parallel during VMM operation while being isolated by transistors during read/write. The validation of this current-mode readout scheme is presented in the next section (Methods 'Verification of Hall current mode reading'). Another issue for the MTM neural network is that the AHE signal could be too small when the device size scales down. The reduced read current and device dimensions result in a significantly smaller readout signal. To overcome this, we flow the read current perpendicular to the external field direction and collect AHC along the field direction. The magnetization states would not be changed by the SOT effect due to symmetry <sup>39</sup>. The read disturbance would be much lower, hence allowing us to increase the read current for a higher AHC signal.

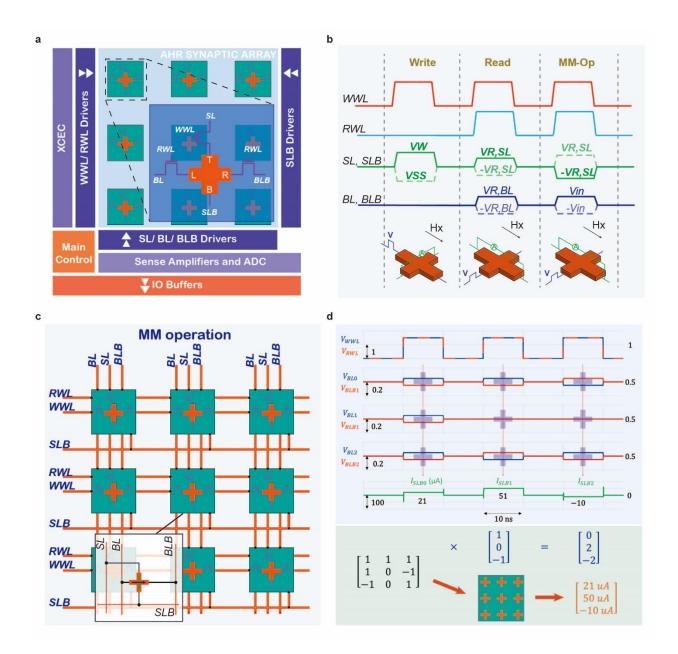

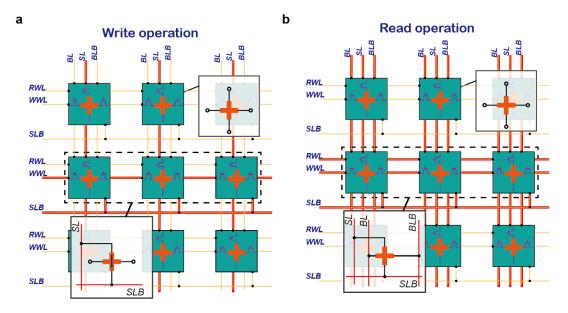

The schematic of the MTM neural network is shown in Extended Data Fig. 6a. Three transistors are introduced to each MTM to form a memory cell. Transistor T<sub>T</sub>, controlled by WWL, connects the top node T to bus SL. Transistors  $T_L$  and  $T_R$ , both controlled by RWL, connect the lateral nodes L and R to bus BL and BLB, respectively. The bottom node B is connected to SLB directly. In the array, cells in the same row share common WWL and BLB buses, while cells of the same column share the same SL, SLB, and BL. The unconventional design of running SL and SLB perpendicular to each other is necessary to enable neural network and read operations within the same array. Extended Data Fig. 6b illustrates the waveforms of the MTM array during memory and VMM operations. During a memory write, the WWL of the selected row is activated, while the rest WWLs and all RWLs are grounded. SL and SLB are biased to the write conditions, e.g.,  $V_{SLi} = V_{w,i}$ ,  $V_{SLBi} = V_{SS}$ . During a memory read, both the WWL and the RWL of the selected row are activated, all BLs and BLBs are biased at the read voltage with the center node of the AHR virtually grounded, e.g.,  $V_{BLi, BLBi} = V_{VGND} \pm V_{RBL}$ , and all SLs and SLBs are clamped to the lateral read voltage, e.g.,  $V_{SLi,SLBi} = V_{VGND} \pm V_{RSL}$ . The AHC of the selected memory cells will be accumulated on each SL as  $I_{SL,i}$ . The virtual ground VGND design avoids electrical current between the horizontal and the lateral channels that disrupts the readout. The schematic description of the write and read operations are depicted in Extended Data Fig. 7. During a VMM operation, all WWLs and RWLs are turned on. Voltages corresponding to the neural network inputs are applied to BL and BLB, e.g.,  $V_{BLi,BLBi} = V_{VGND} \pm V_{in,i}$ . The SLs and SLBs are clamped to the lateral read voltage in reverse, e.g.,  $V_{SLj,SLBj} = V_{VGND} \pm V_{RSL}$ . The neural network output currents are read from each SLB as I<sub>SLB.i</sub>. The schematic description of the VMM operation is shown in Extended Data Fig. 6c.

#### Verification of Hall current mode reading

Experimental characterization of AHC has not been reported despite extensive research on AHV. Hence, we start by characterizing AHC in a Hall bar device where voltages are applied to both longitudinal and transverse channels. We first study AHC via a Finite Element method. **Extended Data Fig. 8a** shows the device model of the simulation where the color represents the voltage potential, and the arrow represents the current. The voltages are applied to the two ends of the longitudinal (x-) channel with the same amplitude but opposite signs so that the center of the device is a virtual ground. The simulation result suggests the y-channel current presents very similar behavior as the AHV. Linear relationship between  $I_y$  and magnetization (**m**) is observed in **Extended Data Fig. 8b**, where **m** changes the off-diagonal conductivity. The terminal current passing through the y-channel,  $I_y$ , is proportional to U as shown in **Extended Data Fig. 8c**.

We then conduct experiments to characterize AHC in an MTI Hall bar device with an AHR of about 8000  $\Omega$ . The hysteresis loop of the device is shown in **Extended Data Fig. 8d** with the device photo shown in the inset. The structure of the device and the experiment configuration are shown in **Extended Data Fig. 8e**. The voltages are applied by 2 *Keithley* 2450 source meters. AHR and AHC are measured by a *Keithley* 2000 multi-meter. U<sub>1</sub> is swept from 10 mV to 100mV while keeping U<sub>2</sub> about 7× of -U<sub>1</sub> to keep the potential at the intersection of the x and y channels near zero. It can be seen in **Extended Data Fig. 8f** that there is a linear relationship between U<sub>1</sub> and the Hall voltage and *I*<sub>y</sub>, and after reversing **m** the slope of the curve reverses sign. This phenomenon agrees with **Extended Data Fig. 8b and 8c** and the numerical values also fit the model. The resistance of the side channel is 52 kΩ. The main channel current (~12.5 uA at U<sub>1</sub> = 100 mV) is about 6 times of AHC while the side Hall bar resistance is also about 6 times of AHR which agrees with the simulation.

We then empirically obtain the following relationship according to the above observations,

$$I_{y} = \frac{V_{x}R_{h}}{R_{sx}R_{sy}} \tag{8}$$

where  $R_{sx}$  and  $R_{sy}$  are the two-terminal resistance of the x-channel and y-channel of the Hall bar, respectively, and  $R_h$  is the Hall resistance of the device. This AHC retains the proportional dependence on  $R_h$  and  $V_x$ .

Having established the characteristics of AHC in a single Hall bar device, we extend our model to parallelconnected Hall bar networks. The equivalent circuit model is shown in **Extended Data Fig. 9a**. Each Hall bar can be modeled as a voltage source with an electromotive force (EMF) of  $V_n$  equal to its AHV and transverse channel (y channel) resistance of  $R_{sy}$ . When the devices are connected in parallel, the total current  $I_t$  will be equal to the sum of the terminal current according to Kirchhoff's law, e.g.

$$I_{t=}I_{1} + I_{2} + \cdots + I_{n} \tag{9}$$

where *n* is the device number,  $I_i$  (i =1, 2..., n) is defined as the AHC of each device. As each Hall bar device and the ampere meter are connected in parallel, the terminal voltage for all Hall bars is zero. We can thus calculate AHV ( $V_i$ ) of each device via Eq. (8) and obtain,

$$V_i = I_i \cdot R_{sy} \tag{10}$$

Combining Eq. (5) and (6), we can obtain

$$V_1 + V_2 + \cdots V_n = I_t \cdot R_{sy} \tag{11}$$

We thus obtain,

$$I_t = \frac{V_1 + V_2 + \cdots + V_n}{R_{sy}} \tag{12}$$

This equation suggests the linear summation of AHV can be represented by measuring the total terminal current  $I_t$  In other words, the current mode reading scheme can be applied to readout VMM operations in neural networks like AHV. Because each Hall bar is driven independently and the potential across the y channel is the same, Hall signals can be correctly summed without the leakage current issue.

To verify our model, we confirm the summation of AHC using COMSOL simulation. We put 3 Hall bar devices in parallel as shown in **Extended Data Fig. 9b**. The top and bottom bus lines are connected so that

the current on the bus line can be measured. The conductivity of connecting wires and each Hall bar is the same as in the section (Methods "Design challenges for Hall effect-based neural network'). The terminal voltages are 2U, 4U, and 6U. The total current on the bus line ( $I_T$ ) is presented in **Extended Data Fig. 9c**. We compare the results with the individual AHC of each device ( $I_1+I_2+I_3$ ) and confirm that the results match Eq. (12). We also successfully verify the summation of AHC signals in a circuit-level simulation (see next section for detail). These results verify the feasibility of summing AHC signals for VMM in the AHR neural network.

It is worth noting that Yang et al. also presents a design that connects Hall bar devices in parallel for neural network operation <sup>41</sup>. Their design reads the terminal voltage of parallel connected devices for VMM. The terminal voltage  $U_t$  will be the average AHV of all devices, e.g.,  $U_t = \frac{V_1 + V_2 + \cdots + V_n}{n}$ . The issue in this design is that the contribution of each device voltage is averaged, prohibiting the development of large neural network arrays (the signal of each device is divided by *n*). On the other hand, our design maintains the output signal.

#### **Circuit simulation**

We simulate the MTM neural network on the commercial design platform Cadence using a foundry process. The MTM model is implemented as a 4-component conductance-transconductance model with respect to the center node of the MTM. The simulation result of a 3-input VMM operation is presented in **Extended Data Fig. 6d**. Three weights are stored as the magnetization of three MTMs  $[m_1, m_2, m_3] = [+1, +0, -1]$ , and the VMM operation is conducted with different input values  $[V_{in,1}, V_{in,2}, V_{in,3}] = [+0.1V, +0.1V, +0.1V]$ , [+0.1V, +0V, -0.1V], and [-0.1V, +0V, +0.1V]. The SLB currents ( $I_{SLB} = 21 \ \mu A, 50 \ \mu A$ , and  $-11 \ \mu A$ ) are almost perfectly linear to the multiply-and-accumulate results (0, +2, -2). The small offset is caused by the nonzero resistance of the access transistors and parasitic along each bus, which reduces the voltage bias on the MTMs. This result further confirms the feasibility of using AHC for VMM in AHR neural networks.

Performance comparison of the MTM device and other memristor devices is presented in Extended Data Tab. 1. The dimension of our AHR memristor is 100 nm×100 nm while RRAM and MRAM devices are 50nm in diameter. To calculate the energy for MNIST, we first extracted the capacitance on the WLs, BLs, and SLs using parasitic extraction (PEX) on the layout of a 3x3 dummy-cell mini-array. The capacitance on the BLs and SLs was about 0.2 fF/cell and that of the WLs was about 0.4fF/cell. The charge/discharge energy of the BLs, SLs, and WLs can be obtained as  $CV_{DD}V_{Swing}$ , where  $V_{DD} = 0.85 V$  is the supply voltage and V<sub>Swing</sub> are the voltages on the BLs, SLs, and WLs during operation. For the STT-MRAM, read and neural network operations use a BL voltage of 300 mV and write a voltage of 1.5 V  $^{42}$ . For the RRAM, read and neural network operations use a BL voltage of 0.7 V and write a voltage of 1.6 V <sup>43</sup>. For our MTM. read and neural network operations use BL and SL voltages of 100mV and write uses an SL voltage of 50mV. All WLs are driven to  $V_{DD}$ . The dissipation energy can be obtained as IVT, where I is the current flowing through the memory cell, V is the supply voltage  $V_{DD}$ , and T is the cycle time. Cell current is obtained by dividing the read/write voltage by the device resistance (RRAM:  $10 \text{ k}\Omega/100 \text{ k}\Omega$ , STT-MRAM:4  $k\Omega/8 k\Omega$ , and MTM:10 k $\Omega$  in either direction) and the cycle time is set to 5ns (100 MHz). The decoder energy was extracted using simulation of the critical decoding path built upon 3-to-8 and 4-to-16 predecoders, resulting in the energy of about 1fJ/bit. The sense amplifier energy was extracted using a simulation of a latch-type sense amplifier and consumed up to 4 fJ/bit in the worst-case condition. The write driver energy was extracted from a FO4-sized buffer and consumed up to 10 fJ/bit. During neural network operation, we add ADC energy of up to 1.9 pJ of energy per row <sup>44</sup>. Finally, we consider the number of write/read cycles and arrays required to carry out each operation. For STT-MRAM and RRAM, write and read are needed for two arrays. For our MTM, a reset operation is necessary before a write operation. The simulation parameter is presented in **Extended Data Tab. 2**.

Compared with the RRAM (MRAM) neural network, the MTM neural network features a 76% (77%) reduction of the read energy, an 81% (92%) lower write energy, and a 74% (78%) lower VMM energy for the same amount of margin due to (a) a large AHE signal, (b) low read/write voltages, and (c) the capability to represent both positive and negative weights on a single device. It is worth noting that the current applied for reading and VMM is increased by 10 times to improve the signal-to-noise ratio (SNR) for our MTM neural network. Considering that the AHR of the MTI device using field experiments can reach 10 times of that programmed using SOT switching, the MTM neural network holds great potential for achieving even lower energy consumption and better performance in accelerating machine learning.

### Acknowledgements

The authors at HKUST acknowledge funding support from National Key R&D Program of China (Grants No.2021YFA1401500), Shenzhen-Hong Kong-Macau Science and Technology Program (Category C) (SGDX2020110309460000), NSFC/RGC Joint Research Scheme (No. N\_HKUST620/21), Research Grant Council—Early Career Scheme (Grant No. 26200520), HKUST-Kaisa Joint Research Institute grant (No. OKT21EG08) and Research Fund of Guangdong-Hong Kong-Macao Joint Laboratory for Intelligent Micro-Nano Optoelectronic Technology (Grant No. 2020B1212030010). Y. Liu acknowledges the partial funding support from the HKUST Postdoc Fellowship Matching fund (NA389).

# **Author Contributions**

Q.S. and K.L.W. conceived the experiments. P.Z. grew films, Y.L., Z.R., X.Z. and Z.M. fabricated the device. Y.L., K.Q. and S.C. conducted the electrical measurements. A.L., H.H. and Z.W. performed the simulation. Y.L., A.L. and Q.S. drafted the manuscript and all authors reviewed the manuscript.

# **Competing Interests**

The authors declare that they have no competing financial interests.

### Correspondence

Correspondence and requests for materials should be addressed to Q.S. (email: eeqshao@ust.hk).

# **Extended Figures and Tables**

**Extended Data Fig. 1**. **Temperature and current dependence of AHE**. **a**, The temperature dependence of saturated anomalous Hall resistance of MTI. **b**, The current dependence of anomalous Hall resistance of MTI.

**Extended Data Fig. 2. Memristive behavior of MTI. a**, The write error distribution of MTI collected from statistical data of different write currents. **b**, The reading error distribution of MTI. **c**, The read discrepancy of MTI at different magnetization states using the same read current. The inset shows the test scheme, where a reset pulse ( $-10^{6}$  A/cm<sup>2</sup>), a writing pulse, and multiple reading pulses with increasing amplitude are applied in sequence. **d**, The reading discrepancy error distribution of MTI using different reading currents. The data is collected from reading current ranging from  $2 \times 10^{4}$  A/cm<sup>2</sup> to  $4 \times 10^{4}$  A/cm<sup>2</sup> when the Hall resistance is between -200  $\Omega$  to 200  $\Omega$ .  $\sigma$  denotes the standard deviation error.

**Extended Data Fig. 3. Simulation result of Iris pattern classification**. **a**, The dependence of classification accuracy on the training epoch. **b**, The dependence of accuracy on the reading noise of MTM. The accuracy is averaged from 100 trials.

**Extended Data Fig. 4. Scheme of MNIST image recognition with the MTM neural network**. The left figure shows the diagram of the inference test. The right figure shows that the software-trained neural network can achieve an accuracy of 97.59%, while the MTM neural network can achieve 97.58% and 97.3% for the continuous weight distribution and the quantized weight distribution.

**Extended Data Fig. 5**. Simulation results of the serial connection of multiple Hall channels. a, Model and simulation results of a single Hall bar device. U = 10 V. **b**, The calculated Hall voltage  $V_{xy}$  as a function of the terminal voltage. **c**, **e**, Model and simulation results of 3 Hall bar devices with Hall channel connected in serial. U = 10 V. **d**, **f**, The calculated Hall voltage  $V_{xy}$  as a function of the terminal voltage. V<sub>t</sub> is the total Hall voltage of the 3-Hall bar device,  $V_{xy1}$ ,  $V_{xy2}$  and  $V_{xy3}$  are the Hall voltage when each of the devices is connected alone.

**Extended Data Fig. 6. MTM neural network circuit design**. **a**, The schematic of the MTM neural network. The inset shows the structure of the memristor cell. **b**, The waveforms of the MTM neural network during each type of operation. **c**, The schematic description of the VMM operation. The activated bus lines are marked in red, and the inset shows the corresponding electrical connection. **d**, The circuit simulation result of a 3-input VMM operation.

**Extended Data Fig. 7. The schematic of write and read operations of the MTM neural network. a**, The schematic of the write operation. **b**, The schematic of the read operation. The inset shows the connection to each bit line of the selected and unselected devices.

**Extended Data Fig. 8. Model and experimental verification of anomalous Hall current (AHC). a**, Model and simulation result of the single Hall bar, where the color represents the voltage potential. U = 5V. **b** and **c**, The lateral current as a function of magnetization and longitudinal voltage U, respectively. **d**, The hysteresis of a MTI sample. The inset shows a picture of the device. **e**, Experimental setup of measuring anomalous Hall voltage (AHV) and AHC. We apply a longitudinal voltage U<sub>1</sub>, and keep the voltage of the red spot to be zero by adjusting the U<sub>2</sub>. **f**, AHV and AHC as a function of U<sub>1</sub>.

**Extended Data Fig. 9. Equivalent circuit model of parallel connected Hall bar device and simulation verification**. **a**, Equivalent circuit model of parallel connected Hall bar devices. Each Hall bar device is treated as a voltage source with an EMF of Vn and internal resistance of  $R_{sy}$ . **b**, Device model of three-Hall bar device with the Hall channel connect in parallel in COMSOL. **c**, Simulation verification of the Hall current summation. The plot shows the lateral current as a function of the terminal voltage, where  $I_t$  is the total current output of the three-Hall bar.  $I_1$ ,  $I_2$  and  $I_3$  are the Hall current when each of the devices is connected alone.

| 14nm CMOS, 784x10 Array<br>100nm device | RRAM/PCM | MRAM    | MTM     |

|-----------------------------------------|----------|---------|---------|

| Energy/Read                             | 0.54 pJ  | 0.58 pJ | 0.13 pJ |

| Energy/Write                            | 1.18 pJ  | 2.8 pJ  | 0.22pJ  |

| Energy/neural network Op                | 2.61nJ   | 3.19 nJ | 0.69 nJ |

Extended Data Table 1. Array performance of different VMM.

|                                    | Circuit level                   |               |                                        |               |  |  |  |  |

|------------------------------------|---------------------------------|---------------|----------------------------------------|---------------|--|--|--|--|

| Symbol                             | Description                     |               | Value                                  |               |  |  |  |  |

| $N_{BL}$                           | BL Length                       |               | 784                                    |               |  |  |  |  |

| $N_{WL}$                           | WL Length                       |               | 10                                     |               |  |  |  |  |

| f                                  | Operating Frequency             |               | 100 MHz                                |               |  |  |  |  |

| $V_{DD}$                           | Supply Voltage                  |               | 0.85 V                                 |               |  |  |  |  |

| $C_{BL}$                           | BL Capacitance/Cell             |               | 0.2 fF                                 |               |  |  |  |  |

| $C_{WL}$                           | WL Capacitance/Cell             |               | 0.4 fF                                 |               |  |  |  |  |

| $E_{SA}$                           | Sense Amplifier Energy          |               | 10 fJ                                  |               |  |  |  |  |

| $E_{ADC}$                          | Analog-Digital Converter Energy |               | 1.2 pJ                                 |               |  |  |  |  |

| $E_{WL}$                           | WL Decoder energy               |               | 1 fJ                                   |               |  |  |  |  |

| E <sub>WLD</sub>                   | BL driver chain energy          |               | 10 fJ                                  |               |  |  |  |  |

| Device level                       |                                 |               |                                        |               |  |  |  |  |

| Symbol                             | Description                     | RRAM          | STT MRAM                               | MTM           |  |  |  |  |

| w, l                               | Width and Length                | 50 nm         | 100 nm                                 | 100 nm×100 nm |  |  |  |  |

| R <sub>ON</sub> , R <sub>OFF</sub> | On and Off Resistance           | 10 kΩ, 100 kΩ | $4 \text{ k}\Omega, 8 \text{ k}\Omega$ | -             |  |  |  |  |

| $R_{XX}$ , $R_{YY}$                | X, Y direction Resistance       | -             | -                                      | 10 kΩ, 10 kΩ  |  |  |  |  |

| $R_{XY}$                           | Hall Resistance                 | -             | -                                      | 1 kΩ          |  |  |  |  |

| V <sub>Write</sub>                 | Write Voltage                   | 1.6 V         | 1.5 V                                  | 0.05 V        |  |  |  |  |

| R <sub>Read</sub>                  | Read Voltage                    | 0.7 V         | 0.3 V                                  | 0.1 V         |  |  |  |  |

Extended Data Table 2. Parameters for the circuit simulation.