# Electron-beam lithography of nanostructures at the tips of scanning probe cantilevers

L. Forrer<sup>1,2</sup>, A. Kamber<sup>1</sup>, A. Knoll<sup>3</sup>, M. Poggio<sup>1,2</sup>, and F. R. Braakman<sup>1,2,\*</sup>

1: Department of Physics, University of Basel, 4056 Basel, Switzerland,

2: Swiss Nanoscience Institute, University of Basel, 4056 Basel, Switzerland and

3: IBM Research Europe - Zürich, 8803 Rueschlikon, Switzerland

(Dated: September 26, 2022)

We developed a process to fabricate nanoscale metallic gate electrodes on scanning probe cantilevers, including on the irregular surface of protruding cantilever tips. The process includes a floating-layer technique to coat the cantilevers in electron-beam resist. We demonstrate gate definition through a lift-off process, as well as through an etching process. The cantilevers maintain a high force sensitivity after undergoing the patterning process. Our method allows the patterning of nanoscale devices on fragile scanning probes, extending their functionality as sensors.

#### INTRODUCTION

Cantilevers are widely used in scanning probe microscopy, where they find application as force transducers in e.g. atomic force microscopy, magnetic force microscopy, and kelvin probe microscopy [1]. These cantilevers are usually optimized for mechanical properties [2], and include only simple tip design features. Integration of more advanced sensors on cantilever tips would allow the combination of extremely sensitive detectors such as superconducting quantum interference devices [3], single-electron transistors and quantum dot devices [4, 5], and other quantum sensors with the navigational toolbox that scanning probe microscopy cantilevers provide. Such advanced devices typically require patterning of multiple metallic or superconducting gate and contact electrodes of nanoscale dimensions.

Electron beam lithography (EBL) is a widespread technique to pattern nanoscale structures, such as gate electrodes. EBL can achieve high patterning resolution, in practice resulting in smallest feature sizes of  $\sim 10 \,\mathrm{nm}$  [6]. Moreover, EBL enables batch production and many standard recipes have been previously developed, facilitating a fast fabrication development process and high device yield. Typically, in EBL, a planar substrate is first spincoated with a resist, which is subsequently irradiated with electrons, developed, and processed further. However, spin-coating of small samples and substrates with non-flat surfaces does not provide a resist layer of acceptable uniformity, due to effects such as edge-beading, liftoff problems, and imperfect pattern transfer. Nonetheless, there are many applications where EBL on such irregular substrates would be of interest.

Various other techniques of coating such substrates with a resist layer exist, including spray coating [7], the use of ice resists [8], evaporative methods [9], and resist transfer techniques [10–12]. Furthermore, focused-ion or electronbeam deposition [13] and milling methods can be used to pattern irregular substrates. However, these techniques are either slow, expensive, only demonstrated for photoresist, or are not tailored towards patterning on fragile substrates, such as scanning probe microscopy cantilevers, which are vulnerable suspended structures with a length typically of the order of  $100 \,\mu\text{m}$  and width and thickness of only a few  $\mu\text{m}$ .

Based on an approach used for patterning on flakes of 2D materials [14], we developed a fabrication process to pattern nanoscale structures on prefabricated cantilevers through EBL. The process involves coating the cantilever with an electron-beam resist using a floatinglayer method. We fabricate metallic gates on various cantilever geometries, including on sloped and tipped parts of the cantilevers. We demonstrate two methods of gate definition: a lift-off process and an etching process. By employing either a standard electron-beam irradiation dose or a much higher dose, we use a poly(methyl methacrylate) (PMMA) layer either as a (standard) positive resist for the lift-off process, or as a negative resist for the etching process. The process allows us to produce gate arrays with gate width down to 70 nm and pitch down to 90 nm. We have successfully applied the method to pattern different types of cantilevers with good reproducibility.

#### FLOATING PMMA METHOD

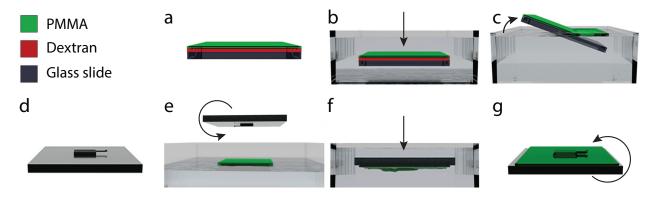

Fig. 1 schematically shows the key steps of our floatinglayer resist coating method. First, a 15% solution of dextran in deionized (DI) water is deposited onto a clean glass slide and spun at 2000 rpm for 40 s. Afterwards, the slide is baked at 150 °C for 3 min. The desired resist layer is then spin-coated on top of the dextran film. For the work shown here, we employ as resist 4.5% PMMA with 950 K molecular weight dissolved in anisole (Allresist AR-P 672.045). The PMMA is spun at 4000 rpm for 40 s and baked at 150 °C for 3 min, resulting in a resist layer thickness of approximately 230 nm (Fig. 1a). Submerging the prepared slide into DI water for about 15 min causes the dextran film to dissolve (Fig. 1b). After this, the slide is removed from the water, tilted by a small angle, and slowly inserted back into the water. This causes the PMMA to peel off the glass slide and float on the water surface, as illustrated in Fig. 1c.

Next, the desired sample is fixed onto a metal holder. In our case, we use a non-contact atomic force microscopy

Figure 1. Overview of resist-coating process. See main text for a step-by-step description of the process.

cantilever (NanoAndMore ATEC-NC) and fix it to an aluminum square slide with Kapton tape (Fig. 1d). We find that it is beneficial for the adhesion of the resist to the sample to perform UV-ozone plasma treatment for 5 min. To coat the sample with the floating PMMA layer, it is turned upside down (Fig. 1e) and slowly lowered into the floating PMMA until the sample is fully submerged, as shown in Fig. 1f. The sample is then removed from the water at a small angle. To remove residual water, the sample is first dried with tissues, followed by a baking step at 150 °C for 3 min. This results in a sample which is coated by a uniform layer of PMMA (Fig. 1g), with minimal wrinkles or bubbles.

In the next sections, we use this method of resist transfer to demonstrate EBL patterning of gate electrodes using a lift-off process, as well as using an etching process. The lift-off process is an additive technique, where a thin metallic layer is deposited on top of the patterned and developed positive resist. In a next step, the resist is washed away in a solvent, leaving deposited material only in the areas where the resist was exposed. This technique is useful when etching or metallization can damage parts of the substrate material, for instance when producing electrical contacts to semiconductor nanostructures or fragile 2D materials. The etching process is a subtractive technique, where a thin metallic layer is deposited onto the sample prior to deposition of the resist. The negative resist is then patterned and developed, after which the deposited layer is etched away only where the resist is not exposed. Such an etching process avoids problems associated with lift-off, such as retention of residual resist and deposited material in unwanted areas of the substrate, and can produce finer structures than possible through lift-off.

# GATES ON CANTILEVERS - LIFT-OFF PROCESS

In order to define gates using the lift-off process, we first structure the non-contact AFM cantilever using focused ion beam (FIB) milling. Originally, the slope of the AFM

tip with respect to the main cantilever surface is 54.7°, resulting from the anisotropic KOH etching of silicon used to fabricate the cantilevers. We succesfully cover cantilevers with such large slope angles with PMMA and perform EBL showing good pattern transfer after development. However, with these large slope angles, we find that the lift-off process does not fully remove the unexposed parts of the resist in the tip area. To improve lift-off, we therefore prestructure the tip by milling away part of it, adjusting its slope to  $\sim 30^{\circ}$  (see inset Fig. 3a). We also mill away selective parts of the tip in this step, resulting in a flat mesa at the top of the tip (see Fig. 2a), which is used as a platform to host a set of parallel gate electrodes. Note that structuring the cantilever tip area can be done already during cantilever fabrication, allowing to mass-produce cantilevers with the required tip geometry.

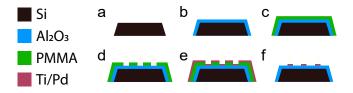

Before fabricating the gates, we use atomic layer deposition (ALD) to cover the cantilever with a 60 nm thick layer of  $Al_2O_3$  (Fig. 2b), which later acts as an insulating layer between the metallic gates and the highly doped silicon cantilever body. Using the floating-layer method described before, we then coat cantilevers with PMMA (Fig. 2c). Here, we coat the cantilevers with three layers of 950K PMMA resist, each spun at 4000 rpm for 40 s and baked at 150 °C for 3 min leading to a total resist thickness of roughly 690 nm. We align on characteristic points of the cantilevers to define the markers

Figure 2. Protocol of gate patterning through lift-off process. (a) Side view of the prepatterned flat mesa on a cantilever tip, (b) mesa is covered with dielectric layer using ALD, (c) floating PMMA transfer, (d) definition of gate pattern through EBL, (e) electron beam evaporation of Ti/Pd, (f) lift-off yields the desired nanostructures.

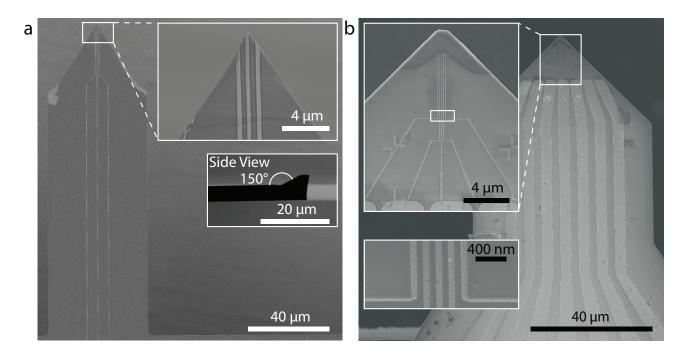

Figure 3. Scanning electron micrographs of cantilevers with gates produced through lift-off process. (a) Tipped cantilever with three Ti/Pd gates. Insets: zoom-in of tip area (top) and side view of cantilever tip part (bottom). (b) Flat cantilever with seven large Au gates connected to five finer Ti/Pd gates in the front part of the cantilever. Insets: zoom-ins of front of cantilever, showing finer gates. Note that the marker structures seen here are deposited together with the finer gates, and are used for subsequent lithography not discussed here. Bottom inset is zoom-in of area delineated by white box in top inset. Note that focussing of the electron beam on specific cantilever parts for alignment purposes results in selective additional metallization, such as the rectangular piece on the right side of the cantilever in b).

(Ti/Au, 5 nm/50 nm) in a first standard EBL step. A second EBL step is employed to define the gate patterns (Fig. 2d), using the predefined markers. The resist is exposed using an acceleration voltage of 30 kV and a dose of  $375 \,\mu\text{C}\,\text{cm}^{-2}$ , followed by development in isopropyl alcohol (IPA) : methyl isobutyl ketone (MIBK) (3:1) for 60 s and IPA for 60 s. Afterwards, 5 nm Ti and 25 nm Pd are deposited using an electron beam evaporator (Fig. 2e). For lift-off, the sample is submerged in acetone for at least 1 h at  $50 \,^{\circ}\text{C}$  (Fig. 2f).

Fig. 3 shows scanning electron micrographs of cantilevers patterned with gates using our method. In Fig. 3a, the tip is modified using FIB milling, as described. Three gates with a width of 350 nm and pitch of 400 nm are fabricated on the cantilever, including on the sloped tip area. For Fig. 3b, we use one layer of resist (230 nm) and pattern five nanoscale gates (width: 70 nm, pitch: 90 nm) on a flat cantilever. The nanoscale gates are patterned such that they connect to larger, prefabricated, contacts which widen out to bondpads on the cantilever base.

## GATES ON CANTILEVERS - ETCHING PROCESS

In order to be able to fabricate gates on cantilever tips with higher slopes, we developed an etching process

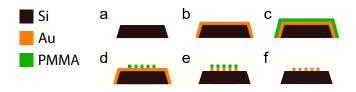

Figure 4. Protocol of gate patterning through etching process. (a) Side view of the prepatterned flat mesa on a cantilever tip, (b) electron beam evaporation of Au, (c) floating PMMA transfer, (d) gates are patterned using overdosing of PMMA, (e) argon ion beam etching transfers the pattern into the Au layer, (f) the resist is removed using oxygen reactive ion etching, yielding the desired nanostructures.

which does not require a lift-off step, thus avoiding problems due to incomplete material lift-off. By overdosing the same type of PMMA as before, it can be used as a negative resist [15] and act as a mask for pattern transfer through subsequent etching. This process is therefore complementary to the one described before and more suitable for removing large parts of a metallic film.

Fig. 4 schematically shows our top-down fabrication strategy to fabricate on a steep slope, as for example on the 54.7° slope of commercially available tipped cantilevers. As before, we start with such a cantilever where a mesa is cut using FIB (Fig. 4a), to host the nanoscale

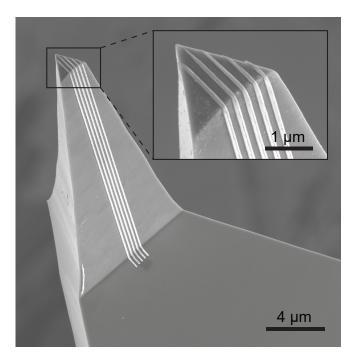

Figure 5. Scanning electron micrograph of tipped end of cantilever, patterned with gate array defined through etching process.

gates at the end of the cantilever tip. Next, 20 nm of Au is deposited using an electron-beam evaporator (Fig. 4b). As shown in the work of Cai et al. [15], overdosing a conventionally positive PMMA resist allows to use it as a negative resist. To coat our lever, we use the technique described in Fig. 1 (Fig. 4c). Next, the PMMA layer is exposed to electron beam radiation at a high dose of  $80\,000\,\mu\mathrm{C\,cm^{-2}}$  using an acceleration voltage of  $30\,\mathrm{kV}$ . Afterwards, the sample is developed in acetone for 10 min and in IPA for 2 min (Fig. 4d). Then, argon ion beam etching (60 s at  $0^{\circ}$  angle and 60 s at 40° angle, 500 V, 20 mA) is used to transfer the pattern of the negative PMMA resist to the Au film (Fig. 4e). The last step of the process is to remove the overexposed PMMA, which is done by using oxygen reactive ion etching for 10 min at 120 W (Fig. 4f). Fig. 5 shows a scanning electron micrograph of a cantilever patterned using the described etching process. Five gates of 100 nm width and 180 nm pitch are fabricated on the tipped end of the cantilever featuring the original 54.7° slope.

# MECHANICAL PROPERTIES

For the cantilevers to maintain their function as sensitive scanning probe force transducers, it is important that their mechanical properties remain unaffected by the lithography processes. To evaluate this, we measure (in high vacuum, at room temperature) the resonance frequency and quality factor of the first flexural mode of a cantilever, before and after processing. We measure the quality factor using a ringdown method. Before processing, we measure a tipped cantilever with a quality factor of 80 k and a resonance frequency of 306.8 kHz. Next, we test the effect of our floating PMMA coating and liftoff process, first without any metal deposition. Here, we find no significant change in resonance frequency or quality factor. Finally, we measure after performing the lift-off process, this time with deposition of 5 nm Ti and 25 nm Pd gates, as in Fig. 3a. Now, the resonance frequency is decreased to 301.4 kHz and the quality factor to 70 k. The decrease of the resonance frequency is expected due to the higher mass of the cantilever. The decrease in quality factor results in a modest decrease of thermal force sensitivity by <15%.

## OUTLOOK

In future work, the resolution of the gate patterns could be improved by the use of thinner PMMA layers, or by etching down the developed PMMA layer before pattern transfer [15]. An interesting use of our method would be to pattern superconducting devices, such as superconducting quantum interference devices [3] or charge qubits [16] of small dimensions, on cantilever tips. This would enable sensitive imaging of nanoscale magnetic fields and charge dynamics with high resolution, for instance in 2D materials [17] or qubit devices [18]. Finally, although not tested here, our method could be used to perform EBL on various other types of samples with irregular surfaces, e.g. to pattern nanostructures on the facets of cleaved optical fibers.

#### ACKNOWLEDGEMENTS

We thank Ute Drechsler, Nadine Leisgang, and Marcus Wyss for helpful discussions and technical support. We acknowledge the support of the Swiss National Science Foundation via the NCCR SPIN, the Canton Aargau, and the European Commission under H2020 FET Open grant "FIBsuperProbes" (Grant No. 892427).

- [1] E. Meyer, R. Bennewitz, H. Hug, *Scanning probe microscopy, Second edition* (Springer, 2021).

- [2] F. Giessibl, Rev. Mod. Phys. 75, 949 (2003).

- [3] M. Wyss, K. Bagani, D. Jetter, E. Marchiori, A. Vervelaki, B. Gross, J. Ridderbos, S. Gliga, C. Schönenberger, and M. Poggio, *Phys. Rev. Appl.* **17**, 034002 (2022).

- [4] I. Khivrich and S. Ilani, Nat. Commun. 11, 2299 (2020).

- [5] M. Yoo, T. Fulton, H. Hess, R. Willett, L. Dunkleberger, R. Chichester, L. Pfeiffer, and K. West, *Science* **276**, 579 (1997).

- [6] C. Vieu, F. Carcenac, A. Pepin, Y. Chen, M. Mejias, A. Lebib, L. Manin-Ferlazzo, L. Couraud, H. Launois, *Appl. Surf. Sci.* 164, 111 (2000).

- [7] J. Linden, C. Thanner, B. Schaaf, S. Wolff, B. Lägel, and E. Oesterschulze, *Microelectron. Eng.* 88, 2030 (2011).

- [8] A. Han, A. Kuan, J. Golovchenko, D. Branton, Nano Lett. 12, 1018 (2012).

- [9] J. Zhang, C. Con, and B. Cui ACS Nano 8, 3483 (2014).

- [10] M. Nilsen, F. Port, M. Roos, K. Gottschalk, and S. Strehle, J. Micromech. Microeng. 29, 025014 (2019).

- [11] J. Chang, Q. Zhou, and A. Zettl, Appl. Phys. Lett. 105, 173109 (2014).

- [12] H. Zhou, B. K. Chong, P. Stopford, G. Mills, A. Midha, L. Donaldson, and J. M. R. Weaver, *J. Vac. Sci. Technol. B* 18, 3594 (2000).

- [13] M. Jaafar, J. Pablo-Navarra, E. Berganza, P. Ares, C. Magén, A. Masseboeuf, C. Gatel, E. Snoeck, J. Gómez-Herrero, J. de Teresa, and A. Asenjo, *Nanoscale* 12, 10090 (2020).

- [14] N. M. Leisgang, Doctoral dissertation (2021).

- [15] H. Cai, K. Zhang, and X. Yu, AIP Adv. 5, 117216 (2015).

- [16] B. Jäck, Phys. Rev. Research 2, 043031 (2020).

- [17] E. Marchiori, L. Ceccarelli. N. Rossi, L. Lorenzelli, C. Degen, and M. Poggio, *Nat. Rev. Phys.* 4, 49 (2021).

- [18] E. Marchiori, L. Ceccarelli. N. Rossi, G. Romagnoli, J. Herrmann, J. Besse, S. Krinner, A. Wallraff, and M. Poggio,, *Appl. Phys. Lett.* **121**, 052601 (2022).