### **NATIONAL TECHNICAL UNIVERSITY OF ATHENS** School of Electrical and Computer Engineering Division of Informatics and Computer Technology

### Accelerating Irregular Applications via Efficient Synchronization and Data Access Techniques

**Doctoral Dissertation**

### CHRISTINA GIANNOULA

NATIONAL TECHNICAL UNIVERSITY OF ATHENS School of Electrical and Computer Engineering Division of Informatics and Computer Technology

### Accelerating Irregular Applications via Efficient Synchronization and Data Access Techniques

**Doctoral Dissertation**

#### CHRISTINA GIANNOULA

Advisory Committee:

Georgios Goumas Nectarios Koziris Onur Mutlu

Accepted by the seven-member committee on 27/09/2022.

.....

Georgios Goumas Associate Professor NTUA

Dionisios Pnevmatikatos Professor NTUA

Dimitris Gizopoutos

Professor University of Athens

Churs Mutter . . . . . . . . . . . .

Onur Mutlu Professor ETH Zurich

Stefanos Kaxiras

Nectarios Koziris

Profesor NTUA

Professor Nppsala University

Vasileios Papaelstathiou Assistant Professor University of Crete

Athens, September 2022

. . . . . . . . . . . .

#### CHRISTINA GIANNOULA

Doctor of Electrical and Computer Engineer, NTUA

Copyright © CHRISTINA GIANNOULA, 2022 All rights reserved.

Copying, storage and distribution of this work, in whole or part of it, is prohibited for commercial purposes. Reproduction, storage and distribution for the purpose of non-profit, educational or research nature, is allowed provided that the source of origin is mentioned and the copyright message is maintained. Questions concerning the use of this work for commercial purposes should be addressed to the author.

The views and conclusions contained in this document reflect the author and should not be interpreted as representing the official position of the National technical University of Athens.

Το my loving parents, Maria and Christoforos. Στους αγαπημένους μου γονείς, Μαρία και Χριστόφορο.

# Acknowledgments

This doctoral thesis is the culmination of five and half years of hard work throughout my PhD studies. My PhD journey was a significant source of learning and growth for me both professionally and personally. There have been many who have supported me and contributed in different ways. These acknowledgments comprise a brief and humble attempt to thank their invaluable contributions.

First and foremost, I wholeheartedly thank my advisors, Prof. Georgios Goumas, Prof. Nectarios Koziris, and Prof. Onur Mutlu. I am very grateful to Prof. Georgios Goumas for helping me to find and follow a very interesting research direction for me, supporting and advising me with great patience and tolerance, motivating me to work on the fields of high-performance computing and computer architecture and providing me a very comfortable, safe and stimulating environment to grow. I also thank him for being open to my collaborations with researchers from other institutions. I am extremely grateful to Prof. Onur Mutlu for his generous guidance, resources and opportunities which constitute the key to my professional growth, success and research achievements. I thank him for giving me the invaluable opportunity to work with him and his research group, providing rigorous feedback to my paper submissions and talks, teaching me how to think critically, write comprehensively, and perform impactful research. His motivation for top-notch research and his passion for excellence were a constant source of inspiration and have significantly shaped my research mindset and personality. I am grateful to Prof. Nectarios Koziris for giving the opportunity to be a member of his research laboratory, inspiring me with his incredible passion for teaching and working in the field of computer architecture, as well as his continuous support and the encouraging environment he has provided. My advisors' influence and constant encouragement provided real-life lessons and shaped my personality as a researcher, scientist and engineer.

I thank my committee members, Dionisios Pnevmatikatos, Stefanos Kaxiras, Dimitris Gizopoulos, and Vasileios Papaefstathiou for supervising this thesis. Their feedback and suggestions were valuable to improving my doctoral thesis and its constituent works.

I am grateful to Nandita Vijaykumar for being a great mentor and encouraging me to become a strong and independent researcher. During my visit at the SAFARI research group of ETH Zurich, Nandita helped me to stay motivated, taught me how to find the right research problem to work on and how to perform quality research. I also wholeheartedly thank Athena Elafrou, Foteini Strati, Ivan Fernandez and Thomas Lagos for being my closest collaborators and friends throughout PhD studies, the many long hours of brainstorming and our stimulating discussions. I am very grateful for their endless support, valuable feedback, kindness, positivity, and confidence in myself, as well as our invaluable synergy and friendship.

Furthermore, I thank all the CSLab group members for being great colleagues, supporting my research and enabling a productive working environment. I want to especially thank Kostis Nikas, Vasileios Karakostas, Nikela Papadopoulou and Dimitris Siakavaras for providing significant intellectual and technical support in my research contributions and willingly sharing their expertise with me. I am grateful to all the students and mentees with who I worked closely: Foteini Strati, Athanasios Peppas, and Thrasyvoulos-Fivos Iliadis. Their work significantly helped me in completing my PhD thesis.

I am immensely grateful to all the members of the SAFARI research group for creating a rich, stimulating and highly motivating research environment. During my visit at the SAFARI research group, I realized that innovative research can vastly benefit from close collaboration among the group members. The valuable advice of the SAFARI group members, consisting of concrete guidelines and useful methodologies, helped me to work effectively and efficiently and stay focused in tackling my research obstacles. I want to especially thank Juan Gomez-Luna, Lois Orosa, Konstantinos Kanellopoulos and Nika Mansouri-Ghiasi for their rigorous feedback and criticism on my progress and research, their friendship, their technical and intellectual suggestions, as well as for generously sharing their deep knowledge on the field of computer architecture with me.

I gratefully acknowledge financial support from my PhD scholarships. Specifically, it was a great honor for me to receive a PhD Fellowship (October 2017 - March 2020) from the General Secretariat for Research and Technology (GSRT) and the Hellenic Foundation for Research and Innovation (HFRI) and a PhD award (September 2021 - October 2022) funded by the Foundation for Education and European Culture (IPEP).

I am immensely grateful to my friends for their support, companionship and patience. I want to particularly thank Katerina Bogiatzoglou, Konstantina Kada, Vicky Routsi, Orestis Alpos, Stamatios Kourkoutas, Stamatios Anoustis, Artemis Zografou, Marina Gourgioti, Katerina Tsesmeli, Isidora Tourni, Athina Kyriakou, Foteini Strati, and Thomas Lagos for our endless conversations, countless laughs, fun nights out and beautiful trips and excursions that were the best discharge from the hard work that I did during my PhD studies.

Last but not least, I am tremendously blessed and would like to express my profound gratitude to my parents, Maria and Christoforos, and my sister, Chara, for their unconditional love and endless encouragement throughout my PhD journey, as well as their valuable support to pursue my academic dreams. I thank my mother for continuously supporting each and every step of this journey. I thank my father for always believing in myself and for helping me with his optimism to pursue my dreams.

I thank my sister for her valuable support and patience throughout my PhD studies. This dissertation would not be possible without them. I will be forever grateful to my loving family for the dedication, support, patience, love and opportunities they have given me.

### Abstract

Irregular applications comprise an increasingly important workload domain for many fields, including bioinformatics, chemistry, graph analytics, physics, social sciences and machine learning. Therefore, achieving high performance and energy efficiency in the execution of emerging irregular applications is of vital importance. While there is abundant research on accelerating irregular applications, in this thesis, we identify two critical challenges. First, irregular applications are hard to scale to a high number of parallel threads due to high synchronization overheads. Second, irregular applications have complex memory access patterns and exhibit low operational intensity, and thus they are bottlenecked by expensive data access costs.

This doctoral thesis studies the root causes of inefficiency of irregular applications in modern computing systems, and aims to fundamentally address such inefficiencies, by 1) proposing low-overhead synchronization techniques among parallel threads in cooperation with 2) well-crafted data access policies. Our approach leads to high system performance and energy efficiency on the execution of irregular applications in modern computing platforms, both processor-centric CPU systems and memory-centric Processing-In-Memory (PIM) systems.

We make four major contributions to accelerating irregular applications in different contexts including CPU and Near-Data-Processing (NDP) (or Processing-In-Memory (PIM)) systems. First, we design *ColorTM*, a novel parallel graph coloring algorithm for CPU systems that trades off using synchronization with lower data access costs. *ColorTM* proposes an efficient data management technique co-designed with a speculative synchronization scheme implemented on Hardware Transactional Memory, and significantly outperforms prior state-of-the-art graph coloring algorithms across a wide range of real-world graphs. Second, we propose *SmartPQ*, an adaptive priority queue that achieves high performance under all various contention scenarios in Non-Uniform Memory Access (NUMA) CPU systems. *SmartPQ* tunes itself by dynamically switching between a NUMA-oblivious and a NUMA-aware algorithmic mode, thus providing low data access costs in high contention scenarios, and high levels of parallelism in low contention scenarios. Our evaluations show that SmartPQ achieves the highest throughput over prior state-of-the-art NUMA-aware and NUMA-oblivious concurrent priority queues under various contention scenarios and even when contention varies during runtime. Third, we introduce SynCron, the first practical and lightweight hardware synchronization mechanism tailored for NDP systems. SynCron minimizes synchronization overheads in NDP systems by (i) adding low-cost hardware support near memory for synchronization acceleration, (ii) directly buffering the synchronization variables in a specialized cache memory structure, (ii) implementing a hierarchical message-passing communication scheme, and (iv) integrating a hardware-only overflow management scheme to avoid performance degradation when hardware resources for synchronization tracking are exceeded. We demonstrate that SynCron outperforms prior state-of-the-art approaches both in performance and energy consumption using a wide range of irregular applications, and has low hardware area and power overheads. Fourth, we design SparseP, the first library for high-performance Sparse Matrix Vector Multiplication (SpMV) on real PIM systems. SparseP is publicly-available and includes a wide range of data partitioning, load balancing, compression and synchronization techniques to accelerate this irregular kernel in current and future PIM systems. We also extensively characterize the widely used SpMV kernel on a real PIM architecture, and provide recommendations for software, system and hardware designers of future PIM systems.

Overall, we demonstrate that the execution of irregular applications in CPU and NDP/PIM architectures can be significantly accelerated by co-designing lightweight synchronization approaches along with well-crafted data access policies. Specifically, we show that efficient synchronization and data access techniques can provide high amount of parallelism, low-overhead inter-thread communication and low data access and data movement costs in emerging irregular applications, thus significantly improving system performance and system energy. This doctoral thesis also bridges the gap between processor-centric CPU systems and memory-centric PIM systems in the critically-important area of irregular applications. We hope that this dissertation inspires future work in co-designing software algorithms with cutting-edge computing platforms to significantly accelerate emerging irregular applications.

**Keywords:** Irregular Applications, Synchronization, Efficient Data Access Techniques, Multicore Systems, Processing-In-Memory Architectures

## Contents

| 1 | Intr | oductio | on                                                                            | 27 |

|---|------|---------|-------------------------------------------------------------------------------|----|

|   | 1.1  | Motiva  | ation: Excessive Synchronization and High Memory Intensity Degrade the Ex-    |    |

|   |      | ecutio  | n of Irregular Applications                                                   | 28 |

|   | 1.2  | Our A   | pproach: Efficient Synchronization and Data Access Techniques for Irregular   |    |

|   |      | Applic  | cations                                                                       | 31 |

|   |      | 1.2.1   | Thesis Statement                                                              | 33 |

|   | 1.3  | Overv   | iew of Our Research                                                           | 33 |

|   |      | 1.3.1   | ColorTM [1–3]: High-Performance and Balanced Parallel Graph Coloring on       |    |

|   |      |         | Multicore CPU Platforms (Chapter 2)                                           | 33 |

|   |      | 1.3.2   | SmartPQ [4]: An Adaptive Concurrent Priority Queue for NUMA CPU Archi-        |    |

|   |      |         | tectures (Chapter 3)                                                          | 34 |

|   |      | 1.3.3   | SynCron [5]: Efficient Synchronization Support for NDP Architectures (Chap-   |    |

|   |      |         | ter 4)                                                                        | 35 |

|   |      | 1.3.4   | SparseP [6–11]: Towards Efficient Sparse Matrix Vector Multiplication on Real |    |

|   |      |         | PIM Architectures (Chapter 5)                                                 | 36 |

|   | 1.4  | Contri  | butions                                                                       | 37 |

|   | 1.5  | Outlin  | e                                                                             | 39 |

| 2 | Colo | orTM    |                                                                               | 41 |

|   | 2.1  | Overv   | iew                                                                           | 41 |

|   | 2.2  | Prior ( | Graph Coloring Algorithms                                                     | 44 |

|   |      | 2.2.1   | The Greedy Algorithm                                                          | 44 |

|   |      | 2.2.2   | Prior Parallel Graph Coloring Algorithms                                      | 44 |

|   |      |         | The SeqSolve Algorithm                                                        | 45 |

|   |             |         | The IterSolve Algorithm                              | 46         |

|---|-------------|---------|------------------------------------------------------|------------|

|   |             |         | The IterSolveR Algorithm                             | 47         |

|   |             | 2.2.3   | Prior Balanced Graph Coloring Algorithms             | 48         |

|   |             |         | The Color-Centric (CLU) Algorithm                    | 49         |

|   |             |         | The Vertex-Centric (VFF) Algorithm                   | 50         |

|   |             |         | The Recoloring Algorithm                             | 51         |

|   | 2.3         | ColorT  | M: Overview                                          | 53         |

|   |             | 2.3.1   | Speculative Computation and Synchronization          | 53         |

|   |             | 2.3.2   | Eager Coloring Conflict Detection and Resolution     | 54         |

|   | 2.4         | ColorT  | M: Detailed Design                                   | 55         |

|   |             | 2.4.1   | Speculative Synchronization via HTM                  | 55         |

|   |             | 2.4.2   | Critical Adjacent Vertices                           | 58         |

|   |             | 2.4.3   | Implementation Details                               | 59         |

|   |             | 2.4.4   | Progress and Correctness                             | 61         |

|   |             | 2.4.5   | The <i>BalColorTM</i> Algorithm                      | 63         |

|   | 2.5         | Evaluat | tion Methodology                                     | 64         |

|   | 2.6         | Evaluat | tion                                                 | 64         |

|   |             | 2.6.1   | Analysis of Parallel Graph Coloring Algorithms       | 64         |

|   |             |         | Analysis of the Coloring Quality                     | 65         |

|   |             |         | Performance Comparison                               | 66         |

|   |             |         | Analysis of <i>ColorTM</i> Execution                 | 69         |

|   |             | 2.6.2   | Analysis of Balanced Graph Coloring Algorithms       | 72         |

|   |             |         | Analysis of Color Balancing Quality                  | 72         |

|   |             |         | Performance Comparison                               | 73         |

|   |             |         | Analysis of <i>BalColorTM</i> Execution              | 77         |

|   |             | 2.6.3   | Analysis of a Real-World Scenario                    | 77         |

|   | 2.7         | Recom   | mendations                                           | 81         |

|   | 2.8         | Related | l Work                                               | 82         |

|   | 2.9         | Summa   | ury                                                  | 84         |

| 2 | <b>C</b>    | +100    |                                                      | 85         |

| 3 | <b>3</b> .1 | rtPQ    | ew                                                   | <b>8</b> 5 |

|   | 3.1         |         | Node Delegation ( <i>Nuddle</i> )                    | 88         |

|   | 5.2         | 3.2.1   | Node Delegation ( <i>Nuaule</i> )           Overview | 00<br>88   |

|   |             | 3.2.1   | Implementation Details                               | 00<br>89   |

|   | 2.2         |         | •                                                    |            |

|   | 3.3         |         | Q                                                    | 92<br>02   |

|   |             | 3.3.1   | Selecting the Algorithmic Mode                       | 93<br>02   |

|   |             |         | The Need for a Machine Learning Approach             | 93<br>04   |

|   |             | 0.0.0   | Decision Tree Classifier                             | 94<br>05   |

|   |             | 3.3.2   | Implementation Details                               | 95         |

|   | 3.4 | Experimental Evaluation                             | 97  |

|---|-----|-----------------------------------------------------|-----|

|   |     | 3.4.1 Throughput of <i>Nuddle</i>                   | 98  |

|   |     | 3.4.2 Throughput of <i>SmartPQ</i>                  | )() |

|   |     | Classifier Accuracy                                 | )0  |

|   |     | Varying the Contention Workload                     | )0  |

|   | 3.5 | Discussion and Future Work                          | )3  |

|   | 3.6 | Recommendations                                     | )3  |

|   | 3.7 | Related Work                                        | )4  |

|   | 3.8 | Summary                                             | )5  |

|   |     |                                                     | _   |

| 4 | Syn |                                                     |     |

|   | 4.1 | Overview                                            |     |

|   | 4.2 | Background and Motivation                           |     |

|   |     | 4.2.1 Baseline Architecture                         |     |

|   |     | 4.2.2 The Solution Space for Synchronization        |     |

|   |     | Synchronization via Shared Memory                   |     |

|   |     | Message-passing Synchronization                     |     |

|   | 4.3 | <i>SynCron</i> : Overview                           |     |

|   |     | 4.3.1 Overview of <i>SynCron</i>                    | 3   |

|   |     | 4.3.2 <i>SynCron</i> 's Operation                   | 4   |

|   | 4.4 | SynCron: Detailed Design                            | 5   |

|   |     | 4.4.1 Programming Interface and ISA Extensions      | 5   |

|   |     | Memory Consistency                                  | 6   |

|   |     | Message Encoding                                    | 17  |

|   |     | 4.4.2 Synchronization Engine (SE)                   | 8   |

|   |     | Synchronization Processing Unit (SPU)               | 8   |

|   |     | Synchronization Table (ST)                          | 8   |

|   |     | Indexing Counters                                   | 9   |

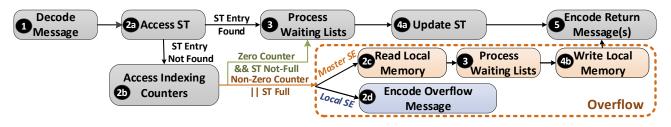

|   |     | Control Flow in SE                                  | 9   |

|   |     | 4.4.3 Overflow Management                           | 9   |

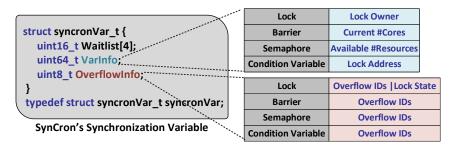

|   |     | SynCron's Synchronization Variable                  | 20  |

|   |     | Communication Protocol between SEs                  | 20  |

|   |     | 4.4.4 SynCron Enhancements                          | 21  |

|   |     | <i>RMW</i> Operations                               | 21  |

|   |     | Lock Fairness                                       | 21  |

|   |     | 4.4.5 Comparison with Prior Work                    | 22  |

|   |     | 4.4.6 Use of <i>SynCron</i> in Conventional Systems |     |

|   | 4.5 | Methodology                                         |     |

|   | 4.6 | Evaluation                                          |     |

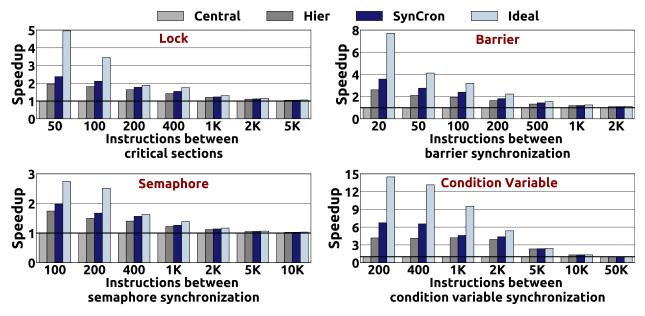

|   |     | 4.6.1 Performance                                   | 26  |

|   |      |               | Synchronization Primitives                                  |

|---|------|---------------|-------------------------------------------------------------|

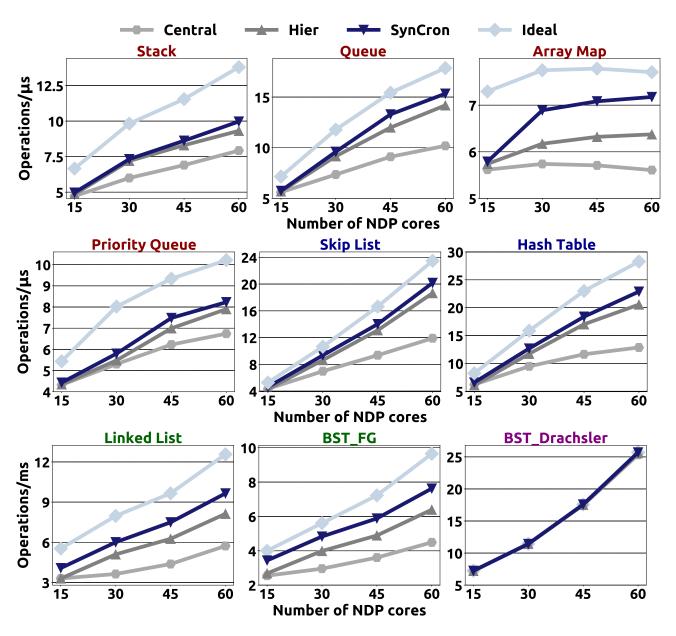

|   |      |               | Pointer-Chasing Data Structures                             |

|   |      |               | Real Applications                                           |

|   |      | 4.6.2         | Energy Consumption                                          |

|   |      | 4.6.3         | Data Movement                                               |

|   |      | 4.6.4         | Non-Uniformity of NDP Systems                               |

|   |      |               | High Contention                                             |

|   |      |               | Low Contention                                              |

|   |      | 4.6.5         | Memory Technologies                                         |

|   |      | 4.6.6         | Effect of Data Placement                                    |

|   |      | 4.6.7         | SynCron's Design Choices 132                                |

|   |      |               | Hierarchical Design                                         |

|   |      |               | ST Size                                                     |

|   |      |               | Overflow Management                                         |

|   |      | 4.6.8         | SynCron's Area and Power Overhead                           |

|   | 4.7  | Recom         | mendations                                                  |

|   | 4.8  | Relate        | d Work                                                      |

|   | 4.9  | Summ          | ary                                                         |

| 5 | Spar | rs <i>a</i> D | 139                                                         |

| 3 | 5,1  |               | iew                                                         |

|   | 5.2  |               | round and Motivation                                        |

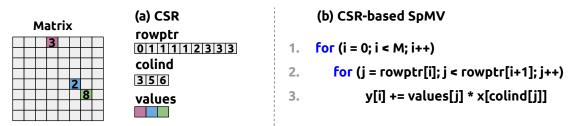

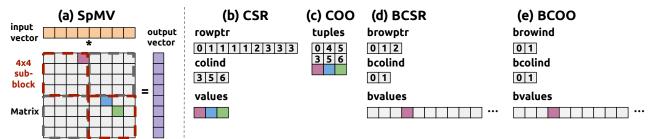

|   | 5.2  | 5.2.1         | Sparse Matrix Vector Multiplication (SpMV)                  |

|   |      | 0.211         | Compressed Matrix Storage Formats                           |

|   |      |               | SpMV in Processor-Centric Systems                           |

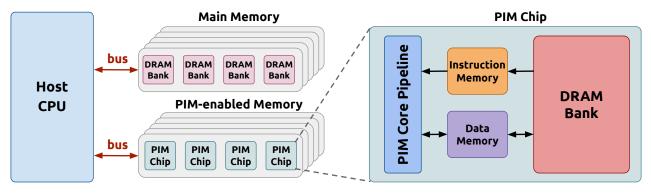

|   |      | 5.2.2         | Near-Bank PIM Systems   145                                 |

|   |      | 0.2.2         | The UPMEM PIM Architecture                                  |

|   | 5.3  | The St        | parseP Library                                              |

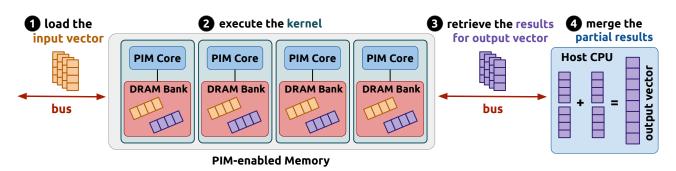

|   |      | 5.3.1         | SpMV Execution on a PIM System                              |

|   |      | 5.3.2         | Overview of Data Partitioning Techniques                    |

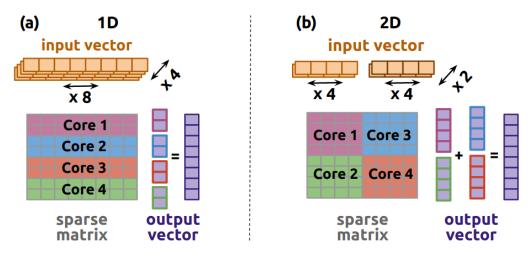

|   |      | 5.3.3         | Parallelization Techniques Across PIM Cores                 |

|   |      |               | 1D Partitioning Technique                                   |

|   |      |               | 2D Partitioning Technique                                   |

|   |      | 5.3.4         | Parallelization Techniques Across Threads within a PIM Core |

|   |      |               | Load Balancing Approaches                                   |

|   |      |               | Synchronization Approaches                                  |

|   |      | 5.3.5         | Kernel Implementation                                       |

|   | 5.4  | Evalua        | tion Methodology                                            |

|   | 5.5  | Analys        | sis of SpMV Execution on One DPU 155                        |

|   |      | 5.5.1         | Load Balancing Schemes Across Tasklets of One DPU           |

|   |      |               | e                                                           |

|   |      | 5.5.2   | Analysis of Compressed Matrix Formats on One DPU                          | 157   |

|---|------|---------|---------------------------------------------------------------------------|-------|

|   | 5.6  | Analy   | sis of SpMV Execution on Multiple DPUs                                    | 159   |

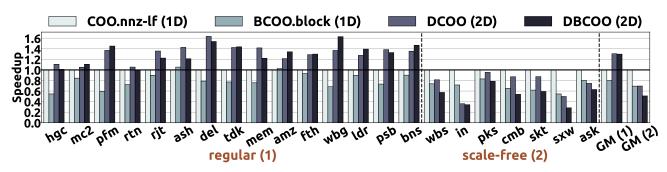

|   |      | 5.6.1   | Analysis of SpMV Execution Using 1D Partitioning Techniques               | 159   |

|   |      |         | Analysis of Kernel Time                                                   | 159   |

|   |      |         | Analysis of End-To-End SpMV Execution                                     | 163   |

|   |      | 5.6.2   | Analysis of SpMV Execution Using 2D Partitioning Techniques               | 165   |

|   |      |         | Sensitivity Studies on 2D Partitioning Techniques                         | 165   |

|   |      |         | Analysis of Compressed Formats                                            | 170   |

|   |      |         | Comparison of 2D Partitioning Techniques                                  | 171   |

|   |      | 5.6.3   | Comparison of 1D and 2D Partitioning Techniques                           | 172   |

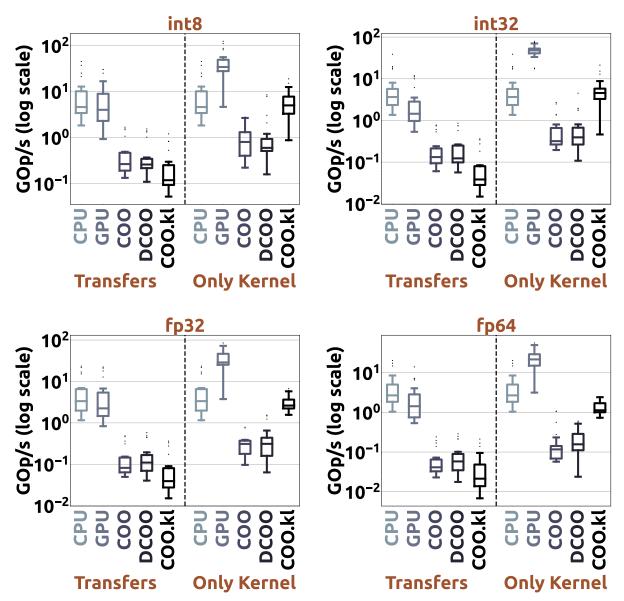

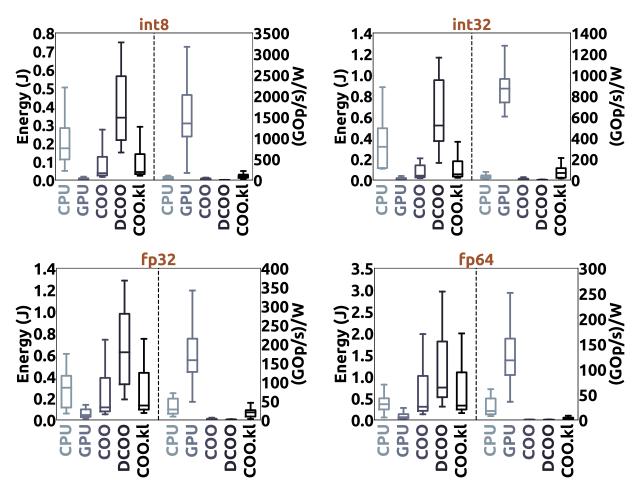

|   | 5.7  | Comp    | arison with CPUs and GPUs                                                 | 174   |

|   |      | 5.7.1   | Performance Comparison                                                    | 174   |

|   |      | 5.7.2   | Energy Comparison                                                         | 176   |

|   |      | 5.7.3   | Discussion                                                                | 177   |

|   | 5.8  | Key Ta  | akeaways and Recommendations                                              | 177   |

|   | 5.9  | Relate  | d Work                                                                    | 179   |

|   | 5.10 | Summ    | ary                                                                       | 181   |

| 6 | Con  | clusior | ns and Future Directions                                                  | 183   |

|   | 6.1  | Future  | Research Directions                                                       | 185   |

|   |      | 6.1.1   | Accelerating Irregular Applications in Unconventional Systems             | 185   |

|   |      | 6.1.2   | Adaptive Algorithmic, System-Level and Hardware-Based Approaches for Ir-  |       |

|   |      |         | regular Applications                                                      | 188   |

|   | 6.2  | Conclu  | uding Remarks                                                             | 190   |

| 7 | Othe | er Wor  | ks of the Author                                                          | 191   |

| 8 | Арр  | endix   | A                                                                         | 193   |

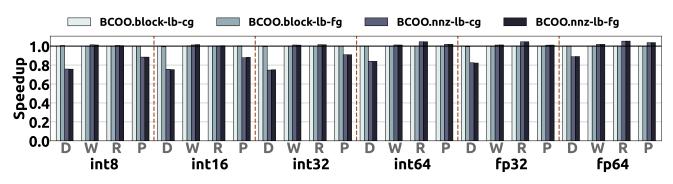

|   | 8.1  |         | ded Results for <i>SparseP</i>                                            | 193   |

|   |      | 8.1.1   | Synchronization Approaches in Block-Based Compressed Matrix Formats       | 193   |

|   |      | 8.1.2   | Fine-Grained Data Transfers in 2D Partitioning Techniques                 |       |

|   |      | 8.1.3   | Effect of the Number of Vertical Partitions Using Two Different UPMEM PIM |       |

|   |      |         | Systems                                                                   | 195   |

|   |      | 8.1.4   | Performance of Compressed Matrix Formats Using 2D Partitioning Techniques | 5 195 |

|   |      | 8.1.5   | Analysis of 1D- and 2D-Partitioned Kernels in Two UPMEM PIM Systems       | 197   |

|   | 8.2  | Arithr  | netic Throughput of One DPU for the Multiplication Operation              | 199   |

|   | 8.3  | The Sp  | parseP Software Package                                                   | 201   |

|   | 8.4  | Large   | Matrix Dataset                                                            | 202   |

|   |      |         |                                                                           |       |

# List of Figures

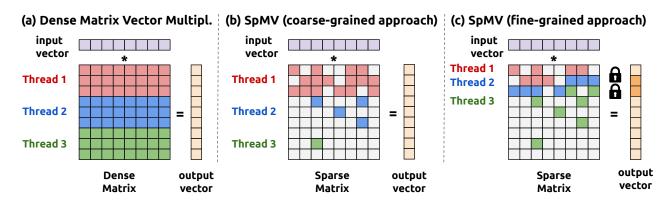

| 1.1  | (a) Dense Matrix Vector Multiplication using three parallel threads. (b) Sparse Matrix     |    |

|------|--------------------------------------------------------------------------------------------|----|

|      | Vector Multiplication with a coarse-grained parallelization strategy among three par-      |    |

|      | allel threads. (c) Sparse Matrix Vector Multiplication with a fine-grained paralleliza-    |    |

|      | tion strategy among three parallel threads. The colored cells of each matrix represent     |    |

|      | non-zero elements.                                                                         | 29 |

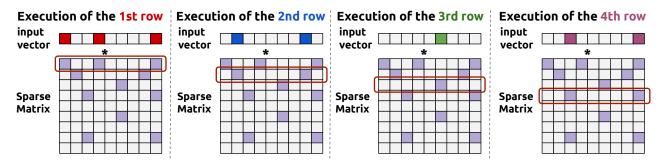

| 1.2  | An example SpMV execution on the first four rows of a sparse $9 \times 9$ matrix with only |    |

|      | 10 non-zero elements. The execution steps are performed at a row granularity. The          |    |

|      | colored cells of the matrix with purple color represent non-zero elements, and the         |    |

|      | colored cells of the input vector represent the elements of the input vector that are      |    |

|      | processed/accessed at each execution step.                                                 | 30 |

| 2.1  | The Greedy algorithm.                                                                      | 44 |

| 2.2  | The SeqSolve algorithm                                                                     | 45 |

| 2.3  | The IterSolve algorithm                                                                    | 46 |

| 2.4  | The IterSolveR algorithm.                                                                  | 48 |

| 2.5  | The CLU algorithm.                                                                         | 49 |

| 2.6  | The VFF algorithm.                                                                         | 50 |

| 2.7  | The Recoloring algorithm.                                                                  | 52 |

| 2.8  | A Naive Approach.                                                                          | 53 |

| 2.9  | <i>ColorTM</i> : Overview                                                                  | 54 |

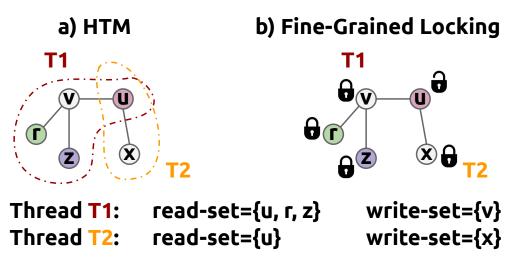

| 2.10 | An example execution scenario in which threads $T1$ and $T2$ attempt to concurrently       |    |

|      | find colors for the vertices $v$ and $x$ , respectively, using a) HTM and b) fine-grained  |    |

|      | locking for synchronization. The white circles represent uncolored vertices, and the       |    |

|      | colorful circles represent vertices that have already obtained a color                     | 56 |

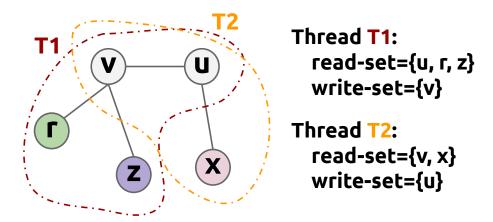

| 2.11 | An example execution scenario in which threads $T1$ and $T2$ attempt to concurrently<br>update the colors of the vertices $v$ and $u$ respectively, using two different transactions,<br>and the HTM mechanism detects read-write conflicts to their data sets. The white<br>circles represent uncolored vertices, and the colorful circles represent vertices that<br>have already obtained a color.                                                                     | 57 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.12 | An example execution scenario in which the graph is partitioned across two parallel threads. The white circles represent uncolored vertices, and the colorful circles represent vertices that have already obtained a color. When the threads $T1$ and $T2$ attempt to color the vertices $v$ and $u$ , respectively, the critical adjacent vertices that need to be validated within the critical section (HTM) are <i>only</i> the vertices $u$ and $v$ , respectively. | 59 |

| 2.13 | The <i>ColorTM</i> algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                             | 60 |

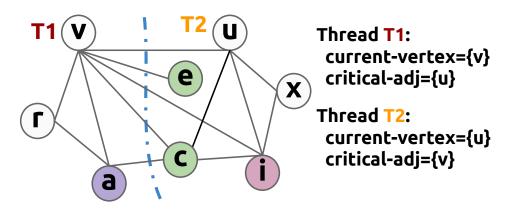

| 2.14 | The <i>BalColorTM</i> algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                          | 62 |

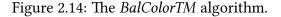

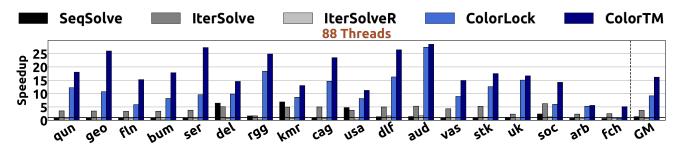

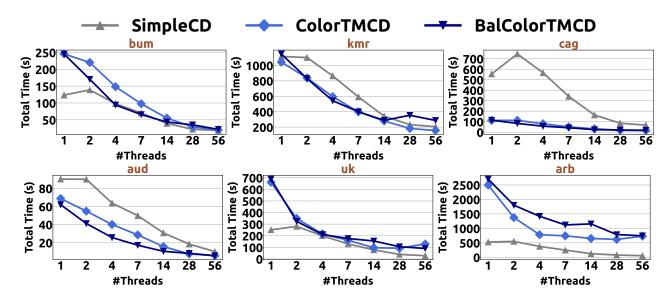

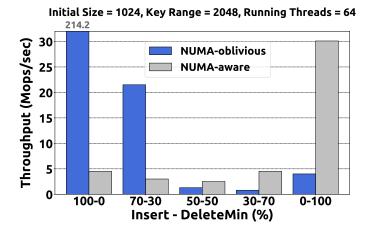

| 2.15 | Scalability achieved by all parallel graph coloring implementations in large real-world graphs.                                                                                                                                                                                                                                                                                                                                                                           | 67 |

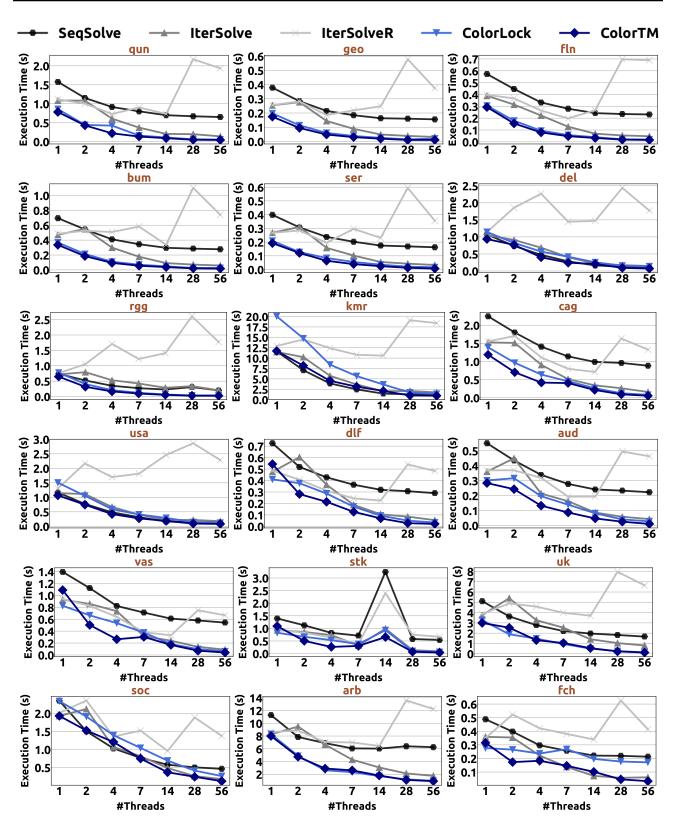

| 2.16 | Speedup achieved by all parallel graph coloring implementations over the sequential Greedy scheme in large real-world graphs using all cores of one socket (14 threads), all cores of two sockets (28 threads), and the maximum hardware thread capacity of our machine with hyperthreading enabled (56 threads).                                                                                                                                                         | 68 |

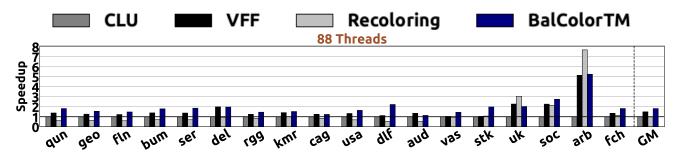

| 2.17 | Speedup achieved by all parallel graph coloring implementations over the sequen-<br>tial Greedy scheme in large real-world graphs using the maximum hardware thread<br>capacity of an Intel Broadwell server with hyperthreading enabled (88 threads)                                                                                                                                                                                                                     | 69 |

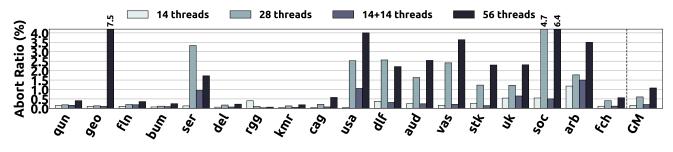

| 2.18 | Abort ratio exhibited by <i>ColorTM</i> in all large real-world graphs.                                                                                                                                                                                                                                                                                                                                                                                                   | 70 |

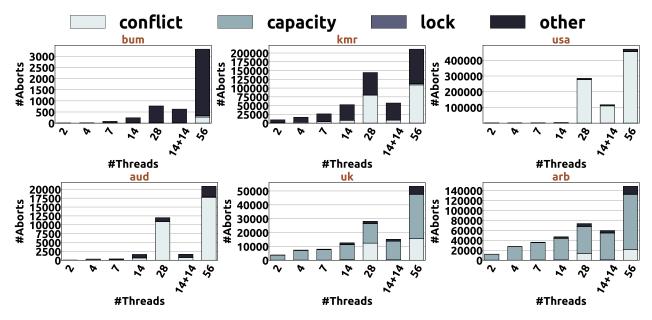

| 2.19 | Breakdown of different types of aborts exhibited by <i>ColorTM</i> in real-world graphs                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

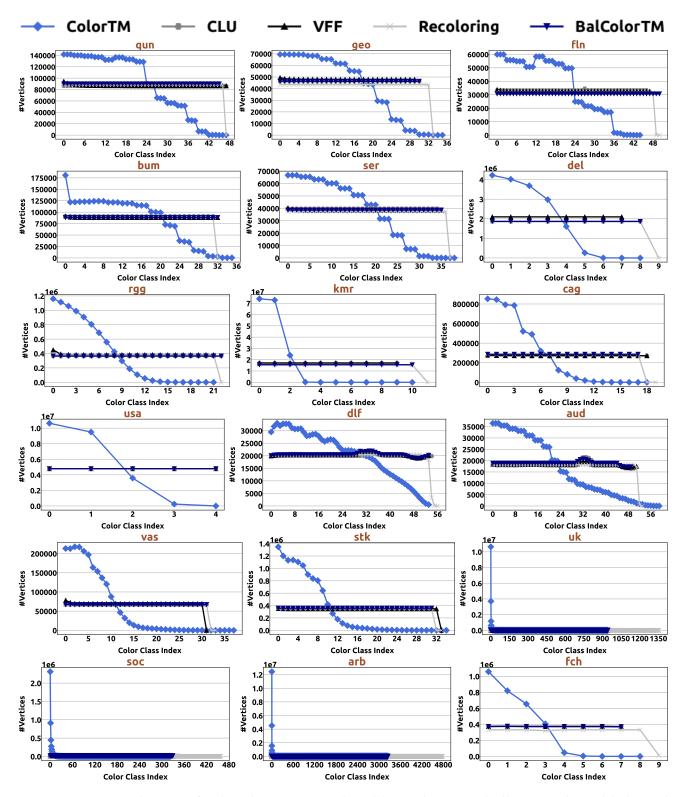

| 2.20 | Distribution of color class sizes produced by <i>ColorTM</i> and all our evaluated balanced graph coloring schemes. Note that small color class sizes result in reduced parallelism in the real-world end-application.                                                                                                                                                                                                                                                    | 74 |

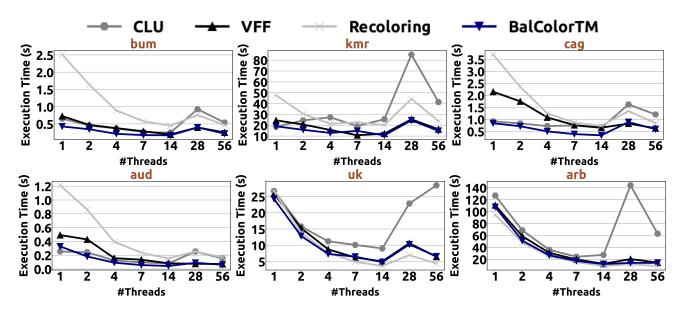

| 2.21 | Scalability achieved by all balanced graph coloring implementations in large real-<br>world graphs.                                                                                                                                                                                                                                                                                                                                                                       | 75 |

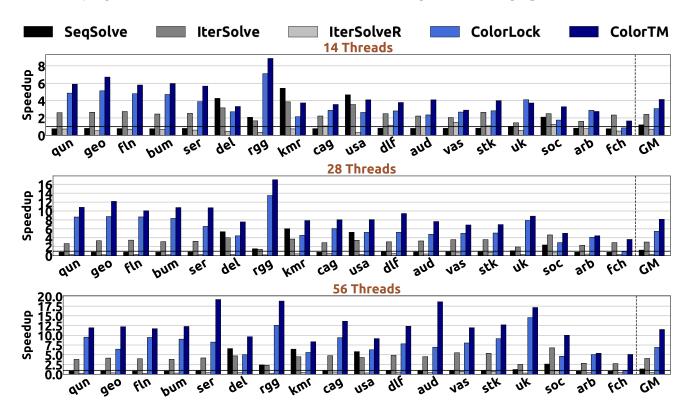

| 2.22 | Speedup achieved by all balanced graph coloring implementations over the CLU scheme<br>in large real-world graphs using all cores of one socket (14 threads), all cores of two<br>sockets (28 threads), and the maximum hardware thread capacity of our machine with<br>hyperthreading enabled (56 threads).                                                                                                                                                              | 76 |

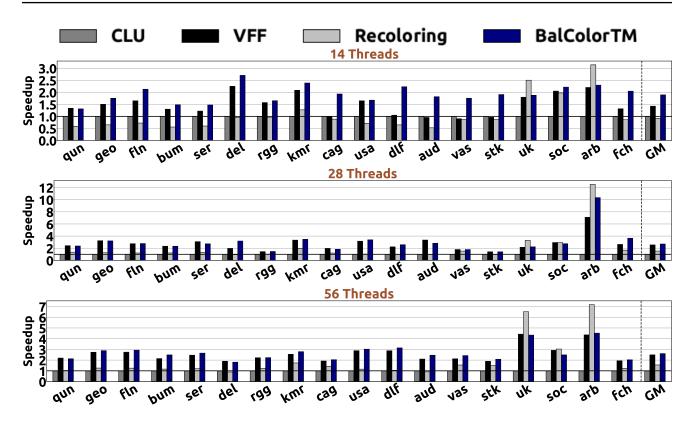

| 2.23 | Speedup achieved by all balanced graph coloring implementations over the CLU scheme<br>in large real-world graphs using the maximum hardware thread capacity of an Intel<br>Broadwell server with hyperthreading enabled (88 threads).                                                                                                                                                                                                                                    | 76 |

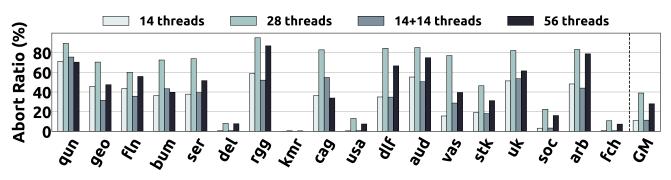

| 2.24 | Abort ratio exhibited by <i>BalColorTM</i> in all large real-world graphs                                                                                                                                                                                                                                                                                                                                                                                                 | 77 |

| 2.25 | Scalability of the end-to-end Community Detection execution achieved by (i) the Grappolo [12] parallelization approach of the Louvain method (SimplCD) and (ii) the chromatic scheduling parallelization approach with <i>ColorTM</i> ( <i>ColorTM</i> CD) and (iii) the chromatic scheduling parallelization approach with both <i>ColorTM</i> and <i>BalColorTM</i> ( <i>BalColorTM</i> CD) in large real-world graphs. | 79 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

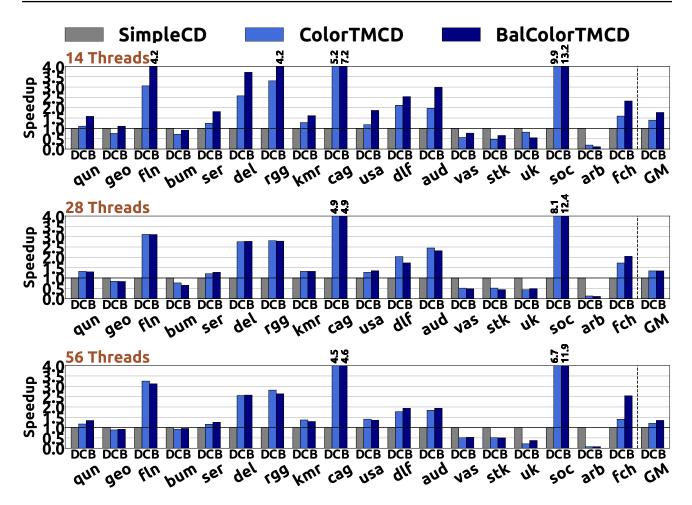

| 2.26 | Speedup of the actual kernel of the Community Detection execution achieved by (i)<br>SimpleCD (D), (ii) <i>ColorTM</i> CD (C) and (iii) <i>BalColorTM</i> CD (B) in large real-world<br>graphs using all cores of one socket (14 threads), all cores of two sockets (28 threads),<br>and the maximum hardware thread capacity of our machine with hyperthreading en-<br>abled (56 threads).                               | 80 |

| 2.27 | Speedup breakdown of the end-to-end Community Detection execution achieved by (i) SimpleCD (D), (ii) <i>ColorTM</i> CD (C) and (iii) <i>BalColorTM</i> CD (B) in large real-world graphs using all cores of one socket (14 threads), all cores of two sockets (28 threads), and the maximum hardware thread capacity of our machine with hyperthreading enabled (56 threads).                                             | 81 |

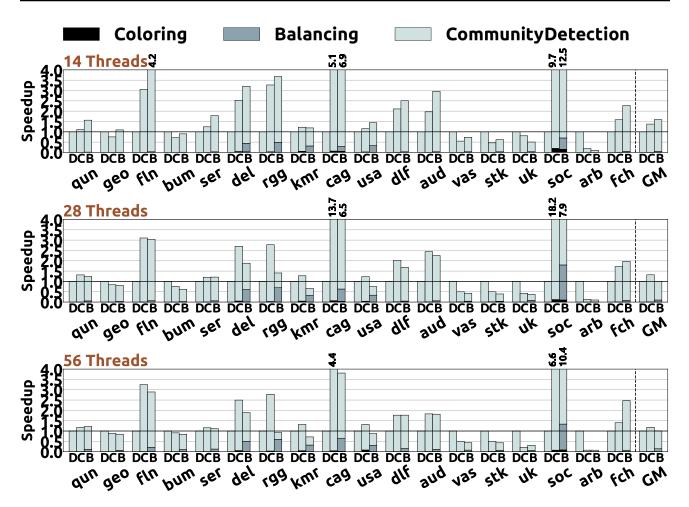

| 3.1  | Throughput achieved by a NUMA-oblivious [13,14] and a NUMA-aware [15] priority queue, both initialized with 1024 keys. We use 64 threads that perform a mix of <i>insert</i> and <i>deleteMin</i> operations in parallel, and the key range is set to 2048 keys. We use <i>all</i> NUMA nodes of a 4-node NUMA system, the characteristics of which are presented in Section 3.4.                                         | 86 |

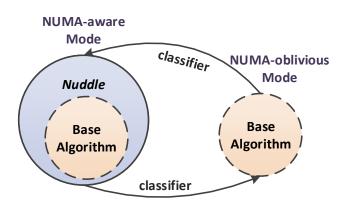

| 3.2  | High-level overview of <i>SmartPQ</i> . <i>SmartPQ</i> dynamically adapts its algorithm to the contention levels of the workload based on the prediction of a simple classifier                                                                                                                                                                                                                                           | 87 |

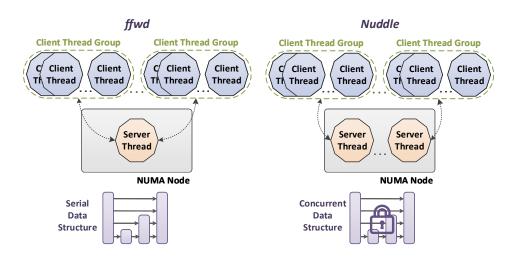

| 3.3  | High-level design of <i>ffwd</i> [15] and <i>Nuddle</i> . <i>Nuddle</i> locates <i>all</i> server threads at the <i>same</i> NUMA node to design a NUMA-aware scheme, and associates each of them to multiple client thread groups. <i>Nuddle</i> uses the communication protocol proposed in <i>ffwd</i> [15]                                                                                                            | 89 |

| 3.4  | Helper structures of <i>Nuddle</i>                                                                                                                                                                                                                                                                                                                                                                                        | 90 |

| 3.5  | Initialization functions of <i>Nuddle</i>                                                                                                                                                                                                                                                                                                                                                                                 | 91 |

| 3.6  | Functions used by server threads and client threads to perform operations using <i>Nuddle</i> .                                                                                                                                                                                                                                                                                                                           | 92 |

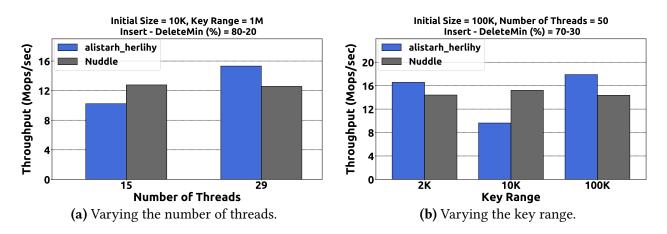

| 3.7  | Throughput achieved by <i>Nuddle</i> (using 8 server threads) and its underlying NUMA-<br>oblivious <i>base algorithm</i> , i.e., <i>alistarh_herlihy</i> [13, 14], when we vary (a) the number<br>of threads that perform operations in the shared data structure, and (b) the key range<br>of the workload.                                                                                                             | 93 |

|      | 3.7a Varying the number of threads.                                                                                                                                                                                                                                                                                                                                                                                       | 93 |

|      | 3.7b Varying the key range                                                                                                                                                                                                                                                                                                                                                                                                | 93 |

| 3.8  | The modified code of Nuddle with the decision-making mechanism to implement                                                                                                                                                                                                                                                                                                                                               |    |

|      | SmartPQ                                                                                                                                                                                                                                                                                                                                                                                                                   | 96 |

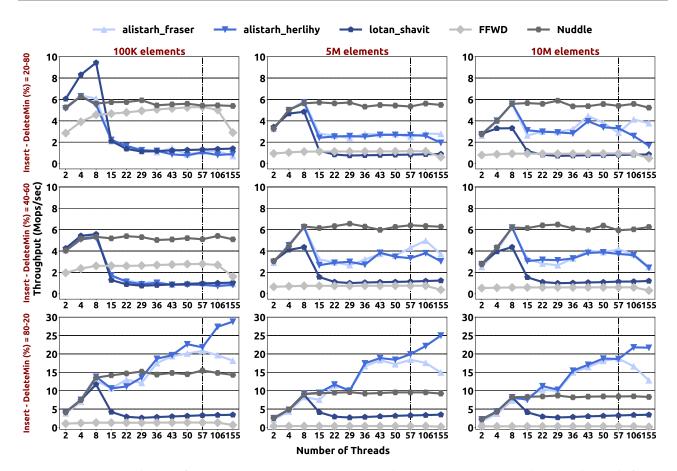

| 3.9  | Throughput of concurrent priority queue implementations. The columns show dif-<br>ferent priority queue sizes using the key range of double the elements of each size.                                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | The rows show different operation workloads. The vertical line in each plot shows                                                                                                                                                                                                   |

|      | the point after which we oversubscribe software threads to hardware contexts 99                                                                                                                                                                                                     |

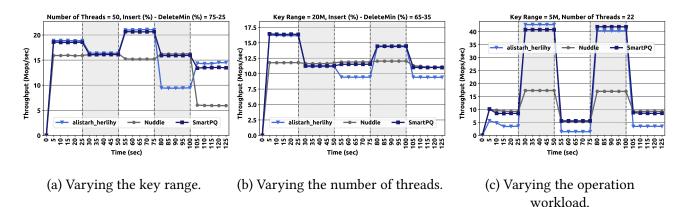

| 3.10 | Throughput achieved by <i>SmartPQ</i> , <i>Nuddle</i> and its underlying <i>base algorithm</i> ( <i>alistarh_herlihy</i> ), in synthetic benchmarks, in which we vary a) the key range, b) the number of threads that perform operations in the data structure, and c) the percent- |

|      | age of <i>insert/deleteMin</i> operations in the workload                                                                                                                                                                                                                           |

|      | 3.10a Varying the key range                                                                                                                                                                                                                                                         |

|      | 3.10b Varying the number of threads                                                                                                                                                                                                                                                 |

|      | 3.10c Varying the operation workload                                                                                                                                                                                                                                                |

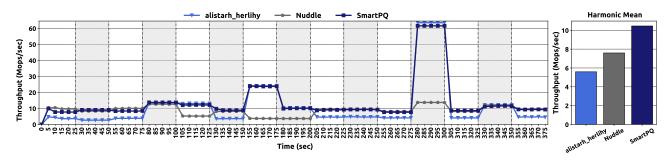

| 3.11 | Throughput achieved by SmartPQ, Nuddle and its underlying base algorithm (alis-                                                                                                                                                                                                     |

|      | tarh_herlihy), in synthetic benchmarks, in which we vary multiple features in the                                                                                                                                                                                                   |

|      | contention workload                                                                                                                                                                                                                                                                 |

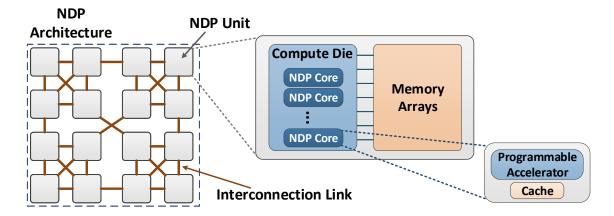

| 4.1  | High-level organization of an NDP architecture                                                                                                                                                                                                                                      |

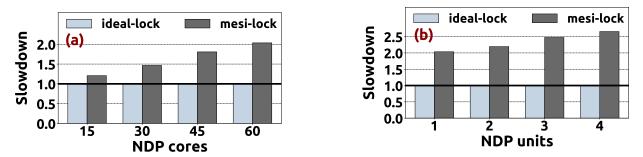

| 4.2  | Slowdown of a stack data structure using a coherence-based lock over using an <i>ideal</i>                                                                                                                                                                                          |

|      | zero-cost lock, when varying (a) the NDP cores within a single NDP unit and (b) the                                                                                                                                                                                                 |

|      | number of NDP units while keeping core count constant at 60                                                                                                                                                                                                                         |

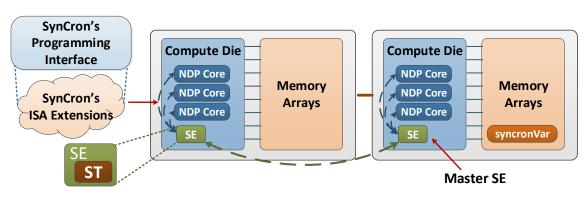

| 4.3  | High-level overview of <i>SynCron</i>                                                                                                                                                                                                                                               |

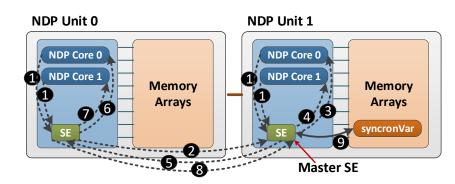

| 4.4  | An example execution scenario for a lock requested by <i>all</i> NDP cores                                                                                                                                                                                                          |

| 4.5  | Message encoding of <i>SynCron</i>                                                                                                                                                                                                                                                  |

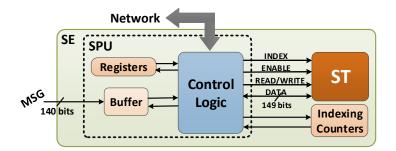

| 4.6  | The Synchronization Engine (SE)                                                                                                                                                                                                                                                     |

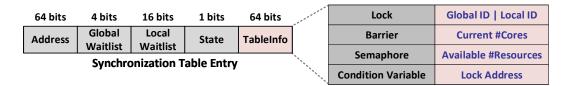

| 4.7  | Synchronization Table (ST) entry                                                                                                                                                                                                                                                    |

| 4.8  | Control flow in SE                                                                                                                                                                                                                                                                  |

| 4.9  | Synchronization variable of <i>SynCron</i> ( <i>syncronVar</i> )                                                                                                                                                                                                                    |

| 4.10 | Speedup of different synchronization primitives                                                                                                                                                                                                                                     |

| 4.11 | Throughput of pointer-chasing using data structures                                                                                                                                                                                                                                 |

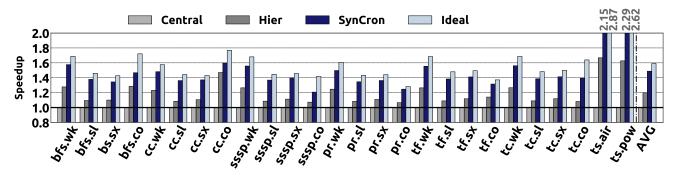

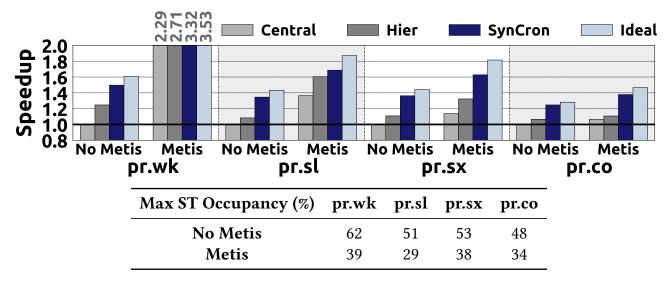

| 4.12 | Speedup in real applications normalized to <i>Central</i>                                                                                                                                                                                                                           |

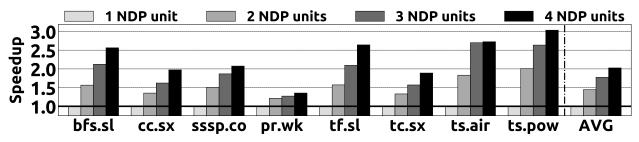

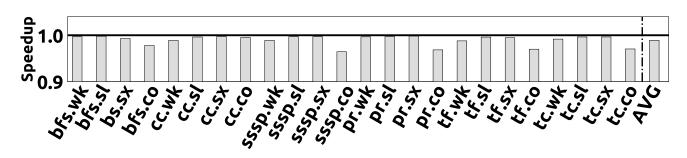

| 4.13 | Scalability of real applications using <i>SynCron</i>                                                                                                                                                                                                                               |

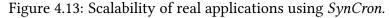

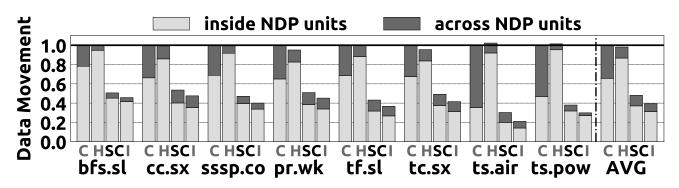

| 4.14 | Energy breakdown in real applications for C: Central, H: Hier, SC: SynCron and I: Ideal. 129                                                                                                                                                                                        |

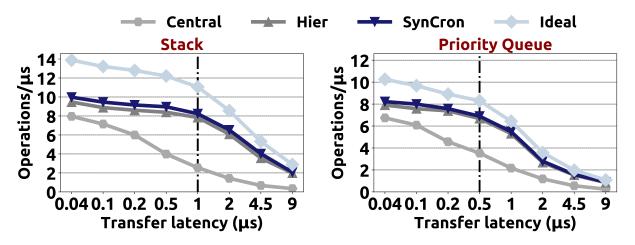

| 4.15 | Data movement in real applications for C: Central, H: Hier, SC: SynCron and I: Ideal 130                                                                                                                                                                                            |

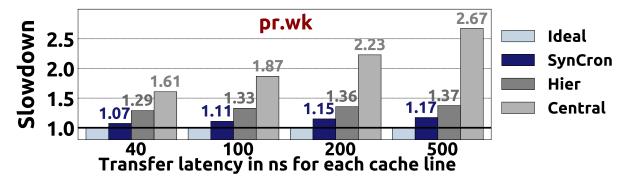

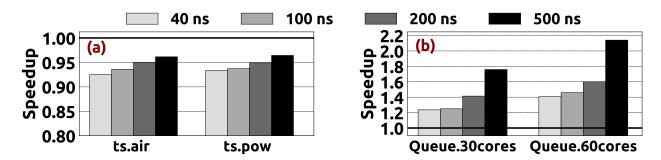

| 4.16 | Performance sensitivity to the transfer latency of the interconnection links used to                                                                                                                                                                                                |

|      | connect the NDP units                                                                                                                                                                                                                                                               |

| 4.17 | Performance sensitivity to the transfer latency of the interconnection links used to                                                                                                                                                                                                |

|      | connect the NDP units. All data is normalized to <i>Ideal (lower is better)</i>                                                                                                                                                                                                     |

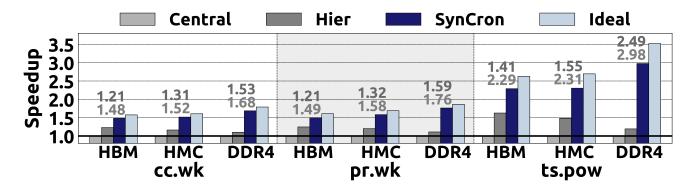

| 4.18 | Speedup with different memory technologies                                                                                                                                                                                                                                          |

| 4.19 | Performance sensitivity to a better graph partitioning and maximum ST occupancy                                                                                                                                                                                                     |

|      | of SynCron                                                                                                                                                                                                                                                                          |

| 4.21 | Speedup of SynCron normalized to flat, as we vary the transfer latency of the intercon-  |     |

|------|------------------------------------------------------------------------------------------|-----|

|      | nection links used to connect NDP units, under (a) a low-contention and synchronization  | -   |

|      | intensive scenario using 4 NDP units, and (b) a high-contention scenario using 2 and     |     |

|      | 4 NDP units.                                                                             | 133 |

| 4.20 | Speedup of SynCron normalized to <i>flat</i> with 40 ns link latency between NDP units,  |     |

|      | under a low-contention and synchronization non-intensive scenario.                       | 133 |

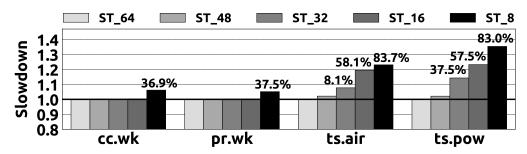

| 4.22 | Slowdown with varying ST size (normalized to 64-entry ST). Numbers on top of bars        |     |

|      | show the percentage of overflowed requests.                                              | 134 |

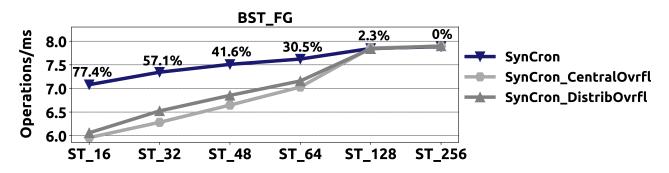

| 4.23 | Throughput achieved by BST_FG using different overflow schemes and varying the           |     |

|      | ST size. The reported numbers show to the percentage of overflowed requests              | 135 |

| 5.1  | (a) CSR representation of a sparse matrix. (b) CSR-based SpMV implementation             | 143 |

| 5.2  | (a) SpMV with a dense matrix representation, and (b) CSR, (c) COO, (d) BCSR, (e)         |     |

|      | BCOO formats                                                                             | 143 |

| 5.3  | High-level organization of a near-bank PIM architecture                                  | 145 |

| 5.4  | Execution of the SpMV kernel on a real PIM system                                        | 147 |

| 5.5  | Data partitioning techniques of the <i>SparseP</i> package                               | 147 |

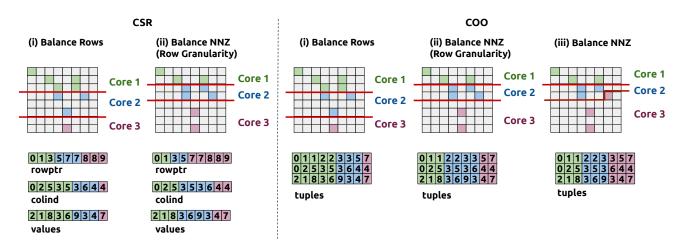

| 5.6  | Load balancing schemes across PIM cores for the CSR (left) and COO (right) formats       |     |

|      | with the 1D partitioning technique. The colored cells of the matrix represent non-zero   |     |

|      | elements                                                                                 | 149 |

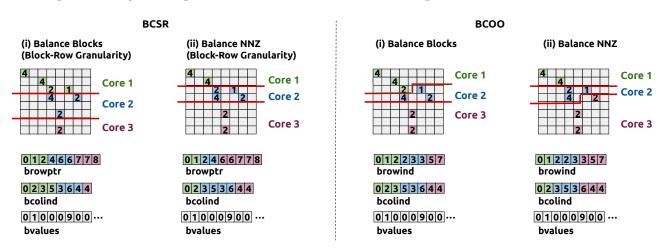

| 5.7  | Load balancing schemes across PIM cores for the BCSR (left) and BCOO (left) formats      |     |

|      | with the 1D partitioning technique. The cells of the matrix represent sub-blocks of size |     |

|      | 4x4. The colored cells of the matrix represent non-zero sub-blocks, and the number       |     |

|      | inside a colored cell describes the number of non-zero elements of the corresponding     |     |

|      | sub-block.                                                                               | 149 |

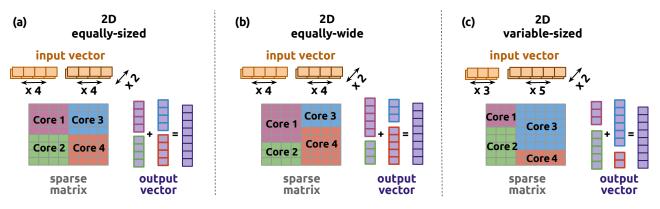

| 5.8  | The 2D partitioning techniques of <i>SparseP</i> package assuming 4 PIM cores and 2 ver- |     |

|      | tical partitions                                                                         | 150 |

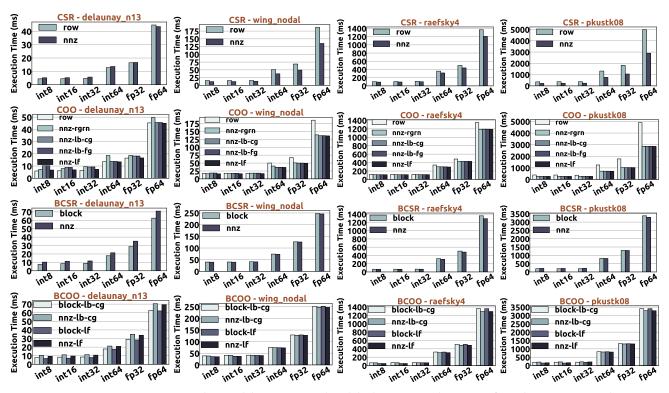

| 5.9  | Execution time achieved by various load balancing schemes of each compressed ma-         |     |

|      | trix format using 16 tasklets of a single DPU                                            | 156 |

| 5.10 | Scalability of all compressed formats for the int8 (top graphs) and fp64 (bottom graphs) |     |

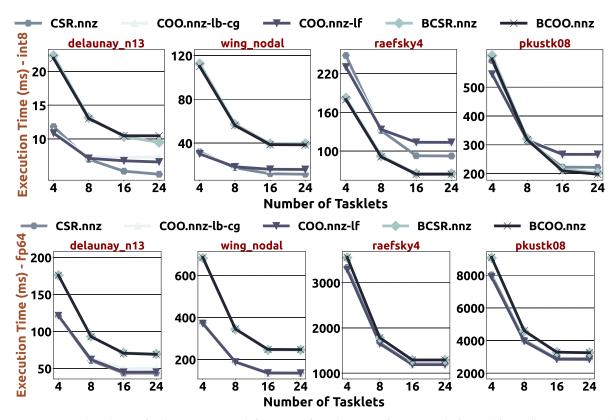

|      | data types as the number of tasklets of a single DPU increases                           | 158 |

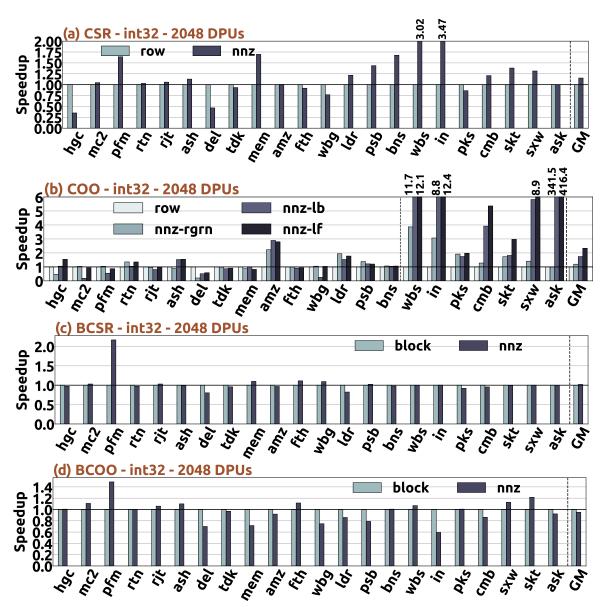

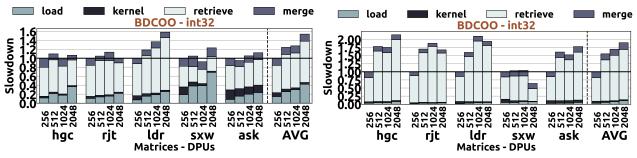

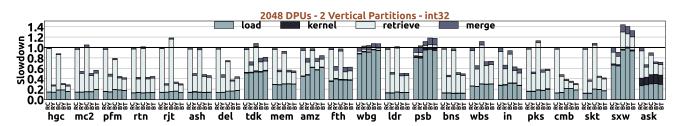

| 5.11 | Performance comparison of load balancing techniques for each particular compressed       |     |

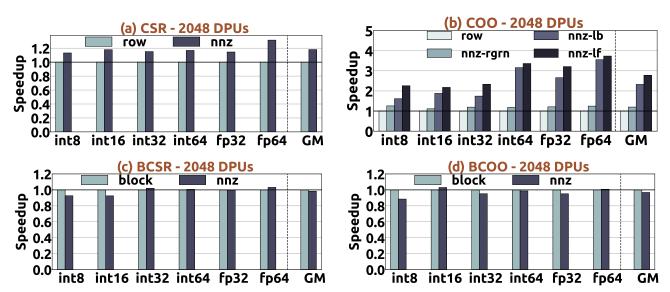

|      | format using 2048 DPUs and the int32 data type                                           | 160 |

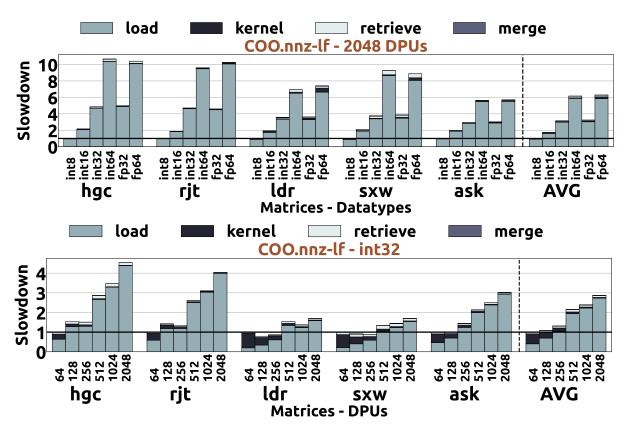

| 5.12 | Performance comparison of load balancing techniques for each data type using 2048        |     |

|      | DPUs                                                                                     | 162 |

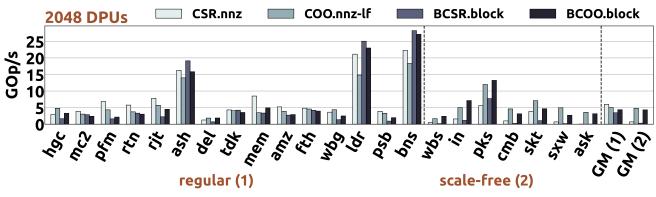

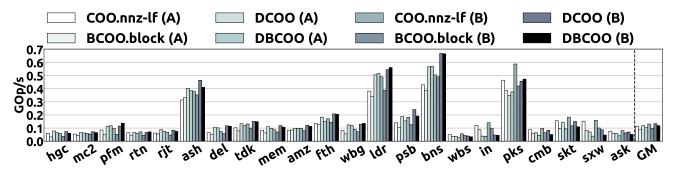

| 5.13 | Throughput of various compressed formats using 2048 DPUs and the int32 data type.        | 162 |

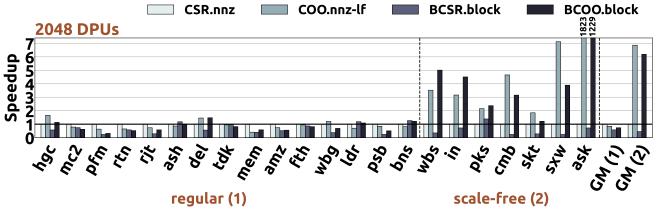

| 5.14 | Performance comparison of various compressed formats using 2048 DPUs and the             |     |

|      | int32 data type. Performance is normalized to that of CSR.nnz.                           | 162 |

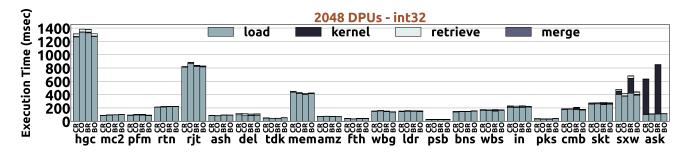

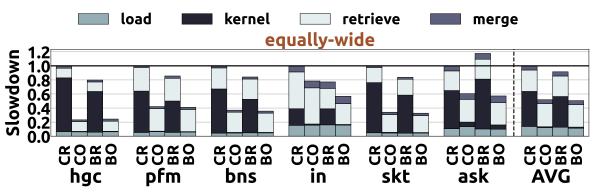

| 5.15 | Total execution time when using 2048 DPUs and the int32 data type for CR: CSR . nnz,     |     |

|      | CO: COO.nnz-lf, BR: BCSR.block and BO: BCOO.block kernels.                               | 163 |

- 5.16 End-to-end execution time breakdown achieved by COO.nnz-lf when varying (a) the data type using 2048 DPUs (normalized to the experiment for the int8 data type), and (b) the number of DPUs for the int32 data type (normalized to 64 DPUs). . . . . 164

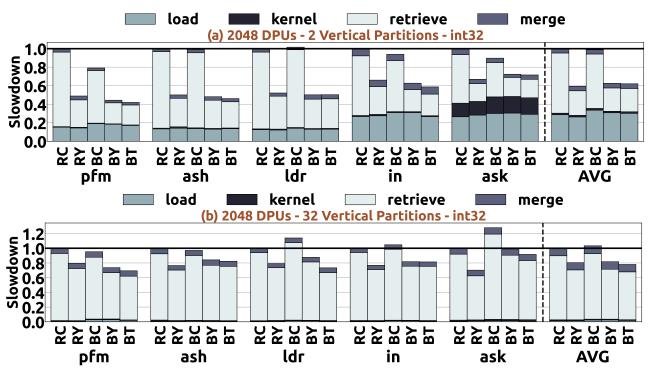

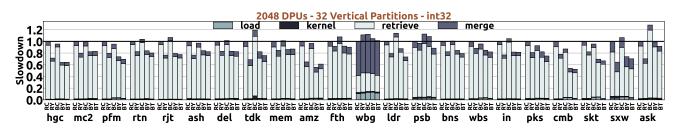

- 5.17 Performance comparison of RC: RBDCOO with coarse-grained transfers, RY: RBDCOO with fine-grained transfers in the output vector, BC: BDCOO with coarse-grained transfers, BY: BDCOO with fine-grained transfers only in the output vector, and BT: BDCOO with fine-grained transfers in both the input and the output vector using the int32 data type, 2048 DPUs and having 2 (left) and 32 (right) vertical partitions. Performance is normalized to that of the RC scheme.

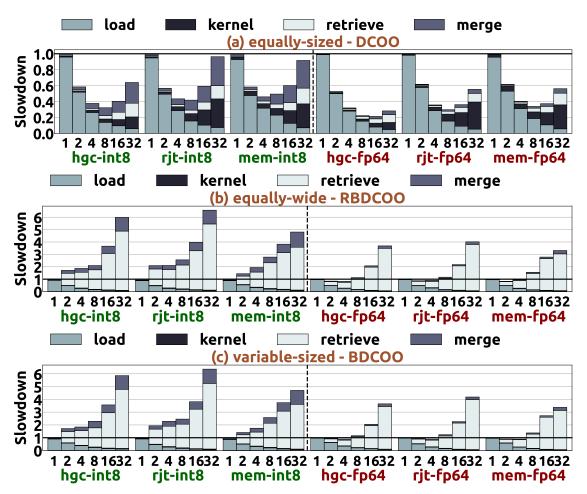

- 5.18 Execution time breakdown of *equally-sized* partitioning technique of the COO format using 4 (left) and 16 (right) vertical partitions when varying the number of DPUs used for the int32 data type. Performance is normalized to that with 256 DPUs. . . . . . 167

- 5.21 Execution time breakdown of 2D partitioning schemes using the COO format and 2048 DPUs when varying the number of vertical partitions from 1 to 32 for the int8 and fp64 data types. Performance is normalized to the performance of the experiment with 1 vertical partition.

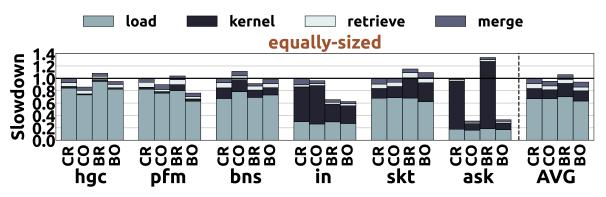

- 5.22 End-to-end execution time breakdown of the *equally-sized* 2D partitioning technique for CR: DCSR, CO: DCOO, BR: DBCSR and BO: DBCOO schemes using 4 vertical partitions and the int32 data type. Performance is normalized to that of DCSR. . . . . 170

- 5.23 End-to-end execution time breakdown of the *equally-wide* 2D partitioning technique for CR: RBDCSR, CO: RBDCOO, BR: RBDBCSR and BO: RBDBCOO schemes using 4 vertical partitions and the int32 data type. Performance is normalized to that of RBDCSR.

171

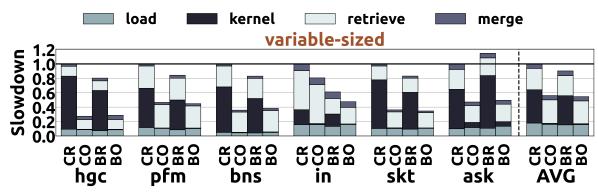

5.24 End-to-end execution time breakdown of the *variable-sized* 2D partitioning technique for CR: BDCSR, CO: BDCOO, BR: BDBCSR and BO: BDBCOO schemes using 4 vertical partitions and the int32 data type. Performance is normalized to that of BDCSR. 171

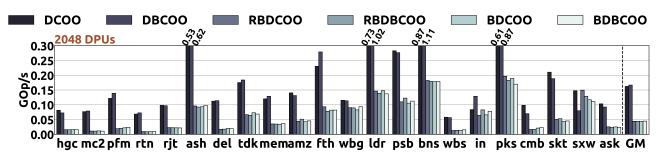

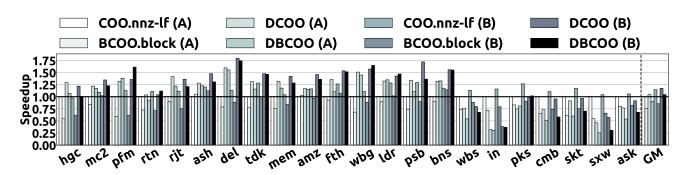

- 5.25 Throughput of 2D partitioning techniques using the COO and BCOO formats, 2048 DPUs and the int32 type.

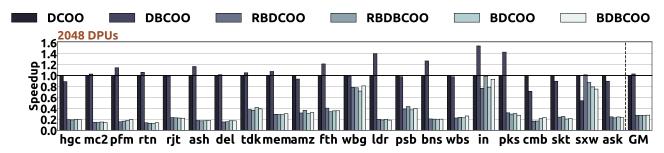

5.26 Performance comparison of 2D partitioning techniques using the COO and BCOO

| 5.29 | Performance comparison between the UPMEM PIM system, Intel Xeon CPU and Tesla V100 GPU on SpMV execution                                                                                                                                                                                                                                                                                                                                                 | 175 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.30 | Energy comparison between the UPMEM PIM system, Intel Xeon CPU and Tesla V100 GPU on SpMV execution.                                                                                                                                                                                                                                                                                                                                                     | 177 |

| 8.1  | Performance of the BCOO format with various load balancing schemes and synchro-<br>nization approaches for all the data types and small matrices using 16 tasklets of one<br>DPU                                                                                                                                                                                                                                                                         | 194 |

| 8.2  | Performance comparison of RC: RBDCOO with coarse-grained transfers, RY: RBDCOO with fine-grained transfers in the output vector, BC: BDCOO with coarse-grained transfers, BY: BDCOO with fine-grained transfers only in the output vector, and BT: BDCOO with fine-grained transfers in both the input and the output vector using the int32 data type, 2048 DPUs and having 2 vertical partitions. Performance is normalized to that of the RC scheme.  | 194 |

| 8.3  | Performance comparison of RC: RBDCOO with coarse-grained transfers, RY: RBDCOO with fine-grained transfers in the output vector, BC: BDCOO with coarse-grained transfers, BY: BDCOO with fine-grained transfers only in the output vector, and BT: BDCOO with fine-grained transfers in both the input and the output vector using the int32 data type, 2048 DPUs and having 32 vertical partitions. Performance is normalized to that of the RC scheme. | 194 |

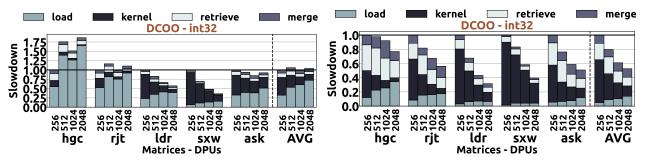

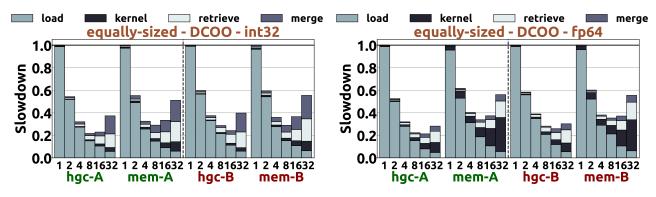

| 8.4  | Execution time breakdown of DCOO using 2048 DPUs when varying the number of vertical partitions from 1 to 32 for the int32 (left) and fp64 (right) data types on two different UPMEM PIM systems.                                                                                                                                                                                                                                                        | 196 |

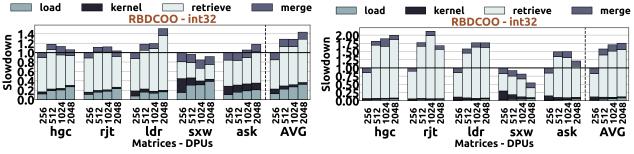

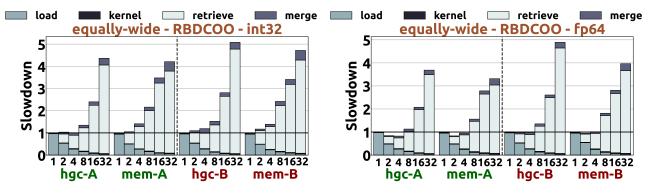

| 8.5  | Execution time breakdown of RBDCOO using 2048 DPUs when varying the number of vertical partitions from 1 to 32 for the int32 (left) and fp64 (right) data types on two different UPMEM PIM systems.                                                                                                                                                                                                                                                      | 106 |

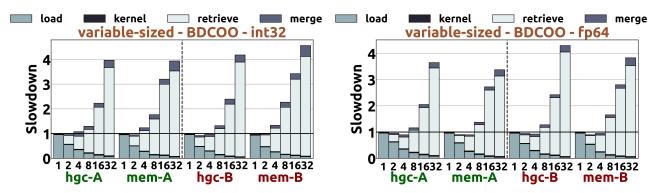

| 8.6  | Execution time breakdown of BDCOO using 2048 DPUs when varying the number of vertical partitions from 1 to 32 for the int32 (left) and fp64 (right) data types on two different UPMEM PIM systems.                                                                                                                                                                                                                                                       |     |

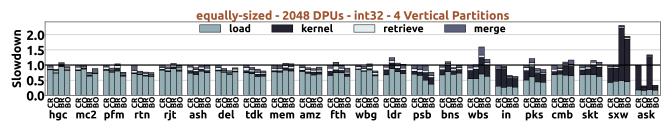

| 8.7  | End-to-end execution time breakdown of the <i>equally-sized</i> 2D partitioning technique for CR: DCSR, CO: DCOO, BR: DBCSR and BO: DBCOO schemes using 4 vertical partitions and the int32 data type. Performance is normalized to that of DCSR                                                                                                                                                                                                         |     |

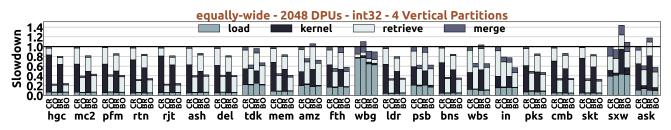

| 8.8  | End-to-end execution time breakdown of the <i>equally-wide</i> 2D partitioning technique for CR: RBDCSR, CO: RBDCOO, BR: RBDBCSR and BO: RBDBCOO schemes using 4 vertical partitions and the int32 data type. Performance is normalized to that of RBDCSR                                                                                                                                                                                                | 197 |

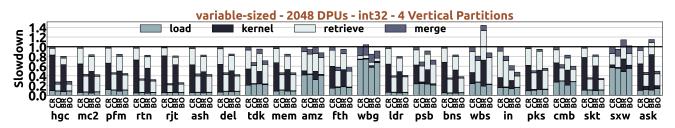

| 8.9  | End-to-end execution time breakdown of the <i>variable-sized</i> 2D partitioning technique for CR: BDCOO, CO: BDCOO, BR: BDBCSR and BO: BDBCOO schemes using 4 vertical partitions and the int32 data type. Performance is normalized to that of BDCSR.                                                                                                                                                                                                  | 197 |

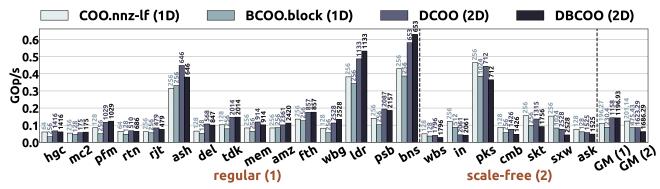

| 8.10 | Throughput of 1D- and 2D-partitioned kernels for the fp32 data type using two dif-             |

|------|------------------------------------------------------------------------------------------------|

|      | ferent UPMEM PIM systems                                                                       |

| 8.11 | Performance comparison of 1D- and 2D-partitioned kernels for the fp32 data type us-            |

|      | ing two different UPMEM PIM systems. Performance is normalized to that of COO . nnz – $1f$     |

|      | (A)                                                                                            |

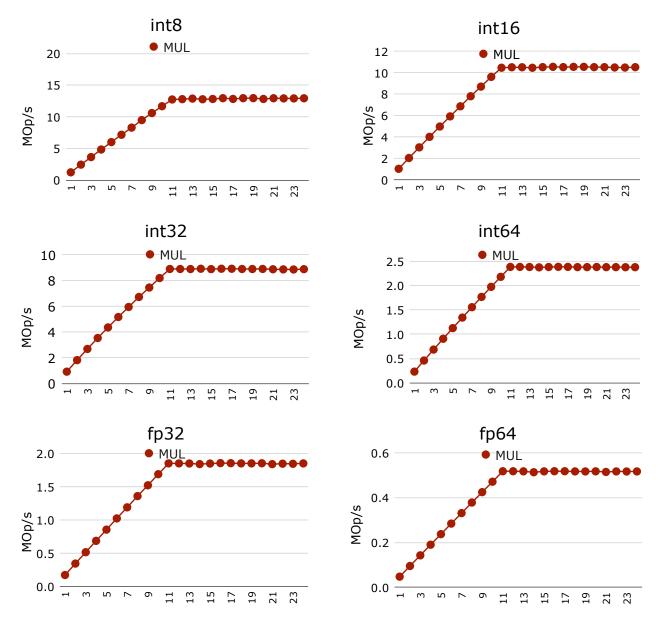

| 8.12 | Throughput of the MUL operation on one DPU at 350 MHz for all the data types. $$ 199           |

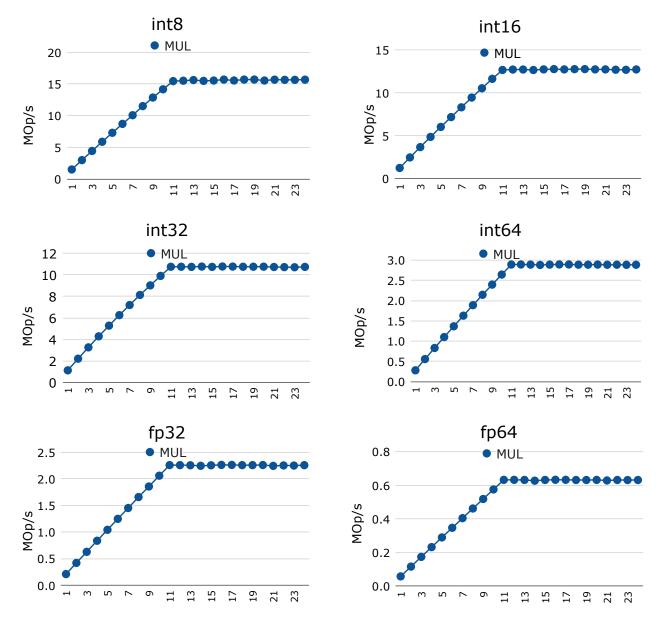

| 8.13 | Throughput of the MUL operation on one DPU at 425 MHz for all the data types. $\therefore$ 200 |

|      |                                                                                                |

# List of Tables

| 2.1 | Large Real-World Graph Dataset.                                                               | 65  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 2.2 | The geometric mean on the number of colors produced across all large real-world               |     |

|     | graphs (lower is better) for each parallel graph coloring implementation using one            |     |

|     | core (1 thread), all cores of one socket (14 threads), all cores of two sockets (28 threads), |     |

|     | and the maximum hardware thread capacity of our machine with hyperthreading                   |     |

|     | enabled (56 threads).                                                                         | 66  |

| 2.3 | Color balancing quality achieved by <i>ColorTM</i> and all balanced graph coloring imple-     |     |

|     | mentations in the large real-world graphs. We present the relative standard deviation         |     |

|     | (in $\%$ ) on the sizes of the color classes obtained by each scheme (lower is better).       |     |

|     | In <i>ColorTM</i> and Recoloring, we provide inside the parentheses the number of color       |     |

|     | classes produced. The CLU, VFF and <i>BalColorTM</i> produce the same number of color         |     |

|     | classes with the initial coloring scheme                                                      | 73  |

| 3.1 | The features of the contention workload which are used for classification                     | 95  |

| 3.2 | Features of the contention workload for benchmarks evaluated in Figure 3.10. We use           |     |

|     | bold font on the features that change in each execution phase                                 | 101 |

|     | 3.2a Varying the key range in the workload.                                                   | 101 |

|     | 3.2b Varying the number of threads that perform operations in the data structure.             | 101 |

|     | 3.2c Varying the percentage of <i>insert/deleteMin</i> operations                             | 101 |

| 3.3 | Features of the contention workload for benchmarks evaluated in Figure 3.11. We use           |     |

|     | bold font on the features that change in each execution phase                                 | 102 |

| 4.1 | Throughput of two coherence-based lock algorithms on an Intel Xeon Gold server                |     |

|     | using the libslock library [16]                                                               | 112 |

| 4.2 | SynCron's Programming Interface (i.e., API).                                                  | 116 |

| 4.3 | Message opcodes of <i>SynCron</i>                                                                        | 117 |

|-----|----------------------------------------------------------------------------------------------------------|-----|

| 4.4 | Comparison of <i>SynCron</i> with prior mechanisms.                                                      | 123 |

| 4.5 | Configuration of our simulated system.                                                                   | 124 |

| 4.6 | Summary of all workloads used in our evaluation.                                                         | 125 |

| 4.7 | ST occupancy in real applications.                                                                       | 134 |

| 4.8 | Comparison of SE with a simple general-purpose in-order core, ARM Cortex A7                              | 135 |

| 5.1 | Parallelization techniques across PIM cores of the SparseP library. *: row-granularity,                  |     |

|     | $^{\dagger}$ : block-row-granularity                                                                     | 151 |

| 5.2 | Parallelization schemes across threads of a PIM core. *: row-granularity, $^{\dagger}$ : block-          |     |

|     | row-granularity                                                                                          | 153 |

| 5.3 | Small Matrix Dataset                                                                                     | 154 |

| 5.4 | Large Matrix Dataset. Matrices are sorted by NNZ-r-std, i.e., based on their irregular                   |     |

|     | pattern. The highlighted matrices with red color exhibit block pattern [17, 18]. $\ldots$                | 155 |

| 5.5 | Evaluated CPU, GPU, and UPMEM PIM Systems.                                                               | 174 |

| 8.1 | Evaluated UPMEM PIM Systems                                                                              | 195 |

| 8.2 | The SparseP library. *: row-granularity, $\dagger$ : block-row-granularity, $\ddagger$ : (only for 8-bit |     |

|     | integer and small block sizes)                                                                           | 201 |

| 8.3 | Large Matrix Dataset. Matrices are sorted by NNZ-r-std, i.e., based on their irregular                   |     |

|     | pattern                                                                                                  | 202 |

|     |                                                                                                          |     |

## CHAPTER 1

## Introduction

Irregular applications such as graph processing, data analytics, sparse linear algebra and dynamic pointer-chasing constitute an important part of software systems we rely on. These applications lie at the heart of many important workloads including deep neural networks [19–24], bioinformatics [25–27], databases [28, 29], data analytics [29–37], large-scale simulations [38–43], medical imaging [18, 40, 44], economic modeling [18, 40, 44], and scientific applications [18, 40–44]. Therefore, optimizing and accelerating irregular applications is of vital importance, and thus a large corpus of research proposes either software designs [1, 13–15, 18, 44–152] or hardware mechanisms [5, 10, 20, 22, 25–29, 32–37, 39, 129, 153–288] to accelerate the execution of such applications.