# Microarchitectural Leakage Templates and Their Application to Cache-Based Side Channels

Ahmad Ibrahim\*

CISPA Helmholtz Center for

Information Security

ahmad.ibrahim@cispa.de

Hamed Nemati\*

Stanford University

CISPA Helmholtz Center for

Information Security

hnnemati@stanford.edu

Till Schlüter

CISPA Helmholtz Center for

Information Security

till.schlueter@cispa.de

Nils Ole Tippenhauer CISPA Helmholtz Center for Information Security tippenhauer@cispa.de

Christian Rossow CISPA Helmholtz Center for Information Security rossow@cispa.de

# **ABSTRACT**

The complexity of modern processor architectures has given rise to sophisticated interactions among their components. Such interactions may result in potential attack vectors in terms of side channels, possibly available to userland exploits to leak secret data. Exploitation and countering of such side channels requires a detailed understanding of the target component. However, such detailed information is commonly unpublished for many CPUs.

In this paper, we introduce the concept of Leakage Templates to abstractly describe specific side channels and identify their occurrences in binary applications. We design and implement Plumber, a framework to derive the generic Leakage Templates from individual code sequences that are known to cause leakage (e.g., found by prior work). Plumber uses a combination of *instruction fuzzing*, *instructions' operand mutation* and *statistical analysis* to explore undocumented behavior of microarchitectural optimizations and derive sufficient conditions on vulnerable code inputs that if hold can trigger a distinguishing behavior. Using Plumber we identified novel leakage primitives based on Leakage Templates (for ARM Cortex-A53 and -A72 cores), in particular related to *previction* (a new premature cache eviction), and prefetching behavior. We show the utility of Leakage Templates by re-identifying a prefetcher-based vulnerability in OpenSSL 1.1.0g first reported by Shin et al. [40].

# **CCS CONCEPTS**

$\bullet$  Security and privacy  $\to$  Side-channel analysis and countermeasures.

#### **KEYWORDS**

microarchitecture, side channel, leakage templates

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

CCS '22, November 7–11, 2022, Los Angeles, CA, USA. © 2022 Association for Computing Machinery.

© 2022 Association for Computing Machiner ACM ISBN 978-1-4503-9450-5/22/11...\$15.00 https://doi.org/10.1145/3548606.3560613

#### **ACM Reference Format:**

Ahmad Ibrahim, Hamed Nemati, Till Schlüter, Nils Ole Tippenhauer, and Christian Rossow. 2022. Microarchitectural Leakage Templates and Their Application to Cache-Based Side Channels. In *Proceedings of the 2022 ACM SIGSAC Conference on Computer and Communications Security (CCS '22), November 7–11, 2022, Los Angeles, CA, USA*. ACM, New York, NY, USA, 15 pages. https://doi.org/10.1145/3548606.3560613

# 1 INTRODUCTION

The past decade has witnessed a surge in side-channel attacks that exploit underspecified or undocumented hardware features [3, 16, 18, 23, 30, 44, 55], mostly focusing on cache-related leakage. The hidden nature of microarchitectural features has led to the development of techniques to test for the presence in hardware, and semi-automatically identify new vulnerabilities [11, 27, 28, 31, 37, 42, 43, 51] that allow the attacker to violate process isolation to obtain secret data, or to manipulate the victim's execution. Existing approaches to identify side channels commonly yield architecturespecific distinguishing examples, i.e., concrete code examples that represent side-channel leakage. Generalization from such concrete examples is a known hard problem, as it requires a detailed understanding of the processor component that introduces the channel. Details on information flow properties of microarchitectures are generally scarce, not publicly available, or depend on industrial secrets. As result, determining whether a given application is vulnerable to cache-related side-channel leakage is challenging.

Recent approaches already demonstrate the power of automation in the context of side channel analysis [11, 27, 37, 42, 51]. Gras et al. propose ABSynthe [11] to automatically infer leakage maps that show how instructions influence each other's contention behavior. Their system can identify and optimize for microarchitecturespecific side channels exploiting hyperthreading. In addition, Weber et al. introduce a fuzzing framework Osiris that synthesizes instruction sequences to identify timing-based side channels [51]. To this end, Osiris proposed an automated system to identify sequences that trigger and reset certain microarchitectural states. Finally, with Transynther [27], Moghimi et al. present an approach to synthesize Meltdown-type attacks. Transynther varies known attack patterns to create candidate attack code snippets and then evaluates whether these snippets leak data. All of these approaches have in common that they automate the search for new (variants of) side channels, a big leap towards automation. Having said this, they (i) are specific

<sup>\*</sup>Both authors contributed equally to the paper

towards their use case (e.g., contention, Meltdown), (ii) limit their search space (e.g., instruction operands are largely ignored), and (iii) focus on attack code generation instead of finding a generic pattern for vulnerabilities that can be matched in existing code.

In this work, we introduce the concept of *Leakage Templates* (or LTs for short), which consist of a generalized code sequence and a set of relations on input parameters that, when satisfied, can trigger specific leakage behavior in victim code (see § 3.4 for more details). Given such an LT for a target hardware platform, we can identify code sequences (and required input values) that expose a specific side channel behavior (see § 7 for an example). We thereby address two research questions: (1) How can we learn generic LTs for largely-undocumented leakage behavior? (2) How can we use the LTs to find side channel vulnerabilities?

To this end, we design and implement Plumber (source is available at [36]) to facilitate generating such LTs, leveraging *instruction fuzzing, instructions' operands mutation*, and *statistical analysis*. The design of Plumber is based on exploring the architectural space through the execution of program-input pairs, and analyzing the resulting microarchitectural states (focusing on caching). We design a domain-specific language that simplifies the generation of a large number of instruction sequences (i.e., programs) and mutating their operands. Further, we use a statistical analysis approach to classify microarchitectural states and to extract relations on inputs. To validate our approach, we studied the cases of the cache replacement policy of the ARM Cortex-A72 and two microarchitectural features of the ARM Cortex-A53 processors: *previction* and *prefetching*.

Previction is a recently discovered yet widely undocumented processor behavior of evicting cache lines *before* the corresponding cache set is full [28]. Since previction behaves differently for two addresses that only differ in their cache lines' offset, it may violate existing assumptions used to secure software [30]. Prefetching, on the other hand, is a partially documented feature that allows the processor to detect regular memory access patterns and to fill cache lines with anticipated addresses by proactively continuing the pattern. However, many details of prefetching (e.g., the number of prefetched lines) are undocumented. In addition, the cache replacement policy of ARM processors is not well-documented.

Leveraging Plumber, we analyze cache replacement policy, previction and prefetching behavior of the processor's core and derive related LTs. For the replacement policy experiment, the derived LT establishes eviction strategies of L1 data cache. In the case of previction, the extracted LTs reveal conditions under which bits of memory address loads are leaked.

For prefetching, we leverage Plumber to discover parameters such as the minimal number of loads to trigger prefetching, the impact of intermediate instructions, the impact of page boundaries on prefetching, and the impact of cache hits. In other words, we show how the obtained LTs expose prefetching side channels that allow to infer the control flow of a program and to leak secret information. Those channels are different from existing prefetching-based attacks discussed in the literature [6, 12, 40, 49], which target the x86 architecture and either attack a software-based prefetcher [12] or use a simulated CPU [6] for their analysis. Most similar to our approach is the work of Shin et al. [40] which exploits the hardware prefetcher to attack a constant-time Elliptic Curve Diffie-Hellman (ECDH) implementation from OpenSSL. However, compared to

ours, they used a different side channel, i.e. the effect of the order of accessed lookup table entries on the behavior of the prefetcher.

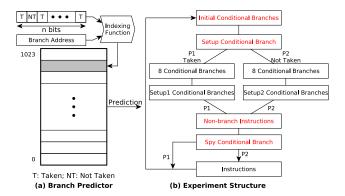

Although our focus in this paper is on the ARM architecture and cache-based side channels, the Plumber design is generic and can be used to detect LTs for other hardware features and on other architectures. Also, while the main goal of Plumber is to ease generating LTs, it can also be used to help reverse engineering of undocumented microarchitectural features. For example, § 10 shows how Plumber can be applied to discover the structure of the Cortex-A53's branch predictor.

Contributions. Our main contributions are as follows:

- We introduce the concept of *Leakage Templates*, which allow to identify code sequences (and required values) that expose a specific side channel behavior in a binary application executed on a specific architecture (§ 3).

- We design and implement Plumber, a framework that generates LTs, and allows to obtain a deeper understanding of hidden behavior of microarchitectures (§ 4, § 5, and § 10).

- We show Plumber's efficacy by investigating the undocumented eviction policy of Cortex-A72's L1 cache and previction and prefetching behaviors of the Cortex-A53 processors (§ 6), and identify five novel side channels (§ 8).

- We demonstrate how a derived LT can be used to identify a side channel in a binary application (§ 7).

# 2 BACKGROUND

Side channels are hidden information flow paths, which are potentially exploitable by an attacker to leak data. The number of attacks exploiting microarchitectural features, like caches [3, 30, 44, 45, 55], continues unabated. Therefore, the study of information flow analysis techniques to ensure the absence of side channel leakages is a topic of increasing relevance. Central to such an analysis is a model capturing the channel. However, the complexity of modern processors and the lack of information about their features make infeasible to explicitly model all the relevant, complex, and intertwined features like cache hierarchies and out-of-order execution. Abstract observational models tackle this problem by over-approximating attacker capabilities to observe flow of information via side channels.

# 2.1 Information Flow Analysis Tools - Scam-V

A key requirement of observational models is their soundness, i.e. observationally equivalent states should lead to executions that cannot be distinguished by an attacker on real hardware. Scam-V [28] automates validation of observational models' soundness. At high level, Scam-V generates well-formed random binary programs, which are denoted by  $\mathcal{P}$ . It then constructs pairs of initial states  $\mathcal{I}$ s.t. executions of  ${\mathcal P}$  from these states are observationally indistinguishable on the model. Scam-V then tests if the two states are also indistinguishable on hardware in the presence of undocumented microarchitectural components. Any experiment which enables the attacker to distinguish one microarchitecture-level execution from another represents a counterexample to the soundness of the observational model. We call a counterexample a leakage witness in this paper. A leakage witness can be seen as an instantiation of our Leakage Templates that can be used by an attacker to infer a function of the (secret) data via relevant side channels.

| Code Templa  | ate Input 1 (Tag/Set)                                   | Input 2 (Tag/Set)                           |

|--------------|---------------------------------------------------------|---------------------------------------------|

| ldr x3, [x6  | $x0: 0x80100000(T_1/S_1)$                               | $0x80100020(T_1/S_1)$                       |

| ldr x24, [x  | <b>x1</b> : 0x80100010(T <sub>1</sub> /S <sub>1</sub> ) | $0 \times 80100010 (T_1/S_1)$               |

| ldr x9, [x   | 2] x2: 0x80100000(T <sub>1</sub> /S <sub>1</sub> )      | $0 \times 80100000 (T_1/S_1)$               |

| ldr x2, [x   | <b>x3</b> : $0x8013e000(T_2/S_1)$                       | $0x8013e000(T_2/S_1)$                       |

| ldr x15, [x4 | <b>x4</b> : 0x80104000(T <sub>3</sub> /S <sub>1</sub> ) | 0x80104000(T <sub>3</sub> /S <sub>1</sub> ) |

Figure 1: A previction counterexample.

**Previction.** Previction is an undocumented behavior of the ARM Cortex-A53 processors which invalidates cache-related observational models. Previction causes a cache line to be evicted *before* the corresponding cache set is full. Scam-V [28] discovers a handful instances of this behavior. However, the real cause of *previction* is unknown. The authors conjecture that the processor detects a short sequence of loads to the same cache set and anticipates more loads to the same set with no reuse of previously loaded values. It evicts the valid cache line in order to make space for more colliding lines.

Fig. 1 depicts a previction counterexample. The program consists of five loads. The given inputs are observationally equivalent: they only differ for the value of x0, which affects the address used for the first load. However, the addresses 0x80100000 and 0x80100020 in x0 have the same tag and cache set index and only differ in the offset within the same cache line. The addresses of all load instructions are mapped to the same cache set, i.e., set 0. Since the cache is 4-way associative and is initially empty, one expects no eviction to occur. Executing the program with the given inputs on the real hardware, however, results in two different cache states. In one case x0 is present in the cache, while in the other case it is not.

# 2.2 ARMv8 internal memory subsystem

ARMv8 processors have two levels of caches: (1) a level one (L1) cache per each core; and (2) a last level cache (L2) shared between cores. When the CPU needs to read a memory location that is currently not cached, it fetches the requested data from memory into a cache line and tags that line with the memory location where the data was read from. When a line is loaded from memory and all potential destination lines in the cache are occupied, the CPU uses a specific replacement policy to decide which colliding line(s) should be evicted. The eviction policy ensures that the cache always stores the most popular content, thus using the available space efficiently.

Table 1 shows our notation to extract cache-related information from an address. sameTag, sameSet and samePage are predicates checking for equality of cache tag, set, or page indices of addresses.

**Prefetcher.** The L1 cache implements a prefetcher, for some configurable  $k \in \mathbb{N}$ . When the prefetcher detects k cache misses whose set indices are separated by a fixed stride, the prefetcher starts to fill the cache with a sequence of lines from memory locations whose addresses match the stride of the initial cache misses. We call such sequences *prefetch streams*. An exception happens when prefetching crosses a small page (4K) boundary. In this case the prefetcher stops fetching data from the adjacent page.

# 3 LEAKAGE TEMPLATES

We now introduce Leakage Templates and motivate their utility.

Table 1: Summary of notations.

| Notation                     | Description                   |

|------------------------------|-------------------------------|

| $a_i$                        | A physical address            |

| $a_i^{m-n}$                  | Bits $m$ through $n$ of $a_i$ |

| $set(a_i) = a_i^{6-12}$      | $a_i$ cache set index         |

| $tag(a_i) = a_i^{13-31}$     | $a_i$ cache tag               |

| $word(a_i) = a_i^{2-5}$      | $a_i$ word offset             |

| $bus(a_i) = a_i^{4-5}$       | $a_i$ bus round               |

| $page(a_i) = a_i^{12-31}$    | $a_i$ page index              |

| $sameTag(a_i, a_j, \ldots)$  | Cache tag equality predicate  |

| $sameSet(a_i, a_j, \ldots)$  | Cache set equality predicate  |

| $samePage(a_i, a_j, \ldots)$ | Page index equality predicate |

# 3.1 Goal and Motivation for Leakage Templates

Goal of the analyst. The overall setting is depicted in Fig. 3. We assume that the analyst has concrete examples of (artificial) code (for a specific hardware architecture) that behave distinctively on the microarchitectural level for different inputs, thus exposing an undocumented behavior. We call these examples distinguishing examples. Plumber takes as input an abstract description of a leaking code snippet in terms of a Generative Testcase Specification (GTS) (see § 4.1 for more details). The goal of the analyst is to utilize this behavior to leak information from a real-world application. To achieve this, the analyst needs to identify code segments in the target application that under certain analyst-controllable conditions trigger the undocumented microarchitectural behavior.

Motivation for Leakage Templates. As the analyst starts with concrete code sequences (in form of distinguishing examples), it is unlikely that the exact same code sequences will appear in another target application. Therefore, we need to abstract from the concrete code sequences and find: (1) a generalized code sequence, (2) a set of relevant attributes, and (3) relations between those attributes that expose the specific side channel. We call such information a Leakage Template or LT. The LT abstractly defines the conditions for code segments under which the leakage is observed. Given an LT, an analyst can identify code segments in a target application that expose a side channel. We demonstrate in § 7 how binaries can be scanned for code sections that match the code pattern from a LT. In addition, we show how dynamic binary analysis techniques can be used to analyze a matching code section for the presence of side-channel leakage based on the relations from a LT.

**Sources of distinguishing examples.** There are at least two general ways of finding distinguishing examples. Such examples can be derived from abstract (natural language) descriptions of the architecture's behavior, e.g., in manuals. Moreover, one can extract these examples from concrete code traces that expose the intended side channel, e.g., out of tools like Scam-V or zero-day exploits.

#### 3.2 Motivating Example I: Caching

Assume that simple caching behavior of a CPU was insufficiently documented, and the analyst tries to understand in which parts of a target application (and under which conditions) caching occurs.

**Initial Information.** A starting *leakage witness* (i.e. a distinguishing code example with a pair of inputs) could contain a sequence of two load instructions (for variable addresses), and two instances (i.e., pairs of input addresses) where different behavior

was observed. In the first instance, both loads refer to the same address, while in the second instance, two distinct addresses (on different cache lines) are accessed. When executing the two instances on a clean cache state, the second load will be considerably faster for the first instance compared to the second one.

**Leakage Template.** An abstract LT that describes this side channel would specify: (1) an abstract code template (i.e., at least two loads from symbolic addresses with potentially other instructions in between); (2) the two possible behaviors (i.e., fast and slow execution time of the second load); and (3) the relations over the loaded addresses which lead to the respective behaviors.

Benefit of the Leakage Template. The starting leakage witness just provides one concrete code instance that leads to the leakage behavior, while the LT ideally covers every possible sequence of instructions in which two loads lead to caching. Consequently, one would expect that the leakage witness alone will not enable the analyst to identify instances of the side channel leakage in an arbitrary target program, while the LT is expected to have much higher chances to discovering related code fragments.

# 3.3 Motivating Example II: Previction

For previction, the leakage behavior appears to require a more complex code sequence (see § 2.1).

**Initial information.** In this case, a starting leakage witness could contain a sequence of five loads, and two sets of addresses which lead to different behaviors, as summarized in Fig. 1.

**Leakage Template.** An LT that describes this side channel would specify: (1) an abstract code template (e.g., at least five loads from symbolic addresses with potentially a number of other instructions in between); (2) the two possible behaviors (i.e., previction or no previction); and (3) the abstract relations over the loaded addresses which lead to the respective behaviors.

# 3.4 Definition of Leakage Templates

Based on the provided motivation for LTs, we now describe the components of LTs themselves. An LT is a triple  $(\mathcal{P}(A), \mathcal{B}, \mathcal{R}(A, b))$ ; with  $\mathcal{P}(A)$  being a *code template* with a set of attributes  $A \subseteq \mathbb{A}$ ,  $\mathcal{B}$  a set of observed distinct behaviors, and  $\mathcal{R}: \mathbb{A} \times \mathcal{B} \to 2^{\mathbb{P}_A}$  maps a behavior  $b \in \mathcal{B}$  to a (set of) predicate(s) on attributes, where  $\mathbb{P}_A$  is the set of predicates on A. We note that our definition of behavior is generic. For instance, it may refer to temporal (e.g., measuring execution time) or spatial (e.g., monitoring cache content) behavior. For the latter, the behavior refers to the difference between the initial (before execution of the code template) and final (after execution of the code template) state of the monitored component (e.g., cache). Given this description, we provide additional details on the resulting LT for our caching example in Fig. 2. In § 6.2 we show how an LT for the previction example can be derived.

# 4 PLUMBER

We now present our design of Plumber, a framework to automatically derive LTs (focusing on caching behavior). In particular, in our design we had to address the following challenges:

• C1: We need to construct efficient specifications to steer testcase generation towards generating inputs which are likely to trigger a specific microarchitectural behavior.

| Code $\mathcal{P}(A)$ | Behavior and Relations                                         |

|-----------------------|----------------------------------------------------------------|

| ldr x0, [x1]          | $\mathcal{B} \mid \mathcal{R}(A,b)$                            |

| ; 0-n NIIs            | $(\bullet)$ sameTag $(x_1, x_2) \land$ sameSet $(x_1, x_2)$    |

| ldr x0, [x2]          | $(\circ)$ $\neg sameTag(x_1, x_2) \lor \neg sameSet(x_1, x_2)$ |

Figure 2: Caching LT. • (fast), ○ (slow) are distinguishing behaviors. NIIs are Non-Interfering Instructions.

- C2: Size of input space (number of possible code sequences and input values) is too large. Thus, we need an approach to explore the input space and ensure high test coverage which in turn increases accuracy of the derived relations.

- C3: We need to get accurate measurements with minimal noise, close to 'ground truth' of the respective channel.

- C4: The relations between attributes in code sequences and triggered behaviors can be very complex and counter-intuitive, and manual derivation of such relations (if not impossible) is highly error prone. So, we need to develop a statistical analysis technique to automate finding the correlation between attributes and observed behavior.

# 4.1 Abstract Framework Design

PLUMBER's input is a *Generative Testcase Specification* (GTS), which abstractly describes programs to analyze in a domain-specific language, and whose leakage effects are to be monitored. The detailed description of GTS and the language (and how it addresses **C1**) is provided in § 4.2 and 4.3. The framework outputs the LT, including the behavior of the monitored microarchitectural components, and the relations between attributes and the behaviors.

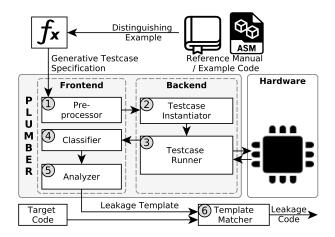

As shown in Fig. 3, the framework consists of two parts. The *Backend* instantiates and executes testcases (i.e., program-input pairs) from a (preprocessed) GTS. The *Frontend* encapsulates the Backend, towards the outside it receives a GTS and outputs LTs.

We present each component by describing the steps required to derive an LT from a GTS. ① The *Preprocessor* parses the GTS and forwards the result to the *Testcase Instantiator*. ② The Instantiator then systematically generates testcases (addressing C2) based on the parsed preprocessed GTS. ③ The *Runner* executes every testcase in a controlled environment (addressing C3) and returns the behavior to the *Classifier*. ④ The Classifier classifies the programs (if necessary) based on their behavior and stores them. ⑤ The *Analyzer* interprets classified behaviors (addressing C4) and returns relations on the attributes which trigger specific microarchitectural behavior (i.e.,  $\mathcal{B}$  and  $\mathcal{R}(A,b)$  of the LT).

A possible application of an LT is to identify instances of it in binaries. This can be done using a *Template Matcher* (6), which may use static and dynamic binary analysis techniques to find code sections matching the LT's code pattern as well as its relations. We discuss a proof-of-concept implementation in § 7.

#### 4.2 Definition of GTS

The GTS (used as input of Plumber) intuitively defines sequence(s) of instructions to be executed over (mutated) operands, and microarchitectural component(s) to be monitored (e.g., content of the cache). The GTS can also specify the initial state of (monitored) component(s) before the execution of its instruction sequences.

Figure 3: Overview of Plumber components.

To address C1 as outlined earlier, we introduce a domain-specific generative language. The language provides three main features. (i) It allows us to abstractly specify possible mutations of the program (i.e. enabling very generic code templates), (ii) it allows us to specify which data in the programs should be fuzzed or mutated (i.e. defining domains for attributes), and (iii) it allows us to specify a set of relations to apply to non-fuzzed data in the testcases.

# 4.3 Specification Language

A Generative Testcase Specification (GTS) is formed of a sequence of directives that specify different operations, e.g., arithmetic operations or nop instructions. The proposed language defines an extensible set of directives, which includes M, A and N. The directive M denotes memory loads, the directive A denotes arithmetic or logical operations, and the directive N denotes nop instructions. Additionally, the language defines two directives that allow reverse engineering the branch predictor (see § 10).  $S_{c_1,bool}$  denotes an instruction that sets a variable (identified by  $c_1$ ) to a boolean value bool, and  $B_{c_1,bool,step}$  denotes a branch instruction that jumps step steps when the value of the variable identified by  $c_1$  is bool. The default value of a variable is false (F).

The addresses of load operations are mapped to a certain cache set and have specific tags. It is possible to define the tag and set attributes of a memory directive. We use  $M_{t_1,S_1}$  to refer to a load from an address with tag  $t_1$  and cache set  $s_1$ . The values of these attributes allow determining the relation between tags or sets of different loads. When omitted, these attributes acquire default values which are identical for the same request. The language allows defining arithmetic relations between the tag (and set) attributes of different memory directives. For example, the GTS M M  $M_{t_1,s_1}$   $M_{t_1,s_1}$   $M_{t_1+1,s_1+5}$  A A N represents two loads of memory addresses with the same set and the same tag (default), followed by two other loads with a different tag t1 and a different set s1 and a fifth load with tag  $(t_2 = t_1 + 1)$  and set  $(s_2 = s_1 + 5)$ , two arithmetic or logical operations, and a nop instruction. The values of the operands of other instructions, e.g., arithmetic operations, can be defined in the same manner, e.g.,  $A_{V_1,V_2}$  represents an arithmetic operation with two operands  $v_1$  and  $v_2$ .

The language also provides an extensible set of macros and operators that allow constructing a meaningful GTS as well as defining the initial state of hardware components. Note that this language is extensible, i.e., it allows defining new macros and operators for investigating various processor components.

**Power** []dir<sub>attr</sub>, n, i. This macro allows repeating directive(s) n times, while incrementing the attribute attr of the directive dir by a value of i. For example, the GTS [ $M_{t_1,s_1}$ ]  $M_s$ , 2, 1 can be used to refer to the GTS:  $M_{t_1,s_1}$   $M_{t_1,s_1+1}$ . The power macro can be also used with a single input n. In this case the directive(s) are repeated n times. For example, the GTS presented above can also be expressed as: [M]2 [ $M_{t_1,s_1}$ ]2 [ $M_{t_1,s_1}$ ]2 [ $M_{t_1,s_1}$ ]3 [ $M_{t_1,s_1}$ ]  $M_{t_1,s_1}$  [ $M_{t_1,s_1}$ ]  $M_{t_1,s_1}$ ]  $M_{t_1,s_1}$  [ $M_{t_1,s_1}$ ]  $M_{t_1,s_1}$ ]  $M_{t_1,s_1}$   $M_{t_1,s_1}$   $M_{t_1,s_1}$   $M_{t_1,s_1}$ ]  $M_{t_1,s_1}$   $M_$

**Wildcard** #n. This macro expands to n arbitrary directives that do not perform memory operations. For example, one possible expansion of M #3 M is M N N N M.

**Shuffle** ()!. This operator generates all possible permutations of a GTS while omitting those with similar directives. For example, ([M]2  $M_{t_1,s_1}$ )! refers to the set: {M M  $M_{t_1,s_1}$ ; M  $M_{t_1,s_1}$  M;  $M_{t_1,s_1}$  M M}.

**Subset** ()⊂. This operator generates all possible subsets of a GTS while omitting those with similar directives. For example, ([M]2  $M_{t_1,s_1}$ )⊂ refers to the set: {M M; M  $M_{t_1,s_1}$ ; M;  $M_{t_1,s_1}$ }.

$\begin{array}{l} \textbf{Slide} \ () n. \ \text{For a given GTS}, \ \text{this operator shifts all loaded addresses one set at a time up to } n \ \text{times}. \ \text{For example}, \left( \texttt{M}_{\texttt{t}_1, \texttt{s}_1} \quad \texttt{M}_{\texttt{t}_2, \texttt{s}_2} \right) 3 \\ \text{refers to the set:} \left\{ \texttt{M}_{\texttt{t}_1, \texttt{s}_1} \quad \texttt{M}_{\texttt{t}_1, \texttt{s}_1+1} \quad \texttt{M}_{\texttt{t}_1, \texttt{s}_1+1}; \ \texttt{M}_{\texttt{t}_1, \texttt{s}_1+2} \quad \texttt{M}_{\texttt{t}_1, \texttt{s}_1+2} \right\}. \end{array}$

**Merge** (:)+. This operator merges two requests by sliding the directives of the first over the second as demonstrated by the following example. (Mt. s. Mt. s. Mt. s. Mt. s. Mt. s.)+ refers to the set:

**Load offset mutation**  $\langle \rangle @$ . For every load instruction, the operator signals generation of a testcase for all possible addresses with the indicated tag and set, i.e., it brute forces word offsets. For example,  $\langle M M \rangle @$  generates a set formed of all two loads having the same tag and set with all possible combinations of word offsets.

**Cache line mutation**  $\langle \rangle \$$ . For every load instruction, this operator signals the generation of a testcase for every possible memory address having the indicated tag and word offset, i.e., it brute forces all possible sets. For example,  $\langle M M \rangle \$$  generates a set formed of all two loads that have the same tag for all possible combinations of sets, i.e.,  $\{M_{t_1,s_1} \ M_{t_1,s_2}\}$  for every set  $s_1$  and  $s_2$ .

**Repetition** ||n. This operator repeats the GTS n times, e.g., the GTS |M  $M_{t_1,s_1}$  |3 corresponds to: {M  $M_{t_1,s_1}$ ; M  $M_{t_1,s_1}$ ; M  $M_{t_1,s_1}$ }.

**Precondition** P(). This operator allows setting up the state of different hardware components before the execution of testcase. For instance, the GTS  $P(M_{t_1,s_1} \ M_{t_2,s_1}) \ \langle M \ M \rangle \$$  generates cache line mutation testcases where two lines in  $s_1$  are already occupied.

# 5 DESIGN & IMPLEMENTATION

PLUMBER currently targets the ARM architecture. It is implemented in C and Python as well as ARM assembly. We exploit ARM assembly for: (a) implementing testcases, (b) setting up and (accurately) reading architectural components, and (c) increasing the performance. However, our design is applicable to other architectures. In the following, we present the implementation details for Plumber's components presented in Fig. 3.

|          | Load Register                           |                                         |    |    |                                         |

|----------|-----------------------------------------|-----------------------------------------|----|----|-----------------------------------------|

| Output   | x0                                      | x1                                      | x2 | x3 | x4                                      |

| 1        | 1 · · · 0000000000000000000000          | 1 · · · 000000000000000000000           |    |    | 1 · · · 10000000000000000               |

| 2        | 1 · · · 00000000000000100               | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

| 3        | 1 · · · 0000000000000000000000000000000 | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

| 4        | 1 · · · 00000000000001100               | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

| 5        | 1 · · · 0000000000000000000000000000000 | 1 · · · 0000000000000000000000          |    |    | 1 · · · 1000000000000000000000000000000 |

| 6        | 1 · · · 0000000000000000000000000000000 | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

| 7        | 1 · · · 00000000000011000               | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

| 8        | 1 · · · 00000000000011100               | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

| 9        | 1 · · · 00000000000000000               | 1 · · · 0000000000000000000000000000000 |    |    | 1 · · · 1000000000000000000000000000000 |

|          | <del></del>                             | _                                       |    |    |                                         |

| $2^{20}$ | 1 · · · 000000000111100                 | 1 · · · 000000000111100                 |    |    | 1 · · · 100000000111100                 |

Figure 4: Input bit table from a class causing previction. Shaded columns are registers responsible for previction. Shaded rows are inputs missing from the table. Mutated bits are in bold and the bits causing previction are underlined.

### 5.1 Frontend

The Frontend handles user interaction and has three components: **Preprocessor**. The preprocessor interprets a given GTS and forwards the results to the Backend. It expands repetition, power and wildcard macros. Wildcard is expanded by randomly picking directives from the set of defined operations. The Preprocessor is also responsible for expanding the shuffle, subset, slide and merge operators, i.e., it generates permutations of a given GTS by applying the respective operations and forwards them to the Backend.

Classifier. This component classifies the output of the Backend based on the behavior of the monitored component, e.g., for previction/prefetching, output is classified based on the occurrence of previction/prefetching (or the previcted/prefetched addresses). For every behavior, the classifier generates a *bit table* containing the *binary representation* of mutated instruction operands, e.g., accessed addresses for cache line mutation. Fig. 4 shows an example of a bit table generated for previction. Each testcase is represented by one row in the table, each column represents a loaded address.

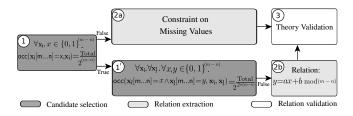

**Analyzer.** The analyzer extracts relations between inputs and their effect on the monitored microarchitectural behavior of the component. It exposes a set of primitive operations over bit tables to generate and validate such relations. Our primitives have similar meaning as SQL statements. Examples include: (a) count() which counts the number of rows (or columns) in a table; (b) the variadic function  $select(cond(\mathbf{x}_i[m_i \dots n_i], \dots), \mathbf{x}_i[m_i \dots n_i], \dots)$  that returns all rows whose fields are in the relation cond, e.g.,  $select(\mathbf{x}_i[j] = 1, \mathbf{x}_i)$  returns rows where the jth bit of the register  $\mathbf{x}_i$  is 1; (c) the variadic function  $relation(\mathbf{x}_i[m_i \dots n_i], \mathbf{x}_j[m_j \dots n_j], \dots)$  which takes two or more inputs and returns a linear relation over specific bits of the inputs. We define an example analyzer function for previction. Other analyzer functions typically follow the same strategy. As shown in Fig. 5, this function has three phases:

Candidate selection. This step pinpoints parts of the inputs (i.e., specific bits from every address) that are correlated with the observed behavior (e.g., previction). Let  $\circ$  denote function composition; occ =  $count \circ select$  defines the composition of count and select. The analyzer determines the candidate bits as follows:

For every address  $\mathbf{x}_i$ , the analyzer uses  $\operatorname{occ}(\mathbf{x}_i[m \dots n] = x, \mathbf{x}_i)$  to find the number of occurrences of each possible value  $x \in \{0, 1\}^{(m-n)}$  for the *non-constant bit sequence* indexed by m and n, i.e., mutated bits (step ①). It compares these actual occurrences

Figure 5: The analyzer function flowchart for previction.

to the expected number of occurrences of this value, i.e., it checks whether  $\operatorname{occ}(\mathbf{x}_i[m\dots n]=x,\mathbf{x}_i)=\frac{\operatorname{Total}}{\operatorname{n}_{\operatorname{pos}}};$  where Total denotes the size of the bit table; and  $\operatorname{n}_{\operatorname{pos}}=2^{(m-n)}$  is the number of different possible values for the bit sequence indexed by m and n. Every address where the number of occurrences of (some or all) values deviates from the expectation is marked as a *candidate address*.

If all addresses have the same number of occurrences equal to  $\frac{\text{Total}}{n_{\text{pos}}}$ , the analyzer proceeds to step ①. In this step, the analyzer repeats the previous check on pairs of operands. For every pair of operands  $\mathbf{x}_i$  and  $\mathbf{x}_j$  the analyzer checks whether  $\text{occ}(\mathbf{x}_i[m \dots n] = x \land \mathbf{x}_j[m \dots n] = y, \mathbf{x}_i, \mathbf{x}_j) = \frac{\text{Total}}{n_{\text{pos}}'}$ , for all possible values  $x, y \in \{0, 1\}^{(m-n)}$ , where  $n_{\text{pos}}' = 2^{2 \times (m-n)}$  is the number of possible values for the two bit sequences. Every pair of addresses for which the number of occurrences of (some or all) values deviates from the expectation is marked as a pair of *candidate interrelated addresses*.

Relation extraction. Next, the analyzer detects the constraints on certain bits in a candidate address or the interrelation between bits in candidate interrelated addresses. In step ②, the analyzer uses occ to determine these constraints by checking every candidate address for the missing values. In step ③, the analyzer uses the function  $relation(\mathbf{x}_i[m \dots n], \mathbf{x}_j[m \dots n])$  to find the interrelation between the non-constant bits of interrelated candidate addresses. It finds a and b in the equation  $y = ax + b \mod (m - n)$ , where x and y represent the interrelated bits in the two addresses, respectively.

*Relation validation.* ③ This phase validates the generated constraints and relations. A constraint is validated by using the occ function to check whether all value combinations of unrelated bits occur in the bit table. A relation is validated by using occ("y = ax + b",  $\mathbf{x}_i[m \dots n]$ ,  $\mathbf{x}_j[m \dots n]$ ) to check whether: (i) every row in the bit table satisfies the extracted relation and (ii) every value combination of unrelated bits occurs in the bit table.

#### 5.2 Backend

The Backend is responsible for generating concrete testcases (a set of programs and their inputs) from a GTS, setting up microarchitectural components, executing the programs over their respective inputs on real hardware, and returning the microarchitectural behavior of this execution. The Backend is formed of two components:

**Instantiator.** This component receives an expanded GTS from the Preprocessor and generates concrete testcases. It uses an instruction store to pick instructions for each operation when generating programs. It further uses an address store to generate inputs. In particular, for the first occurrence of every tag and/or set attribute value, the generator picks random values from the store and queries their corresponding address. For every consecutive occurrence of a

Table 2: Approximate total execution time for the experiments. d, m and s stand for day(s), minute(s) and second(s).

|         | Execution time |      |            |            |              |      |

|---------|----------------|------|------------|------------|--------------|------|

| ^       | Eviction 62m   |      |            |            |              |      |

| study   | Previction     | E1   | E2         | E3         | E4           | E5   |

|         | Fieviction     | 0.7d | 6 <i>s</i> | 7 <i>m</i> | 1.5 <i>d</i> | > 1s |

| Case    | Prefetching    | E6   | E7         | E8         | E9           | E10  |

| $\circ$ |                | 4d   | 6 <i>m</i> | > 1s       | > 1s         | 0.2d |

tag or set, the generator uses the previously selected tag and/or set from the first occurrence. In the case of arithmetic relation between these attributes, the generator searches for addresses that satisfy this relation. Alternatively, the Testcase Instantiator can generate new addresses and add them to the address store. Finally, the Instantiator generates and/or mutates inputs of instructions as requested. For example, when the GTS includes an offset mutation operator, the generator generates inputs with all possible address combinations by brute forcing their word offset. The generated testcases are forwarded to the Runner. When the cache line mutation operator is used, the Instantiator generates inputs with all possible address combinations by brute forcing the set index.

Runner. The Testcase Runner receives a testcase from the Instantiator to be executed on the hardware. The Runner first inserts memory barriers between the program's instructions. It then connects to the hardware, and refreshes the microarchitectural state, e.g., clears the cache. The Runner then sets up microarchitectural components by executing the precondition part of the program. The program is then executed using ARM TrustZone. ARM TrustZone provides the highest level of privilege that allows the execution of all possible instructions as well as the inspection of microarchitectural states. Most importantly, TrustZone provides direct access to the cache state through privileged debug instructions. Having said that, Plumber may also leverage other techniques to infer the microarchitectural state (e.g., Reload+Time typically used in cache side-channel attacks [34, 53] to infer the content of the cache) if such special debug instructions are unavailable.

We conduct our experiments as bare-metal code—there are no background processes or interrupts which could induce noise in terms of cache content or timing. We still experience a low amount of noise due to the shared memory subsystem (such as the GPU) and because our experiments are not synchronized with the memory controller. We found that this noise could be safely ignored.

#### 6 APPLICATION

We show the utility of LTs and the effectiveness of Plumber through three case studies: cache eviction policy, previction and prefetching. For each case the presented LT is only a fragment of the identified LT. Missing cases are omitted due to either (1) clarity, i.e., complex relations are omitted, or (2) inconclusive outcome, i.e., cases that generate random behavior and may not be reliably exploited. Experiments are done on Raspberry Pi 3 & 4— widely used ARMv8 platforms, which use Cortex-A53 and -A72 CPUs, respectively. On these processors, data is transferred between memory and cache in blocks of 64 bytes and the L1 data cache is 4-way set associative.

Cortex-A53 cores show the previction behavior, and although the CPU is well-documented, the *exact* behavior of the prefetcher on these cores is unknown. For example, the ARM manuals do not answer any of the following questions: (Q1) How much data is prefetched? (Q2) Do non-memory operations influence the prefetching behavior? And (Q3), do load operations in one page affect prefetching due to memory loads from a different page?

To perform the experiments, we used a cluster of five Raspberry Pi 3 and one Pi 4 boards. Table 2 shows the approximate total execution time to perform each experiment. Note that each experiment is a one-time effort required once per side channel and architecture.

# 6.1 Case Study: Eviction

To best illustrate the utility of LTs, we use Plumber to analyze the ARM Cortex-A72 cache eviction behavior. For experiment generation we leverage the parameterized eviction strategy from Rowhammer.js [13] for x86 architectures and adopted in ARMageddon [22] for ARM CPUs. The eviction strategy is shown in Algorithm 1.

Algorithm 1: Parameterized eviction strategy

```

1 for (s = 0; s \le S - D; s += L) do

2 for (c = 0; c \le C; c += 1) do

3 for (d = 0; d \le D; d += 1) do

4 *a[s + d];

```

For this experiment, we created the following GTS which corresponds to the parameterized eviction strategy:

$\begin{array}{l} \left|P\left(M_{t_2,S_1} \ \left[\left[\left[M_{t_1,S_1}\right]M_t,D,1\right]C\right]M_t,S,L\right)M_{t_2,S_1}\right|1000\\ \text{where each experiment is repeated 1000 times. The results were classified based on the existence of the pre-loaded address, indicating whether eviction occurred. Based on the results, the LT in Fig. 6.a was generated. The generated LT has an error tolerance of 5%, i.e., testcases that lead to eviction in more than 95% of the times where classified as triggering (<math>\bullet$ ) behaviors.

The eviction test characterized by the parameterized eviction strategy is not a typical use case for Plumber. However, it is suitable for illustrating LTs. This test also demonstrates how Plumber facilitates reverse engineering tasks as will be shown in § 10.

# 6.2 Case Study: Previction

We used Scam-V [28] to generate a set of leakage witnesses, i.e., programs that may cause previction on the ARM Cortex-A53 (see § 2.1). All the generated examples were formed of exactly five load instructions. Moreover, looking at the cache content, it was evident that all leakage witnesses loaded three different tags to the same cache set (and optionally a fourth tag to a different set), i.e., two to three loads targeted the same cache line. We exploit this knowledge to construct initial GTSes. We use these GTSes in five experiments (E1–E5) to iteratively refine an LT for previction:

E1: Minimal Code. First, we wanted to check whether the obtained leakage witnesses contain minimal programs that trigger previction. We created a GTS which generates testcases containing all possible subsets (without repetition) of all instructions of each leakage witness. The GTS further mutated the word offsets for each of the loaded addresses. None of the generated testcases triggered previction. Thus, the leakage witnesses contained minimal previction programs.

| ( ((ldr $\times 0$ ,[pa])^D)^C )S-D/L Step size: $d+=1; s+=L$ Stop condition: $D \le d; S-D \le s$ | Behavior and Relations     B   $\Re(A,b)$ • sameSet(x <sub>1</sub> ) ∧ (D = 3∧3 ≤ C ≤ 4∧L = 1∧22 ≤ S ≤ 23 ∨  D = 4∧4 ≤ C ≤ 6∧L = 1∧19 ≤ S ≤ 22 ∨  D = 5∧3 ≤ C ≤ 6∧L = 1∧18 ≤ S ≤ 22 ∨  D = 6 ∧ C = 6 ∧ L = 1 ∧ 18 ≤ S ≤ 22)  • Negation of the condition • | 1dr x0, [x1] | $ \begin{array}{c} \operatorname{dis}(x_1) + \operatorname{Dis}(x_2) + 1 \operatorname{Ind}(x_1) \\ \vee \\ (\operatorname{sameTag}(x_2, x_3, x_4) \wedge \\ \operatorname{sameSet}(x_1, x_2, x_3, x_4, x_5) \wedge \\ \operatorname{bus}(x_1) \neq \operatorname{bus}(x_2) + 1 \operatorname{mod}(4) \\ \operatorname{bus}(x_1) \neq \operatorname{bus}(x_2) + 2 \operatorname{mod}(4) \\ \vee \cdots \\ \operatorname{Negation of the condition} \bullet \\ \end{array} $ | Let a a a a a a a a a a a a a a a a a a a | $ \begin{array}{l} -samePage(a_{\min}, a_{\max}) \vee \\ -samePage(a_{\max}, a_{\max} + d_1) \\ (N_3 \vee N_4 \vee N_7) \wedge \neg samePage(a_{\max}, a_{\max} + 2d_1) \\ (N_3 \vee N_4 \vee N_7) \wedge \neg samePage(a_{\max}, a_{\max} + 3d_1) \\ N_3 \vee (N_4 \vee N_7) \wedge \neg samePage(a_{\max}, a_{\max} + 3d_1) \\ N_4 \vee (N_7 \wedge n-samePage(a_{\max}, a_{\max} + 3d_1)) \\ N_7 \wedge \neg samePage(a_{\max}, a_{\max} + 5d_1) \\ N_7 \wedge \neg samePage(a_{\max}, a_{\max} + 7d_1) \\ N_7 \wedge \neg samePage(a_{\max}, a_{\max} + 7d_1) \\ N_7 \end{pmatrix} \\ \\ N_7 \end{array} $ |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a)                                                                                                | Cache Eviction                                                                                                                                                                                                                                             | (b           | o) Previction                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                           | (c) Prefetching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Figure 6: Case studies' LTs with selected relations. In (a)  $a^b$  means b times inlining repetition of instruction a. In (b),  $\#n_i$  is inlining  $n_i$  simple arithmetic, logical or nop instructions. For (a) and (b) triggering and not triggering behavior are denoted by  $\bullet$  and  $\circ$ , respectively. In (c),  $P_l$  denotes distinguishing behaviors and l is the number of prefetched lines. Relations must be checked in order, the first matching relation determines the number of expected prefetches.

Table 3: Example permutation outcome. Each number represents an instruction from the initial testcase. Underlined numbers are loads from addresses that have the same tag.

| PR  | 1-2-3-4-5, 1-2-3-5-4, 2-1-3-4-5, 2-1-3-5-4,<br>4-1-2-3-5, 4-2-1-3-5, 4-3-1-2-5, 4-1-3-2-5,<br>5-1-2-3-4, 5-2-1-3-4, 5-3-1-2-4, 5-1-3-2-4                                                   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nPR | $\underline{2} - \underline{3} - \underline{1} - 5 - 4, \dots, \underline{2} - \underline{3} - \underline{1} - 4 - 5, \dots, \underline{3} - 4 - \underline{1} - 5 - \underline{2}, \dots$ |

Performing **E1** requires doing 4 sets of experiments, each consisting of  $5!/(5-x)! \times 16^x$  testcases, where  $1 \le x \le 4$ . Table 2 shows the total execution time to perform this experiment.

**E2: Order of Instructions.** Next, we checked whether the order of instructions affects previction. We created GTSes which generate testcases containing all possible permutations of instructions in distinct leakage witnesses, e.g.,  $(M_{t_1,s_1} \ M_{t_1,s_1} \ M_{t_1,s_1} \ M_{t_2,s_1} \ M_{t_3,s_1})!$ . In this GTS, the first three loads (denoted as  $\underline{1},\underline{2}$  and  $\underline{3}$ ) target the same cache line, but at different offsets. The outcome of the permutation is shown in Table 3. PR (first row) denotes previction and nPR (second row) denotes that no previction occurred. We draw three conclusions from this test:

- *Relation on tags:* The relation between the location of tags affects previction. Only programs with three consecutive load instructions with the same tag cause previction.

- Tag value: The exact tag value and location of the three consecutive loads does not matter, and can be similarly arbitrary for the non-consecutive load instructions.

- Word offset: Previction behavior differs based on the byte (word) offset of the loaded addresses. In our example, multiple programs with the same order of cache sets and tags are in both PR and nPR, e.g., 2-1-3-5-4 (PR) and 2-3-1-5-4 (nPR). These permutations have instructions 1 and 3 swapped, i.e., two load instructions that only differ in their word offset.

E3: Tags and Sets. We also checked the effect of exact tag and set values on previction. We created GTSes which generate test-cases that preserve the relations between tags and/or sets of loaded addresses, while randomly changing these addresses:

For every GTS, all 10,000 generated testcases show the same behavior. Thus, the exact values of tags and sets do not matter.

**E4: Word Offset Behavior.** In E2, we observed that the byte offsets of loaded addresses affect previction. To broaden our understanding, in this experiment, we leveraged GTSes as shown in Table 4. They generate testcases for 5-load programs with all possible combinations of tags and sets (for loads targeting up to two cache sets) while mutating the word offset. On Cortex-A53, each cache line (64 bytes) is divided into four disjoint "buses" of 16 bytes (i.e. a cache line is loaded in 4 bus rounds). For example, for three tag-identical loads in a sequence of five set-identical loads, previction occurs if the bus of the first load is not the direct successor to the bus targeted by the second load.

This experiment took approximately 1.5 days to complete. The most time consuming part of this experiment is the case number 12 in Table 4 which consists of  $12 \times 16^5$  testcases.

**E5: Priming the Cache.** We further checked if previction also affects data cached before the execution of a testcase. We created GTSes which generate and execute previction testcases while 1-4 lines of a cache set are occupied:

The results show that when the targeted set is half full (the second GTS), one of the two preloaded cache lines is evicted. As we will show, this insight may result in a side-channel attack (see § 8).

Previction Leakage Template. Our experiments resulted in LTs that allow us to identify previction side channels in applications. Fig. 6.b illustrates an example LT. Each of the experiments substantially refined this template. E1 dictated the general structure of five loads; E2 contributed to the set and tag affinity; E3 showed that we do not need to constrain certain tag/set values; E4 revealed the bus relationship; and E5 gave auxiliary information

Table 4: Example GTSes used as input to PLUMBER

|            | Requests                                                                                             | description     |

|------------|------------------------------------------------------------------------------------------------------|-----------------|

| (1)        | ⟨[M]5⟩@                                                                                              | 1 Tag & 1 Set   |

| (2)<br>(3) | $\langle [M_{t_1,s_1}] 4 M_{t_2,s_1} \rangle @ \\ \langle [M_{t_1,s_1}] 3 [M_{t_2,s_1}] 2 \rangle @$ | 2 Tags & 1 Set  |

|            | •••                                                                                                  |                 |

| (12)       | $\langle M_{t_1,s_1} \ M_{t_2,s_1} \ M_{t_3,s_1} \ M_{t_4,s_1} \ M_{t_5,s_2} \rangle @$              | 5 Tags & 2 Sets |

about previction behavior when caches are primed. E7 explains how we derived the wildcard instructions between the loads.

# 6.3 Case Study: Prefetching

Based on the ARM Cortex-A53's reference manual, prefetching could leak the (1) number of loads, (2) relation between loaded addresses (a.k.a. *stride*), (3) cache miss occurrences, and (4) end of a page. These characteristics are not sensitive, as they can be extracted from the cache content even in the absence of prefetching. We aim at validating the documented behavior, and also examine whether the undocumented behavior could leak sensitive information. To this end, we again design five experiments (E6–E10).

**E6:** Prerequisites for Prefetching. First, we wanted to devise necessary conditions for prefetching and determine the number of prefetched cache lines (Q1). We created GTSes which generate testcases for all possible programs consisting of (three to five)<sup>1</sup> loads while mutating their set index:

$$\langle [M_{t_1,s_1}]3 \rangle \$, \langle [M_{t_1,s_1}]4 \rangle \$, \langle [M_{t_1,s_1}]5 \rangle \$.$$

The main outcome of this test is an LT describing the relations between loaded cache lines and the number of prefetched addresses. Consider the GTS  $M_{t_1,s_1}$   $M_{t_1,s_2}$   $M_{t_1,s_3}$ . Prefetching occurs when  $s_3 - s_2 = s_2 - s_1 \leq \delta_{max}$ , where  $\delta_{max} = 4$  denotes the maximum stride. Moreover, programs with 3–4 consecutive loads trigger the prefetching of 3 additional cache lines, while streams with 5 loads lead to 4 prefetched addresses.

For prefetching, **E6** is the most time consuming case, as it consists of 3 sets of experiment each containing  $2^{(7\times x)}$  testcases of x-loads programs, where  $x \in \{3,4,5\}$ . For the x=3 case we have done the full experiment but for the two other cases we have fixed a few bits (1 and 2 bits resp.) of the set indices to make the experiment manageable. Overall this experiment took 4 days to complete: 0.2d for x=3, 1d for x=4 and 2.8d for x=5.

**E7: Intermediate Instructions.** Next, we wanted to check the effect of intervening instructions on prefetching (**Q2**). For this, we have created GTSes which generate testcases containing programs with a fixed stride and a varying number of intermediate arithmetic instructions. For  $0 < n \le 100$  and  $0 < m \le 30$  we created:

- $(1) \ M_{t_1,s_1} \quad \text{[A]} n \ M_{t_1,s_1+1} \ M_{t_2,s_1+2} \ M_{t_1,s_1+3}$

- (2)  $M_{t_1,s_1}$   $M_{t_1,s_1+1}$  [A]n  $M_{t_2,s_1+2}$   $M_{t_1,s_1+3}$

- (3)  $M_{t_1,s_1}$   $M_{t_1,s_1+1}$   $M_{t_2,s_1+2}$  [A] n  $M_{t_1,s_1+3}$

- (4)  $M_{t_1,s_1}$  [A]m  $M_{t_1,s_1+1}$  [A]m  $M_{t_2,s_1+2}$  [A]m  $M_{t_1,s_1+3}$

We created similar GTSes for 3- and 6-load streams.

Our results showed that adding instructions between consecutive loads could alter the number of prefetched addresses, e.g., adding 3 arithmetic instructions between two consecutive loads can increase the number of prefetched addresses from 3 to 4. Similarly, adding

4 arithmetic instructions increases this number to 7 and adding 5 instructions reduces it again to 3. Thus, the prefetcher may leak the control flow at the granularity of one instruction, a new insight which may lead to potential side channels (see § 8).

**E8: Respecting Page Boundary.** We also checked whether prefetching respects page boundaries (as stated in the manual), i.e., if the processor prefetches addresses past the end of a page (Q3). To this end, we created GTSes to generate testcases containing programs with fixed strides while gradually shifting the loaded addresses toward the next page, i.e., up to one page (64\*64 = 4096). For  $0 < n \le 5$  we created:

- (1)  $(M_{t_1,s_1} \ M_{t_1,s_1+n} \ M_{t_1,s_1+2n})64$

- (2)  $(M_{t_1,s_1} \ M_{t_1,s_1+n} \ M_{t_1,s_1+2n} \ M_{t_1,s_1+3n})64$

- (3)  $(M_{t_1,s_1} \ M_{t_1,s_1+n} \ M_{t_1,s_1+2n} \ M_{t_1,s_1+3n} \ M_{t_1,s_1+4n})$ 64

The results show that testcases at the end of the page had fewer prefetched cache lines as not to cross page boundary. Testcases with loads spread across different pages did not cause prefetching.

**E9: Multiple Prefetching Sequences.** We now explore how the prefetcher handles multiple, possibly interleaving sequences. To this end, we specify a GTS that merges three 3-load sequences with distinct tags and sets, i.e., from different memory pages.

Our results show that the prefetcher becomes active for only the first two sequences; any additional sequence will *not* be prefetched. To decide which one is first, the prefetcher picks the first sequences of three consecutive loads (two strides). This means that multiple independent sequences can cause interference, even if they are on different pages (Q3). Again, this novel observation can lead to potential side channels to leak information (§ 8).

**E10:** Cache Hits. Finally, we tested the influence of cache hits on prefetching. We created GTSes, which generated and executed prefetching testcases while one of the loaded addresses is cached:

- (1)  $P(M_{t_1,s_1})\langle M_{t_1,s_1} M_{t_1,s_1+1} M_{t_1,s_1+2} \rangle$ \$

- $(2) \; P \big( M_{t_2,s_2} \big) M_{t_1,s_1} \;\; M_{t_2,s_2} \;\; M_{t_1,s_1+1} \;\; M_{t_1,s_1+2}$

The GTS (1) did not trigger prefetching for all generated test-cases, while the GTS (2) induced a behavior similar to that of  $M_{t_1,s_1}$ ,  $M_{t_1,s_1+1}$ ,  $M_{t_1,s_1+2}$ . Thus, the prefetcher only monitors cache misses, i.e., preloaded data may destroy sequences that would have otherwise been prefetched. This is problematic if prefetched sequences from different pages (and contexts) interfere with each other.

**Prefetching Leakage Template.** Fig. 6.c illustrates an LT for a 3-load stream, allowing to identify prefetching side channels in applications. To construct this LT: **E6** identified constraints on the cache sets; **E7** derived bounds on intermediate instructions and their effect on the prefetching behavior; **E8** refined constraints on cache sets based on page boundaries; **E9** revealed the interference between interleaving prefetching sequences; and **E10** gave auxiliary information about the effect of cache hits on prefetching.

# 7 MATCHING PREFETCHING LT IN BINARIES

We now demonstrate how an LT can be used to identify an instance of the side channel it describes in a target binary.

Target Binary and Side Channel. As a proof of concept, we re-identify a known prefetching-based side channel in OpenSSL

$<sup>^1\</sup>mathrm{We}$  chose this range as 1–2 loads do not trigger prefetching, and more than 5 loads would create too many test cases.

1.1.0g. It was first found and exploited on an Intel CPU by Shin et al. [40]. Data-dependent loads from a lookup table may or may not trigger the prefetcher to load certain cache lines into the cache, depending on the resulting memory access pattern. Therefore, the cache state of potentially prefetched cache lines indicates the existence of relations between the accessed lookup table elements and, by extension, the processed data. Shin et al. exploit these relations to leak the scalar of a scalar point multiplication on an elliptic curve. In Elliptic Curve Diffie-Hellman (ECDH), a scalar represents the private key. The attack recovers the key incrementally. The same computation is applied to both the target scalar and a candidate scalar. By changing the candidate scalar such that the prefetching behavior assimilates, both scalars assimilate as well. Even though this vulnerability is no longer present in recent OpenSSL versions, we still consider it a reasonable case study to demonstrate that LTs can be used to identify real-world vulnerabilities in binaries.

**Approach: Combining Static and Dynamic Analysis.** Shin et al. [40] limit the scope of their search to a specific cryptographic operation. In contrast, our starting point is the whole OpenSSL binary. We combine static and dynamic binary analysis techniques to search it for instances of the prefetching LT (see Fig. 6.c). First, we scan the binary for code sections that match the code pattern  $\mathcal{P}(A)$  of the LT. This results in a list of candidate code sections that potentially contain a prefetching side-channel. Second, we need to check whether a candidate section satisfies different relations  $\mathcal{R}(A,b)$  for different input values. If this is the case, we expect the section to show input-dependent behavior, indicating a side channel. Not all relations can be resolved statically, especially if they refer to addresses in instruction operands. To overcome this, we dynamically analyze the target code to learn its concrete addresses.

**Performing Static Analysis.** We use *asmregex* [5] to statically scan the target binary for the code pattern  $\mathcal{P}(A)$  of the prefetching LT. Asmregex searches binaries for code sections that match a specified pattern. We extended the tool by approx. 200 LoC (code available at [36]) to support a subset of the ARM instruction set and added support for backreferences to the pattern language. Backreferences allow to express simple relations between instructions. For instance, two subsequent load instructions can be required to use the same base address register. To identify code sections matching  $\mathcal{P}(A)$  in OpenSSL, we convert  $\mathcal{P}(A)$  into an asmregex pattern. This pattern matches 429 3-load sequences across 18 OpenSSL modules. By briefly inspecting the matching candidate sections, we identify accesses to lookup tables in 11 of these modules. The remaining matches are predominantly caused by operations on complex data structures. Most importantly, we identify the code section exploited in [40] among the candidates in the module crypto/bn/bn\_gf2m.o. Further investigation of other matches is considered out of scope.

**Performing Dynamic Analysis.** We proceed with the dynamic analysis step to check a candidate code section for input-dependent behavior using the relations  $\mathcal{R}(A,b)$  from the LT. We create a simple wrapper program that calls the matching library function with varying input values. This program can be used to log all (input-dependent) loads from the relevant lookup table SQR\_tb, which spans across three cache lines in memory. We record two different traces for each input value. First, we use Valgrind [29] and GDB [10] to record an *access trace*, a list of all loads from SQR\_tb during program execution. This trace can be used to determine the *expected*

Table 5: Confusion matrix, comparing prefetching behavior classification based on relations with the actual behavior.

|          |       | Relation-based classification |   |    |  |

|----------|-------|-------------------------------|---|----|--|

|          |       | $P_0$ $P_3$ undec             |   |    |  |

| Actual   | $P_0$ | 66                            | 0 | 0  |  |

| behavior | $P_3$ | 0                             | 6 | 28 |  |

prefetching behavior based on the relations  $\mathcal{R}(A,b)$  from the LT. Second, we use a Flush+Reload side channel to record a *cache trace*. This trace contains the cache state of the memory lines around SQR\_tb after execution. It is captured for evaluation purposes and indicates the *actual* prefetching behavior of the CPU.

In order to show that the LT accurately represents the prefetching behavior, we recorded traces for 100 random input values to the library function. For each input value, we determined the expected prefetching behavior using the access trace<sup>2</sup> and compared it with the actual behavior using the corresponding cache trace.

**Evaluation.** Table 5 illustrates the classification performance. For all 66 cases where the load instructions satisfy the relations for  $P_0$ , the cache traces show that no prefetching occurred. In six cases, the relations for behavior  $P_3$  are satisfied. The three relevant load instructions load data from three consecutive cache lines and the number of instructions between the load instructions ( $n_1$  and  $n_2$ ) is within the specified bounds. In all six cases, the cache trace shows that prefetching of three additional cache lines occurred. In the remaining 28 cases, the relations for none of the behaviors from the LT are satisfied. The reason is that the distances  $n_1$  and  $n_2$  between the relevant load instructions are outside the parameter range we tested when the LT was created. We denote these cases as undecidable cases. We note that no misclassifications occurred.

**Conclusion.** We successfully demonstrated that the prefetcher of the Cortex-A53 CPU shows input-dependent behavior for the library function under investigation. This is the base requirement for the differential attack in [40]. The LT helped us to re-identify this vulnerability known from the Intel architecture in ARM binary code. In contrast to prior work, our starting point was the whole OpenSSL code base. For code sections that closely match the LT (i.e., they closely correspond to code and relations that Plumber encountered during creation of the LT), the behavior classification based on the relations is accurate. When unknown relations occur, undecidable cases are more likely to appear. In our example, undecidable cases occur due to higher values of  $n_1$  and  $n_2$  than we used when creating the LT (to keep the number of test cases within a reasonable range). However, these cases can be detected and the analyst may use them to design further experiments in order to refine the LT in a targeted manner. This highlights again that a LT, which can hardly be ever complete, can be developed in an iterative fashion.

# 8 NOVEL LEAKAGE PRIMITIVES

Our experiments in § 6 also helped us to identify five novel prefetching based leakage primitives. For four of these primitives, we present a minimal code example and evaluation results of its leakage speed

<sup>&</sup>lt;sup>2</sup>As we found in § 6.3-E10 that the prefetcher only operates on cache misses, the load instructions relevant to the prefetcher are not necessarily the first three load instructions in the matching code section. Therefore, we perform our analysis based on the first three loads in each access trace that target different cache lines.

Table 6: Transmission and error rates of sota. covert channels.

| Covert channel (Element)       | Speed      | Error rate |

|--------------------------------|------------|------------|

| Liu et al. [24] (L3)           | 600 kbit/s | 1 %        |

| Pessl et al. [35] (DRAM)       | 411 kbit/s | 4.11 %     |

| Maurice et al. [26] (L3)       | 362 kbit/s | 0 %        |

| PRF_IS                         | 276 kbit/s | 0.05 %     |

| PRF_OS                         | 206 kbit/s | 2.1 %      |

| PRF_CF                         | 76 kbit/s  | 0.7 %      |

| PR_FR                          | 73 kbit/s  | 1.2 %      |

| Maurice et al. [25] (L3)       | 751 bit/s  | 5.7 %      |

| Wu et al. [52] (memory bus)    | 747 bit/s  | 0.09 %     |

| Semal et al. [39] (memory bus) | 480 bit/s  | 5.46 %     |

| Schwarz et al. [38] (DRAM)     | 11 bit/s   | 0 %        |

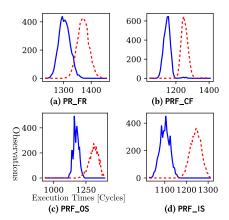

Figure 7: Histograms showing the execution time of the channel w.r.t. behavior (solid blue line) or not (dashed red line).

and error rate (see Table 6 and Fig. 7). We omit the evaluation of PR\_PP as it is not applicable in our covert channel setup.

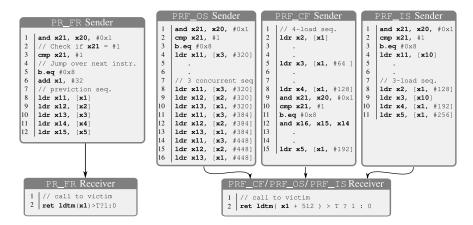

# 8.1 Previction w/ Shared Memory (PR\_FR)

Our previction-based Flush+Reload primitive PR\_FR is based on our insights from **E4** in § 6.2. Unlike traditional Flush+Reload primitives, PR\_FR allows leaking information based on a *bus* rather than cache lines. The idea is to make the (observable) occurrence of previction dependent on a secret bit (the leak target) by changing bus relations.

The primitive PR\_FR in Fig. 8 leverages the strong bus dependency between the consecutive load instructions in a valid previction sequence. Let the lines 8-12 be a valid previction sequence following our LT in Fig. 6.b, i.e., x1-x3 being consecutive loads with a "valid" bus relation, and x4/x5 arbitrary other loads from the same set. The idea is to use a secret-dependent conditional change to the byte offset of the first load (x1) to destroy previction (lines 1 through 6). That is, the word offset of the first address loaded (in x1) depends on the value of the least significant bit of the data stored in x20. According to the LT, the relation between the offsets in the addresses in x1 and x2 determines if x1 will be previcted from the cache. Thus, by measuring the time required to load from the

address stored in x1, the receiver can learn whether this address resides in the cache and consequently leak the secret bit.

# 8.2 Previction w/o Shared Memory (PR\_PP)

Based on experiment **E5** in § 6.2, previction may target preloaded memory addresses and leak information in the absence of shared memory, e.g., through Prime+Probe. The sender code of our previction-based Prime+Probe primitive PR\_PP is similar to that of PR\_FR. However, in PR\_PP, the receiver first loads two memory lines into the targeted cache set before the execution of the sender code. The receiver then probes the lines to determine the leaked bits.

# 8.3 Prefetching Control-Flow Leakage (PRF\_CF)

PRF\_CF allows leaking the control flow of a program based on prefetching. It is based on the results of E7 in § 6.3. Fig. 8 shows an example code of PRF\_CF. The sender code has a 4-load prefetching sequence with a fixed stride (lines 2, 5, 8, and 15). The loads are separated by a number of arithmetic instructions. The instruction at line 12 is conditionally executed depending on one bit of a secret that is stored in x20 (lines 9 through 12). According to E7, the number of executed instructions within a prefetching sequence affects the number of prefetched cache lines. By measuring the time required to reload a (possibly prefetched) address x1+512, the receiver can determine whether an instruction was executed and consequently learn the secret bit.

# 8.4 Prefetching on an Interrupted Seq. (PRF\_IS)

Inspired by E7, we tested the effect of intermediate memory operations on prefetching. We observed that an intermediate load from a different page leads to prefetching of additional cache lines by a 3-load stream. PRF\_IS is based on this outcome. It also allows leaking accesses to non-shared memory through shared pages.

As shown in Fig. 8, the sender code contains a 3-load prefetching sequence with a fixed stride and an interleaving load from a different page, i.e., [x10] (lines 8 through 11). Since the processor ignores cache hits, the number of prefetched lines will depend on whether x10 is cached. Consequently, by measuring the time required to load from x1+512, the receiver can determine whether x10 has been cached and consequently learn the secret bit.

In contrast to the prefetching experiment in § 6.3, PRF\_IS checks how the prefetcher's behavior changes when it *observes* interleaved loads from different pages (i.e., across page boundaries). Note that in PRF\_IS all *predicted* addresses are within bounds of the same page (in accordance with E7).

# 8.5 Prefetching and Outstanding Seq. (PRF\_OS)