# Protecting Cache States Against Both Speculative Execution Attacks and Side-channel Attacks

Guangyuan Hu and Ruby B. Lee

Princeton University

{gh9,rblee}@princeton.edu

#### Abstract

Hardware caches are essential performance optimization features in modern processors to reduce the effective memory access time. Unfortunately, they are also the prime targets for attacks on computer processors because they are highbandwidth and reliable side or covert channels for leaking secrets. Conventional cache timing attacks typically leak secret encryption keys, while recent speculative execution attacks typically leak arbitrary illegally-obtained secrets through cache timing channels. While many hardware defenses have been proposed for each class of attacks, we show that those for conventional (non-speculative) cache timing channels do not work for all speculative execution attacks, and vice versa. We maintain that a cache is not secure unless it can defend against both of these major attack classes.

We propose a new methodology and framework for covering such relatively large attack surfaces to produce a Speculative and Timing Attack Resilient (STAR) cache subsystem. We use this to design two comprehensive secure cache architectures, STAR-FARR and STAR-NEWS, that have very low performance overheads of 5.6% and 6.8%, respectively. To the best of our knowledge, these are the first secure cache designs that cover both non-speculative cache side channels and cache-based speculative execution attacks.

Our methodology can be used to compose and check other secure cache designs. It can also be extended to other attack classes and hardware systems. Additionally, we also highlight the intrinsic security and performance benefits of a randomized cache like a real Fully Associative cache with Random Replacement (FARR) and a lower-latency, speculation-aware version (NEWS).

#### 1 Introduction

Timing-based side-channel attacks recover a secret by observing timing differences in accessing a resource shared with the victim. Caches have large timing differences between a cache hit and a cache miss. They have been frequently exploited to leak secret information. In recent speculative execution attacks, cache-based covert channels are also used to leak out secrets obtained during the transient execution of mispredicted execution paths.

In this paper, we focus on defeating attacks that use the microarchitectural cache states to leak secret information. While there are many other types of microarchitectural states that can be used as timing channels, the cache state is one of the most exploited timing channels because of its ubiquity in modern computers, its clear timing differences, high bandwidth, and state persistence that cannot be rapidly cleared.

Since both non-speculative cache side channels and speculative cache-based attacks are attacks on hardware microarchitecture, a hardware microarchitectural solution is preferred. Although many hardware defenses have been proposed to prevent information leakage from the cache state, they addressed only one of the attack families but not both. We provide the first comprehensive secure cache architectures, Speculative and Timing Attack Resilient (STAR) cache that defeat both attack families, with low performance overhead.

We present a methodology to analyze the security of various defense mechanisms. Our critical insight is that in speculative execution attacks, the sender and the receiver can be in the same security domain, thus making security domain based defenses ineffective for these attacks. On the other hand, conventional side-channel attacks assume that the send and receiver are in different security domains. Our analysis shows that none of side-channel defenses and speculative execution defenses can fully cover the attacks in the other category.

We then propose hardware security features to build a comprehensive defense. We show that a fully-associative cache with a random replacement policy (FARR) can be used to prevent contention-based (missed-based) attacks. Cross-domain hit-based attacks can be mitigated by marking the security domain of (the owner of) a cache line. We identify the samedomain, hit-based speculative execution attacks, and show that they can be defended by a new "speculatively fill the cache, but invalidate on squash (SFill-Inv)" defense which has lower cost and overhead than other defenses covering speculative cache channels.

We further show that the fully-associative cache can be replaced with a new speculation-aware cache, with the same security profile but lower access latency or power. NewCache [16,68] is a randomized cache with dynamic remapping on each cache miss, proposed to defeat contention based sidechannel attacks, and has not been broken for 15 years [8,51, 61]. We show how a comprehensive defense can be designed to also defeat speculative attacks with a speculation-aware, low-latency randomized cache inspired by NewCache.

Our key contributions are:

- Showing the attack space covering cache side-channel attacks and cache-based speculative execution attacks. Identifying speculative attacks where the sender and receiver of covert channel are in the same security domain. Showing no existing defense has fully addressed both attack classes.

- Proposing a methodology to analyze hardware security features for their coverage of the attack space. Additionally, identifying defense features with significant performance overhead (Table 1).

- Proposing a new defense feature that allows speculative cache fills with a low-cost invalidation mechanism on the infrequent squash path.

- Designing a speculation-aware, low-latency, dynamic remapping, randomized cache, inspired by the previous NewCache design [42,68].

- Designing two Speculative and Timing Attack Resilient (STAR) cache architectures, STAR-FARR and STAR-NEWS, defeating all considered cache timing attacks with low performance overhead of 5.6% and 6.8% respectively.

#### 2 Background

## 2.1 Cache Timing Side-channel Attacks

Cache side-channel attacks observe the cache access time and infer the address used by the victim.

A **hit-based cache side channel** allows an attacker to infer victim's information by observing cache hits. One common example of hit-based side channels is using the flush-reload technique, e.g., [75], with the following steps:

- 1. (Flush) The attacker first flushes all cache lines of a shared memory region from cache.

- 2. The victim accesses one of the cache lines using a secretdependent address.

- 3. (Reload) The attacker reloads all cache lines and finds a cache hit at the address just accessed by the victim. The secret can be recovered from this address.

The flush-reload cache side channel is an effective technique which can recover the secret as long as the secretdependent address is in the cache. While the first step of flushing is through the clflush instruction in the x86 architecture, it can also be achieved in other architectures by causing

| Sender Code:                        |                 |  |  |  |  |

|-------------------------------------|-----------------|--|--|--|--|

| if (x < array_size)                 | // Authorize    |  |  |  |  |

| y = array[x]                        | // Access       |  |  |  |  |

| z = shared[y*4096]                  | // Use and Send |  |  |  |  |

| Receiver Code:                      |                 |  |  |  |  |

| for i from 0 to 255                 | // Receive      |  |  |  |  |

| t[i] = TimeToReload(shared[i*4096]) |                 |  |  |  |  |

| Find the minimal t[i]               |                 |  |  |  |  |

Figure 1: The code of a Spectre-v1 Attack. The mistraining of branch predictor and the flushing of all cache blocks of *shared* happen before the sender code and are not shown.

conflicts to evict related cache lines, leading to a similar variant of the eviction-reload side channel.

A miss-based cache side channel [5, 43, 53], has the victim's secret-dependent access evicting the attacker's cache line(s). The attacker can then recover the secret value by observing where he has a cache miss when accessing the previous lines. The common example of prime-probe attack [50] leveraging cache contention consists of three steps:

- 1. (Prime) The attacker fills the cache with his cache lines.

- 2. The victim accesses a secret-dependent address, which evicts one of the attacker's cache lines.

- 3. (Probe) The attacker reaccesses his cache lines and finds a cache miss at the cache set that was accessed by the victim. Information is leaked from the evicted address.

Miss-based cache side channel attacks do not require shared memory between the victim and the attacker to succeed, making it a more practical attack than some hit-based side-channel attacks. However, the effectiveness of a miss-based cache side channel can be reduced if there are other memory accesses which introduce unrelated cache conflicts.

## 2.2 Speculative Execution Attacks

Speculative execution attacks or transient execution attacks are subtle microarchitectural attacks that leak the secret which the software should not access. Research works [10, 12, 21, 23, 72] systematically characterized these speculative execution attacks. There are 2 main operations in a speculative execution attack: illegally accessing a secret, and sending the secret out through a covert channel. [21, 23] further broke the attack down to six critical attack steps: *Setup* of microarchitectural states, *Authorize* for bypassed software authorization, *Access* for speculative secret access, *Use* to use the secret, *Send* and *Receive* for covert sending and receiving where the cache states can be used.

If the speculation was incorrect, i.e., the access is not authorized, the hardware microarchitecture backs out of the instructions speculatively executed, thus voiding the *Access*, *Use* and *Send* operations. However, since microarchitectural changes, e.g., cache state changes, are supposed to be invisible to software, they are not backed out of. Hence, a cache state change by the *Send* operation may still be visible, after the incorrect speculation is squashed, thus leaking the secret through the microarchitectural covert channel.

Variants of speculative execution attacks [4, 11, 22, 25–31, 35–37, 40, 46, 54, 59, 60, 63–66, 70] exploit different vulnerabilities that allow a transient but illegal access to secret data before this access is verified or authorized. Depending on the vulnerability exploited, the secret can be from special registers, caches, memory or other microarchitectural buffers. All the vulnerabilities can later leverage the cache channel to transmit the secret.

We show an example of Spectre-v1 attack using the flushreload cache channel in Figure 1. The sender code speculatively reads an out-of-bounds secret into y and executes the covert sending even if x is larger than the array size. The setup step (mistraining for the illegal secret access and flushing for setting up the covert channel) happen before the sender code, and is not shown.

# 3 Motivation and Threat Model

**Cache as a critical leakage channel.** There are other hardware units that can be used as the microarchitectural channel for both non-speculative and speculative attacks, e.g., the execution port [6], the miss status holding register (MSHR) usage [4] and the branch predictor states [17, 69]. However, the cache state has the following advantages for being a reliable and commonly used channel.

Distinguishable timing difference. There is a clear difference in timing, e.g., a load instruction takes a few cycles for a L1 cache hit versus hundreds of cycles for a cache miss when the main memory has to be accessed. These make cache timing channels reliable and fast.

Persistence. The cache stores cache lines that remain after the program finished or terminated. States such as port contention and MSHR usage can be protected by not scheduling concurrent processes. However, the measurement of cache lines can be done by an attack program which runs after the victim program finishes.

High cost to clear. In-core hardware states such as branch predictors can be erased or masked, e.g., with operations like indirect branch prediction barrier [2], after a program finishes or a context switch happens. However, cache is a hardware unit that has multiple cache levels and a large number of cache lines. These make it a difficult and high-cost operation in hardware to select and clear all cache lines of the victim.

High bandwidth for leakage. Compared to the usage of hardware units which can encode 1 bit of information, the address used to access the cache can encode more bits. Figure 1 shows an example of leaking 8 bits. Leaking more bits is possible by using a larger shared array.

Threat Model. Our threat model considers the attacker that

can leak a secret by making a secret-dependent cache state change. The scope includes the cache side-channel attacks where the victim's execution is non-speculative and cachebased speculative execution attacks. Specifically, we protect the addresses of cache lines and cache replacement state.

In the scope of speculative execution attacks, we consider a load being speculative if not all previous instructions have finished execution without having a fault when the load executes. This covers all forms of malicious speculative execution using different techniques, e.g., predictor mistraining, malicious jump target injection, speculative store-to-load forwarding or delayed exceptions or faults. We assume the strong attacker who can trigger speculative execution even through the victim's own behavior [60].

We protect the secret from the memory, caches, registers, microarchitectural buffers and other units, i.e., how the address of memory access is computed does not impact the protection. We assume the attacker is able to get timing measurement to detect the presence of his cache lines in various cache levels. Our solution focuses on protecting the level one (L1) data cache, which is close to the processor core and can be easily exploited for cache timing channel. The protection of shared last-level cache using techniques like encrypted set indexing [52, 53, 71] is in parallel with our work.

We do not protect against security issues due to software bugs or malicious code injection which give an attacker the permission of legal secret access. We assume the system is able to allocate security domains to software programs automatically or upon programs' request. A security-sensitive program should be assigned a unique DomainID. Security domain ID does not equate to process ID. A given process can have more than one security domain. One security domain can also comprise many processes.

We allow and protect read-only memory regions to be shared between security domains for purposes such as shared software library [19]. Sharing writable pages between security domains is dangerous as it allows direct information leakage.

We do not address physical attacks or circuit-level faults such as Rowhammer-type attacks [33, 47].

#### 4 Methodology

We propose a methodology to investigate the scope of attacks to be covered (Section 4.1), and which mechanisms defeat which attacks (Section 4.2), and what performance overhead is incurred (Section 4.3). Our critical insight from security analysis is that side-channel defenses cannot mitigate speculative execution attacks which do covert sending and receiving in the same security domain. On the other hand, the defenses against speculative execution attacks do not protect the cache state changes by the victim's authorized execution in nonspeculative cache side-channel attacks. We also present our observations of the hardware events that cause performance overhead.

| Hardware Features                                                     | Security: Coverage of Cache Attacks |                  |                 |                 |                 | acks            | Impact on Performance             |                                        |                                      |                                  |                                      |                          |

|-----------------------------------------------------------------------|-------------------------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------------------------|----------------------------------------|--------------------------------------|----------------------------------|--------------------------------------|--------------------------|

|                                                                       | NS-<br>CD-<br>FR                    | NS-<br>CD-<br>PP | S-<br>CD-<br>FR | S-<br>CD-<br>PP | S-<br>SD-<br>FR | S-<br>SD-<br>PP | Pause<br>speculative<br>execution | Disallow<br>correct-path<br>cache fill | Periodic<br>moving of<br>cache lines | Additional<br>access needed      | Stall due to<br>additional<br>access | Additional cache latency |

| 1. Cache Partitioning                                                 |                                     | $\checkmark$     |                 |                 |                 |                 | No                                | No                                     | No                                   | No                               | No                                   | No                       |

| 2. No hit across domains (SW defined)                                 | $\checkmark$                        | $\checkmark$     | $\checkmark$    |                 |                 |                 | No                                | No                                     | No                                   | No                               | No                                   | Hit filter               |

| 3. Encrypted cache with domain-specific keyed remapping, e.g., CEASER |                                     | $\sqrt{*}$       |                 | √*              |                 | √*              | No                                | No                                     | Yes                                  | No                               | No                                   | Encryption               |

| 4. Dynamic remapping on cache miss,<br>e.g., NewCache                 |                                     | $\checkmark$     |                 | $\checkmark$    |                 |                 | No                                | No                                     | No                                   | No                               | No                                   | Small<br>mapping table   |

| 5. Special fence preventing speculative cache fills                   |                                     |                  | $\checkmark$    | $\checkmark$    | $\checkmark$    | $\checkmark$    | No                                | Yes                                    | No                                   | No                               | No                                   | No                       |

| 6. Delay speculative data access                                      |                                     |                  | √src            | √src            | √src            | √src            | Yes                               | Delay until<br>authorized              | No                                   | No                               | No                                   | No                       |

| 7. Delay speculative data forwarding                                  |                                     |                  | √src            | √src            | √src            | √src            | Yes                               | Delay until<br>authorized              | No                                   | No                               | No                                   | No                       |

| 8. Delay speculative cache fills                                      |                                     |                  | $\checkmark$    | $\checkmark$    | $\checkmark$    | $\checkmark$    | Yes                               | Delay until<br>authorized              | No                                   | No                               | No                                   | No                       |

| 9. Buffer and redo speculative cache fills                            |                                     |                  | $\checkmark$    | $\checkmark$    |                 |                 | No                                | Delay until<br>authorized              | No                                   | For correct-path<br>(Round-trip) | Stall until<br>returned              | No                       |

| 10. Undo speculative cache evictions and fills                        |                                     |                  | $\checkmark$    | $\checkmark$    |                 |                 | No                                | No                                     | No                                   | For wrong-path<br>(Round-trip)   | Stall until<br>returned              | No                       |

| New Defense Mechanisms                                                |                                     |                  |                 |                 |                 |                 |                                   |                                        |                                      |                                  |                                      |                          |

| Domain-tagged cache to prevent cross-<br>domain hits ( <b>NoHit</b> ) | $\checkmark$                        |                  | $\checkmark$    |                 |                 |                 | No                                | No                                     | No                                   | No                               | No                                   | No                       |

| Fully-associative cache with random replacement (FARR)                |                                     | $\checkmark$     |                 | $\checkmark$    |                 | $\checkmark$    | No                                | No                                     | No                                   | No                               | No                                   | Large<br>mapping table   |

| NewCache with Speculation resilience (NEWS)                           |                                     | $\checkmark$     |                 | $\checkmark$    |                 | $\checkmark$    | No                                | Upon tag<br>miss                       | No                                   | No                               | No                                   | Small<br>mapping table   |

| Speculative cache fill + Invalidate<br>(SFill-Inv)                    |                                     |                  |                 |                 | $\checkmark$    |                 | No                                | No                                     | No                                   | For wrong-path<br>(One way)      | Stall until<br>issued                | No                       |

| Comprehensive Defenses                                                |                                     |                  |                 |                 |                 |                 |                                   |                                        |                                      |                                  |                                      |                          |

| STAR-FARR<br>(SFill-Inv + NoHit + FARR)                               |                                     |                  | $\checkmark$    | $\checkmark$    | $\checkmark$    | $\checkmark$    | No                                | No                                     | No                                   | For wrong-path<br>(One way)      | Stall until<br>issued                | Large<br>mapping table   |

| STAR-NEWS<br>(SFill-Inv + NoHit + NEWS)                               |                                     | $\checkmark$     | $\checkmark$    | $\checkmark$    | $\checkmark$    | $\checkmark$    | No                                | Upon tag<br>miss                       | No                                   | For wrong-path<br>(One way)      | Stall until<br>issued                | Small<br>mapping table   |

Table 1: Defense mechanisms against different cache timing attacks. NS is the non-speculative side-channel attack and S is the speculative execution attack. CD stands for a cross-domain attack and SD for a same-domain attack. FR stands for the flush-reload cache channel and PP for the prime-probe cache channel.  $\checkmark$ \* means the security relies on the design parameter.  $\checkmark$  src means the defense protects certain sources of secret, which are usually caches and memory.

## 4.1 Similarities and Differences of Attacks

Cache timing attacks include two families of non-speculative (NS) execution attacks and speculative (S) execution attacks. There are two further dimensions: hit-based (exemplified by the Flush-Reload attack, FR) vs miss-based (examplified by the Prime-Probe attack, PP) attacks, and cross-domain (CD) vs same-domain (SD) attacks. This gives rise to the 6 classes of attacks shown by the columns in Table 1.

Both non-speculative and and speculative attack families use either a hit-based or a miss-based channel. The cache states are prepared and measured in the same way (see Section 2). The state change is made by the victim's load either non-speculatively or speculatively.

A critical difference between the non-speculative sidechannel attacks and the speculative execution attacks, is that the sender and the receiver can be either in the same domain or different domains. For non-speculative conventional cache side channels, the attacker and the victim are in different security domains. A same-domain attacker with legal permission can access and leak the secret directly instead of leveraging side channels. In speculative execution attacks, the sender and the receiver can be in the same domain or in different domains. The same-domain attack is more dangerous and has been shown to be practical [24, 46].

#### 4.2 Analysis of Past Hardware Defenses

Table 1 shows the security analysis on what cache-based attacks are mitigated by each of the hardware features. Rows 1 to 10 are features implemented by hardware defenses in past work. The columns are the six types of cache timing attacks (see Section 4.1). A checkmark in the table means the hardware feature is able to prevent the corresponding attack. **Side-channel defenses.** Secure caches against cache side-channel attacks has two major directions. The first direction is to partition the cache resources between security domains [9, 15, 41, 49, 67] (row 1). This method prevents the leakage through secret-dependent cache evictions if the system can separate the victim and the attacker. Advanced designs, e.g.,

DAWG [34] and Hybcache [14], implement mechanisms to filter cache hits (row 2) to also prevent the cross-domain hitbased attacks.

The second direction is randomizing the cache change, so the attacker gets no useful information. The keyed remapping in row 3, e.g., CEASER [52] and ScatterCache [71], uses the domain-specific keys to randomize cache line placement. To prevent eviction set based attacks [43,53], the key needs to be changed periodically, which requires existing cache lines to be moved to adapt to the new mapping. The period of rekeying may impact its security against same-domain prime-probe speculative execution attacks ( $\checkmark$ \* in Table 1) [8,51,61].

Dynamic remapping caches in row 4, e.g., RPCache [67] and NewCache [42, 68], randomly replace cache lines on contention-based evictions, so the attacker cannot get any useful information about the cache lines used by the victim. They can mitigate all miss-based cache side-channels, including the ones based on measuring the time taken by a whole operation (e.g., encryption of a whole block) rather than just the time taken for a single memory access. Since these attacks, e.g., the Evict-Time attack [5], are much slower, we do not consider them here. NewCache [42] uses the terms Domain ID and P-bit to define security domains for different cache lines. The dynamic remapping effectively does remapping on every cache miss and has not been broken in recent studies of randomized caches [8,51,61]. We study if it can be used for a comprehensive solution for both cache side-channel attacks and speculative cache-based attacks.

Previously, dynamic remapping was mainly applied to L1 caches while the keyed remapping was applied to last-level caches (LLC's). We envision the future that both techniques could be used for either cache level, with the emergence of designs for pseudo fully-associative LLC's [56] and high-performance hardware lookup tables [45].

We note that side-channel defenses cannot defend against same-domain speculative execution attacks.

**Defenses against speculative execution attacks.** Defenses against speculative execution attacks can be categorized as preventing the *Setup* of microarchitectural states, preventing the secret *Access*, preventing the *Use* of secret and preventing the state change by *Send* operations [21].

Protection against malicious *Setup*, e.g., by encrypting or flushing predictor states [2, 20, 62], does not prevent non-speculative cache side-channel attacks and the strong attacker who can trigger speculative execution from the same domain. We do not include it in Table 1.

A defense can delay the speculative execution until it is authorized. Row 6 in Table 1 includes mechanisms to delay the speculative secret access, e.g., Context-sensitive Fencing [62] and secure bounds check [48]. Row 7 analyzes defenses delaying the forwarding (use) of secret, e.g., NDA [69], SpectreGuard [18], ConTExT [58], SpecShield [3] and STT [76]. These defenses can mitigate multiple covert channels but can only protect specified accesses such as loads of memory or

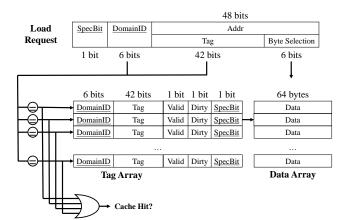

Figure 2: Architecture of STAR-FARR. DomainID and SpecBit are attached to memory requests and cache lines to indicate the owner and the speculation status.

special register reads.

Specific to the cache state, a special fence (row 5) can be inserted to make a speculative load uncacheable to avoid fetching new cache lines [62]. A defense can delay only speculative loads which have a cache miss (row 8), e.g., Conditional Speculation [39], Efficient Speculation [57] and DOLMA [44]. Speculative cache lines can also be put in a special buffer (row 9) and made visible once it is authorized, e.g., InvisiSpec [73], SafeSpec [32] and MuonTrap [1].

To improve the performance with the insight that most of the instructions in benign programs are not squashed, a defense can also allow speculative cache fills and restore the cache state if the execution is squashed (row 10). Cleanup-Spec [55], for each squahsed loads, removes the speculatively fetched cache line and refetches the evicted cache line. However, CleanupSpec needs to wait until the restoration is finished. The wait time is found to be secret-dependent and measureable in the unXpec attack [38].

These defenses can mitigate cache-based speculative execution attacks either from the same domain or a different domain. However, these defenses against speculative execution attacks will not defeat non-speculative side-channel attacks as the victim's execution will not be squashed.

**Takeaways.** We show that none of the existing cache defenses can cover both the same-domain speculative execution attacks and the non-speculative side-channel attacks. Hence, our goal is to design a secure cache that covers all of these attacks with minimal performance impact and hardware complexity.

## 4.3 Factors of Performance Overhead

We identify six types of hardware events which lead to performance degradation by the defenses in Table 1. A good defense should try to reduce the possibility of all these events happening while maintaining the coverage of attacks. **Delay correct-path execution.** Defenses on rows 6 to 8 delay the execution and related cache fills of speculative instructions. This can cause severe performance overhead as the correctpath execution is more frequent.

**Disallow correct-path cache fill.** Cache fills are critical for performance. While permitting speculative data accesses, fill-prevention fences on row 5 may disallow a large portion of cache fills if implemented with the strict threat model.

**Periodic moving of cache lines.** Periodic moving of existing cache lines is required as the keyed remapping defense (row 2) changes the mapping of address to cache line. It is a heavy-weight hardware operation to examine existing cache lines for their ownership and perform manipulation.

Additional access needed. Defenses using speculative buffers (row 9) need a second access to redo accesses for more frequent correct-path execution. It is a round-trip operation in cache to access the address and refetch it into the cache. Fill-and-undo defenses (row 10) need to both invalidate the speculatively accessed address and refill the evicted address if the speculative execution is squashed (wrong-path).

Undo-based defenses can be intrinsically better in terms of performance overhead since they do extra work on the less frequent, wrong speculation path. However, CleanupSpec has to bring back the evicted cache line to the L1 cache which is complicated and timing consuming.

**Stall due to additional access.** Defenses using speculative buffers (row 9) need to stall the commit of speculative instructions as the validity of speculatively accessed data needs to be verified. Fill-and-restore defenses (row 10) also need to stall the execution of later memory operations before the restoration is finished.

Additional cache latency. Hardware units required by defenses may add to the cache access latency time, e.g., encryption for randomization and large fully-associative caches.

# 5 STAR Cache Architecture

#### 5.1 Overview

Speculative and Timing Attack Resilient (STAR) Cache is a comprehensive defense against both speculative execution and side-channel attacks. To cover the non-speculative cache side-channel attacks in Table 1, we suggest using some form of randomized cache for contention-based PP attacks and a security domain field to disallow cache hits across domains for FR attacks. These cover all the attack columns in Table 1 for both non-speculative and speculative execution attacks except for the same domain speculative flush-reload attacks. We propose a low-cost and high-performance solution to this (*SFill-Inv*).

We introduce the following four new defense features and two variants of STAR Cache protecting the L1 cache. These

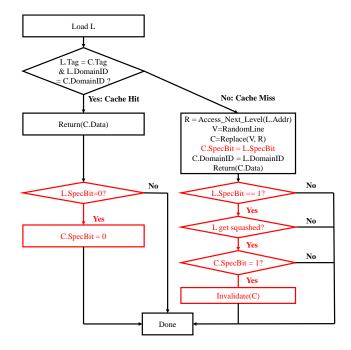

Figure 3: Load handling in STAR-FARR. Modifications to handle speculative execution attacks are shown in red.

build upon fully-associative cache with random replacement (STAR-FARR in Section 5.2) and a new speculation-aware randomized cache (STAR-NEWS in Section 5.3). They are shown to defeat all columns of attack types and compared with existing defenses in Table 1

**Domain-tagged cache to prevent cross-domain hits** (*No-Hit*). We attach DomainID's to cache lines as well as internal buffers such as miss status holding registers and write-back buffers. Memory accesses from a different domain cannot get a hit on a cache line with a different DomainID, which defeats different-domain flush-reload attacks. While the existing defense of software-defined hit filter [34] requires the system software to be aware of hardware configurations and manually allocate resources for each domain, the domain-tagged cache only requires the system software to assign DomainID's and the cache allocation is done automatically by hardware.

**Fully-associative cache with a random replacement policy**(*FARR*). We show that the *FARR*, as a basic cache architecture, provides security against miss-based cache attacks. This is because cache lines of the attacker have the equal chance to be replaced no matter what address is accessed. *FARR* also prevents the leakage through the cache replacement state.

**Speculation-aware NewCache** (*NEWS*). NewCache [42,68] has the same security profile as *FARR*. FARR is conceptually simpler but may increase access latency. The original NewCache has been shown to have the same access time as a same-size set-associative cache [16]. Inspired by New-Cache, we propose a speculative-aware cache with dynamic

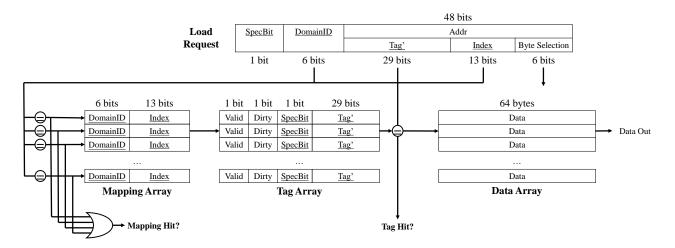

Figure 4: Architecture of NewCache-inspired STAR Cache (STAR-NEWS). New and modified fields of load requests and cache lines are underlined. For a 32kB L1 cache with 64-byte cache line size, there are with  $2^9 = 512$  cache lines so an index width of 9 bits is required. By making the index field wider by adding k bits (k = 4 in this example), it is like mapping to a logical cache that is  $2^k$  times larger. If a 48-bit address is used, the modified *Index* field has 9 + 4 = 13 bits while the *Tag*' field is 42 - 13 = 29 bits.

remapping. We show adjustments for security in Section 5.3. **Speculative cache fill and invalidate on squash (SFill-Inv).** We propose *SFill-Inv*, a new mechanism to invalidate speculatively fetched cache lines upon a squash. This is a new feature that can improve the security and also reduce performance overhead compared to the previous undo-type defense such as CleanupSpec [55]. For security, *SFill-Inv* does not require the processor to wait until completion, eliminating the root cause of the unXpec [38] attack on CleanupSpec due to measureable restoration time. For performance, it does only invalidation on squash and does not require bringing back the evicted cache line. The details of *SFill-Inv* is described in Section 5.4.

## 5.2 STAR-FARR

STAR-FARR implements speculative cache fill + invalidation (*SFill-Inv*), preventing cross-domain hit (*NoHit*) and a fully-associative cache with random replacement(*FARR*). STAR-FARR defeats all the attack columns in Table 1.

The hardware modifications of STAR-FARR are shown in Figure 2. A load request records in *SpecBit* whether it is speculatively executed and considered insecure. Store operations are always issued when it can no longer be squashed so the SpecBit of stores will always be 0. *DomainID* field in the request and in the cache line denotes the security domain of the memory operation and the cache line respectively.

Figure 3 shows the load handling in STAR-FARR. A prefix of *L*. refers to the load request, while a prefix of *C*. refers to a cache line. STAR-FARR checks the *Tag* and the *DomainID* to decide whether there is a cache hit. A non-speculative request can clear the *SpecBit* of the cache line at which it has a hit. A missing request can randomly replace an old cache line even if it is speculative. If the speculative load is squashed later, a

SFill-Inv request is sent to the cache to invalidate the address.

## 5.3 STAR-NEWS

Using fully-associative caches in STAR-FARR can increase the latency of an access, the circuit size and the power consumption. STAR-NEWS is the optimized architecture to reduces access time latency and power consumption by adopting the enhanced NewCache with speculation resilience (*NEWS*) instead of the fully-associative cache.

STAR-NEWS architecture is shown in Figure 4. The new or modified fields of load requests and cache lines are shown as underlined items. In a NewCache-like archiecture, the *Tag* field in a *FARR* (Figure 2) is divided into a shorter *Index* field and a *Tag*' field. The power needed to compare with every long *Tag* in *FARR* is reduced because the parallel comparisons are only with the shorter *Index* field. When both *DomainID* and *Index* fields match on an cache access, the comparison is done with the *Tag*' of that cache line.

STAR-NEWS allows allocating more bits in the address as index bits to represent "a bigger logical cache (than the actual physical cache size)", which is later shown to have further performance benefits. In Figure 4, we show an example with 4 extra bits allocated to the *Index* field. The mapping entry of a cache line consists of *DomainID* and *Index*, giving a dynamic address-to-cache remapping for that domain.

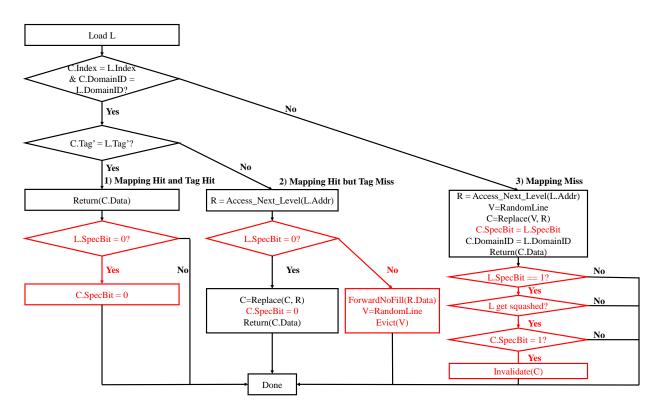

Figure 5 shows the load handling in STAR-NEWS. For memory accesses, STAR-NEWS first checks the mapping entry array to see if there is a cache line with the matching *DomainID* and Index bits.

A mapping miss happens if there is no cache line that has the same mapping entry bits as the request. The tag array is only checked if the mapping entry array has a **Mapping**

Figure 5: Load handling for STAR-NEWS. Modifications to handle speculative execution attacks are shown in red.

**Hit**. A cache hit is when the cache has both a mapping and a tag hit. If there is a mapping hit but the *Tag*' fields do not match, a tag miss happens. We show that the handling of a load request in different paths will not leak information and cannot be used to measure existing cache states.

**Mapping hit and Tag Hit.** For a cache hit, STAR-NEWS returns the data as a normal hit in conventional caches. As a side effect, if the cache line was fetched by a previous speculative memory operation (with the *SpecBit* set) and is accessed by a non-speculative operation, its *SpecBit* is cleared.

Introducing the comparison of *DomainID* when looking for a mapping hit means cache lines of shared memory region are not shared. In other words, a program from another security domain cannot get a hit at the current security domain's cache line even if the address bits match. This *NoHit* feature prevents the hit-based side-channel attacks since the attacker cannot observe a hit at the address used by the victim.

**Mapping Hit but Tag Miss.** For a mapping hit at a cache line C but a miss for *Tag*', it needs to fetch the cache line from the next level of memory. If the load is a non-speculative load with its *SpecBit* cleared, when the requested cache line R is returned, it is allowed to replace C. At the same time, STAR-NEWS will clear the *SpecBit* of R and return the data.

However, for a speculative load, replacing the cache line C can cause leakage of the address if C was placed for a same-domain speculative execution attack. Evicting C enables the attacker to infer the *Index* bits of the load address.

STAR-NEWS disallows filling the cache with R and forwards the data, which causes no leakage. In addition, STAR-NEWS needs to evict a random cache line as keeping all old lines can cause an observation different from the handling of a mapping miss which evicts one of the lines. A strong attacker can try to construct eviction sets [43, 53] from this difference. Handling speculative loads and non-speculative loads differently allows STAR-NEWS to defeat the same-domain miss-based attack (S-SD-PP in Table 1) which the original NewCache cannot prevent. This also shows that *designing a comprehensive design is not just combining different security features, and adjustment should be made to avoid introducing new attacks*.

Although STAR-NEWS protects the security, evicting a cache line but not filling the cache can lead to performance overhead. STAR-NEWS can reduce the frequency of not filling by having more bits in the index, which makes it less likely for STAR-NEWS to have a mapping hit and tag miss. It also allows the flexibility of performance tuning (see Section 6.3) while maintaining the security and the physical cache size.

**Mapping Miss.** For a mapping miss, the next level of memory is also accessed. When the requested cache line R is returned, a random cache line V is replaced by R. The *SpecBit* and the *DomainID* of R are then set to be the same as the load request. If the load is speculative and gets squashed later, the processor will send a *SFill-Inv* signal to the cache to invalidate the speculatively fetched cache line R. If R has been accessed by

some non-speculative memory operations and has its *SpecBit* cleared before the squash, R can be preserved.

In a miss-based side-channel attack, the victim will always have a mapping miss and replace the attacker's cache lines as their *DomainID*'s do not match. The randomized replacement in STAR-NEWS prevents the leakage as the victim's line can evict any of the attacker's lines with the same probability.

Similar protection is offered against speculative execution attacks. A miss-based different-domain attacker can only see a random eviction and learn nothing about the address of the speculative load L. For same-domain attacks, if the sender's speculative load has a mapping miss, it still randomly replaces a line, leaking no information to the attacker.

**Take-aways.** STAR-NEWS achieves a low-latency speculation-aware randomized cache. While inspired by New-Cache, it further solves the subtle but critical same-domain prime-probe attack exploiting the mapping hit case.

## 5.4 Implementation of SFill-Inv

We optimize the performance of our new "Speculative cache fill + Invalidate (*SFill-Inv*)" feature to reduce the pipeline stalls and round-trip memory traffic. We describe the modifications to the memory request, memory response, the squash procedure of loads and the handling of *SFill-Inv* in cache.

**Memory Request and Response.** Each memory response is extended with an extra *SourceLevel* field. *SourceLevel* records the cache level where a memory access finds the requested address. In a two-level cache system, *SourceLevel* is set to 1 for a L1 cache hit. Similarly, *SourceLevel* is set to 2 for L2 cache hit, and 3 if the the data is from memory.

Load Squash Procedure Upon a pipeline squash, squashed loads are required to send a *SFill-Inv* request to invalidate the cache line it fetched. The *SFill-Inv* request is skipped if the speculative load had an L1 cache hit and the returned *SourceLevel* was 1. *SourceLevel* is attached to the *SFill-Inv* request and used for handling. Compared to defenses which need to stall the processor until the response of the second access is returned (Section 4.3), *SFill-Inv* resumes the execution as soon as all the *SFill-Inv* requests are sent. The subtle unXpec [38] attack trying to observe the restoration time will not work as the processor only sends the *SFill-Inv* request without knowing when it will be completed.

Handling of *SFill-Inv*. We implement a low-cost *SFill-Inv* operation which does not fetch a new cache line or generate a response. This makes the *SFill-Inv* operation a one-way request, reducing half of traffics in the cache system compared to a round-trip memory request. Our implementation is based on an inclusive and write-back cache system. When a cache receives a *SFill-Inv* request, it looks up the address of *SFill-Inv*, which have three possible results.

If the address is found and the *SpecBit* of the cache line is 0, this means the cache line has been accessed by non-

| Name      | SA-LRU                                  | STAR-FARR                  | STAR-NEWS         |  |  |  |

|-----------|-----------------------------------------|----------------------------|-------------------|--|--|--|

| Processor | 1 Out-of-order X86 Core, 2GHz           |                            |                   |  |  |  |

|           | #Load queue entries: 32                 |                            |                   |  |  |  |

|           | #Store queue entries: 32                |                            |                   |  |  |  |

|           | #ROB entries: 192                       |                            |                   |  |  |  |

|           | #BTB entries: 4096                      |                            |                   |  |  |  |

|           | #RAS entries: 16                        |                            |                   |  |  |  |

| L1I Cache | 32KB, 64B cache line                    |                            |                   |  |  |  |

|           | 4 ways, 128 sets                        |                            |                   |  |  |  |

| L1D Cache | 32KB, 64B cache line                    |                            |                   |  |  |  |

|           | 8 ways, 64 sets                         | 512 ways, 1 set            | 512 cache lines   |  |  |  |

|           | LRU Replacement                         | Random Replacement         | Modified NewCache |  |  |  |

|           | 1-cycle latency                         | 1-cycle or 2-cycle latency | 1-cycle latency   |  |  |  |

| L2 Cache  | 2MB, 64B cache line, 16 ways, 2048 sets |                            |                   |  |  |  |

|           | 12-cycle latency                        |                            |                   |  |  |  |

| Memory    | 50ns delay (100 cycle)                  |                            |                   |  |  |  |

Table 2: Hardware Configurations of GEM5 Simulator.

speculative memory accesses. This cache line is considered safe and the *SFill-Inv* request can be safely dropped.

If the address is found and the *SpecBit* of the cache line is 1, the cache line is invalidated. The cache then checks the *SourceLevel* of *SFill-Inv* and sends the request to the next level if *SourceLevel* is larger than the current cache level.

If the address is not found, this could happen if the speculatively fetched cache line gets replaced or evicted before the squash. The request will propagate to the next cache level if *SourceLevel* is larger than the current cache level.

#### 5.5 Performance Impact

Considering the performance factors in Section 4.3, STAR-FARR and STAR-NEWS neither affect frequent correct-path execution nor require periodic moving of cache lines. They only perform extra work when a squash happens (infrequent wrong path) to send a light-weight *SFill-Inv* request without the need to bring back the evicted cache line. Pipeline stall time is also reduced by not waiting for *SFill-Inv*'s completion.

#### 6 Evaluation

We evaluate the security and the performance of hardware architectures whose design parameters are shown in Figure 2. We use similar size and latency parameters as InvisiSpec [73] and CleanupSpec [55] to get comparable results. The architectures are implemented in the cycle-accurate GEM5 simulator [7]. We evaluate the set-associative cache with least-recently-used replacement (SA-LRU) as the baseline.

STAR-FARR and STAR-NEWS are our proposed defenses which defeat all attacks. As the access latency of a fullyassociative cache cannot always be as small as the setassociative cache, we run experiments of STAR-FARR with both a fast design with 1-cycle latency and a slow design with 2-cycle latency. The access latency of NewCache-type L1 cache in STAR-NEWS can be as low as the set-associative cache in real circuits [16]. The L2 cache is a set-associative design representing the last-level cache (LLC). The latest secure

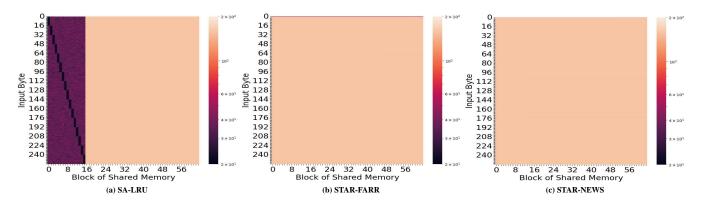

Figure 6: Flush-reload side-channel attack on AES. Lighter is longer cache access time. The key byte is 0, and the dark diagonal shows its XOR result with the input byte which leads to shorter execution time.

Figure 7: Prime-probe side-channel attack on AES. Lighter is longer cache access time. The key byte is 0, and the light diagonal shows its XOR result with the input byte which leads to longer execution time.

LLCs using randomization [52, 71] are also set-associative so the configuration can also model the timing with LLC protection before a remapping of cache sets is performed.

The security evaluation uses the following 4 representative attacks covering side-channel attacks and speculative execution attacks: (1) A flush-reload side-channel attack on the Advanced Encryption Standard (AES) algorithm. (2) A prime-probe side-channel attack on AES. (3) A Spectre-v1 speculative execution attack leveraging the flush-reload cache covert channel. (4) A Spectre-v1 speculative execution attack leveraging the prime-probe cache covert channel. For the two spectre-v1 attacks, we use a same-domain attacker which is more dangerous than a cross-domain attack.

#### 6.1 Security: Side-channel Attack

We evaluate the side-channel attacks on the first round of the AES-128 encryption process. Optimized AES implementations [13] compute its operations, *SubBytes*, *ShiftRows* and *MixColumns*, using pre-computed lookup tables. As the read addresses to lookup tables are decided by the encryption key,

a side-channel attacker can recover bits in the secret key by analyzing memory access patterns to the cache.

In the first round, the encryption algorithm reads 4 lookup tables, each of which have 256 4-byte entries. We denote the 16 bytes of input data as  $D_i$  and the 16 key bytes as  $K_i$  with i from 1 to 16. The accesses to lookup tables  $T_1$  to  $T_4$  are:

$$\begin{split} T_1[D_1 \oplus K_1], T_1[D_5 \oplus K_5], T_1[D_9 \oplus K_9], T_1[D_{13} \oplus K_{13}] \\ T_2[D_2 \oplus K_2], T_2[D_6 \oplus K_6], T_2[D_{10} \oplus K_{10}], T_2[D_{14} \oplus K_{14}] \\ T_3[D_3 \oplus K_3], T_3[D_7 \oplus K_7], T_3[D_{11} \oplus K_{11}], T_3[D_{15} \oplus K_{15}] \\ T_4[D_4 \oplus K_4], T_4[D_8 \oplus K_8], T_4[D_{12} \oplus K_{12}], T_4[D_{16} \oplus K_{16}] \end{split}$$

Each access to the lookup table brings a cache block that contains this address into the cache. We verify the security against a strong attacker who knows or controls the input data to the AES algorithm and tries to recover the key by executing memory accesses and observing timing differences. The side-channel attack on AES is repeated by 2<sup>15</sup> times with random input data and the receiver's timing measurements are averaged as the final results.

Flush-reload Side-channel Attack. A flush-reload attack can happen when the AES table is in a memory region shared

Figure 9: Prime-probe Spectre v1 attack. The secret is 30.

(b) STAR-FARR

by the attacker and the victim. To recover one key byte, the attacker flushes lookup table entries and waits for the victim to execute. As key bytes  $K_1, K_5, K_9$  and  $K_{13}$  are used to access  $T_1$  in the first round, the attacker can infer the value of these bytes by reloading all  $T_1$  entries and observing caches hits. Similarly, the attacker can flush and reload entries in  $T_2, T_3$  and  $T_4$  and recover other key bytes.

(a) SA-LRU

Figure 6 (a) shows a successful flush-reload side-channel attack on AES. The experiment represents a shared 4kB memory region (64 cache blocks as the x axis) whose first part saves a 1kB AES lookup table. The y axis is the value of the input byte  $D_1$ . The light region is never accessed in the AES encryption so reloading these blocks takes the longest time. The first 16 cache blocks contain the AES table entries and have shorter average access latency. There is a dark diagonal in the figure, meaning that a cache block has even shorter reload time when the input byte is of certain values. When the value of input byte is from 0 to 15 (0x00 to 0x0f), the first block of AES table  $T_1$  (offset: 0x00) is accessed. As the access to  $T_1$  in the first round is  $T_1[D_1 \oplus K_1]$ ,  $K_1$  is partially leaked to be 0x0u (u is the unknown 4 bits as the 16 lookup table entries in the same cache line cannot be distinguished ).

In STAR-FARR and STAR-NEWS, the victim AES encryption and the flush-reload attacker have different DomainID's so any cache lines used by the victim will not cause a cache hit in the attacker's reloading (see Figure 6 (b) and (c)).

**Prime-probe Side-channel Attack.** A prime-probe attack does not require shared AES lookup tables. The attacker fills the cache with the cache lines of his array. The lookup table access, e.g.,  $T_1[D_1 \oplus K_1]$ , will replace cache lines in one cache set determined by  $D_1$  and  $K_1$ , which causes a longer latency when the attacker probes this set later.

Figure 7 (a) shows a successful prime-probe side-channel attack on a AES key byte which is 0. For each cache set (x axis), the heatmap shows whether certain input values lead to longer access time than the average. The light line shows The attacker's cache lines in the first 16 cache sets are shown to conflict with AES table entries, leading to larger access time. Similar to the previous flush-reload attack, the key byte can be recovered as 0x0u (u is the unknown bits).

(c) STAR-NEWS

The fully-associative cache with random replacement in STAR-FARR defeats the prime-probe attack on AES (see Figure 7 (b)). The dynamic remapping cache in STAR-NEWS also guarantees a random replacement as a DomainID mismatch always leads to the path of *Mapping Miss* in Figure 5, defeating the attack in Figure 7 (c).

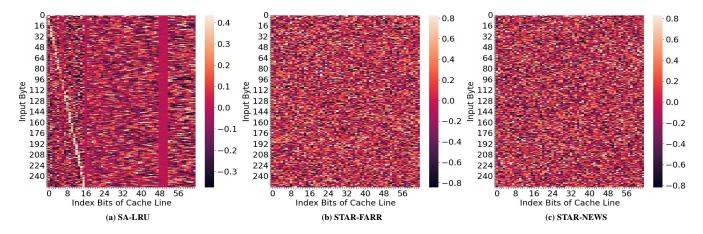

#### 6.2 Security: Speculative Execution Attack

The Spectre v1 attack [36] exploits misprediction for conditional branches. The sender transiently bypasses the bounds checking which prevents illegal out-of-bounds accesses. A cache-based Spectre v1 sender transiently reads an out-ofbounds secret and uses the secret to generate a memory access that will fetch or evict a cache line observable by the receiver.

**Flush-reload Speculative Execution Attack.** The gadget shown in Figure 1 leaks a 8-bit secret through the flush-reload covert channel. The sender code in the conditional branch is executed due to branch misprediction. The secret at array[x] is accessed using an illegal offset x and used to access a cache line in the *shared* array. The receiver can infer the secret value by looking for the *i* which gives the shortest reload time.

Figure 8 shows the results of running the flush-reload Spectre v1 attack when the secret is 30. For the SA-LRU baseline

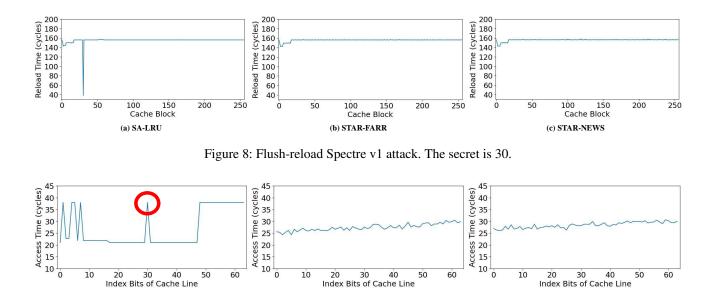

Figure 10: Statistics for performance evaluation: (a) Overall performance: relative execution time of tested architectures running different benchmarks. The last set is the geometric means of relative performance. (b) The number of *SFill-Inv* requests sent to the cache system. (c) The number of speculative loads which have a mapping hit but tag miss in STAR-NEWS systems.

(blue), the corresponding short access time at the 30th block, leaking the secret which is 30. STAR-FARR (orange) and STAR-NEWS (green) have no observable low reloading latency as the speculatively fetched cache line is cleared by the *SFill-Inv* feature.

**Prime-probe Speculative Execution Attack.** In a primeprobe Spectre v1 attack, the attacker uses its array to fill the cache. The Spectre v1 sender gadget will access the secret and evict a cache line when using the secret as the address. The access latency to different cache sets are later accumulated by the receiver. The cache set which has evictions during speculative execution will give longer access time.

Figure 9 shows the prime-probe Spectre v1 attack (accessing a secret of 30) manages to evict the receiver's circled cache line whose index is 30 in the SA-LRU system (blue). There are more than one peak of high access latency because there are other memory accesses in the sender code. These unrelated accesses cause conflicts at fixed cache sets while the circled peak moves as the secret value changes. The result shows while the prime-probe channel does not require shared memory regions, its result contains more noise than the flush-reload speculative execution attack.

The fully-associative cache of STAR-FARR (orange) defeats the attack as shown in Figure 9. The sender code running in STAR-NEWS (green) will always cause a random eviction of cache lines upon either a *Tag Miss* or a *Mapping Miss*, which causes no secret-dependent timing difference.

While there are many other variants of speculative attacks, they mostly differ in how the secret is illegally e accessed. Since we are only interested in preventing the secret from being leaked out through a cache timing channel, the tests with flush-reload and prime-probe Spectre V1 attacks are representative. We also tested with the speculative store bypass attack [22] using both flush-reload and prime-probe covert channels, and obtained similar results (not shown).

#### 6.3 Performance Evaluation

The performance of tested architectures is measured by running 24 benchmarks with the reference dataset in the SPEC CPU2006 benchmark suite. We skip the first 10 billion instructions in the benchmarks and run the next 500 million instructions. STAR-FARR has two tested configurations, STAR-FARR-T1 with a 1-cycle fully-associative L1D cache and STAR-FARR-T2 with a 2-cycle L1D cache. STAR-NEWS has four tested configurations with 0, 2, 4 and 6 extra index bits, denoted as STAR-NEWS-k0, k2, k4 and k6. STAR-NEWS-k4 is shown and explained in Figure 4.

**Overall performance.** Figure 10 (a) demonstrates the relative performance of STAR Cache in terms of execution time compared to the SA-LRU baseline whose performance is normalized to 1. The last column of Figure 10 (a) is the geometric mean of overhead.

The average execution time of STAR-FARR-T1 is 5.6% longer than SA-LRU. It improves the performance of zeusmp by 1.3% in the best case, showing both better security and higher performance. The worst-case overhead is 39.6% for mcf. Having a slower fully-associative L1 cache in STAR-FARR-T2 increases the average overhead to 10.8%.

For STAR-NEWS (blues bars), adding additional index bits, k, improves the performance. STAR-NEWS-k0 has a high average overhead of 15.3%. STAR-NEWS-k2 reduces the overhead to 9.4% (5.9% better than STAR-NEWS-k0). STAR-NEWS-k4 has an overhead of 7.2% (2.2% better than STAR-NEWS-k2) and STAR-NEWS-k6 has an overhead of 6.8% (0.4% better than STAR-NEWS-k4). Having more index bits improves the performance but the incremental benefit is decreasing. Further increasing k may cause the cache access latency to increase, reducing overall system performance.

Since we use the same hardware configurations, we can compare STAR-FARR-T1 (overhead 5.6%) and STAR-NEWS-k6 (overhead 6.8%) to leading defenses such as InvisiSpec [74] with 16.8% overhead and CleanupSpec [74] with 5.1% overhead. However, InvisiSpec and CleanupSpec do not prevent all non-speculative side-channel attacks, which STAR-FARR and STAR-NEWS do.

We also see that STAR-FARR is better if a fast fullyassociative cache design that has the same access latency as SA-LRU is feasible. Although STAR-FARR-T1 has an overhead of 5.6%, the overhead of STAR-FARR-T2 becomes 10.8%. In this case, STAR-NEWS-k6 which has an overhead of only 6.8% becomes the better choice.

**Factors causing performance overhead.** There are two major factors which cause performance degradation in STAR Cache. The first one affecting both STAR-FARR and STAR-NEWS is squashed loads which need to send *SFill-Inv* to invalidate cache lines upon incorrect speculation. The second one affecting only STAR-NEWS is the *ForwardNoFill* path upon a mapping hit but tag miss (see Figure 5), which prevents the cache fill and performs a cache line eviction. Both can lead

to a higher cache miss rate and therefore lower performance.

Figure 10 (b) shows the number of *SFill-Inv* requests that are sent in each benchmark. A strong correlation is observed when we compare Figure 10 (a) with Figure 10 (b). Benchmarks incurring highest performance overhead in both STAR-FARR and STAR-NEWS systems, e.g., astar, bzip2, calculix and mcf, are also the benchmarks requiring more *SFill-Inv* operations. This means that speculatively accessed cache lines are likely to be used by later instructions. While invalidating such cache lines degrades performance, this feature is needed to enforce the security against speculative execution attacks.

Figure 10 (c) shows the number of speculative loads which have a mapping hit but tag miss (TagMiss load). For TagMiss loads, cache fills are disallowed and data is directly forwarded to the processor; a random cache line eviction is also triggered (see the middle red path in Figure 5). The advantage of STAR-NEWS having more index bits can be clearly seen. With no extra bits, STAR-NEWS-k0 has a large number of TagMiss loads in benchmarks such as leslie3d. By adding a few extra bits, we can significantly reduce the number of TagMiss loads.

We show that even using a small *k* such as 2, 4 and 6 can greatly reduce these cache fill preventions and cache line evictions. In Figure 10 (c), STAR-NEWS-k2, STAR-NEWS-k4 and STAR-NEWS-k6 reduce the number of TagMiss loads doing *ForwardNoFill* by an average of 70.4%, 91.5% and 97.3% respectively for all benchmarks. This is because having more bits in the index field can reduce the chance of having a mapping hit (C.Index == L.Index in Figure 5), allowing more useful replacements. Similar to the observations for overall performance, we recommend k = 4 or 6 as the best options.

**Fraction of wrong-path loads.** We collect the fraction of speculative loads that are squashed for all benchmarks. This ranges from 0.0% to 52.7%, with an average of 11.1%. This means most of speculative loads are correct-path instructions, which is also why CleanupSpec and our proposed *SFill-Inv* have lower performance overhead.

## 7 Conclusion

The cache state is an important target for side-channel attacks and speculative execution attacks for leaking information. Prior hardware defenses covered either side-channel or speculative attacks but not both. To the best of our knowledge, this is the first paper that clearly shows the dimensions of both attack families, highlighting the danger of same-domain speculative attacks, and proposing comprehensive solutions for both attack families. Our new STAR-FARR and STAR-NEWS cache architectures have low performance overhead of 5.6% and 6.8%. Our proposed design methodology can be used to design other secure caches and cover other attack classes and different secure hardware subsystems.

# References

- AINSWORTH, S., AND JONES, T. M. Muontrap: Preventing cross-domain spectre-like attacks by capturing speculative state. In *The ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA)* (2020).

- [2] AMD. Amd64 technology indirect branch control extension. https://developer.amd.com/wp-content /resources/Architecture\_Guidelines\_Update\_ Indirect\_Branch\_Control.pdf, 2018.

- [3] BARBER, K., BACHA, A., ZHOU, L., ZHANG, Y., AND TEODORESCU, R. Specshield: Shielding speculative data from microarchitectural covert channels. In *The* 28th International Conference on Parallel Architectures and Compilation Techniques (PACT) (2019).

- [4] BEHNIA, M., SAHU, P., PACCAGNELLA, R., YU, J., ZHAO, Z. N., ZOU, X., UNTERLUGGAUER, T., TOR-RELLAS, J., ROZAS, C., MORRISON, A., MCKEEN, F., LIU, F., GABOR, R., FLETCHER, C. W., BASAK, A., AND ALAMELDEEN, A. Speculative interference attacks: Breaking invisible speculation schemes. In Proceedings of the 26th ACM International Conference on Architectural Support for Programming Languages and Operating Systems (New York, NY, USA, 2021), ASPLOS '21, Association for Computing Machinery, pp. 1046–1060.

- [5] BERNSTEIN, D. J. Cache-timing attacks on aes. *Online* (2005).

- [6] BHATTACHARYYA, A., SANDULESCU, A., NEUGSCHWANDTNER, M., SORNIOTTI, A., FALSAFI, B., PAYER, M., AND KURMUS, A. Smotherspectre: exploiting speculative execution through port contention. In *The 2019 ACM SIGSAC Conference on Computer* and Communications Security (2019).

- [7] BINKERT, N., BECKMANN, B., BLACK, G., REIN-HARDT, S. K., SAIDI, A., BASU, A., HESTNESS, J., HOWER, D. R., KRISHNA, T., SARDASHTI, S., SEN, R., SEWELL, K., SHOAIB, M., VAISH, N., HILL, M. D., AND WOOD, D. A. The gem5 simulator. SIGARCH Comput. Archit. News 39, 2 (aug 2011), 1–7.

- [8] BOURGEAT, T., DREAN, J., YANG, Y., TSAI, L., EMER, J., AND YAN, M. Casa: End-to-end quantitative security analysis of randomly mapped caches. In 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO) (2020), pp. 1110–1123.

- [9] BOURGEAT, T., LEBEDEV, I., WRIGHT, A., ZHANG, S., ARVIND, AND DEVADAS, S. Mi6: Secure enclaves

in a speculative out-of-order processor. In *The 52nd Annual IEEE/ACM International Symposium on Microarchitecture* (2019).

- [10] CANELLA, C., BULCK, J. V., SCHWARZ, M., LIPP, M., VON BERG, B., ORTNER, P., PIESSENS, F., EV-TYUSHKIN, D., AND GRUSS, D. A systematic evaluation of transient execution attacks and defenses. In 28th USENIX Security Symposium (2019).

- [11] CANELLA, C., GENKIN, D., GINER, L., GRUSS, D., LIPP, M., MINKIN, M., MOGHIMI, D., PIESSENS, F., SCHWARZ, M., SUNAR, B., VAN BULCK, J., AND YAROM, Y. Fallout: Leaking data on meltdown-resistant cpus. In Proceedings of the 2019 ACM SIGSAC Conference on Computer and Communications Security (New York, NY, USA, 2019), CCS '19, Association for Computing Machinery, pp. 769–784.

- [12] CENTER, M. S. R. Mitigating speculative execution side channel hardware vulnerabilities. https://msrc -blog.microsoft.com/2018/03/15/mitigating-s peculative-execution-side-channel-hardwar e-vulnerabilities.

- [13] DAEMEN, J., AND RIJMEN, V. The design of Rijndael, vol. 2. Springer, 2002.

- [14] DESSOUKY, G., FRASSETTO, T., AND SADEGHI, A.-R. Hybcache: Hybrid side-channel-resilient caches for trusted execution environments. In *Proceedings* of the 29th USENIX Conference on Security Symposium (2020), pp. 451–468.

- [15] DOMNITSER, L., JALEEL, A., LOEW, J., ABU-GHAZALEH, N., AND PONOMAREV, D. Non-monopolizable caches: Low-complexity mitigation of cache side channel attacks. ACM Trans. Archit. Code Optim. 8, 4 (2012).

- [16] ERBAGCI, B., LIU, F., CAKIR, C., AKKAYA, N. E. C., LEE, R., AND MAI, K. A 32kb secure cache memory with dynamic replacement mapping in 65nm bulk cmos. In 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC) (2015), pp. 1–4.

- [17] EVTYUSHKIN, D., RILEY, R., ABU-GHAZALEH, N., AND PONOMAREV, D. Branchscope: A new sidechannel attack on directional branch predictor. In *The Twenty-Third International Conference on Architectural Support for Programming Languages and Operating Systems* (2018).

- [18] FUSTOS, J., FARSHCHI, F., AND YUN, H. Spectreguard: An efficient data-centric defense mechanism against spectre attacks. In *The 56th Design Automation Conference (DAC)* (2019).

- [19] GINGELL, R. A., LEE, M., DANG, X. T., AND WEEKS, M. S. Shared libraries in sunos. *AUUGN 8*, 5 (1987), 112.

- [20] GRAYSON, B., RUPLEY, J., ZURASKI, G. Z., QUIN-NELL, E., JIMÉNEZ, D. A., NAKRA, T., KITCHIN, P., HENSLEY, R., BREKELBAUM, E., SINHA, V., AND GHIYA, A. Evolution of the samsung exynos cpu microarchitecture. In *The ACM/IEEE 47th Annual International Symposium on Computer Architecture (ISCA)* (2020).

- [21] HE, Z., HU, G., AND LEE, R. New models for understanding and reasoning about speculative execution attacks. In 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA) (2021), pp. 40–53.

- [22] HORN, J. Speculative execution, variant 4: Speculative store bypass, 2018. URI: https://bugs.chromium.org/p/projectzero/issues/detail?id=1528 (2018).

- [23] HU, G., HE, Z., AND LEE, R. B. Sok: Hardware defenses against speculative execution attacks. In 2021 International Symposium on Secure and Private Execution Environment Design (SEED) (2021), IEEE, pp. 108– 120.

- [24] IAIK. Meltdown proof-of-concept. https://github .com/IAIK/meltdown, 2019.

- [25] INTEL. Lazy fp. https://www.intel.com/content/ www/us/en/security-center/advisory/intel-s a-00145.html, 2018.

- [26] INTEL. Spectre v3a (rsre). https://www.intel.com/ content/www/us/en/security-center/advisory /intel-sa-00115.html, 2018.

- [27] INTEL. Microarchitectural data sampling. https://so ftware.intel.com/content/www/us/en/develop /articles/software-security-guidance/tech nical-documentation/intel-analysis-microar chitectural-data-sampling.html, 2019.

- [28] INTEL. TAA. https://software.intel.com/con tent/www/us/en/develop/articles/software-s ecurity-guidance/advisory-guidance/intel-t sx-asynchronous-abort.html, 2019.

- [29] INTEL. L1d eviction sampling. https://software.i ntel.com/content/www/us/en/develop/article s/software-security-guidance/advisory-gui dance/l1d-eviction-sampling.html, 2020.

- [30] INTEL. Special register buffer data sampling. https: //software.intel.com/content/www/us/en/dev

elop/articles/software-security-guidance/ technical-documentation/special-register-b uffer-data-sampling.html, 2020.

- [31] INTEL. VRS. https://software.intel.com/conte nt/www/us/en/develop/articles/software-sec urity-guidance/advisory-guidance/vector-r egister-sampling.html, 2020.

- [32] KHASAWNEH, K. N., KORUYEH, E. M., SONG, C., EVTYUSHKIN, D., PONOMAREV, D., AND ABU-GHAZALEH, N. Safespec: Banishing the spectre of a meltdown with leakage-free speculation. In *The 56th Design Automation Conference (DAC)* (2019).

- [33] KIM, Y., DALY, R., KIM, J., FALLIN, C., LEE, J. H., LEE, D., WILKERSON, C., LAI, K., AND MUTLU, O. Flipping bits in memory without accessing them: An experimental study of dram disturbance errors. In *Proceeding of the 41st Annual International Symposium on Computer Architecuture* (2014), ISCA '14, IEEE Press, pp. 361–372.

- [34] KIRIANSKY, V., LEBEDEV, I., AMARASINGHE, S., DEVADAS, S., AND EMER, J. Dawg: A defense against cache timing attacks in speculative execution processors. In *The 51st Annual IEEE/ACM International Symposium* on Microarchitecture (MICRO) (2018).

- [35] KIRIANSKY, V., AND WALDSPURGER, C. Speculative buffer overflows: Attacks and defenses. arXiv preprint arXiv:1807.03757 (2018).

- [36] KOCHER, P., HORN, J., FOGH, A., GENKIN, D., GRUSS, D., HAAS, W., HAMBURG, M., LIPP, M., MANGARD, S., PRESCHER, T., SCHWARZ, M., AND YAROM, Y. Spectre attacks: Exploiting speculative execution. In 2019 IEEE Symposium on Security and Privacy (SP) (2019), pp. 1–19.

- [37] KORUYEH, E. M., KHASAWNEH, K. N., SONG, C., AND ABU-GHAZALEH, N. Spectre returns! speculation attacks using the return stack buffer. In *12th USENIX* Workshop on Offensive Technologies (WOOT 18) (2018).

- [38] LI, M., MIAO, C., YANG, Y., AND BU, K. unxpec: Breaking undo-based safe speculation. In 2022 IEEE International Symposium on High-Performance Computer Architecture (HPCA) (2022), pp. 98–112.

- [39] LI, P., ZHAO, L., HOU, R., ZHANG, L., AND MENG, D. Conditional speculation: An effective approach to safeguard out-of-order execution against spectre attacks. In 2019 IEEE International Symposium on High Performance Computer Architecture (HPCA) (2019).

- [40] LIPP, M., SCHWARZ, M., GRUSS, D., PRESCHER, T., HAAS, W., FOGH, A., HORN, J., MANGARD, S., KOCHER, P., GENKIN, D., YAROM, Y., AND HAM-BURG, M. Meltdown: Reading kernel memory from user space. In 27th USENIX Security Symposium (2018).

- [41] LIU, F., GE, Q., YAROM, Y., MCKEEN, F., ROZAS, C., HEISER, G., AND LEE, R. B. Catalyst: Defeating last-level cache side channel attacks in cloud computing. In 2016 IEEE International Symposium on High Performance Computer Architecture (HPCA) (2016), pp. 406–418.

- [42] LIU, F., WU, H., MAI, K., AND LEE, R. B. Newcache: Secure cache architecture thwarting cache side-channel attacks. *IEEE Micro 36*, 5 (2016), 8–16.

- [43] LIU, F., YAROM, Y., GE, Q., HEISER, G., AND LEE, R. B. Last-level cache side-channel attacks are practical. In 2015 IEEE Symposium on Security and Privacy (2015), pp. 605–622.

- [44] LOUGHLIN, K., NEAL, I., MA, J., TSAI, E., WEISSE, O., NARAYANASAMY, S., AND KASIKCI, B. DOLMA: Securing speculation with the principle of transient nonobservability. In 30th USENIX Security Symposium (USENIX Security 21) (2021).

- [45] MA, X., ZHONG, H., XIU, N., CHEN, Y., YIN, G., NARAYANAN, V., LIU, Y., NI, K., YANG, H., AND LI, X. Capcam: A multilevel capacitive content addressable memory for high-accuracy and high-scalability search and compute applications. *IEEE Transactions on Very Large Scale Integration (VLSI) Systems 30*, 11 (2022), 1770–1782.

- [46] MAISURADZE, G., AND ROSSOW, C. Ret2spec: Speculative execution using return stack buffers. In *The 2018* ACM SIGSAC Conference on Computer and Communications Security (2018).

- [47] MUTLU, O., AND KIM, J. S. Rowhammer: A retrospective. *IEEE Transactions on Computer-Aided Design* of Integrated Circuits and Systems 39, 8 (2020), 1555– 1571.

- [48] OJOGBO, E. J., THOTTETHODI, M., AND VIJAYKU-MAR, T. N. Secure automatic bounds checking: Prevention is simpler than cure. In *The 18th ACM/IEEE International Symposium on Code Generation and Optimization* (2020).

- [49] OMAR, H., AND KHAN, O. Ironhide: A secure multicore that efficiently mitigates microarchitecture state attacks for interactive applications. In 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA) (2020).

- [50] OSVIK, D. A., SHAMIR, A., AND TROMER, E. Cache attacks and countermeasures: The case of aes. In *Topics* in Cryptology – CT-RSA 2006 (2006), D. Pointcheval, Ed.

- [51] PURNAL, A., GINER, L., GRUSS, D., AND VER-BAUWHEDE, I. Systematic analysis of randomizationbased protected cache architectures. In 2021 IEEE Symposium on Security and Privacy (SP) (2021), pp. 987– 1002.

- [52] QURESHI, M. K. Ceaser: Mitigating conflict-based cache attacks via encrypted-address and remapping. In *The 51st Annual IEEE/ACM International Symposium* on Microarchitecture (MICRO) (2018).

- [53] QURESHI, M. K. New attacks and defense for encrypted-address cache. In 2019 ACM/IEEE 46th Annual International Symposium on Computer Architecture (ISCA) (2019), pp. 360–371.

- [54] RAGAB, H., MILBURN, A., RAZAVI, K., BOS, H., AND GIUFFRIDA, C. Crosstalk: Speculative data leaks across cores are real. In 2021 IEEE Symposium on Security and Privacy (SP) (2021).

- [55] SAILESHWAR, G., AND QURESHI, M. K. Cleanupspec: An "undo" approach to safe speculation. In *The* 52nd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO) (2019).

- [56] SAILESHWAR, G., AND QURESHI, M. K. Mirage: Mitigating conflict-based cache attacks with a practical fullyassociative design. In USENIX Security Symposium (2021), pp. 1379–1396.

- [57] SAKALIS, C., KAXIRAS, S., ROS, A., JIMBOREAN, A., AND SJÄLANDER, M. Efficient invisible speculative execution through selective delay and value prediction. In *The 46th International Symposium on Computer Architecture (ISCA)* (2019).