# J-PARALLELIO - AUTOMATIC PARALLELIZATION FRAMEWORK FOR JAVA VIRTUAL MACHINE CODE

#### A PREPRINT

Krzysztof Stuglik Institute of Computer Science University of Science and Technology Cracow, Poland stuglik@student.agh.edu.pl

Mateusz Kulczyk Institute of Computer Science University of Science and Technology Cracow, Poland kulczyk@student.agh.edu.pl Piotr Listkiewicz Institute of Computer Science University of Science and Technology Cracow, Poland listkiewicz@student.agh.edu.pl

Marcin Pietron Institute of Electronics University of Science and Technology Cracow, Poland deep-cogni.com pietron@agh.edu.pl

March 16, 2023

#### ABSTRACT

Manual translation of the algorithms from sequential version to its parallel counterpart is time consuming and can be done only with the specific knowledge of hardware accelerator architecture, parallel programming or programming environment. The automation of this process makes porting the code much easier and faster. The key aspect in this case is how efficient the generated parallel code will be. The paper describes J-Parallelio, the framework for automatic analysis of the bytecode source codes and its parallelisation on multicore processors. The process consists of a few steps. First step is a process of decompilation of JVM and its translation to internal abstract syntax tree, the dependency extraction and memory analysis is performed. Finally, the mapping process is performed which consists of a set of rules responsible for translating the input virtual machine source code to its parallel version. The main novelty is that it can deal with pure java virtual machine and can generate parallel code for multicore processors. This makes the system portable and it can work with different languages based on JVM after some small modifications. The efficiency of automatically translated source codes were compared with their manually written counterparts on chosen benchmarks.

Keywords automatic parallelization · java virtual machine · multicore processors · HPC

## 1 Introduction

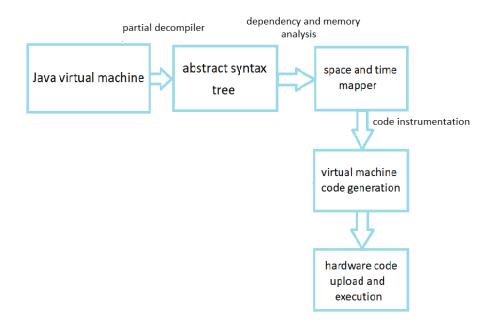

Over the last few years we have observed a lot of trials of building tools that can help with automatic code parallelisation on different hardware platforms. We have also observed intensive research in parallelisation of source codes written in C/C++ language and speed up using OpenMP and OpenCL environments [11], [13], [14]. Recently, we have been able notice that tools for transforming C to CUDA or OpenCL for GPU acceleration are a common topic of interest in automatic code parallelisation [4], [3], [6], [13] and [7]. There were also trials to automatically speed up different languages (e.g. Java [20]) on multicore processors. In the J-Paralellio system, a fairly new approach is presented. The framework is fully based on java virtual machine code and language independent, fig. 1. The main input is java virtual machine code. JVM is parsed and partially decompiled and transformed to intermediate structures, then analysed, instrumented and transformed back to virtual machine in a parallelised version. The crucial element of its functionality is an engine incorporated with a decompiler and abstract syntax tree builder, pool of algorithms responsible for dependency and memory access analysis and set of rules for java virtual machine code transformation. In the first stage, the system parses JVM source code and extracts loops from the JVM code. It then generates an Abstract Syntax Tree with Data Flow Graph which helps to identify the potential parallelism by extracting internal dependencies. The system mainly concentrates on loops analysis. The framework performs the dependency analysis using the same algorithms as other automatic paralellisation systems [11], [4], [5], [13]. Finally, the system maps the loops iterations and data structures to the hardware accelerator by using built-in translation rules. After the system engine analysis, it generates a parallel version of java virtual machine code. It instruments java virtual machine code with instructions responsible for the creation of threads. It automatically maps the loops to multi-thread execution. Finally, the work presents the results of mapping a few benchmarks from sequential to parallel versions. The main advantage of the presented approach is its portability. There are several languages (Ruby and Python respectively). The new languages that have been created from scratch to compile to Java bytecode, Clojure, Groovy and Scala may be the most popular examples.

The paper is organised as follows: the second section describes the related works in the field of automatic parallelisation. The next sections concentrates on methodology and algorithms which analyse and translate the parallel version of the input sequential JVM source code. The fifth section presents the results, the sixth conclusions and future work.

# 2 Related works

The articles [20], [23] and [24] present approaches for automatic java source code parallelisation. In [20] dependency extraction methods are used for java source code analysis. The translator is built for sequential JAVA code which generates a highly parallel version of the same program. The translation process interprets the AST nodes for signatures such as read-write access, execution-flow modifications, among others and generates a set of dependencies between executable tasks. The presented approach has been applied for recursive Fibonacci and FFT algorithms. The methods obtained a 10.97x and 9.0x increase in speed on a twelve-core machine. The latter two methods [23] and [24] concentrate on parallelisation using trace information. The approach presented in [23] collects on-line trace information during program execution, and dynamically recompiles methods that can be executed in parallel. In [24], the authors implement a system that demonstrates the benefits and addresses the challenges of using traces for data-parallel applications. They propose an execution model for automatic parallelisation based on traces. In [21], a novel approach is described and evaluated for the automatic parallelisation of programs that use pointer-based dynamic data structures written in Java. The approach exploits parallelism among methods by creating an asynchronous thread of execution for each method invocation in a program. The only work in which java code parallelisation is done directly on a java virtual machine is shown in [19]. It is semi-automatic, there is no detailed JVM code analysis, it has not decompilation, automatic JVM code transformation and generation. It presents the process of the automatic instrumentation of virtual machine code by preparing and invoking special adapters which can run the original methods in a multi-threaded java environment. The results are presented using the Mandelbrot benchmark. The drawback of the article is the lack of results of running the algorithm on more benchmarks.

Several other systems were designed for automatic code parallelisation which are mainly based on C/C++ language. YUCCA [2] designed by KPIT Technologies is an automatic parallelisation tool for projects written in C language. It provides source to source conversion - on input, it takes the source code of the application written in C and produces a parallelised version of the source code as an output. YUCCA output is a multithreaded version of the input with Pthreads or OpenMP pragmas inserted at appropriate places. YUCCA uses PThreads to perform task parallelisation and OpenMP to make loops run in parallel. YUCCA consists of two main parts: the front-end, which is responsible for parsing source code, the back-end which performs static dependency analysis to identify parts of code that is worth being parallelised. PLUTO [11], [12] is an automatic parallelisation tool based on a polyhedral model. PLUTO performs source to source transformation - it conducts coarse-grained parallelism and at the same time ensures data locality. The core transformation framework mainly works by finding affine transformations for efficient tiling. PLUTO performs to tune aspects such as tile sizes, unroll factors and outer loop fusion structure. C-to-CUDA [4] and PPCG [5] propose similar steps to solve the automatic GPGPU code-generation problem. They concentrate on finding parallel loops, the creation of a polyhedral model from the loops; they tile and map the loops to GPU blocks and threads and determine where to place the data.

Par4All [13] is an automatic parallelising and optimising compiler for C and Fortran sequential programs. The purpose of this source-to-source compiler is to adapt existing applications to various hardware targets such as multicore systems, high performance computers and GPUs. It creates a new source code and thus allows the original source code of the application to remain unchanged. The auto-parallelisation feature of the Intel C++ Compiler [15] automatically translates serial portions of the input program into semantically equivalent multi-threaded code. Automatic parallelisation

Figure 1: Automatic java virtual machine parallelization system.

determines the loops that are good candidates, performs the data-flow analysis to verify correct parallel execution, and partitions the data for threaded code generation as is needed in programming with OpenMP directives. The OpenMP and auto-parallelisation applications provide the performance gains from shared memory on multiprocessor systems. AutoPar [14] is a tool which can automatically insert OpenMP pragmas into input serial C/C++ codes. For input programs with existing OpenMP directives, the tool double checks the correctness when the right option is turned on. Compared to conventional tools, AutoPar can incorporate user knowledge (semantics) to discover more parallelisation opportunities.

The iPat/OMP [16] tool provides users with the assistance needed for the OpenMP parallelisation of a sequential program. This tool is implemented as a set of functions on the Emacs editor. All the activities related to program parallelisation, such as selecting a target portion of the program, invoking an assistance command, and modifying the program based on the assistance information shown by the tool, can be handled in the source program editor environment. OMP2MPI [17] automatically generates MPI source code from OpenMP, allowing the program to exploit non shared-memory architectures such as cluster, or Network-on-Chip-based (NoC-based) Multiprocessors-System-on-Chip (MPSoC). OMP2MPI provides a solution that allows further optimisation by an expert who wants to achieve better results.

# 3 Methodology

The framework consists of a few submodules. The first is a decompilation comprised of AST building components. It is responsible for transforming the Java bytecode to Java instructions and building an Abstract Syntax Tree from them. In parallel with decompilation, the loops extraction module works. It enables extraction of the loops in a java bytecode. The loops are the analysed by a specialised algorithm to extract potential parallelism (see Section 3.1). After analysis, mapping the bytecode to a multithread version is performed. The bytecode is instrumented with special instructions which are responsible for the thread, the task and their memory management. The multithreaded bytecode can then be run or decompiled to any language based on a java virtual machine. The main phases of the framework method are:

- Decompilation

- Abstract syntax tree building

- Loops extraction

- Data flow and dependency analysis

• Multithread mapping and JVM code instrumentation

## 3.1 Java virtual machine and BCEL

A Java virtual machine (JVM) is an abstract computing machine that enables a computer to run a Java program or program in other language which is based on JVM (e.g. Clojure, Groovy or Scala). One of the organisational units of JVM bytecode is a class. The JVM has instructions for the following groups of tasks: arithmetic operations, load and store arithmetic, type conversion, object creation and manipulation, stack management (stack operations push / pop), control transfer (branching), field access, method invocation, throwing exceptions and monitor-based concurrency. The JVM operation set can be represented as: OP ARG, where OP belongs to set of JVM available elementary operations, ARG is an argument. Argument can be constant or variable. In each single instruction can be one or two arguments. The bytecode instruction set currently consists of 212 instructions and 44 opcodes.

The presented framework uses ByteCode Engineering Library (BCEL) which enables reading and manipulating in Java bytecode. The BCEL is intended to give users a convenient way to analyse, create, and manipulate Java class files. Classes are represented by objects which contain all the symbolic information of the given class: methods, fields and bytecode instructions, in particular. Such objects can be read from an existing file, transformed by a program (e.g. a class loader at run-time) and written to a file again.

## 3.2 Decompilation and AST building

The first stage of the framework is responsible for translation of the raw Java bytecode to higher level instructions. Next, the translated instructions should be analysed to extract dependency between program components. Therefore the algorithm was built to fulfill this goal. Each single bytecode operation can pop or push elements on the JVM stack. Each single instruction in high-level language ends when the stack is empty. Therefore to extract whole Java instruction the module monitors the state of the stack. The approach is presented in Algorithm 1. It loads a class implementation in Java bytecode and gets a list of its methods (line 1). It also initializes the stack of the virtual machine (S) and decompiled instruction collections  $(J_i \text{ and } J)$ .

```

Algorithm 1 Decompilation the JVM

1: S \leftarrow \emptyset, J_i \leftarrow \emptyset, J \leftarrow \emptyset, C \leftarrow \text{load class}, M_C \leftarrow \text{get methods in } C

2: for m in M_C do

3:

I_{set} \leftarrow get instructions from m

4:

while I_{set} \notin \emptyset do

i \leftarrow remove first instruction from I_{set}

5:

6:

push i to S

7:

while S \notin \emptyset do

8:

i \leftarrow remove first instruction from I_{set}

if i \in OP then

9:

ARG \leftarrow pop \ ARG \ from \ S

10:

R \leftarrow OP \ ARG

11:

push R to S

12:

end if

13:

14:

if i \in PUSH then

push \ ARG to S

15:

end if

16:

if i \in POP then

17:

J_i \leftarrow pop \text{ from } S

18:

19:

end if

20:

end while

21:

return J_i

22:

J \leftarrow J_i \cup J

end while

23:

24: end for

```

Then the algorithm iterates over the class methods. It gets an instruction list from each method m (line 3). It translates each instruction in a sequence and monitors the state of the stack. At the beginning it pushes the first instruction i of  $J_i$  to S (line 6). In a while loop it processes next bytecode instructions until stack S is empty. If it recognizes the operand

instruction then it takes arguments of operation from the stack (line 10). It forms the triple address instruction (line 11) and pushes it to the stack. If PUSH operation is recognized (line 14) it pushes the argument of bytecode instruction to the stack. Finally if a single POP instruction is met the algorithm takes the final decompiled instruction ( $J_i$ ) from the stack (line 18). All decompiled instructions are stored in J list (line 22).

The Algorithm 2 presents building Abstract Syntax Tree from the list of the decompiled instructions. It initializes data structures (line 1) in which it stores dependencies between instructions (T) and list of assigned variables (L). Then, it goes through the list of instructions and takes left and right hand variables from the analysed instruction (line 3-5). It checks in a loop if every right hand variable of  $J_i$  (from  $J_{iR}$ ) already exists in L. If it is true, the algorithm takes the last instruction in which the specified right hand variable has appeared (var, line 8).

#### Algorithm 2 AST building

```

1: T \leftarrow \emptyset, L \leftarrow \emptyset

2: while J \notin \emptyset do

3:

J_i \leftarrow remove first instruction from J

4:

J_{iR} \leftarrow get right hand variables of J_i

J_{iL} \leftarrow get left hand variable of J_i

5:

for var in J_{iR} do

6:

if var \in L then

7:

I_R \leftarrow take last instruction from L: var \in I_R

8:

9:

d \leftarrow (I_R \rightarrow J_i)

T \leftarrow T \cup d

10:

11:

end if

end for

12:

L \leftarrow J_{iR} \cup L

13:

14: end while

15: return T

```

The dependency d is extracted between these two instructions ( $I_R$  and  $J_i$ , line 9) and added to the set T. After the instruction is processed the right hand variable is added to L set (line 13). At the end of the algorithm set of dependencies T is returned (line 15) which can be directly used to create the AST.

#### 3.3 Loops extraction and data flow analysis

The loop extraction and their analysis are the next step of Java bytecode analysis. It is a crucial stage in the automatic parallelisation because loops are the main source of hidden parallelism. The Algorithm 3 presents how loops are extracted from the bytecode. The process starts from finding jump GOTO instruction. Then the argument of jump instruction is read (jump address, line 2). The address is the start of the program loop. The algorithm goes to this location and parses the iteration variable with its initialization value and loop boundary condition. It takes the list of the instruction from the location just after conditional bytecode instruction to the GOTO instruction (line 6). The extracted body of the loop can be decompiled using Algorithm 1. Very often loops can be nested. Therefore to extract hierarchy of the loops presented method should run recursively.

#### Algorithm 3 The JVM loop extraction

- 1:  $I_{goto} \leftarrow \text{find } GOTO \text{ instruction}$

- 2:  $L_s \leftarrow$  take address from  $I_{qoto}$  instruction

- 3: jump to  $L_s$

- 4:  $i \leftarrow$  take iteration variable

- 5:  $B \leftarrow$  take condition boundary of the loop

- 6:  $L \leftarrow$  take block from condition to  $I_{goto}$

- 7: decompile loop L //Algorithm 1

After loop extraction the loop analysis is performed. Formal analysis is based on a polyhedral model; algorithms for dependency detection are run by using symbolic Fourier-Motzkin elimination.

## **4** Java virtual machine automatic parallelisation module

The Algorithm 4 describes the process of instrumenting the JVM bytecode. The first two steps are responsible for initialization the thread executors and tasks list (line 1 and 2). The next part depends on type of parallelism. If data-driven dependency is recognized (lines 3-7, e.g. histogram) the input data is divided to independent data chunks (line 4). Output data is copied and create separate instance for each parallel thread (line 5). Then subtasks methods are created to work on these data chunks (line 6). At the end the single thread code responsible for merging result data is added (line 7).

#### Algorithm 4 The JVM parallelisation

1:  $Ex \leftarrow$  create executors 2:  $[T_1, T_2, ..., T_N] \leftarrow \text{create task list}$ 3: if  $P_t$  is DP then 4:  $[D_{i1}, D_{i2}, ..., D_{iN}] \leftarrow$  divide the input data  $D_i$ 5:  $[D_{o1}, D_{o2}, ..., D_{oN}] \leftarrow$  make copy of output data  $D_o$ 6:  $P \leftarrow \text{add pool of subtasks}(D_{in}, D_{on})$ 7:  $D_o \leftarrow \text{add merging output data } D$ 8: end if 9: if  $P_t$  is IP then  $[(start_1, step_1), (start_2, step_2), ..., (start_N, step_N)] \leftarrow$  divide iterations to chunks 10:  $P \leftarrow \text{add pool of subtasks in parallelised regions } (start_n, step_n)$ 11: 12: end if

The JVM instrumentation is finally used in the main parallelisation algorithm which is shown in Algorithm 5. The algorithm tries to find best parallel configuration of the input sequential program. The parallelisation concentrates mainly on program loops extracted by Algorithm 3 (line 2). Then the dependency analysis is performed (line 3). The loops can be fully or partially parallelised or unable to run in parallel (line 4). In the case of fully parallel loops the main decision is which loop to choose in a nested loop structure. Additionally, loops can be transformed by interchanging, tiling, skewing etc. By making appropriate selections from this choice of transformations it is possible to achieve better mapping and more efficient implementation. All these configurations are generated in line 5. Then they are tested in a loop (lines 6-10). Each candidate transformation is parallelised in JVM. Next, they are run with reduced number of iteration r (line 8). Finally, the most efficient configuration is chosen (lines 12 and 13).

#### Algorithm 5 The parallelisation algorithm

1:  $E \leftarrow \emptyset, V \leftarrow \emptyset$ 2:  $L_d \leftarrow \text{Algorithm 3}$ 3:  $L_p \leftarrow \text{Fourier-Motzkin}(L_d)$ 4:  $P_t \leftarrow$  check parallelism type( $L_d$ ) 5:  $L_t \leftarrow$  get loop transformations 6: for  $l_t$  in  $L_t$  do  $L = \text{parallelise_jvm}(l_t) //\text{Algorithm 4}$ 7: 8:  $e = \operatorname{run}(L, r)$ 9:  $E \leftarrow E \cup e$ 10:  $V \leftarrow V \cup L$ 11: end for 12:  $id_{min} \leftarrow arg \min E$ 13: return  $V[id_{min}]$

### **5** Results

The presented framework was run on the following benchmarks: matrix multiplication, histogram computing, vanilla NBody problem and Fast Fourier Transform. The two parameters are efficiency and speedup are main indicators of parallelisation algorithm quality. The efficiency (E) is defined as:

$$E(N,P) = \frac{S(N,P)}{P} = \frac{T(N,1)}{P*T(N,P)}$$

(1)

and speedup (S):

$$S(N,P) = \frac{T(N,1)}{T(N,P)}$$

(2)

where:

- N size of the problem,

- P number of cores,

- T(N,P) time execution for problem with size N and with P cores

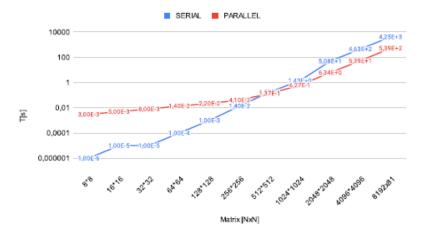

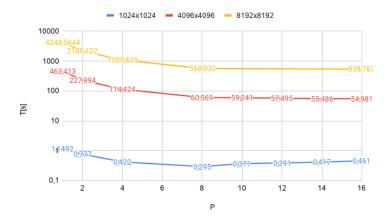

In Table 1 and Figures 2 and 3 the results for matrix multiplication are described.

|    | 1024x1024 |      |      | 4096x4096 |      |      | 8192x8192 |      |      |

|----|-----------|------|------|-----------|------|------|-----------|------|------|

| Р  | T[s]      | Е    | S    | T[s]      | E    | S    | T[s]      | Е    | S    |

| 1  | 1.15      | 1    | 1    | 463.41    | 1    | 1    | 4 248.56  | 1    | 1    |

| 2  | 0.78      | 0.74 | 1.48 | 227.99    | 1.02 | 2.03 | 2 180.12  | 0.97 | 1.95 |

| 4  | 0.42      | 0.68 | 2.72 | 114.42    | 1.01 | 4.05 | 1 087.61  | 0.98 | 3.91 |

| 8  | 0.30      | 0.49 | 3.90 | 60.57     | 0.96 | 7.65 | 568.00    | 0.93 | 7.48 |

| 10 | 0.37      | 0.31 | 3.10 | 59.24     | 0.78 | 7.82 |           |      |      |

| 12 | 0.39      | 0.24 | 2.94 | 57.50     | 0.67 | 8.06 |           |      |      |

| 14 | 0.42      | 0.20 | 2.76 | 55.49     | 0.60 | 8.35 |           |      |      |

| 16 | 0.46      | 0.16 | 2.49 | 54.98     | 0.53 | 8.43 | 538.77    | 0.49 | 7.89 |

Table 1: Results of matrix multiplication with efficiency parameter E and acceleration S

In Table 1, the results for different sizes of matrix are shown (1024x1024, 4096x4096 and 8192x8192). The efficiency is presented for serial and multicore version. The results are described for different numbers of cores. It can be observed that for smaller matrices (1024x1024) the peak performance is in the case of using eight cores.

Figure 2: Logarithmic chart from serial and parallel time execution of matrix multiplication.

If the size is bigger (4096x4096 and 8192x8192) the best speedup is achieved while using all available cores - sixteen.

Figures 2 and 3 present these results using a logarithmic scale. Figure 2 shows comparison of execution times between serial and automatically generated parallel versions. It can be observed that around 256x256 size the generated code outperforms the serial one.

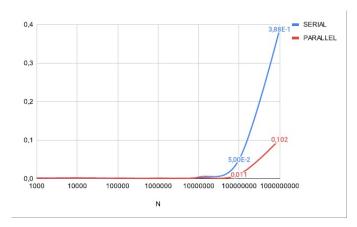

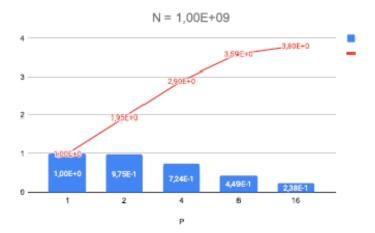

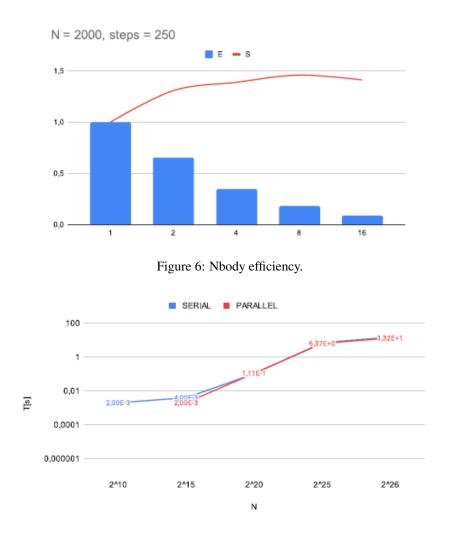

Figures 4 and 5 show histogram efficiency related to the size of input data and the number of cores. The histogram algorithm has data-driven parallelism. When the amount of data is about  $10^7$  or higher then the acceleration can be noticed (Figure 4). Figure 6 presents Nbody efficiency.

It shows that maximum speedup achieved by automatically generated code was around 1.5 (for eight cores). Figure 7 describes FFT scalability. The serial version is slightly more efficient than parallel. In all experiments the automatic

Figure 3: Logarithmic chart from matrix multiplication on different number of processor cores.

Figure 4: Scalability of histogram.

Figure 5: Histogram efficiency.

Figure 7: Logarithmic chart from FFT with different number of data points.

parallel version is at the peak 15% worse than its manually created counterpart.

All experiments were run on the processor Intel Core i9-9900K, 3.6GHz, RAM 16MB. Each experiment was repeated five times and average values were computed. The version of Java used in simulations was JDK 12.0.

# 6 Conclusions and future work

Presented results show that described automatic translation algorithms can speedup various algorithms in java virtual machine. Moreover in many cases the generated parallel code can be as efficient as manually written code. Additionally, the depicted system can choose a proper accelerator and use appropriate strategy by using machine learning approaches. Future work will concentrate on further improvements in automatic parallelisation and testing JVM parallelisation modules on more languages like Scala, JRuby etc. New improvements will also concern machine learning techniques for execution parameter prediction and partial parallel code generation. Further work will also concentrate on testing more complex testbench algorithms for parallelisation.

# References

[1] Joao Rafael, Ivo Correia, Alcides Fonseca, and Bruno Cabral, *Dependency-Based Automatic Parallelization of Java Applications*, August 2014, DOI: 10.1007/978-3-319-14313-2\_16

- [2] Smitha K.P, Aditi Sahasrabudhe, Vinay Vaidya, Method of Extracting Parallelization in Very Large Applications through Automated Tool and Iterative Manual Intervention, Center for Research in Engineering Sciences and Technology (CREST), KPIT Technologies, Pune, India, 2012

- [3] Hilding Elmqvist, Hans Olsson, Axel Goteman, Vilhelm Roxling, Dirk Zimmer, Alexander Pollok, Automatic GPU Code Generation of Modelica Functions, September 2015, DOI: 10.3384/ecp15118235, 11th International Modelica Conference, At Paris, France

- [4] Muthu Manikandan Baskaran, J. Ramanujam and P. Sadayappan, Automatic C-to-CUDA Code Generation for Affine Programs. International Conference on Compiler Construction (CC) 2010

- [5] PPCG Project, http://freecode.com/projects/ppcg

- [6] Javier Setoain, Christian Tenllado, Jose Ignacio Gomez, Manuel Arenaz, Manuel Prieto, and Juan Tourino, *Towards Automatic Code Generation for GPUs*

- [7] Kaixi Hou, Hao Wang, Wu-chun Feng, GPU-UniCache: Automatic Code Generation of Spatial Blocking for Stencils on GPUs

- [8] Benvan Werkhoven, Kernel Tuner: A search-optimizing GPU code auto-tuner, Future Generation Computer Systems Volume 90, January 2019, Pages 347-358

- [9] Alcides Fonseca, Bruno Cabral, João Rafael, Ivo Correia, Automatic Parallelization: Executing Sequential Programs on a Task-Based Parallel Runtime

- [10] Bryan Chan, Run-Time Support for the Automatic Parallelization of Java Programs

- [11] Uday Bondhugula, M. Baskaran, S. Krishnamoorthy, J. Ramanujam, A. Rountev, P. Sadayappan. Automatic Transformations for Communication-Minimized Parallelization and Locality Optimization in the Polyhedral Model. International Conference on Compiler Construction (ETAPS CC), Apr 2008, Budapest, Hungary.

- [12] Uday Bondhugula, A. Hartono, J. Ramanujan, P. Sadayappan. A Practical Automatic Polyhedral Parallelizer and Locality Optimizer. ACM SIGPLAN Programming Languages Design and Implementation (PLDI), Jun 2008, Tucson, Arizona.

- [13] Mehdi Amini, Beatrice Creusillet, Stephanie Even, Ronan Keryell, Onig Goubier, Serge Guelton, Janice Onanian McMahon, François-Xavier Pasquier, Grégoire Péan, Pierre Villalon Par4All: From Convex Array Regions to Heterogeneous Computing. IMPACT 2012, Second International Workshop on Polyhedral Compilation TechniquesJan 23, 2012, Paris, France.

- [14] Chunhua Liao, Daniel J. Quinlan, Jeremiah J. Willcock, Thomas Panas. Semantic-Aware Automatic Parallelization of Modern Applications Using High-Level Abstractions. Journal of Parallel Programming, 2010.

- [15] Intel Corporation (2021). Intel® oneAPI DPC++/C++ Compiler. software.intel.com.

- [16] Makoto Ishihara, Hiroki Honda, Mitsuhisa Sato. Development and Implementation of an Interactive Parallelization Assistance Tool for OpenMP: iPat/OMP.

- [17] Albert Saa-Garriga, David Castells-Rufas, Jordi Carrabina. *OMP2MPI: Automatic MPI code generation from OpenMP programs*. In High Performance Energy Efficient Embedded Systems, 2015.

- [18] Albert Saa-Garriga, David Castells-Rufas, Jordi Carrabina. *OMP2HMPP: HMPP Source Code Generation from Programs with Pragma Extensions*. In High Performance Energy Efficient Embedded Systems, 2014.

- [19] Pascal A. Felber. *OMP2HMPP: Semi-automatic Parallelization of Java Applications*. On The Move to Meaningful Internet Systems 2003, pp. 1369–1383, LNCS, volume 2888.

- [20] João Rafael, Ivo Correia, Alcides Fonseca, Bruno Cabral. Dependency-Based Automatic Parallelization of Java Applications. Euro-Par 2014: Parallel Processing Workshops, pp. 182–193, LNCS, volume 8806.

- [21] Bryan Chan, Tarek S. Abdelrahman. Run-Time Support for the Automatic Parallelization of Java Programs. The Journal of Supercomputing, pp. 91–117, 2004.

- [22] Guodong Han, Chenggang Zhang, King Tin Lam, Cho-Li Wang. Java with Auto-Parallelization on Graphics Coprocessing Architecture. Conference: 42nd International Conference on Parallel Processing (ICPP '13), Lyon, France, October 2013.

- [23] Yu Sun; Wei Zhang. On-Line Trace Based Automatic Parallelization of Java Programs on Multicore Platforms. 15th Workshop on Interaction between Compilers and Computer Architectures, 2011.

- [24] Borys J. Bradel; Tarek S. Abdelrahman. Automatic Trace-Based Parallelization of Java Programs. International Conference on Parallel Processing, ICPP 2007.