# Tailoring potentials by simulation-aided design of gate layouts for spin qubit applications

Inga Seidler,<sup>1</sup> Malte Neul,<sup>1</sup> Eugen Kammerloher,<sup>1</sup> Matthias Künne,<sup>1</sup> Andreas Schmidbauer,<sup>2</sup> Laura Diebel,<sup>2</sup> Arne Ludwig,<sup>3</sup> Julian Ritzmann,<sup>3</sup> Andreas D. Wieck,<sup>3</sup> Dominique Bougeard,<sup>2</sup> Hendrik Bluhm,<sup>1</sup> and Lars R. Schreiber<sup>1, \*</sup>

<sup>1</sup>JARA-FIT Institute for Quantum Information, RWTH Aachen University, 52074 Aachen, Germany

<sup>2</sup> Fakultät für Physik, Universität Regensburg, 93040 Regensburg, Germany

<sup>3</sup>Applied Solid State Physics, Ruhr-Universität Bochum, 44801 Bochum, Germany

(Dated: March 24, 2023)

Gate-layouts of spin qubit devices are commonly adapted from previous successful devices. As qubit numbers and the device complexity increase, modelling new device layouts and optimizing for yield and performance becomes necessary. Simulation tools from advanced semiconductor industry need to be adapted for smaller structure sizes and electron numbers. Here, we present a general approach for electrostatically modelling new spin qubit device layouts, considering gate voltages, heterostructures, reservoirs and an applied source-drain bias. Exemplified by a specific potential, we study the influence of each parameter. We verify our model by indirectly probing the potential landscape of two design implementations through transport measurements. We use the simulations to identify critical design areas and optimize for robustness with regard to influence and resolution limits of the fabrication process.

### I. INTRODUCTION

Demonstrator devices for electron spin qubits have been shown to work with high manipulation [1-9] and readout fidelities [9–12] and indicate a possible path to scaling to a quantum computer [13–18]. Gate-layouts of most demonstrator devices are closely related to or copies of previous devices of a research group or of published layouts. Their functionality has been mostly tested as completed devices and therefore only few iterations are made due to the relatively slow feedback cycle. Scaling up to larger qubit numbers requires optimized and new device layouts. As devices become more complex, testing of many device generations is not sufficient to achieve high yield and robustness to material variations. To this end, simulations are needed to predict functionalities and finally increase the feedback cycle from device measurement to fabrication. Simulation tools are extensively used throughout the advanced semiconductor industry for high complexity devices, as for example technology computer-aided design which is used for transistor, photo detector and miniature solar cell designs [19–21].

In contrast to these applications, spin qubit devices require the accuracy of single electron control, include tunnel barriers and are mostly based on smaller designs. These simulations require additional quantum mechanical constrains. Adaptions of the TCAD software allowing for quantum mechanical restrictions have been implemented with the focus on optimizing qubit distances for manipulation and tunnel couplings [22]. There are simulation-based micro-magnet designs optimised for fast and precise spin manipulation by electric dipolar spin resonance [8, 23, 24]. The coupling to electron reservoirs has been calculated by simulating the induced potential in the 2DEG and approximating the Hamiltonian [25, 26]. A detailed comparison to experimentally applied voltages has only been shown for gate pinchoffs [27].

These modelling efforts are based on ideal devices layouts. However, the consideration of process constrains promises higher functionality and device yields. To that extend, fabricational variations such as line-edge roughness on the order of a few new nanometers [28], and the limitations of patterning with electron beam lithography at non-vertical angles need to be considered [29].

Here, we present a general approach to electrostatic modelling of a targeted potential taking into account the gate structure, doping, reservoirs and applied bias. We consider the influence of fabricational variability to optimize for stability and few device iterations. For a specific targeted potential, implementations for both undoped and doped heterostructures as well as a depletion and accumulation mode designs are considered. For two different heterostructure implementations, the simulated functionality is ratified experimentally.

## **II. TARGET POTENTIAL**

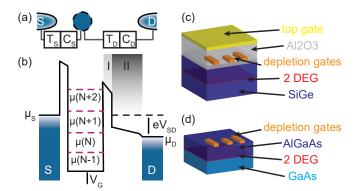

Our approach can be used to implement any targeted potential. To exemplify the possible application, we discuss one specific potential to highlight the studied parameters. For this example, the aim is to form a quantum dot (QD) that has identical tunnel couplings to source and drain reservoir, but a significantly larger capacitive coupling to the source than the drain reservoir (Fig. 1a). We implement this configuration by forming a QD potential with a sharp tunnel barrier to the source reservoir and the drain reservoir with an added potential section in between the second barrier and the drain reservoir. The potential in this added section, named slide, slowly decreases the potential to the chemical potential of the

<sup>\*</sup> lars.schreiber@physik.rwth-aachen.de

drain reservoir over a distance of several 100 nm (Fig. 1b). This specific potential is studied as a QD charge sensor with enhanced performance [12]. A double quantum dot (DQD) is added next to it, which can host the spin qubit. The capacitive coupling between the QD of the sensor and the DQD must be high for good charge sensitivity.

### **III. GATE LAYOUTS**

To highlight the versatility of our simulation approach regarding the heterostructure and the charge accumulation, we choose three different realization, including both a doped and an undoped heterostructure as well as a depletion- and an accumulation-mode design. A depletion-mode design requires a filled two-dimensional electron gas (2DEG) and depletes the QD regions to the few electron regime and has been studied for both doped [30-34] and undoped [1, 3, 35, 36] heterostructures. In the later case, the lack of doping of the 2DEG is compensated by a global top-gate, to which a positive voltage is applied for accumulating charge carriers in the 2DEG. Therefore, on the one hand the gate voltage applied to this global top-gate determines the electron reservoir accumulation, but at the same time it influences the potential in the QD region. This lack of tuning flexibility is often problematic. The problem is solved by an accumulation-mode layout: This is a device with multiple pattern gate-layers, for which positive and negative voltages for accumulation and depletion are chosen within layers [2, 37-40].

We built a finite-element model of a doped GaAs/AlGaAs and undoped Si/SiGe heterostructures with simplified layer stacks in regards to the permittivity of the different materials (Fig. 1c,d) as the basis of the electrostatic simulations. For the GaAs/AlGaAs devices, the depletion gate layer is added directly on top of the heterostructure as metal surfaces. The Si/SiGe devices include an oxide layer underneath the depletion gate layer and between metal gate layers. For the multi-gate layer accumulation design, oxide layers and metal gate layers are alternated. The quantum wells are implemented as a two-dimensional layer within which charges can be accumulated according to the Thomas-Fermi approximation (see Appendix A) [41, 42]. We perform the electrostatic simulation using the finite-element solver COM-SOL Multiphysics (simulation parameters in Appendix B) and determine tunnel-barriers by Wentzel-Kramers-Brillouin (WKB) approximation.

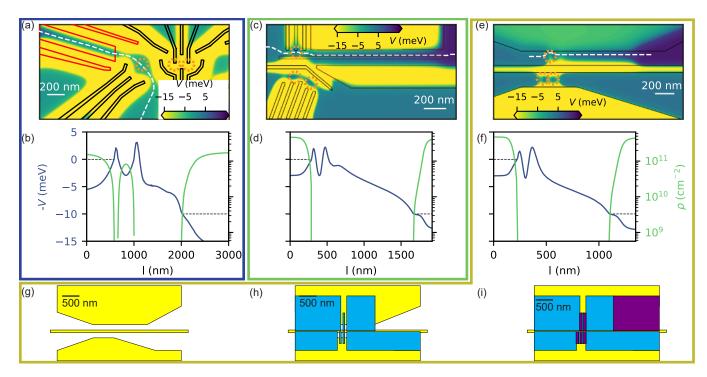

We realize the potential for three different boundary conditions: (I) a doped GaAs/AlGaAs heterostructure (II) an undoped Si/SiGe heterostructure with a global topgate and (III) an undoped Si/SiGe heterostructure with an accumulation mode design. Next to the sensor, a DQD is formed in the QW by properly shaped metal gates. For the GaAs/AlGaAs implementation (I, Fig.2a) the targeted potential is formed by three additional gates

FIG. 1. Parameter Settings. **a** Targeted coupling of a QD (blue) to source (S) and drain (D) reservoir. The tunnel couplings are identical,  $T_S=T_D$ , and the capacitive coupling of the dot to the drain is significantly smaller than to the source,  $C_D \ll C_S$ . **b** Schematic potential matching the requirements in panel a. The tunnel coupling and capacitive decoupling is defined by the potential in section I and II, respectively. **c**,**d** Simulation input parameterization for Si/SiGe and GaAs/AlGaAs heterostructures, respectively.

added to the sensor design (marked red in Fig. 2a). The angle and shape of which are adjusted in the simulation. In the slide region the potential is depleted without generating a barrier. As the optimal path is nontrivial, the Dijkstra's algorithm (see Appendix C) is used to find the optimal path through the tunnel barriers of the sensor and the slide potential (Fig.2b). The charge density shows that due to the applied bias  $V_{\rm SD} = 10 \,\mathrm{mV}$  the 2DEG in the slide region is depleted.

One Si/SiGe implementation (II, Fig.2c) uses similarly to the previous case a gate on top of the slide and two side gates (marked red in Fig. 2c). All three gates are set to positive voltages. The side gates have a small angle  $\alpha$  between each other to ensure a widening potential. The potential line cut through the sensor and corresponding charge density show the targeted slide potential depleted from charge carriers according to the negligibly small charge density  $\rho$  (Fig.2d).

The second Si/SiGe implementation uses an angle in the confinement gates and a separated accumulation gate in the slide region to define the potential (III, Fig. 2e,f), as shown in the gate structure separated into metal layers (Fig. 2g-i). These simulations allow us to optimize the gate layout without fabricating each design while adhering to the fabrication limitations. For each realization, we are able to judge the feasibility of tuning the voltages applied in each layout to generate the targeted potential. Especially, regions with nontrivial cross-coupling from individual gates (mainly non-orthogonal gate structures) can be studied and optimized to fit a specific potential. Therefore, problems such as required unrealistic fine tuning of specific gates can be avoided.

FIG. 2. Modeled electrostatic potential. **a** Potential realization for a doped GaAs/AlGaAs heterostructure. The gate structure (black) and the optimal path (white) are indicated as well as the sensor QD and DQD regions (dashed orange). **b** Line cut of potential V (blue) and charge carrier density  $\rho$  (green) along the optimal path for the realization in panel a. The source and drain levels are indicated (black dashed). **c** Potential realization for an undoped Si/SiGe heterostructure with a global top gate. **d** Line cut of potential and charge carrier density along the optimal path for the realization in panel b. **e** Potential realization for a closed-gate design in an undoped Si/SiGe heterostructure with the first gate layer (black). **g-i** Stacking of layers one (yellow), two (blue) and three (purple) of closed gate design.

#### IV. BENCHMARK SIMULATIONS BY EXPERIMENTS

#### A. Capacitive coupling to sensor QD

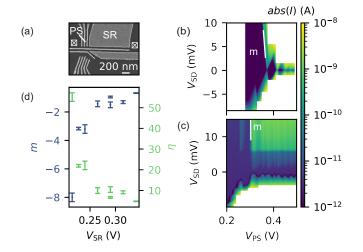

After modelling these very different design layouts, it is indispensable to confirm our simulation methods. To ratify our simulations, we fabricate and test the last design iteration. While the potential is the obvious parameter extracted from the simulations, direct probing of the potential shape for the entire device is hardly possible. Instead we limit ourselves to benchmarking specific measurable properties related to the targeted potential. As an alternative measure, we choose the capacitive coupling of the drain reservoir  $C_{\rm D}$  to the sensor QD for this specific application, which can be extracted from both the simulations and transport measurements.  $C_{\rm D}$  allows us to indirectly probe parameters of the specific underlying potential landscape. Simulations of other device layouts can require an adjusted probing measure, with possibilities being calculated and measured tunnel couplings or relative lever arms of different gates among others.  $C_{\rm D}$ can be extracted from the simulations, by varying the bias  $V_{SD}$  applied between the reservoirs and extracting the leverarm of one reservoir on the QD potential (see Appendix D).

On the experimental side, measuring a QD in transport formed in the targeted at potential (cf. Fig. 1) leads to strongly tilted Coulomb diamonds [12] from which  $C_{\rm D}$ can be measured. A large and continuously declining slide region decouples the drain reservoir. This decoupling leads to a large negative Coulomb diamond slope m, while the positive slope  $(m_+)$  remains nearly constant.

We correlate the slope m to the capacitive coupling  $C_D$  between the drain reservoir and the QD, via the coupling asymmetry  $\eta$  to source and drain reservoir:

$$\eta = \left| \frac{dV_{\rm SD}/dV_{\rm PS}}{dV_{\rm SD}/dV_{\rm PS}} \right| = \left| \frac{m}{m_+} \right|$$

$$= \left| \frac{C_{\rm PS}}{C_{\rm D}} \cdot \frac{C_{\Sigma} - C_{\rm D}}{C_{\rm PS}} \right| = \left| \frac{C_{\Sigma}}{C_{\rm D}} - 1 \right|, \qquad (1)$$

where  $V_{\rm PS}$  is the voltage applied to the QD plunger PS,  $C_{\rm PS}$  and  $C_{\Sigma}$  are the capacitive coupling of the gate PS and the total capacitive coupling of all gates, respectively. To probe the potential, we vary the applied gate voltages in the slide region and extract the slopes of the Coulomb diamonds measured for various voltage configurations. For the case II, Si/SiGe with a global accumulation gate, we measure this experimental dependence.

A device similar to the tested one is depicted in Fig. 3a. The voltage of the marked gate SR is adapted to

FIG. 3. Experimental slide variation. **a** Scanning electron micrograph (SEM) of an identical device with marked slide gate (SR), plunger (PS) and sensor dot Ohmic contacts (crosses). **b,c** Coulomb diamonds with marked slope m for  $V_{\rm SR} = 0.35$  V and  $V_{\rm SR} = 0.24$  V, respectively. **d** Coulomb diamond slopes (blue) and  $\eta$  (green) in dependence of slide gate voltage.

change the potential of the sensor region and control the coupling to the drain reservoir, while the gate PS and the bias applied between the ohmics  $V_{SD}$  are used to measure the diamonds. For larger values of  $V_{SR}$ , the standard Coulomb diamonds (Fig.3b) are measured and the negative slope m of the diamond is extracted. The diamond tilt is enhanced for a decreased voltage applied to gate SR. A steep negative Coulomb diamond slope m is observed for a very low voltage  $V_{SR}$  (Fig. 3c). Comparing m for different slide configurations reveals a systematic decrease in m as a function of a decreasing voltage applied to SR (Fig. 3d). This corresponds to a formation of a slide region after the second barrier which is elongated as lower SR values narrow the path to the drain contact.

The device layout is optimized for an  $\eta = 200$  by simulation. Note that larger asymmetries parameterized by  $\eta$  are possible according to the simulation, but are of limited use as the corresponding tuning of the plunger voltage applied to gate PS needs to be as accurate as  $\Delta V_{\rm PS}=0.5$  mV to use the QD as a sensor. The maximum value obtained experimentally during a separated measurement on second sample is  $\eta=85$ . The discrepancy between the simulation and experiments can be attributed to imperfect gate structures or defects as both required an adjustment of the applied voltages, which will shorten the length of the slide region.

Via this indirect probe, we can measure a few aspects of the potential, such as verifying the tunnel barriers and the formation of a tunable slide region. Even without a general or global potential probe, we can ratify our simulation assumptions.

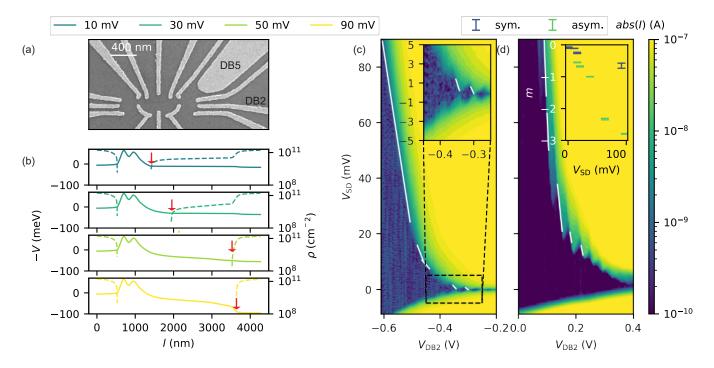

# B. Influence of reservoir bias

Essential for accurately modelling the potential landscape is not only a description of the gate layer influence, but also a good description of the impact of the electron reservoirs and the applied bias  $V_{\rm SD}$  between the source and the drain reservoir of the sensor. The extend of the reservoirs determines the reach of the screening effects of accumulated electrons. A change in  $V_{\rm SD}$  has a large influence on the overall potential landscape and changes the size of reservoirs. For complex gate layouts and bias  $V_{\rm SD}$  electrostatic landscapes, the extend of the reservoirs is non trivial and can only be predicted by simulations.

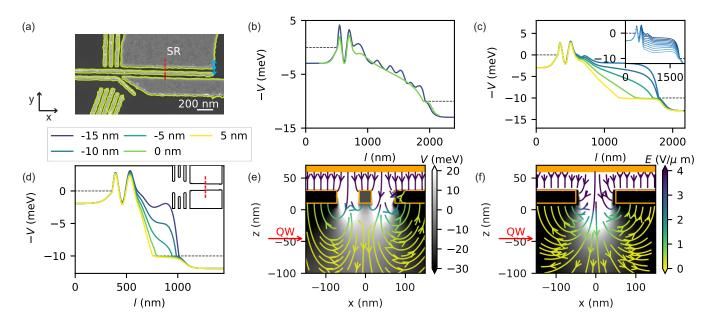

To study the bias  $V_{\rm SD}$  influence, we exemplary use a device similar to case I (Fig. 2a), a doped GaAs/AlGaAs device, which was optimized for larger bias values. A device identical to the one measured and simulated is depicted in Fig. 4a. For this layout, simulations with varying bias voltages  $V_{SD}$  are performed without changing the gate voltages in between (Fig. 4b). The bias  $V_{\rm SD}$  is applied asymmetrically, meaning that only one reservoir potential is shifted. The length of the slide region is determined by the applied  $V_{\rm SD}$  as the reservoir moves into the slide region for low  $V_{SD}$ . The boundaries of the reservoir can be identified by the charge carrier density. We experimentally verify this simulation of the bias impact by comparing to the measured Coulomb diamonds of the device. As discussed for Fig. 3, the extracted capacitive coupling  $C_{\rm D}$  is used as the probe for the potential shape. For large bias voltages  $V_{SD}$ , the Coulomb diamonds tilt even for a QD, which has nearly equal capacitive coupling between sensor QD and its source and drain reservoirs, respectively. We name this type of SET, which does not employ a slide potential, a symmetrically-coupled QD. Here, the asymmetry arise due to a large bias  $V_{\rm SD}$  applied only to one of the two reservoirs. As this device is based on a doped heterostructure, measuring the device with no voltage applied to the gate DB5 allows for the use as a symmetrically-coupled QD. We extract the slope m of the Coulomb diamonds as a function of the bias  $V_{\rm SD}$ (Fig. 4c). The absolute value of the slope increases with the applied bias  $V_{\rm SD}$ .

An asymmetrically coupled QD can be formed, when depleting the slide region by the voltage applied to gate DB5, forming a potential as intended in the simulations (cf. Fig.1b). Then, steeper diamond slopes are observed (Fig. 4d). With an added slide region to the potential, the increase of the slope's m absolute value with an increasing bias  $V_{\rm SD}$  is significantly larger, as expected from the simulations, where the slide length and therefore the capacitive coupling of the drain reservoir to the QD strongly depends on the value of the V<sub>SD</sub> applied (inset Fig. 4d). The experimentally observed larger tilt of the Coulomb-diamonds (Fig. 4c vs d) is correctly predicted by our simulation.

FIG. 4. Bias Influence. **a** SEM of an identical device with marked slide gate (DB5) and sensor plunger (DB2). **b** Simulation of bias influence on the formed potential. Only increasing the bias voltage, the slide length of the induced potential V (solid line) increases. Accordingly, the charge density  $\rho$  (dashed lines) extends into the slide region depending the applied bias. The beginning of the drain reservoir is marked with red arrows. **c** Coulomb diamonds of SET operation with asymmetrically applied bias voltage. The slopes (white lines) of the Coulomb diamond are extracted in the dependence of the applied bias. A current level of 1.5 nA is used as a threshold. For clarity, the low bias regime is depicted as an inset. To realize the SET operation, the slide forming gate voltage  $V_{\text{DB5}}$  is set to zero. **d** Coulomb diamonds of ASD operation with  $V_{\text{DB5}}$ =-0.31 V. For the same current threshold I = 1.5 nA, the slopes m(white lines) are extracted. The extracted m for both operation modes are depicted in the inset in dependence of the applied bias.

### C. Fabricational variability

A significant benefit of simulating different layouts is the possibility to find a robust design with regard to fabricational influences and imperfections. Therefore, we analyze the stability of the simulated gate-layouts with regard to the spatial resolution limit of the nanolithography of the metal gates. Exemplary for the geometry of device type II (cf. Fig.2c), we first study the impact of the line-edge roughness of a patterned gate structure. The edges of the metallic gates of an exemplary device are identified by applying shape recognition on a scanningelectron micrograph (Fig. 5a). The observed realistic line-edge roughness is fed back to our finite-element device model to predict its impact on the targeted potential shape. The calculated potential along the optimal path predicts a slide potential with multiple ripples after fine tuning the voltages applied when using the realistic lineedge roughness in contrast to the perfect gate edges (Fig. 5b). Although the general potential is obtained, we note that a shorter slide region than compared to the ideal gate-layout is likely to occur as the voltages are tuned to form only one QD with two sharp barriers.

Note that in general it is even not required to fabricate an exemplary device. A simple variation of the shape of the metal gates in the simulation is sufficient to study the robustness to fabrications imperfections. In addition to line-edge roughness [43], limitations to accurate alignments of nano-lithography [44] can be explored by simulation. Non-orthogonal and especially small angled gate structures are not fabricated accurately when relying on electron beam lithography [29, 45]. To quantify its impact on the generated potential, we implement small change in angles of the gates in our finite-element model. As an example of angle variation, the position of the corner of the gate labelled SR is changed along the y-axis. This results in variations of the opening angle of the gap between the gates in the slide region (bright blue dot Fig. 5a). For a few nanometers' displacement, our potential simulation predicts that the potential slide is reduced to half its original length or that a flat potential region might occur (yellow and blue line in Fig. 5c, respectively). In the first case, a significantly lower asymmetry n would be experimentally obtained causing a decrease in sensor gain [12]. In the second case the sensor current might be blocked, since the potential disorder (cf. Fig. 5b) alters the flat potential region into a series of disordered QDs and possibly block the current through the sensor region.

Tuning the voltages applied to specific gates can partly

improve the shape of the potential. Also this tunability can be predicted by our device model: For the case of -10 nm displacement, the tunability of the slide with respect to the  $V_{\rm SR}$  voltage is shown in the inset of Fig. 5c. Tuning the voltage dominantly alters the height of the potential within the slide region and therefore has a small influence on the linear slope of the slide. Our discussions show that gate-layouts, which are unreliable with respect to fabrications imperfections, can be studied and the impact of these imperfections can be eliminated by simulation.

We conclude with a final example of simulationsupported gate design, which has motivated our choice to use the thin metal gate in the device type II (Fig. 5a). For this purpose, we compare a summarized and simplified Si/SiGe device-layout (inset Fig. 5d) of a sensor without a capacitivly coupled DQD. Similar to device type II, we include a global accumulation gate in our device model. The simplification to a symmetric single dot without a DQD nearby allows us to reduce the input parameters. Electrostatic simulation of the variation of the angle of the slide forming gates (cf. Fig. 5c) reveal a larger influence on the slide potential shape (Fig. 5d): A second unintentional potential minimum emerges in the optimal path.

The larger influence of variations in the simple device than the case II device (Fig. 2c) can be understood by our simulations as well: It is caused by the electric field gradients at the quantum well (Figs. 5e,f). For the device type II, the simulated potential forms a single minimum at the height of the quantum well (grev scale Fig. 5e, where a little center gate is included). However, the electric field is mainly defined by the gates patterned on the depletion gate layer while the accumulation gate influence is blocked by the central gate along the current path (colorscaled arrows Fig. 5e). For the simple device without the central thin gate, the influence of the global accumulation gate dominates (Fig 5f). Both the electric field (color scaled arrows) and the potential (greyscale) strongly depend on the global accumulation gate. For both devices the gates in the depletion gate layer are tuned to have similar voltages to be less sensitive to variations. Thus, we conclude that the thin long gate in device layout II better screens the effect from the top-gate, which has larger potential difference compared to the difference of the slide gates within the depletion layer. For any aimed at design, the consideration of the generated electric fields is useful, as they indicate layout positions which are most impacted by small variations. As it is not possible to fully avoid fabricational fluctuations, reducing generated electric fields improves the robustness and leads to a higher yield.

#### V. CONCLUSIONS AND OUTLOOK

We show a general approach to electrostatic modelling of spin qubit devices. Our model includes descriptions of the heterostructure, gate layers, reservoirs and applied bias and can be applied to accumulation or depletion type heterostructures. We show gate-designing by device simulation for an exemplary targeted potential shape, which is rather demanding. We experimentally benchmark our simulation by probing predicted gate-voltage dependencies of current through the device. By simulating our device layout, we were able to predict the properties of and successfully operate first generation devices [12]. We included a study to make the gate layout robust to unavoidable fabrications imperfections. With our general finite-element modelling of qubit devices, the electrostatic potential landscape can be predicted and the gate-layout optimized without the need of resource-costly fabrication iterations.

### ACKNOWLEDGEMENTS

This work was funded by ARO under the contract NO W911NF-17-1-0349 titled "A scalable and high performance approach to readout of silicon qubits" and by the German Research Foundation (DFG) within the project 289786932 (BO 3140/4-1 and SCHR 1404/2-1). The device fabrication has been done at HNF - Helmholtz Nano Facility, Research Center Juelich GmbH [46].

#### Appendix A: Thomas-Fermi approximation

The 2DEG is implemented in the simulation as a two dimensional plane throughout which the charge density  $\rho$  determined with the Thomas-Fermi Approximation (TFA):

$$n_{\rm el}(x) = \int D(E) f([[E + eV(x)] - \mu]/k_{\rm B}T) dE$$

(A1)

In the case of SiGe, the valley degeneracy leads to a partially defined electron density:

$$n_{\rm el}(x) = \begin{cases} \frac{2m^*}{\pi\hbar^2}, \ E_{\rm F} + E_{\rm VS} < eV(x) \\ \frac{m^*}{\pi\hbar^2}, \ E_{\rm F} < eV(x) < E_{\rm F} + E_{\rm VS} \\ 0 \ eV(x) < E_{\rm F} \end{cases}$$

(A2)

with  $E_{\rm F}$  corresponding to the Fermi energy,  $E_{\rm VS}$  to the valley splitting energy and V(x) to the potential. Since  $\rho(V) = en_{\rm el}(V)$  and  $V = V(\rho)$ ,  $\rho$  and V have to be solved self-consistently. To include the applied bias,  $V_{\rm SD}$  is added to V(x), where applicable. The boundaries of these regions are determined by the maximum of the tunnel barriers, where the charge density  $\rho = 0$ .

As the TFA is most accurate for large electron numbers, the QD regions need to be considered carefully. For the SiGe simulations, the charge density is set to zero in the QD regions limited by the tunnel barriers. For GaAs, the charge density is measured by TFA also in the QD region.

FIG. 5. Potential robustness. **a** SEM of an indentical device. The edges of the fabricated gates (yellow) are extracted by image processing. **b** Potential line cut along optimal path using the gate edges (panel a) of a fabricated device (blue) and optimal gate edges (green).**c** Influence of slide angle on optimal path potential. The slide angle is varied by changing the y position of the slide endpoint (blue dot panel a). The inset shows the compensation by slide voltage tuning for  $\Delta y = -10$  nm. Starting from the top  $\Delta V_{\text{SR},i} = (i-1) \cdot 10 \text{ mV}$ . **d** Slide angle influence for a simpler device (layout in inset). **e** Cross section of slide potential and electrical field perpendicular to the path at the position marked in red in panel a. The gate edges are marked in field perpendicular to the path at the position for the source cross section of slide potential and electrical field perpendicular to the path at the position for the source cross section of slide potential and electrical field perpendicular to the path at the position for the source cross section of slide potential and electrical field perpendicular to the path at the position for the source cross section of slide potential and electrical field perpendicular to the path at the position marked in red in the inset of panel d.

| Description                        | Variable                    | Si/SiGe            | AlGaAs/GaAs       |

|------------------------------------|-----------------------------|--------------------|-------------------|

| effective<br>electron mass         | $m^*$                       | $0.19 \ m_e^*$     | $0.067  m_e^*$    |

| valley splitting                   | $E_{\rm VS}$                | $70\mu\mathrm{eV}$ | n.a.              |

| Fermi energy                       | $E_F$                       | $555\mathrm{meV}$  | $6.5\mathrm{meV}$ |

| permittivity of<br>heterostructure | $\epsilon_r$                | 13                 | 13                |

| permittivity of oxide              | $\epsilon_{\mathrm{oxide}}$ | 11.3               | n.a.              |

| gate height                        | $h_{\text{gate}}$           | 20 nm              | 30 nm             |

| oxide height                       | $h_{\text{oxide}}$          | 10 nm              | n.a.              |

| min. element<br>size (ES)          | $d_{\min}$                  | $5\mathrm{nm}$     | $1\mathrm{nm}$    |

| max. ES                            | $d_{\max}$                  | 75 nm              | $150\mathrm{nm}$  |

| min. 2DEG ES                       | $d_{\min,2DEG}$             | 1 nm               | $1\mathrm{nm}$    |

| max. 2DEG ES                       | $d_{\rm max, 2DEG}$         | 15 nm              | $15\mathrm{nm}$   |

| depth of 2DEG                      | $z_{ m 2DEG}$               | $45\mathrm{nm}$    | 90 nm             |

TABLE I. COMSOL simulation parameters.

#### **Appendix B: Simulation parameters**

The parameters used to model the Si/SiGe and Al-GaAs/GaAs implementations are listed in Tab. I. Both the AlGaAs/GaAs and the Si/SiGe implementation use a fine mesh in the 2DEG region and specifically the QD regions as well as a limited maximum element size to accurately describe the effect of the small gates.

### Appendix C: Dijkstra's algorithm for determination of linecuts

As the simulated potential channel has no inherent symmetry, Dijkstra's algorithm used to calculate a well defined path for a linecut through the two-dimensional (2D) potential landscape. This algorithm calculates the cheapest path between two nodes in a graph, where the nodes were defined as the mesh points used for the simulation. The cost function C between the nodes was defined as

$$C = \operatorname{Re}\left(\sqrt{E_F - eV(\mathbf{x})}\right) - \epsilon eV(\mathbf{x}), \qquad (C1)$$

where the first part  $(\sqrt{E_F - eV(\mathbf{x})})$  was based on the semiclassical Wentzel-Kramers-Brillouin (WKB) approximation and the second part  $(eV(\mathbf{x}))$  was based on a classical path-of-lowest-potential. The WKB approximation was thereby used to determine the path through the barriers. Only the real part of the square root was therefore of interest and constants were neglected. The dynamically calculated prefactor  $\epsilon$  was chosen to be small, so that the cost function was completely dominated by the WKB contribution and the potential only had an influence outside the barrier zones.

The calculated path supports visualization of the relevant potential region. While the well defined cost function allows the comparison between different devices, it does not represent the quantum mechanical behavior of the electron.

### Appendix D: Capacity extraction from simulation

The coupling asymmetry  $\eta$  depends on the capacitance ratio  $C_{\Sigma}C_{\rm D}^{-1}$ . The potential of the dot depends linearly on the voltage applied to the drain reservoir  $V_{\rm SD}$  with the factor  $\alpha_{\rm D} = -C_{\rm D}C_{\Sigma}^{-1}$ . This was extracted from the simulations by varying  $V_{\rm SD}$  and monitoring the potential minimum  $V_0$ .  $\eta$  is then given by

$$\eta = \left| \frac{C_{\Sigma}}{C_{\rm D}} - 1 \right| = \frac{1}{\alpha_{\rm D}} + 1 \tag{D1}$$

This was realized by running the simulation for a specific design nine times with varying  $V_{\rm SD} = -10 \,\mathrm{mV} + [-1 \,\mathrm{mV}, -0.75 \,\mathrm{mV}, -0.5 \,\mathrm{mV}, -0.25 \,\mathrm{mV}, 0 \,\mathrm{mV}, +0.25 \,\mathrm{mV}, +0.5 \,\mathrm{mV}, +0.75 \,\mathrm{mV}, +1 \,\mathrm{mV}]$ . The potential minimum was determined for each simulation by placing an ellipse around the dot and evaluating the potential on each mesh point inside. As the potential was only evaluated on the points of the discrete mesh, the element density was set accordingly to ensure a high enough resolution to cover possible shifts in the spatial position of the potential minimum. The so obtained potential minima were then plot-

- J. Yoneda, K. Takeda, T. Otsuka, T. Nakajima, M. R. Delbecq, G. Allison, T. Honda, T. Kodera, S. Oda, Y. Hoshi, N. Usami, K. M. Itoh, and S. Tarucha, A quantum-dot spin qubit with coherence limited by charge noise and fidelity higher than 99.9%, Nat. Nanotechnol. 13, 102 (2018).

- D. M. Zajac, A. J. Sigillito, M. Russ, F. Borjans, J. M. Taylor, G. Burkard, and J. R. Petta, Resonantly driven CNOT gate for electron spins, Science **359**, 439 (2018).

- 3. T. F. Watson, S. G. J. Philips, E. Kawakami, D. R. Ward, P. Scarlino, M. Veldhorst, D. E. Savage, M. G. Lagally, M. Friesen, S. N. Coppersmith, M. A. Eriksson, and L. M. K. Vandersypen, A programmable two-qubit quantum processor in silicon, Nature 555, 633 (2018).

- X. Xue, T. F. Watson, J. Helsen, D. R. Ward, D. E. Savage, M. G. Lagally, S. N. Coppersmith, M. A. Eriksson, S. Wehner, and L. M. K. Vandersypen, Benchmarking gate fidelities in a Si/SiGe two-qubit device, Phys. Rev. X 9, 021011 (2019).

- X. Xue, M. Russ, N. Samkharadze, B. Undseth, A. Sammak, G. Scappucci, and L. M. K. Vandersypen, Quantum logic with spin qubits crossing the surface code threshold, Nature 601, 343 (2022).

- 6. M. T. Madzik, S. Asaad, A. Youssry, B. Joecker, K. M. Rudinger, E. Nielsen, K. C. Young, T. J. Proctor, A. D. Baczewski, A. Laucht, V. Schmitt, F. E. Hudson, K. M. Itoh, A. M. Jakob, B. C. Johnson, D. N. Jamieson, A. S. Dzurak, C. Ferrie, R. Blume-Kohout, and A. Morello, Precision tomography of a three-qubit donor quantum

480 500

10

0

-10

-20

0

$\Delta V_{SD}$  (meV)

1

$\Delta V_{dot}$  ( $\mu eV$ )

-2.4

500

1000

1 (nm)

0

-3

-6

-9

-12

-V (meV)

ted against  $V_{\rm SD}$  and fitted to obtain  $\alpha_{\rm D}$  as shown in Fig.

FIG. 6. Determination of the gate lever-arm  $\alpha_{\rm D}$  by simulation. **a** Potential line cut along optimal path for bias voltages  $V_{\rm SD}$ . **b** Change in potential minima  $\Delta V_{\rm dot}$ , obtained from an interpolation in the QD region of the 2D data of the potential linecuts in panel a, as a function of the change in bias voltage  $\Delta V_{\rm SD}$ . The data points are linearly fitted to obtain the slope  $\alpha_{\rm D}$  (green).

1500

processor in silicon, Nature 601, 348 (2022).

- A. Noiri, K. Takeda, T. Nakajima, T. Kobayashi, A. Sammak, G. Scappucci, and S. Tarucha, Fast universal quantum gate above the fault-tolerance threshold in silicon, Nature **601**, 338 (2022).

- S. G. J. Philips, M. T. Madzik, S. V. Amitonov, S. L. de Snoo, M. Russ, N. Kalhor, C. Volk, W. I. L. Lawrie, D. Brousse, L. Tryputen, B. P. Wuetz, A. Sammak, M. Veldhorst, G. Scappucci, and L. M. K. Vandersypen, Universal control of a six-qubit quantum processor in silicon, Nature **609**, 919 (2022).

- 9. A. R. Mills, C. R. Guinn, M. M. Feldman, A. J. Sigillito, M. J. Gullans, M. T. Rakher, J. Kerckhoff, C. A. C. Jackson, and J. R. Petta, High-fidelity state preparation, quantum control, and readout of an isotopically enriched silicon spin qubit, Phys. Rev. Appl. 18, 064028 (2022).

- E. J. Connors, J. Nelson, and J. M. Nichol, Rapid highfidelity spin-state readout in Si/Si-Ge quantum dots via rf reflectometry, Phys. Rev. Appl. 13, 024019 (2020).

- A. Noiri, K. Takeda, J. Yoneda, T. Nakajima, T. Kodera, and S. Tarucha, Radio-frequency-detected fast charge sensing in undoped silicon quantum dots, Nano Lett. 20, 947 (2020).

- 12. E. Kammerloher, A. Schmidbauer, L. Diebel, I. Seidler, M. Neul, M. Künne, A. Ludwig, J. Ritzmann, A. D. Wieck, D. Bougeard, L. R. Schreiber, and H. Bluhm, Sensing dot with high output swing for scalable baseband readout of spin qubits, arXiv:2107.13598 [cond-mat.meshall] (2021).

- L. C. L. Hollenberg, A. D. Greentree, A. G. Fowler, and C. J. Wellard, Two-dimensional architectures for donorbased quantum computing, Phys. Rev. B 74, 045311 (2006).

- 14. L. M. K. Vandersypen, H. Bluhm, J. S. Clarke, A. S. Dzurak, R. Ishihara, A. Morello, D. Reilly, L. R. Schreiber, and M. Veldhorst, Interfacing spin qubits in quantum dots and donors—hot, dense, and coherent, npj Quantum Inf. 3, 34 (2017).

- M. Veldhorst, H. G. J. Eenink, C. H. Yang, and A. S. Dzurak, Silicon CMOS architecture for a spin-based quantum computer, Nat. Commun. 8, 1766 (2017).

- 16. R. Li, L. Petit, D. P. Franke, J. P. Dehollain, J. Helsen, M. Steudtner, N. K. Thomas, Z. R. Yoscovits, K. J. Singh, S. Wehner, L. M. K. Vandersypen, J. S. Clarke, and M. Veldhorst, A crossbar network for silicon quantum dot qubits, Sci. Adv. 4, eaar3960 (2018).

- 17. J. M. Boter, J. P. Dehollain, J. P. G. van Dijk, T. Hensgens, R. Versluis, J. S. Clarke, M. Veldhorst, F. Sebastiano, and L. M. K. Vandersypen, A sparse spin qubit array with integrated control electronics, 2019 IEEE International Electron Devices Meeting (IEDM), 31.4.1 (2019).

- 18. J. M. Boter, J. P. Dehollain, J. P. G. van Dijk, Y. Xu, T. Hensgens, R. Versluis, H. W. L. Naus, J. S. Clarke, M. Veldhorst, F. Sebastiano, and L. M. K. Vandersypen, The spider-web array: A sparse spin-qubit array, Phys. Rev. Appl. 18, 024053 (2022).

- R. Tiwari, N. Parihar, K. Thakor, H. Y. Wong, S. Motzny, M. Choi, V. Moroz, and S. Mahapatra, A 3-d tcad framework for nbti—part i: Implementation details and finfet channel material impact, IEEE Transactions on Electron Devices 66, 2086 (2019).

- 20. B. Jacob, B. Witzigmann, M. Klemenc, and C. Petit, A tcad methodology for high-speed photodetectors, Solid State Electron. 49, 1002 (2005).

- 21. J. Greulich, A.-K. Volk, N. Wöhrle, I. Haedrich, M. Wiese, M. Hermle, and S. Rein, Optical simulation and analysis of iso-textured silicon solar cells and modules including light trapping, Energy Procedia 77, 69 (2015), 5th International Conference on Silicon Photovoltaics, SiliconPV 2015.

- 22. F. A. Mohiyaddin, G. Simion, N. I. D. Stuyck, R. Li, F. Ciubotaru, G. Eneman, F. M. Bufler, S. Kubicek, J. Jussot, B. Chan, T. Ivanov, A. Spessot, P. Matagne, J. Lee, B. Govoreanu, and I. P. Raduimec, Multiphysics simulation & design of silicon quantum dot qubit devices, in 2019 IEEE International Electron Devices Meeting (IEDM) (2019) pp. 39.5.1–39.5.4.

- 23. M. Pioro-Ladrière, T. Obata, Y. Tokura, Y.-S. Shin, T. Kubo, K. Yoshida, T. Taniyama, and S. Tarucha, Electrically driven single-electron spin resonance in a slanting Zeeman field, Nat. Phys. 4, 776 (2008).

- R. Neumann and L. R. Schreiber, Simulation of micromagnet stray-field dynamics for spin qubit manipulation, J. Appl. Phys. 117, 193903 (2015).

- 25. J. Klos, F. Hassler, P. Cerfontaine, H. Bluhm, and L. R. Schreiber, Calculation of tunnel couplings in open gatedefined disordered quantum dot systems, Phys. Rev. B 98, 155320 (2018).

- 26. S. Rochette, M. Rudolph, A.-M. Roy, M. J. Curry, G. A. T. Eyck, R. P. Manginell, J. R. Wendt, T. Pluym, S. M. Carr, D. R. Ward, M. P. Lilly, M. S. Carroll, and M. Pioro-Ladrière, Quantum dots with split enhancement

gate tunnel barrier control, Appl. Phys. Lett. **114**, 083101 (2019).

- E. Chatzikyriakou, J. Wang, L. Mazzella, A. Lacerda-Santos, M. C. d. S. Figueira, A. Trellakis, S. Birner, T. Grange, C. Bäuerle, and X. Waintal, Unveiling the charge distribution of a gaas-based nanoelectronic device: A large experimental dataset approach, Phys. Rev. Res. 4, 043163 (2022).

- 28. H. Miyoshi and J. Taniguchi, Fabricating a highresolution mask with improved line-edge roughness by using a nonchemically amplified resist and a postexposure bake, J. Vac. Sci. Technol. B **33**, 06FD05 (2015).

- 29. I. W. Rangelow, Z. Borkowicz, P. Hudek, and I. Kostič, Transfer of single-layer positive resist sub-micrometer and nanometer structures into silicon, Microelectron. Eng. 25, 49 (1994).

- 30. H. Bluhm, S. Foletti, I. Neder, M. Rudner, D. Mahalu, V. Umansky, and A. Yacoby, Dephasing time of GaAs electron-spin qubits coupled to a nuclear bath exceeding 200  $\mu$ s, Nat. Phys. **7**, 109 (2011).

- 31. T. A. Baart, M. Shafiei, T. Fujita, C. Reichl, W. Wegscheider, and L. M. K. Vandersypen, Single-spin CCD, Nat. Nanotechnol. **11**, 330 (2016).

- 32. H. Flentje, P.-A. Mortemousque, R. Thalineau, A. Ludwig, A. D. Wieck, C. Bäuerle, and T. Meunier, Coherent long-distance displacement of individual electron spins, Nat. Commun. 8, 501 (2017).

- 33. C. Payette, K. Wang, P. J. Koppinen, Y. Dovzhenko, J. C. Sturm, and J. R. Petta, Single charge sensing and transport in double quantum dots fabricated from commercially grown si/sige heterostructures, Appl. Phys. Lett. 100, 043508 (2012).

- 34. J. R. Prance, Z. Shi, C. B. Simmons, D. E. Savage, M. G. Lagally, L. R. Schreiber, L. M. K. Vandersypen, M. Friesen, R. Joynt, S. N. Coppersmith, and M. A. Eriksson, Single-shot measurement of triplet-singlet relaxation in a Si/SiGe double quantum dot, Phys. Rev. Lett. **108**, 046808 (2012).

- 35. A. Hollmann, T. Struck, V. Langrock, A. Schmidbauer, F. Schauer, T. Leonhardt, K. Sawano, H. Riemann, N. V. Abrosimov, D. Bougeard, and L. R. Schreiber, Large, tunable valley splitting and single-spin relaxation mechanisms in a  $Si/Si_xGe_{1-x}$  quantum dot, Phys. Rev. Appl. **13**, 034068 (2020).

- 36. T. Struck, A. Hollmann, F. Schauer, O. Fedorets, A. Schmidbauer, K. Sawano, H. Riemann, N. V. Abrosimov, L. Cywiński, D. Bougeard, and L. R. Schreiber, Low-frequency spin qubit energy splitting noise in highly purified 28 Si/SiGe, npj Quantum Inf. 6, 1 (2020).

- 37. M. Veldhorst, J. C. C. Hwang, C. H. Yang, A. W. Leenstra, B. de Ronde, J. P. Dehollain, J. T. Muhonen, F. E. Hudson, K. M. Itoh, A. Morello, and A. S. Dzurak, An addressable quantum dot qubit with fault-tolerant controlfidelity, Nat. Nanotechnol. 9, 981 (2014).

- 38. T. McJunkin, E. R. MacQuarrie, L. Tom, S. F. Neyens, J. P. Dodson, B. Thorgrimsson, J. Corrigan, H. E. Ercan, D. E. Savage, M. G. Lagally, R. Joynt, S. N. Coppersmith, M. Friesen, and M. A. Eriksson, Valley splittings in si/sige quantum dots with a germanium spike in the silicon well, Phys. Rev. B **104**, 085406 (2021).

- 39. Y.-Y. Liu, S. G. J. Philips, L. A. Orona, N. Samkharadze, T. McJunkin, E. R. MacQuarrie, M. A. Eriksson, L. M. K. Vandersypen, and A. Yacoby, Radio-frequency reflectometry in silicon-based quantum dots, Phys. Rev.

Appl. 16, 014057 (2021).

- 40. I. Seidler, T. Struck, R. Xue, N. Focke, S. Trellenkamp, H. Bluhm, and L. R. Schreiber, Conveyor-mode singleelectron shuttling in Si/SiGe for a scalable quantum computing architecture, npj Quantum Inf. 8, 100 (2022).

- L. H. Thomas, The calculation of atomic fields, Math. Proc. Camb. Philos. Soc. 23, 542–548 (1927).

- 42. E. Fermi, Eine statistische Methode zur Bestimmung einiger Eigenschaften des Atoms und ihre Anwendung auf die Theorie des periodischen Systems der Elemente, Z. Phys. 48, 73 (1928).

- 43. M. Brauns, S. V. Amitonov, P.-C. Spruijtenburg, and F. A. Zwanenburg, Palladium gates for reproducible quantum dots in silicon, Sci. Rep. 8, 5690 (2018).

- 44. J. Moers, S. Trellenkamp, D. Grützmacher, A. Offenhäusser, and B. Rienks, Optimized marker definition

for high overlay accuracy e-beam lithography, Microelectron. Eng. **97**, 68 (2012).

- 45. V. Brackmann, M. Friedrich, C. Browning, N. Hanisch, and B. Uhlig, Influence of the dose assignment and fracturing type on patterns exposed by a variable shaped e-beam writer: simulation vs experiment, in 35th European Mask and Lithography Conference (EMLC 2019), Vol. 11177, edited by U. F. W. Behringer and J. Finders, International Society for Optics and Photonics (SPIE, 2019) p. 1117713.

- 46. W. Albrecht, J. Moers, and B. Hermanns, HNF -Helmholtz Nano Facility, Journal of large-scale research facilities JLSRF 3, A112 (2017).