## E lectrostatic Engineering of N anotube Transistors for Im proved Perform ance

S.Heinze, J.Terso <sup>y</sup>, and Ph.Avouris

IBM Research Division, T.J.W atson Research Center, Yorktown Heights, New York 10598

(M arch 22, 2024)

W ith decreasing device dimensions, the performance of carbon nanotube eld-e ect transistors (CNFETs) is limited by high O currents except at low drain voltages. We show that an asymmetric design improves the performance, reducing O -currents and extending the usable range of drain voltage. The improvement is most dramatic for ambipolar Schottky-barrierCNFETs. Moreover, this approach allows a single device to exhibit equally good performance as an n-or p-type transistor, by changing only the sign of the drain voltage. Even for CNFET shaving ohm ic contacts, an asymmetric design can greatly improve the performance for small-bandgap nanotubes.

The perform ance of carbon nanotube eld-e ect transistors (CNFETs) can be greatly improved in many respects by scaling the devices to smaller size<sup>1</sup><sup>4</sup>. However, the improvements with smaller size are accompanied by the undesired e ect of a lowered 0 n-0 ratio at typical drain voltages. This restricts the range of usable drain voltage, which in turn limits the achievable 0 n-currents. Most CNFETs to date operate as Schottky barrier (SB) CNFETs<sup>1</sup><sup>7</sup>, and the issue has been studied in detail for such devices<sup>7,8</sup>. But the problem occurs even for ohm ic contacts, especially for small-bandgap tubes, as shown below.

Here, we propose a novel device design for CNFETs that can be scaled down in size for good turn-on perform ance without severe restrictions on the usable drain voltage. The key idea of the new design is to have large electric elds at the source contact but sm all elds at the drain, to suppress unwanted tunneling. A related approach has recently been demonstrated for Sibased SB-FETs<sup>9</sup>.

For an ambipolar SB-CNFET, the asymmetric design can suppress either the p-or the n-type branch of the ambipolar transport characteristic, depending only on the sign of the drain voltage. Thus the same device can act as an excellent p- or n-type transistor, and the tum-on performance for both types is controlled by the electrostatics (the geometry of the contact and gate) at the source electrode. By choosing metals of di erent work function for the gates, it should be possible to fabricate com plan entary SB-CNFETs that have the desired alignment of transfer characteristics (I vs.  $V_g$ ) for standard logic applications.

For a SB-CNFET, the asymmetric design solves the problem of O -current that increases exponentially with drain voltage, so it allows larger On-currents. This is a critical issue as the device dimensions decrease<sup>7,8</sup>. Moreover, even for a CNFET having ohm ic contacts<sup>10</sup>, e.g. to the valence band, suppressing the current into the conduction band can be essential when the nanotube (NT) bandgap is sm all.

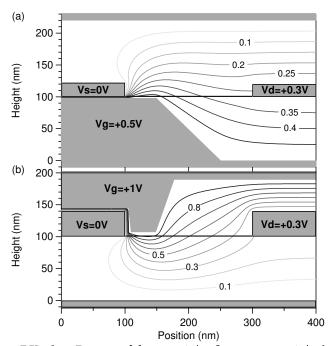

Two examples of possible asymmetric device geometries are shown in Fig. 1. The rst design, Fig. 1(a), relies on having a di erent thickness for the bottom oxide at the source and drain contacts. The second design, Fig. 1 (b), em ploys a top gate close to the source contact but not the drain. O ther ways of engineering the electric elds are possible, such as a sharp source electrode to focus the eld at the contact, and a blunt drain electrode to reduce the eld there.

FIG.1. Two possible geometries for an asymmetric device. Contour lines show the electrostatic potential. The applied voltages are given in the plot. (a) A bottom gate device with di erent oxide thicknesses at source (2 nm) and drain (100 nm) contact. The top plane is grounded. A djacent contour lines di er by 0.05 V. (b) A local top gate close to the source contact. The bottom plane is grounded. A djacent contour lines di er by 0.15 V.

To study the transport characteristics of these devices, we use a sem iclassical model which has been described elsewhere<sup>2;4;7</sup>. We assume ballistic transport within the NT (over the short distances of interest here)<sup>10;11</sup>. For SB-CNFETs, the current is controlled by the rate of therm ally assisted tunneling (at room temperature) through the SBs at the source and drain contact. We neglect charge on the NT, which is a good approximation for the O -state and in the turn-on regim  $e^{2/8}$ .

For concreteness, we focus on the asym metric bottom gate device, Fig. 1(a). At the source contact the oxide thickness,  $t_{ox}$ , is only 2 nm. CNFETs with symmetric source and drain contacts of such low oxide thickness have been fabricated and show very good turn-on perform ance<sup>4;7</sup>. We rst treat ideally ambipolar devices, where the metalFerm i level falls in the middle of the NT bandgap at each contact. The NT band gap is taken to be 0:6 eV, corresponding to a diameter of 1:4 nm. O ther cases are discussed below.

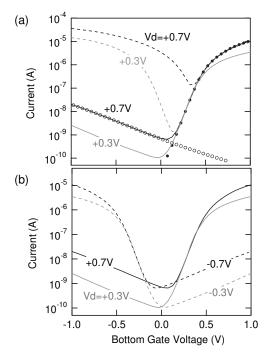

FIG.2. (a) Calculated transfer characteristics for a sym – m etric ( $t_{\rm ox}$  = 2 nm, dashed lines) and an asymmetric CN-FET (geometry of Fig.1(a), solid lines). For the asymmetric CNFET, the electron and hole contributions to the current are given separately (lled and open circles, respectively) for  $V_d = +0.7 V$ . (b) Transfer characteristics of the asymmetric CNFET at positive  $V_d$  (solid lines) and negative  $V_d$  (dashed lines).

The calculated transfer characteristics for a sym metric CNFET with  $t_{ox} = 2$  nm are shown as dashed lines in Fig. 2 (a). The quality of the turn-on perform ance can be quanti ed by the subtrreshold slope, de ned by  $S = (d \log_{10} I=dV_g)^{-1}$ , where I is the device current and  $V_g$  is the gate voltage. The value of S for the sym metric CNFET of Fig. 2 (a) is 110 mV/decade. (This is already within a factor of 2 of the therm all in it of a conventional transistor, 60 mV/decade.) How ever, the ratio between 0 n-and 0 -current decreases with increased drain voltage  $V_d$ . At  $V_d = +0.7 \text{ V}$ , the ratio is only two orders of m agnitude, well below the range desired for transistors. This drain voltage e ect has been investigated in detail for such symmetric  $CNFETs^{7,8}$ , where it represents an important limitation.

In contrast, the asymmetric design of Fig.1(a) allows a high  $0\,n/0~$  ratio even at higher  $V_d$ , while preserving other good features of the behavior. This is shown by the solid lines in Fig.2(a). At positive  $V_d$ , the slope in the turn-on regime (e.g.  $V_g~~0.3$ ) is the same as for the symmetric device. However, the 0~-current is much lower than for the symmetric device, and the  $0\,n-0~$  ratio is greatly in proved, to over 4 orders of magnitude at  $V_d$  =  $+\,0.7\,V$ .

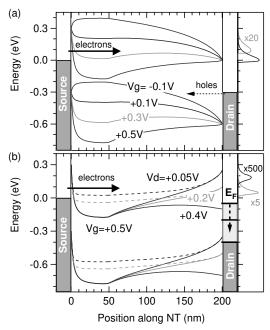

FIG.3. The calculated band bending within the nanotube channel for the asymmetric device of Fig.1(a). (a) Fixed  $V_d = \pm 0.3$  V with varying  $V_g$ . The right side shows the contribution to the current vs. energy in arbitrary units for  $V_g = \pm 0.3$  V (gray line) and  $\pm 0.5$  V (black line). (b) Fixed  $V_g = \pm 0.5$  V with varying  $V_d$ . The right side shows the contribution to the current vs. energy in arbitrary units for  $V_d = \pm 0.05$  V (black line) and  $\pm 0.2$  V (gray line). Dashed lines illustrate (for  $V_d = \pm 0.05$  V and 0.2 V) the elect of including charge on the NT, within a local approximation<sup>2</sup>. W hile the band bending is substantially di erent in the channel, the current in the subthreshold regime is virtually unchanged<sup>12</sup>.

The contributions of electrons and holes to the current are shown separately for one case in Fig. 2(a). For the asymmetric CNFET at positive  $V_d$ , the hole current is suppressed, changing the behavior from ambipolar for a symmetric device to n-type for the asymmetric device. By merely reversing the sign of  $V_d$ , one can instead suppress the electron current, making the same asymmetric CNFET behave as a p-type transistor with identical perform ance, as shown in Fig. 2(b). The transfer characteristics (I vs.  $V_g$ ) of the asymm etric device can be understood based on the calculated band bending shown in Fig. 3(a) for  $V_d = +0.3$  V. At large positive  $V_g$  (+0.5 V) the behavior is similar to a symmetric device | the SB at the source is su ciently thin for electrons to be injected, and there is little or no barrier for them to be collected at the drain. Thus the current is relatively large [see Fig. 2(a)]. As  $V_g$  is reduced, the source SB becomes wider, until electron injection becomes negligible for  $V_g$ . +0.1 V.

For negative  $V_g$ , while the electron current remains negligible, holes can be injected at the drain and are then easily collected at the source. This is the origin of the ambipolar characteristic (and of the undesirable O -current) in symmetric devices<sup>7</sup>. In our asymmetric device, however, the geometry is chosen so that the SB at the drain remains rather wide, suppressing hole tunneling. Thus the device shows purely n-type character.

At negative  $V_d$ , the argument is reversed electron transport is suppressed due to the barrier at the drain contact, while the hole current is as for a symmetric device. Thus by simply changing the sign of  $V_d$ , we can operate the same device as either an excellent p-or n-type transistor, with a turn-on performance controlled by the source contact geometry. This is a key advantage of the new device design. In principle, complementary n- and p-type transistors based on ohm ic contacts (to the conduction and valence band respectively) would give even better performance; but the need for both kinds of contacts presents a form idable obstacle to such a design at present.

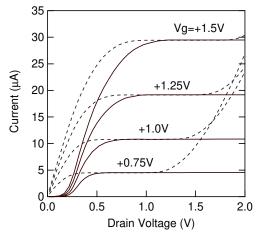

FIG.4. Calculated output characteristics of the sym m etric (dashed lines) and the asym metric (solid lines) CNFET. D evice geometries are the same as for Fig.2.

The output characteristics (I vs. $V_d$ ) of the asym m etric and the sym m etric CNFET are compared in Fig. 4. For the asym m etric device, the current starts to rise appreciable only for  $V_d$  & half the NT bandgap. The lack of a linear regim e of I vs.  $V_d$  for the asym m etric device does not hinder digital/logic applications which rely on the plateau of saturating current. The plateaus are actually greatly improved for asymmetric CNFETs. For symmetric devices, these plateaus are limited by the onset of the drain leakage current<sup>7</sup>.

The output characteristics can be understood by examining the band bending at xed V<sub>g</sub>, Fig. 3(b). At V<sub>g</sub> = 0.5 V, the SB at the source is su ciently thin for high transmission. However, at low V<sub>d</sub> (= +0.05 V) the electrons injected at the source contact cannot enter the drain contact due to the thick potential barrier<sup>12</sup>. By increasing V<sub>d</sub> the barrier at the drain contact is low ered and the injected electrons can be collected at the drain. Thus a V<sub>d</sub> of about half the NT band gap is required for a signi cant ow of current (c.f. Fig. 4). W ith further increase of V<sub>d</sub> the current saturates, being limited by V<sub>g</sub> in the absence of short-channel e ects) rather than by the drain.

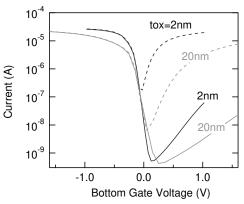

FIG.5. Calculated transfer characteristics at  $V_d = 0.2 V$  for a NT with a bandgap of 0.3 eV and an ohm ic contact to the valence band. Solid and dashed lines are for asym m etric and sym m etric CNFET, respectively.

So farwe have focused on am bipolar SB-CNFETs; but ohm ic contacts could provide further perform ance im provem ents<sup>10</sup>. O hm ic contacts are m ost readily achieved for NTs having sm all bandgap<sup>10</sup>, in which case we nd that drain leakage current is still an issue, except at very sm all V<sub>d</sub>. Figure 5 shows calculations for a device having ohm ic contacts to the valence band, and where the NT bandgap is 0.3 eV, as in Ref. 10. As expected, the subthreshold slope is excellent (65 m V /dec for  $t_{ox} = 2 \text{ nm}$ ). However, for a sym metric CNFET, the SB to the conduction band (i.e. the bandgap) is only 03 eV. Thus positive V<sub>g</sub> can induce substantial electron tunneling, leading to the behavior shown by dashed lines in Fig. 5. This electron tunneling is signi cant even for a 20 nm oxide; and for very thin oxides the e ect is dram atic, as shown for  $t_{ox} = 2 \text{ nm}$  .

For a CNFET having ohm ic contacts, the leakage current can be suppressed by an asymmetric geometry, just as for the ambipolar devices described above. Thus, without excessively restricting  $V_d$ , one can achieve a dramatic

in provem ent of the On-O  $\,$  ratio, suppressing the drain leakage current over a large range of  $V_g$ . As thin oxides are necessary for high perform ance CNFETs, the asym-m etric device design m ay play a key role even for devices based on ohm ic contacts, and even m ore so for Schottky barrier transistors.

We thank M arko Radosavljevic and Richard M artel for valuable discussions. S. H. thanks the Deutsche Forschungsgem einschaft for nancial support under the G rant num ber HE 3292/2-1.

- Present address: Institut fur Festkorperforschung, Forschungszentrum Julich, 52425 Julich, Germany.

- <sup>y</sup> E lectronic address: terso @ us.ibm.com

- <sup>1</sup> A . Bachtold, P. Hadley, T. Nakanishi, and C. Dekker, Science 294, 1317 (2001).

- <sup>2</sup> S.Heinze et al, Phys.Rev.Lett. 89, 106801 (2002).

- <sup>3</sup> J.Appenzeller et al, Phys. Rev. Lett. 89, 126801 (2002).

- <sup>4</sup> S.Heinze, M.Radosavljevic, J.Terso, and Ph.Avouris, cond-m at/0302175.

- <sup>5</sup> R.M artel et al, Phys.Rev.Lett. 87, 256805 (2001).

- <sup>6</sup> M.Freitag, M.Radosavljevic, Y.Zhou, A.T.Johnson, and W.F.Smith, Appl. Phys. Lett. 79, 3326 (2001).

- <sup>7</sup> M.Radosavljevic, S.Heinze, J.Terso, and Ph.Avouris, cond-mat/0305570 (to appear in Appl.Phys.Lett.)

- <sup>8</sup> J.Guo, S.Datta, and M.Lundstrom, cond-m at/0306199.

<sup>9</sup> H.C.Lin, K.L.Yeh, R.G.Huang, C.Y.Lin, and T.Y.Huang, EEE Electron Device Lett. 22, 179 (2001).

- <sup>10</sup> A. Javey, J. Guo, Q. W ang, M. Lundstrom, and H. Dai, Nature 424, 654 (2003).

- <sup>11</sup> P.L.McEuen, M.S.Fuhrer, and H.Park, IEEE Trans. Nanotech.1, 78 (2002).

- <sup>12</sup> The main e ect of charge on the NT (which we neglect) is to alter the potential within the NT channel. Source and drain SBs are relatively una ected in the energy range of signi cant tunneling current (c.f. Fig. 3). The current is limited by the channel only when there is negligible charge in the channel. As a result, the approximation gives a good description of the current (except perhaps in the fully \0 n" regim e<sup>8</sup>), and so does not a ect our conclusions.