# Ion beam sputtering method for progressive reduction of nanostructures dimensions

M. Savolainen, ', V. Touboltzev, P. Koppinen, K. P. Riikonen, and K. Arutyunov

<sup>1</sup>NanoScience Center, Department of Physics, University of Jyvaskyla

PB 35 (YFL), FIN-40014 University of Jyvaskyla

Jyvaskyla, Finland

(D ated: D ecem ber 11, 2021)

A n ion beam based dry etching m ethod has been developed for progressive reduction of dimensions of prefabricated nanostructures. The m ethod has been successfully applied to alum inum nanow ires and alum inum single electron transistors (SET). The m ethod is based on rem oval of m aterial from the structures when exposed to energetic argon ions and it was shown to be applicable multiple times to the same sample. The electrical m easurem ents and sam ples im aging in between the sputtering sessions clearly indicated that the dimensions, i.e. cross-section of the nanow ires and area of the tunnel junctions in SET, were progressively reduced without noticeable degradation of the sam ple structure. W e were able to reduce the electric diam eter of alum inum nanow ires from 65 nm down to 30 nm, whereas the tunnel junction area has been reduced by 40 %.

PACS num bers: 74.40.+ k, 68.65 La, 73.23 H k, 61.80 Jh

## I. IN TRODUCTION

There is a variety of di erent techniques available for fabrication of nano-or m icron-sized structures. U ltraviolet (UV) lithography is widely used in microelectronic industry to fabricate large-scale integrated circuits with vast am ount of functional elem ents at once. How ever, the minimum lateral dimensions attainable with this technique is about 250 nm. By using deep UV light the lim it might be pushed close to 100 nm in the future [1]. More advanced m ethods based on electron beam lithography (EBL) are capable to provide even smaller dimensions and have been applied, e.g., for fabrication of 5-7 nm wide etched lines on a silicon substrate[2]. However, when evaporating metallic structures through masksmadewith EBL the limit is higher, around 20-50 nm, depending on the molecule size of the resist material and the perform ance of the particular equipment. The disadvantage of EBL is that it is rather slow. X-rays lithography can in principle be used for patterning, but this method requires signi cantly more e orts and com plicated masks[1]. It is also possible to use the sharp tip of an atom ic force m icroscope (AFM ) to transfer single particles on a substrate to form a nanopattern [3]. A Itematively, one can oxidize patterns on the hydrogenpassivated surface with the tip or scratch the pattern on a thin resist layer (see R ef. 4 and references therein for detailed description of the AFM based methods). The di culty in using AFM in patterning is in rem ovalof the mask material (lift-o) after metalevaporation. As a result, at present m om ent AFM based nanofabrication has rather limited range of applications.

W e studied a di erent kind of approach where the dim ensions of the prefabricated nanosized structures are reduced by ion beam sputtering in controllable and reproducible way. We used alum inum nanow ires and single electron transistors (SET) to test applicability of the sputtering method. SET is one of the fundamental components in nanoelectronics and ultrasmall tunnel junctions in general have a lot of potential applications in the future [5]. The change in the dimensions of the tunnel junctions was detected by electrical measurements of the charging energy E  $_{\rm C}$  at liquid helium temperature 4.2 K. In case of a nanow ire, the decrease of the diameter was determined from the width of superconducting transition R (T).

G enerally speaking, it is common to study particular properties of the system of interest as a function of some characteristic dimension. Traditionally, many samples of di erent sizes are fabricated for this purpose. By using the sputtering method, the electrical measurements can be performed on the same sample, which dimensions are progressively reduced between the measurements. This way the inner structure of the system stays the same and thus there are less possibilities of having statistical errors due to circum stantial factors in fabrication.

# II. EXPERIMENTAL

#### A. Sam ple fabrication

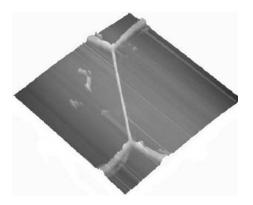

All samples were fabricated on oxidized silicon substrates. Conventional EBL technique was used in patterning followed by metallization in an UHV (Ultra High Vacuum) chamber. Double layer PMMA/MAA resist was used to form an appropriate undercut structure for the angle evaporation. N anow ires were formed by evaporating 45 nm of alum inum on top of the substrate through the PMMA mask. W idths of the fabricated nanow ires were approximately 50-80 nm. Figure 1 shows an AFM

E lectronic address: m arko.savolainen@ phys.jyu.

im age of a typical sam ple.

FIG.1: An overview AFM -im age of approximately 60 nm wide and 10 m long alum inum nanowire.

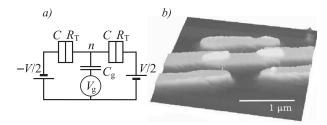

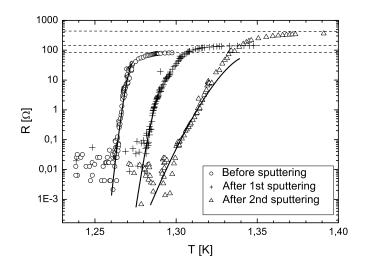

SET swere fabricated with a standard shadow evaporation technique. First 45 nm thick layer of alum inum was evaporated. A lum inum oxide barrier was grown in situ by natural oxidation in pure oxygen atm osphere (20 m bar) in the bading chamber of the UHV system. A fter oxidation another 45 nm layer of alum inum was deposited from another angle on top of the previously grown oxide layer to form tunnel junctions. Fig. 2 b) shows an AFM in age of a typical SET with two A LA D<sub>x</sub>-Al junctions. A bout 1 nm thick alum inum oxide layer between the alum inum electrodes forms a tunnel junction, which is thin enough to provide quantum mechanical tunneling of electrons through it[8].

FIG.2: a) Schem atics of a single electron transistor biased to voltage V,  $V_g$  is gate voltage. b) AFM im age of the SET after ion beam etching. This im age does not show the gate electrode. The top m ost and the bottom m ost lines are parasitic structures due to two-angle evaporation m ethod.

#### B. Description of the etching method

The sam ples were three-dimensionally dry etched by ion beam sputtering in a set-up consisting of a high vacuum (p  $10^{5}$  mbar) experimental chamber equipped with a sam ple manipulator and TECTRA Electron Cyclotron Resonance (ECR) plasma ion source capable of delivering high current, wide and hom ogeneous ion beam s. Before sputtering, the sam ples were cleaned with acetone in an ultrasonic bath and subsequently rinsed in

TABLE I: Sputtering rates of various m aterials [nm /m in] by 1 keV A  $r^+$  ions (0.014 m A /cm<sup>2</sup>).

| A lum inum <sup>a</sup> | SiO <sub>x</sub> /Si | Bulk Sapphire |

|-------------------------|----------------------|---------------|

| 1.1                     | 3.9                  | 0.75          |

$^{\rm a}{\rm T}\,{\rm he}$  alum inum had a natural oxide layer of about 1-2 nm on the surface when sputtered.

isopropanol. P rior to sputtering the surface of the structures was always checked by pro ler Tencor P15 that is capable to provide a vertical step height repeatability of

6-7 A. For dry etching, the sam ples were bom barded by 1 keV Ar<sup>+</sup> ions to a certain uence using an ion beam current density of about 0.014 m A /cm  $^2$  . In order to ensure uniform etching over the whole sputtered area, the ions incidence was 60 o the surface norm al, and the sam ples were rotated while sputtering. To avoid overheating of the sam ples exposed to high current ion beam , the sam ple holderm ade of copperwas cooled with water and the tem perature while sputtering was estim ated to be close to room temperature. Each sample contained co-evaporated strips, which were partly protected from the ion beam exposure by a droplet of a varnish. After etching the varnish was rem oved enabling the pro lom eter control of the surface step between the etched and the non-etched area. Sputtering rates for various m aterials are listed in the Table I.

A  $r^{+}$  ions of energy 1 keV in pinging on the surface at the angle of 60 degrees with respect to the surface norm all practically do not penetrate into the subsurface layers. Penetration depth of the A  $r^{+}$  ions into A lm atrix calculated by SR IM (Stopping and Ranges of Ions M atter) program [6] for the selected irradiation conditions is less than 15 A. Taking into account the high rate of the surface sputtering due to high density of the ion current and the glancing incidence, the ion beam etching can be considered as 'a gentle cut' of the up-m ost surface atom s without appreciable in uence on the underlying layers. The surface of the sam ples was controlled before and after the ion bom bardm ent with AFM, SEM and pro lom eter. The in uence of the sputtering has a polishing e ect, causing no noticeable destruction to the nanostructures.

#### C. Electrical m easurem ents

The superconducting transition of the wires was measured before and after the sputtering sessions. The resistance of the wires as a function of temperature was measured with the four-probem ethod. The samples were inserted into a directly pumped  ${}^{4}\text{H}$  e bath, where the tem – perature can be tuned with the accuracy of 0.1 mK.

In case of SETs the di erential conductance vs. bias voltage characteristics was measured at low voltages ( 10 mV per junction) at liquid helium temperature 4.2 K.The conductance measurements were performed with Nanoway CBT Monitor 400R, an instrument based on

The shape of the bottom part of a superconducting transition R (T) of not too narrow [13, 14] 1-D w ires is described by the model of temperature activated phase slips[15, 16]. The elective resistance exponentially depends on the ratio of the condensation energy of a m inimum size superconducting domain of size and the therm all energy  $k_{\rm B}$  T [15]:

$$R_{e}$$

(T)  $R_{N} \frac{L}{-} \exp \frac{B_{C}^{2}}{k_{B}T}$ ; (1)

where  $R_{\,N}\,$  is the norm all state resistance,  $L\,$  is the length of the wire,  $B_{\,C}\,$  (T ) is the critical magnetic  $\,$  eld, and

= K is the volume of the so-called phase-slip center (m in im um size of a superconductor to be driven norm al). Coe cient K should be of the order of one: K 1, relating the geom etrical size to the e ective one. The com – plete expression for the e ective resistance used for R (T) data thing includes other term sl5], being dependent, for example, on the ratio between the m easuring current and the critical current. However, the used m easuring currents (10 nA) were m uch sm aller than the critical value. Hence, these terms do not contribute quantitatively and are skipped in (1) for simplicity.

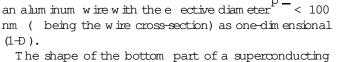

The cross-sections obtained from the measurements of the norm alstate resistance correlate wellw ith the ones used in the tting procedure (Table II). The common parameters used for the ts are the sample length L =10 m,  $_{BCS}(0) = 1.6$  m, K = 0.7, and the product of resistivity and m ean free path  $l = 4:3 \quad 10^{16} \quad m^2$ . The critical tem peratures T<sub>C</sub> used in thing procedure (Table II) correspond well to the experim entally observed on sets of superconductivity (Fig. 3). The increase of the critical temperature with the reduction of the alum inum wire cross-section (and, in general, the thickness of a lm ) is a well-known e ect. C om m only accepted explanation for this phenom enon is not yet settled, while various models are currently discussed [10, 11]. So far, no traces of the quantum phase slip phenom ena [13, 14, 17, 18] have been detected. At least, down to the alum inum wire e ective diam eter 30 nm .

The tting of the experimental data with model calculations[15] clearly indicates the reduction of the wire cross-section (Table II) while subsequent sputtering sessions. The absence of artefacts on the experimental R (T) dependencies (Fig. 3) proves that the dry ion etching does not cause 'serious' dam age to the sample (voids or constrictions), but removes the material from the surface gently and in a controllable way. Qualitatively similar results were obtained on few tens of samples.

#### B. Sputtered single electron transistors

A single electron transistor consists of an island isolated from the environm ent via two tunnel junctions, and

FIG. 3: R (T) dependency of an alum inum nanow ire before and after sputtering. Solid lines are the theoretical ts according to LAM H m odel[15]. Fitting parameters are listed in table II.

TABLE II: The tting parameters for the LAM H model[15] for the data from Fig. 3.

|                          | 0 riginal 2 | A fter 1st sputtering | A fter 2nd sputtering |

|--------------------------|-------------|-----------------------|-----------------------|

| T <sub>C</sub> [K]       | 1,285       | 1.316                 | 1.371                 |

| R <sub>N</sub> []        | 82          | 142                   | 380                   |

| В <sub>С</sub> (0) [m Т] | 8.0         | 7.5                   | 7.0                   |

| <u>][nm]</u>             | 15.8        | 12.8                  | 9.5                   |

| P _ [nm ]                | 65          | 55                    | 39                    |

an AC resistance bridge [9].

#### III. RESULTSAND DISCUSSION

#### A. Sputtered alum inum nanow ires

Fig. 3 shows a typicale ect of sputtering on the shape of superconducting transition of a w ire. It is clearly seen, that the transition becomes wider and the critical tem – perature  $T_C$  [10, 11] and the norm all state resistance  $R_N$  changes. All these observations indicate that the wire cross-section has decreased.

The dimensionality of a superconductor is determined by the temperature-dependent coherence length (T). For the 'dirty limit' superconductors (mean free path 1 is smaller than ) the elective coherence length (T) =  $0.85 (1_{BCS}(T))^{1=2}$  [12], where the zero-temperature BCS coherence length for aluminum is  $_{BCS}(0)$  1.6 m. Thus, formally, any size superconductor suiciently close to the critical temperature T<sub>C</sub> can be considered as 'low – dimensional'. However, if to restrict ourselves to tem – peratures apart from the luctuation range and the reasonably 'dirty' samples (1 10–30 nm), one can consider

a gate electrode which is not important for this study. The characteristic parameter of a single electron transistor is the charging energy, which is the energy required to add one extra electron into the island of an SET,

$$E_{C} = \frac{e^2}{2C}; \qquad (2)$$

where  $C = C_1 + C_2 + C_0$  is the sum of the capacitances of the junctions and the capacitance of the central island to the ground. U sually it is assumed that the ground capacitance  $C_0$  is negligible and the capacitances of the junctions are equal,  $C_1 = C_2$  C. The charging energy is of particular interest in this study because it is inversely proportional to the area of the junctions. This can be seen by substituting the expression for the plate capacitor  $C = ""_0A = d \text{ to } Eq. (2), where A is the junction area, d is the thickness and " the dielectric constant of an insulating barrier. Thus the charging energy depends on the size of the junctions.$

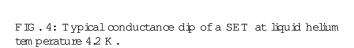

The conductance of a SET as a function of the bias voltage at low tem peratures shows a dip [7]. In this study the parameter of interest is the relative height of the G = G dip (Fig. 4), which is proportional to the charging energy [7]:

$G = G_T = \frac{E_C}{6k_B T}$ : (3)

∆G

10

15

By measuring the charging energy at liquid helium tem -

27.15

27,10

27,05

27,00

26,95

26,90

26.85

26,80 -15

-10

G [µS]

0

V [mV]

5

-5

perature 4.2 K before and after ion beam etching, one can determ ine how the areas of junctions have changed by sputtering. Here a natural assumption has been m ade that the thickness of the insulating layer and its dielectric constant " are not altered while etching.

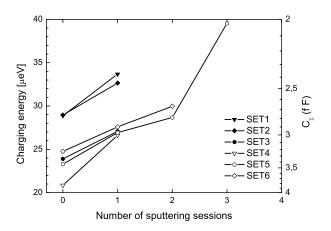

Figure 5 shows the charging energy of di erent SET samples measured after fabrication and each sputtering session. It is clearly seen that the sputtering increases the

charging energy gradually, indicating that the m ethod is capable of reducing the areas of the tunnel junctions. Similar e ect has been already observed [9]. As it follows from equation (3), the relative height of the conductance dip is inversely proportional to the junction area. Therefore, one can conclude from the Figure 5, that the junction areas of the sample "SET 5" have reduced by

40 % with respect to the original after three sputtering sessions. The tunnel junction resistances also increased while etching, additionally indicating the reduction of the tunnel junction areas. For instance, in sample "SET5" the original resistance was 37 k , and it became 84 k after third sputtering. Multisession sputtering was performed on m any of the samples without dam aging them . A ctually the sputtering was not always the cause of the broken SETs; m any of those were destroyed while m aking the electric contacts.

Since the tunnel junctions are form ed by thin oxide layers in between alum inum electrodes, there exists a possibility of natural 'aging' of the sam ples at norm al atm ospheric conditions leading to changes of characteristics. R efference m easurem ents were perform ed to rule out the possibility that charging energy changes 'by itself' by this natural aging. The charging energy of these sam ples was m easured repeatedly during the tim e period of several days. No increases in charging energy were observed. So we can be sure that the aging e lect is negligible.

FIG. 5: Charging energy of single electron transistors (left axis) and the total capacitance (rigth axis) as functions of the number of sputtering sessions.

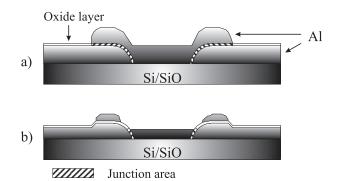

In the rst sputtering session a surface layer of approxim ately 25 nm was rem oved from the electrodes and the island form ing the SET. In the following 5-7 nm per session were etched. The behavior of sample "SET 5" is a bit surprising: although the sputtering conditions and estim ated thickness of the rem oved layers were the sam e in sessions 2 and 3, the increase of the charging energy is much larger after the third session. It im plies that either the sputtering rate changes as the dimensions of the SET structure become smaller, or a certain critical state of the system has been reached. W hat could this critical state be? Fig. 6 a) shows a schem atic drawing of the SET structure seen from the side just after fabrication. Due to of the shadow evapo-

FIG. 6: Schematic sideview of a single electron transistor. Figure a) represents the SET just after fabrication and b) after sputtering.

ration m ethod the m etal parts do overlap and the oxide layer gets its characteristic form having approximately vertical and horizontal parts. W hile sputtering, one – nally reaches a state pictured in Fig. 6 b). The m etallic contact between the m etal of the island and the m etal on top of the electrode is lost and 'suddenly' the e ective junction area is much smaller. W e assume, that the abrupt increase after third sputtering session for the structure "SET 5" (Fig. 5) is at least partly due to this threshold e ect.

The sputtering rate should not be necessarily the same form acroscopically large and nanosized objects. The calibration of sputtering rate in our experiments was done by measuring the height of the step developed between sputtered and non-sputtered regions on the large alum inum contact pads. A lthough the pro lom eter provides high vertical resolution ( 5-7A), the lateral dimensions of the nest parts in the nanostructures studied were not resolvable. Therefore, if at certain stage of sputtering the etching rate of the nest parts has dram atically increased, this would result in fast reduction of the areas of tunnel junctions and abrupt increase of the observed charging energy, e.g., after third sputtering session (Fig. 5). The possibility of such a scenario is currently under investigation. At present, know ledge about interaction of ions with low dimensional objects, like nanowires, ultrasm all tunnel junctions and nano-islands, is rather scarce. Ion sputtering of nanosized objects has not been well explored yet, and various aspects of this m ethod still have to be studied and developed in order to achieve a level suitable for various applications in nanofabrication.

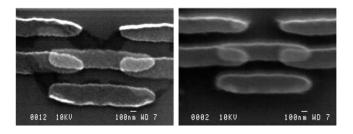

SEM and AFM in aging of the sputtered samples revealed no strongly developed topography on the surface norm ally attributed to a high uence ion irradiation. No trenches, craters or other extended defects on the surface were observed. On the contrary, the surface of the sputtered alum inum structures and their topography becam e sm oother after sputtering when com pared to as-

FIG.7: SEM images of SET.Left and right images represent the same sample before and after ion beam etching, respectively.

fabricated state (Fig. 7). It should be noted that single electron transistors are usually considered as very fragile to stay 'alive' under experim ental manipulations. Nevertheless, in our experiments both alum inum nanow ires and SETs showed a very high degree of stability under high current ion irradiation. Even those SET sam ples which were 'destroyed' in a sense that the resistance became in nite, SEM and AFM observations revealed no breakages or discontinuity. This peculiarity of SETs is still unexplained: they may show in nite resistance and still look perfect. In our experiments any radiation dam – age fatal for the perform ance of the wires and SETs should be smaller than 5 nm in size, otherwise they would be detected by our SEM and AFM.

## IV. CONCLUSIONS

We have demonstrated that the ion beam sputtering can be e ectively used for reducing the dimensions of prefabricated m etallic nanostructures without degradation of their properties and performance. The applicability of the method has been veried with alum inum nanowires and SETs. In the former case, the diameter of the wires was reduced from the initial 60-70 nm down to 30 nm. When the method was applied to SETs, the charging energy was found to increase indicating that the total area of the tunnel junctions decreased. Therefore, it was shown that dimensions of the nanostructures can be reduced by ion sputtering in a controllable and reproducible way.

By virtue of the surface nature of sputtering phenom enon, the m ethod was proved to be very 'gentle' in a sense that it allows to decrease the dim ensions of delicate nanostructures by gradually rem oving the surface layers w ithout introducing any changes into the interior. Reproducibility and controllability provided by the m ethod im ply that ion sputtering is in general applicable to nanoelectronic components and circuits containing nanosized w ires and tunnel junctions. The fact that the tunnel junctions 'stay alive' while sputterings m akes the range of applicability of the m ethod w ider. For instance the operational tem peratures of single electron devices can be extended by increasing the charging energy. It is believed, that bom bardm ent w ith low energy inert argon gas ions causes no chem ical reactions. The method is envisaged to be applicable to circuits based on any kind ofm etals, sem iconductors, insulators and their com binations, regardless of the chem ical composition and morphology. Since the method can be applied repeatedly to the same sample, gradual reduction of dimensions is achievable in those applications where the size e ect is studied or employed. Instead of fabricating a number of samples of di erent sizes and comparing their properties and perform ance, the sputtering method allows to work only with a single sample, thereby, avoiding uncertainties due to the circum stantial factors in fabrication.

- [L] Y.X ia and G M.W hitesides, Annu. Rev. M ater. Sci., 28, 153 (1998).

- [2] W . Chen and H. Ahm ed, Appl. Phys. Lett., 62, 1499 (1993).

- [3] A. Lindell, P. Davidsson and J. Pekola, M icroelectronic engineering, 45, 363 (1999).

- [4] A. Lindell, PhD. Thesis, Univ. of Jyvaskyla, Finland, 2000.

- [5] Yu A. Pashkin, Y. Nakam ura and J.S. Tsai, Appl. Phys. Lett. 76, 2256 (2000).

- [6] J.F. Ziegler, J.P. Biersack and U. Littmark, "The Stopping and Ranges of Ions in Solids", (Pergamon, New York, 1985).

- [7] J.P.Pekola, K.P.H irvi, J.P.K auppinen and M.A.Paalanen, Phys. Rev. Lett., 73, 2903 (1994); J.P.K auppinen, K.T.Loberg, A.J.M anninen and J.P.Pekola: "Coulom b blockade therm om eter: Tests and instrum entation", Review of Scienti c Instrum ents 69 (12), 4166-4175 (1998).

- [8] D etailed description of single charge tunneling phenom ena can be found for instance from "Single Charge Tunneling", ed. H.G rabert and M.H.D evoret (Plenum Press, New York, 1992).

- [9] V isit N anoway web site for a detailed m easurement principle of CBT M onitor 400R on http://www.nanoway.

## A cknow ledgm ents

This work has been supported by the A cadem y of Finland under the Finnish C entre of Excellence P rogram m e 2000-2005 (P roject No. 44875, Nuclear and C ondensed M atter P rogram m e at JYFL) and the EU C om m ission FP-6 NM P-1 "ULT RA -1D " project No:505457-1 "Experimm ental and theoretical investication of electron transport in ultra-narrow 1-dim ensional nanostructures".

- [10] Y. O reg and A M. Finkelstein, Phys. Rev. Lett., 83, 191 (1999).

- [11] R A.Sm ith, B.S.H andy, and V.Am begaokar, Phys. Rev. B, 63, 94513-1 (2001).

- [12] M. Tinkham, "Introduction to superconductivity" (second edition), (M cG raw Hill, Inc., New York, 1996).

- [13] A D. Zaikin, D S. Golubev, A. van Otterlo and G.T. Zim anyi, Phys. Rev. Lett., 78, 1552 (1997).

- [14] D S.G olubev and A D.Zaikin, Phys. Rev. B, 64, 014504 (2001).

- [15] J.S. Langer and V. Ambegaokar, Phys. Rev., 164, 498 (1967); D E. M cC umber and B J. Halperin, Phys. Rev. B, 1, 1054 (1970).

- [16] J.L. Lukens, R.J. W arburton and W W. Webb, Phys. Rev. Lett., 25, 1180 (1970); R.S. Newbower, M.R. Beasley and M. Tinkham, Phys. Rev. B, 5, 864 (1972).

- [17] N.Giordano, Physica B 203, 460 (1994).

- [18] A.Bezryadin, C.N.Lau, and M.Tinkham, Nature 404, 971 (2000); C.N.Lau, N.Markovic, M.Bockrath, A. Bezryadin, and M.Tinkham, Phys. Rev. Lett. 87, 217003 (2001).

- [19] Y.Nakamura, D.L.Klein and J.S.Tsai, Appl. Phys.Lett. 68, 275 (1996); and the cited literature.