## A lum inum Oxide Layers as Possible Components for Layered Tunnel Barriers

E.Cim poiasu<sup>1</sup>, S.K. Tolpygo<sup>1</sup>, X. Liu<sup>1</sup>, N. Sim onian<sup>1</sup>, J.E. Lukens<sup>1</sup>, R.F.K lie<sup>2</sup>, Y. Zhu<sup>2</sup>, and K.K. Likharev<sup>1</sup>

<sup>1</sup>Stony Brook University, Stony Brook, NY 11794-3800

<sup>2</sup>Brookhaven National Laboratory, Upton, NY 11973-5000

(D ated: A pril 14, 2024)

We have studied transport properties of N b/A l/A lb  $_{\rm x}$ /N b tunnel junctions with ultrathin alum inum oxide layers form ed by (i) them aloxidation and (ii) plasm a oxidation, before and after rapid them alpost-annealing of the completed structures at tem peratures up to 550 C . Post-annealing at tem peratures above 300 C results in a signi cant decrease of the tunneling conductance of them allygrown barriers, while plasm a-grown barriers start to change only at annealing tem peratures above 450 C . Fitting the experimental I-V curves of the junctions using the results of the m icroscopic theory of direct tunneling shows that the annealing of them ally-grown oxides at tem peratures above 300 C results in a substantial increase of their average tunnel barriers height, from 1.8 eV to 2.45 eV, versus the practically unchanged height of 2.0 eV for the plasm a-grown layers. This di erence, together with high endurance of annealed barriers under electric stress (breakdown eld above 10 M V/cm) m ay enable all-A lb  $_{\rm X}$  and SiO  $_2$ /A lb  $_{\rm X}$  layered "crested" barriers for advanced oating-gate m em ory applications.

PACS num bers: 73.40 Rw, 85.30 Kk, 85.30 M n

Calculations<sup>1,2,3</sup> indicate that tunnel conductance of layered barriers, in particular those with "crested" potential pro le peaking in the middle, may be much more sensitive to the applied voltage than that of the uniform layers.<sup>4</sup> This sensitivity, if combined with high endurance to electric stress, may be used in advanced oatinggate m em ories, including fast and scalable random access m em ories<sup>5</sup> and fast single-and few -electron m em ories, $^{6,7}$ and ultradense data storage system  $s_{r}^{1}$  as well as for improvement of the usual nonvolatile (e.g., "ash") m em ories.<sup>8,9</sup> H ow ever, nding an appropriate com bination of materials for crested barrier layers presents a challenge. Indeed, num erous experim ents (for a review see, e.g., Ref.[10]) indicate that just a few known CMOScompatible materials may combine the barrier height su cient for therm ionic current suppression at room tem perature (above 1.5 eV), with the necessary high breakdown eld (above 10 MV/cm), and negligible trapassisted tunneling. To our know ledge (see also the recent theoretical calculations)<sup>11</sup>, the list of such candidate m aterials is essentially limited to: (i) silicon dioxide, (ii) low-trap-density silicon nitride that m ay be grown using special methods,<sup>12,13</sup> and (iii) alum inum oxides grown by a variety of m ethods including notably therm  $al^{14}$  and  $plasm a^{15}$  oxidation.

The goal of this paper is to show that the alum inum oxides represent a good material choice for fabrication of crested barriers. Experimental measurements of the most important parameter in this context, the average tunnel barrier height hU i, have been reported for aluminum oxide layers in quite a few publications. Unfortunately, the cited values of hU i, are scattered rather broadly: for thermally-grown oxides, most results are in the range from 1.7 to 2.5 eV (see, e.g., Refs. [16-22]), but values as low as 1.2 eV, <sup>23</sup> and as high as 4.75 eV, <sup>24</sup> or even 20 eV, <sup>25</sup> have also been derived from the data. Similarly, for plasm a-grown layers, most reported values

of hU i, are in the range from 1.7 to 2.3 eV (see, e.g., Refs. [24], [26-30], <sup>31</sup> but num bers as high as 3.6 eV have also been claim ed.<sup>29</sup> The published results for the apparent barrier asymmetry, U  $U_{max}$   $U_{min}$ , are scattered even more, from a few tenths of eV all the way up to 6  $eV_{r}^{24}$  and the only apparent consensus is that the barrier is always higher at the top (counter-electrode) interface. Probably, the most important source of these di erences are those of the lm fabrication, including the substrate tem perature (that has not always been carefully m onitored) and the counter-electrodem aterial. How ever, som e result scattering m ay be also attributed to the variety oftechniques used for barrier height measurem ent, including I-V curve tting,<sup>16,17,18,19,20,21,22,24,25,27,28,29,30</sup> photoelectric e ect, 18,20,26 and ballistic electron em ission spectroscopy.<sup>23</sup> Som e of these m ethods m ay give rather inaccurate results. For example, as it has been shown in our recent work,<sup>22</sup> tting of I-V curves of alum inum oxide barriers with WKB approximation results may lead to substantial errors, since such barriers are rather thin and sharp. These errors may be dram atically increased if low-V expansions of W KB form ulas<sup>32,33</sup> are used, as this procedure is highly vulnerable to m inor additional currents due to inelastic (e.g., trap-assisted) tunneling - see, e.g., Fig. 2 and its discussion below . Our experience shows that thing the slope of the "Fow ler-Nordheim" plot" (lnI vs. 1=V) of high-V data may also lead to very substantial errors. The experim ental inform ation on the e ective m ass of the tunneling electrons is even m ore lim ited (see the discussion below).

O ne m ore m otivation for additional experim entation was to study the e ects of rapid therm alpost-annealing of tunnel junctions. It was noticed previously that thermalannealing m ay in prove tunneling m agnetoresistance of junctions between m agnetic layers<sup>34,35,36,37,38,39,40</sup> and, for high annealing temperatures  $T_a$ , change the atom ic structure of the oxide quite substantially<sup>41</sup>. How -

ever, the annealing e ect on the barrier height HJ i, has not been studied in any detail, to the best of our know ledge. (Some changes in HJ i, at  $T_a < 300$  C were noticed in Refs. [34], [36], and [38-40], but the uncertainty of the results, obtained using the W KB expansion,<sup>32,33</sup> was comparable with the change itself.) Thus, we have carried out detailed studies of tunnel barriers grown by therm al and plasm a oxidation of alum inum, and rapid post-annealed at various tem peratures.

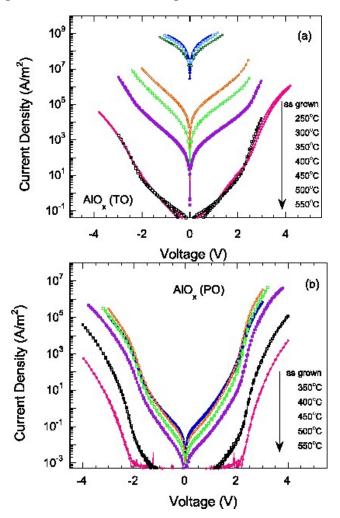

FIG.1: Experimental current density J as a function of the applied dc voltage V for Nb/A  $I/A D_x/Nb$  junctions with (a) them ally-grown (C rest 5) and (b) plasm a-grown (C rest 19) oxide layers, before and after the rapid them all anneals at indicated tem peratures, as measured at 4.2 K. The noisy attening of the lower curve in panel (b) at sm all voltages is due to leakage of our measurement setup at I 10<sup>13</sup> A.

The oxide layers have been grown on oxidized Siw afers (10 -cm) covered by 500 nm of therm ally-grown SiD<sub>2</sub>, as components of standard Nb-trilayer junctions.<sup>42</sup> The oxides were form ed in-situ on 10-nm -thick alum inum

In s that had been dc-m agnetron-sputtered on sim ilarly deposited 150-nm thick niobium Im s, using either exposure to dry oxygen or in 13.6 M H z oxygen plasm a, both at room temperature. (W afers were kept on a watercooled, dc-insulated holder.) A fter in-situ sputtering of a niobium 100-nm -thick counter-electrode and sam ple patterning into junctions of various area A (3 3, 30 30, and 300 300 mm<sup>2</sup>), a few chips from each wafer were subjected to rapid therm alannealing. D C I-V m easurements of both as-oxidized and annealed junctions have been carried out at both room and helium (4.2 K) tem peratures, using a special low -noise, high-sensitive setup. Voltage sweeps with gradually growing amplitude were used to characterize transport up to the very onset of hard breakdown.

Here we focus on comparing the results from two representative wafers: "C rest 5" (therm alloxidation for 40 m inutes at 100 Torr) and "C rest 19" (plasm a oxidation for 3 m inutes at 15 m Torr), both post-annealed at tem – peratures up to 550 C in inert atm osphere (either A r or N<sub>2</sub>).<sup>43</sup> The junctions, both before and after post-annealing, were highly reproducible, with the rm s. on-chip (junction-to-junction) variation of low -voltage conductance from as low as 0.8% (considerably better than any published results we are aware of) to 20% (comparable with the reported results – see, e.g., Ref. [44]).

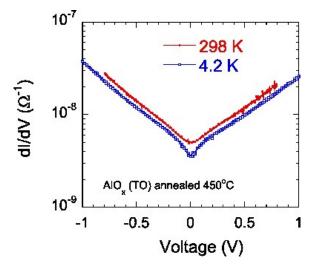

FIG. 2: The nonlinear "dynamic" conductance G (V) dI=dV of a typical 450 C -annealed sample from wafer C rest 5, measured at liquid-helium and room temperatures.

Figure 1 shows I-V curves of representative junctions from these two wafers, both before and after postannealing at various temperatures. (These data have been taken at helium temperature; however, the increase oftem perature to 300 K changes the current only slightly – see Fig. 2). First of all, one can see that the annealing above 300 C leads to a considerable improvement of the junction quality: the hard breakdown voltage V<sub>b</sub> increases, and the I-V curves show virtually no hysteresis or "soft breakdown", up to V<sub>b</sub>. (For therm ally-grown oxides annealed at 500 C and beyond, the hysteresis appears again, though V<sub>b</sub> continues to grow .) M ore quantitatively, the charge to breakdown, m easured at room temperature for sam ples annealed at 450 C, stays above  $10^5$  C/cm<sup>2</sup> (i.e., a few orders of m agnitude higher than the level typical for industrial grade SiO  $_2$  barriers)<sup>14</sup> until 2.1 V for both C rest 5 and C rest 19 samples.

However, our most important observation is a dramatic di erence between the e ects of annealing tem – perature upon the therm ally-grown and plasm a-grown oxides: while the low-voltage conductance of the former junctions drops sharply starting above 300 C and reaches almost 6 orders of magnitude by 450 C,<sup>45</sup> the reduction in the latter barriers is m inor (below 2 orders of magnitude) until the annealing tem perature has been raised to 500 C. In order to give at least a phenom enological interpretation of this e ect, we have used theoretical ts to extract essential tunnel barrier parameters of the A D<sub>x</sub> layers.

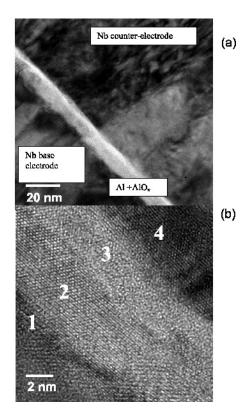

FIG.3: (a) High-resolution transm ission-electron-m icroscope im ages of a 450 C post-annealed sample from wafer C rest 5 for two di erent m agni cations and (b) m agni ed part of the layered structure with the position of the electron energy loss spectroscopy spectra indicated.

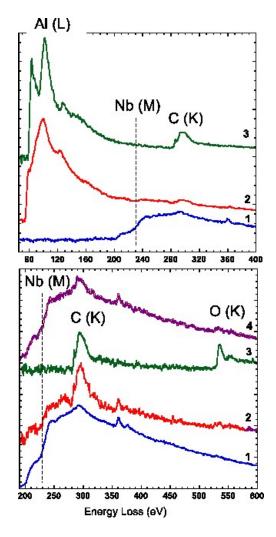

The shape of I-V curves of the sam ples (Fig. 1), and their very weak temperature dependence (Fig. 2) are consistent with the assumption of direct tunneling of electrons through the barrier.<sup>46</sup> [This conclusion is also supported by the results of high-resolution m icroscopy (Fig. 3) and electron energy loss spectroscopy (Fig. 4) of the annealed sam ples, show ing a well-de ned oxide layer with sharp interfaces with both base and counter-electrodes.] This is why we have tted our experimental data with results of a "m icroscopic" (non-W K B) theory of such tunneling. Our general com puter algorithm is based on the

FIG. 4: Results of the electron energy loss spectroscopy for two energy ranges from the positions indicated in Fig. 3b: 1 - Nb base electrode,  $2 - the middle of Al layer, <math>3 - A D_x$ layer, and 4 - Nb counter-electrode. The spectra are background subtracted, and corrected for multiple scattering contributions. The carbon K-edge present in all the spectra stem s from the carbon build-up during the spectrum acquisition and is not a feature of the sam ple structure.

jpint solution of the 1D Schrödinger equation (using the transferm atrix technique) and Poisson equation for tunneling electrons.<sup>47</sup> How ever, we have found that the barrier shape modi cation by the charge of tunneling electrons is very small. The exclusion of the Poisson solver from the code makes it very fast: simulation of one I-V curve in 100 points with a few percent accuracy takes about 1 minute on a single-processor workstation. The code has been checked on the results for SiO<sub>2</sub> layers described in Ref. [48], and gave similar results to those of the theoretical calculations in that sem inal paper.

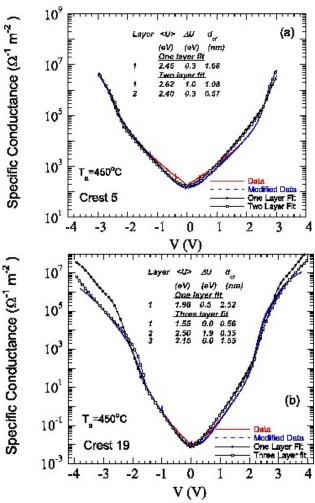

Figure 5 shows the results of the tting of the voltage dependence of the speci c dynam ic conductance g(V)A <sup>1</sup> dI(V)=dV for junctions of both types post-annealed at 450 C. The advantage of tting the semilog g(V) plots

4

rather than the lnI(V) curves (Fig. 1) is that in the form er case the peculiarities of low -voltage behavior are revealed m ore clearly - see also F ig. 2. T hey show, in particular, a m inor "cusp" contribution  $G_h$  / j j<sup>1</sup> to the conductance (and hence  $I_h$  / sgn (V) J j to current,) sim ilar to that observed and discussed by others - see, e.g., Refs. [46], [49-51]. Figure 2 shows that this current component is more sensitive to temperature than the current at higher voltages, though this tem perature dependence is stillm uch weaker than that for the Poole-Frenkel conductance m echanism .52 Though the exact identi cation of the physics of the  $I_h$  component is beyond the scope of this work, we believe that it is due to som e sort of hopping (trap-assisted tunneling) strongly a ected by the Coulomb interaction of the hopping electrons. In fact, it may be best tted with the values ( =  $1.8 \quad 0.1$ for C rest 5 and  $= 2.0 \ 0.3$  for C rest 19) that are relatively close to that of the classical M ott-G unney law ( = 2) for space-charge-lim ited current.<sup>53</sup> A better agreement would be hard to expect, since the Mott-Gumey model implies that the layer thickness d is much larger than the localization radius a of a typical trap, and the thickness of our barriers (d 2 to 3 nm as shown below) is comparable with the estimated value a 1 nm . For the best tting, we have subtracted Ih from the data (see the dashed lines in Fig. 5), although the tting results are appropriate even for the raw data.

As Fig. 5 shows, a relatively good tting of the data m ay be achieved with the traditional trapezoidal (i.e., one-layer) m odel of the barrier. How ever, better tting is provided by the potential pro le approximation with two (for C rest 5) or three (for C rest 19) linear pieces, im plying a layered structure of the oxide. This is not too surprising, since the com plex interface chem istry, as well as trapped charge in purities (see, e.g., Ref. [54]) m ay provide interfacial layers with properties di erent from the oxide bulk. Note that while the I-V curve tting gives very de nite results for the e ective thickness  $d_{ef} = (m = m_0)^{1=2}d$  of the layers, it cannot distinguish the contributions to  $d_{ef}$  from the e ective m assm of the tunneling electron and from the physical thickness d of the barrier.<sup>55</sup>

In order to estimate d (and hence m), we have used m easurem ents of speci c capacitance C 0 of the annealed junctions (at  $T_a = 450$  C). The speci c capacitance has turned out to be close to 2.8  $0.7 \,\mathrm{m\,F/cm^{2}}$  for C rest 5 and 2.3 0.5 m F/cm<sup>2</sup> for C rest 19. A ssum ing that the dielectric constant of the alum inum oxides is within the range 9 1 (cited in most publications), the capacitance values imply that the physical thickness of oxides is 2.85 0.25 nm for the therm algrow th and 3.45 0.25 nm for the plasm a oxidation. These estimates have been con med using high-resolution transmission electron microscopy (HRTEM). For example, Fig. 3 shows two images of a representative C rest 5 junction annealed at 450 C. The picture quality is a ected by the fact that the base Nb electrode is relatively thick and polycrystalline, so its surface is uneven at a-few-nm scale. Nevertheless, the im-

FIG.5: Fitting of the speci c dynam ic conductance g(V) A  $^1$  dI (V)=dV of post-annealed (450 C) junctions with (a) them ally-grown and (b) plasm a-grown barriers with m icroscopic theory of direct tunneling. Solid lines show raw data, dashed lines – the data corrected for trap-assisted tunneling (see the text), curves with solid points show the best ts with one-layer (trapezoidal) m odel, while those with open points for m ore com plex potential pro les. The tting param eters (the average barrier height hU i, asymmetry U, and e ective thickness  $d_{\rm ef} = (m = m_0)^{1=2}$ d) are listed inside for each layer, from the base electrode up).

ages reveal an am orphous  $A lO_x$  layer with a thickness of 3 nm, i.e. reasonably close to that extracted from capacitance m easurem ents.

U sing the e ective thickness determ ined by our tting procedure (see Fig. 5) we estimate the e ective mass  $(0.35 \ 0.20)$ m<sub>0</sub> for the thermally-grown oxide and  $(0.50 \ 0.15)$ m<sub>0</sub> for the plasm a-grown oxide. These values are in a reasonable agreement with the theoretical result 0.4m 0 of Ref. [56], but substantially somewhat lower than the value 1.0m<sub>0</sub>, which may be deduced from the experimental results of Ref. [58], assuming that the average barrier height for those lm s (thermally-grown with UV stimulation and then annealed at 250 C) is the same as for our therm ally-grown layers annealed at the sim ilar tem perature. (Probably, the reason of the discrepancy is that the above assumption is incorrect, i.e. that the UV stimulation increases the barrier height substantially.)

We have applied the tting procedure described above to extract the average barrier height for both as-grown and post-annealed alum inum oxides. We found that the average barrier height hU i, of the therm ally-grown oxide increases rapidly at annealing tem peratures above 300 C: from an initial value of  $1.8 \text{ eV}^{22}$  to 2.45 eV at 450 C, and rem ains close to this value for all the higher annealing tem peratures we have explored (up to 550 C). On the other hand, the average barrier height of the plasm agrown oxide remains practically unchanged at around 2 eV. Sem i-quantitatively, this is directly visible from the high-V experimental data shown in Fig. 1, since the barrier height (expressed in electron-Volts) is always close<sup>20</sup> to the voltage of the maximum positive curvature of sem i-logarithm ic plots lnI vs. V, corresponding to the crossover between tunneling through the barrier as a whole at lower voltages, and the Fow ler-Nordheim tunneling through its unsuppressed part at higher V.

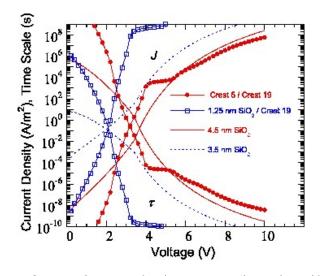

Thus the average barrier height for them ally-grown, post-annealed alum inum oxide layers is substantially (by 25%) higher than that in the plasm a-grown layers. This fact o ers the possibility of using the oxides in layered (e.g., "crested") barriers for advanced oating-gatem em - ories and other applications.<sup>1</sup> Figure 6 shows the tunnel current density J I=A and the corresponding time scale of oating gate recharging calculated for two prom ising layer combinations: (i) them al oxide sim ilar to annealed C rest 5, plus plasm a oxide sim ilar to C rest 19, and (ii) 1.25-nm SiO<sub>2</sub> layer, plus A D<sub>x</sub> layer sim ilar to C rest 19.

The plots show that the all-alum inum layered barrier of type (i) m ay sustain the 10-year retention time (standard for nonvolatile m em ories) at voltages below 1.5 V, while the voltage increase to 4 V (i.e., by a factor less than 3, enabling a simple NOR structure of m em ory blocks5) would cause the gate recharging in 10 s. Such w rite/erase time is still too long for RAM applications. Notice, how ever, that the voltage applied to each of the layers would be below 2.2 V, ensuring high endurance: charge-to-breakdow n well above  $10^5 \text{ C/cm}^2$ , corresponding to m ore than  $10^6 \text{ re-w}$  rite cycles. This option m ay be attractive for low-voltage ash m em ories, especially because there are good prospects of increasing the barrier endurance even further by using higher post-annealing tem peratures<sup>58</sup> and/or Zr alloying of the barriers.

The results for option (ii), i.e., SiO<sub>2</sub>/A lO<sub>x</sub> barriers, are even more interesting. At V = 3.2 V (or higher) such a barrier would allow the oating gate to recharge in less than 1 nanosecond, with voltage about 1.6 V across each layer. For electric elds that are so low, we could not even m easure the charge-to-breakdown experim entally, but a simple extrapolation of the high-V data gives an estim ate of  $10^{15}$ C/cm<sup>2</sup>, corresponding to  $10^{11}$  re-writing cycles, which are su cient for RAM applications. The draw back of these barriers would be a relatively short retention time ( 100 s at 1.5 V). Too short for nonvolatile m em ories, this time is still su ciently long for DRAM – like m em ories with periodic refresh.

FIG. 6: Tunnel current density J = I=A (increasing with the applied voltage V) and the recharging time constant  $C_0V=J(V)$  (decreasing with voltage) for two layered tunnel barriers and two uniform  $SiO_2$  barriers, calculated using the alum inum oxide parameters shown in the inset of Fig. 5 and for silicon dioxide parameters taken from R ef. 48 (U = 3.34 eV, m = m\_0 = 0.35). The used dielectric constant values are 10 and 3.9, respectively.

These estimates should be, of course, looked upon with caution, since the calculations shown in Fig. 6 in ply that the two layers, which had been grown and measured separately in our experiments, may be combined without a substantial change of their properties. It is more probable that the sequential deposition of the layers will cause at least a moderate change of their parameters and, hence, a deviation from these predictions. Note, how ever, that these changes may be either detrimental or bene – cial for the crested barrier properties. Moreover, some barrier parameters (e.g., thickness of the plasma-grown layer) can be easily changed to compensate for undesirable barrier alterations and to improve the crested barriers performance even further.

To sum marize, we have found experimental evidence that electron transport through thermally-or plasmagrown, post-annealed ultrathin alum inum oxide layers is dominated by direct tunneling in electric elds up to

10 MV/cm. The e ective height of the corresponding tunneling barriers, within the annealing temperature range from 300 C to 550 C, is substantially dependent on whether the layer has been grown by therm alor plasm a oxidation. This fact o ers hope for the implementation of layered all-A D<sub>x</sub> and SiD<sub>2</sub>/A D<sub>x</sub> barriers for advanced oating-gate memories. Our plans are to explore such barriers experimentally in near future.

This work was supported in part by AFOSR. The authors are grateful to Yu. A. Polyakov and X. W ang for technical assistance. Useful discussions with A. Bratkovsky, J.Cosgrove, M.Gribelyuk, M.Gurvitch, E.

- <sup>1</sup> K.K.Likharev, Appl. Phys. Lett. 73, 2137 (1998).

- <sup>2</sup> A.N.Korotkov and K.K.Likharev, in 1999 EDM Tech. Digest (EEE Press, Piscataway, NY, 1999), p.223.

- <sup>3</sup> J.D.Casperson, L.D.Bell, and H.A.Atwater, J.Appl. Phys. 92, 261 (2002).

- <sup>4</sup> A similar, but smaller increase of the voltage sensitivity may come from the di erence of the dielectric constants of the layers - see B.G ovoreanu, P.B lom me, M.R osmeulen, J.Van Houdt, and K.DeMayer, IEEE Electron Dev.Lett. 24, 99 (2003).

- $^5\,$  K .K .Likharev, <code>EEE C</code> incuits and <code>Devices16,16</code> (2000).

- <sup>6</sup> K.K.Likharev, Proc. EEE 87, 606 (1999).

- <sup>7</sup> A.N.Korotkov, J.Appl.Phys. 92, 7291 (2002).

- <sup>8</sup> W. D. Brown and J. E. Brewer (eds.), Nonvolatile Sem iconductor Memory Technology, (IEEE Press, New York, 1998).

- <sup>9</sup> P.Pavan, R.Bez, P.O livo, and E.Zanoni, Proc. IEEE 85, 1248 (1997).

- <sup>10</sup> G.D.W ik, R.M.W allace, and J.M.Anthony, J.Appl. Phys. 89, 5243 (2001).

- <sup>11</sup> J.W .M cPherson, J.K im, A.Shanware, H.M ogul, and J. Rodriguez, IEEE Trans. on Electron Dev. 50, 1771 (2003).

- <sup>12</sup> T.P.Ma, EEE Trans. on Electron Dev. 45, 680 (1998).

- <sup>13</sup> M. She, H. Takeuchi, and T.-S.King, IEEE Electron Dev. Lett. 24, 309 (2003).

- <sup>14</sup> J.C.Fisher and I.G iaever, J.Appl.Phys. 32, 172 (1961).

- <sup>15</sup> J. L. M iles and P. H. Sm ith, J. Electrochem. Soc. 110, 1240 (1963).

- <sup>16</sup> D.M eyerhofer and S.A.Ochs, J.Appl. Phys. 34, 2535 (1963).

- <sup>17</sup> S.R.Pollack and C.E.Morris, J.Appl.Phys. 35, 1503 (1963).

- <sup>18</sup> K.W. Shepard, J.Appl.Phys. 36, 796 (1965).

- <sup>19</sup> L.L.Chang, P.J.Stiles, and L.Esaki, J.Appl. Phys. 38, 4440 (1967).

- <sup>20</sup> K.H.Gundlach and J.H ltz, Surf. Sci. 27, 125 (1971).

- <sup>21</sup> D.McBride, G.Rochlin, and P.Hansma, J.Appl.Phys. 45, 2305 (1974).

- <sup>22</sup> S.K. Tolpygo, E.Cimpoiasu, X.Liu, Yu.A.Polyakov, J.E.Lukens, and K.K.Likharev, IEEE Trans. on Appl. Supercond.13, 99 (2003).

- <sup>23</sup> W. H. Rippard, A. C. Perrella, F. J. A lbert, and R. A. Buhrm an, Phys. Rev. Lett. 88, 046805 (2002).

- <sup>24</sup> J.C. Lau and R.V. Coleman, Phys. Rev. B 24, 2985 (1981).

- <sup>25</sup> K.G loss, P.J.K oppinen, and J.P.Pekola, J.Phys.: Cond. M att. 15, 1733 (2003).

- <sup>26</sup> A. I. Braunstein, M. Braunstein, G. S. Picus, and C. A. Mead, Phys. Rev. Lett. 14, 219 (1965).

- <sup>27</sup> A.M. Goodman, J. Appl. Phys. 41, 2176 (1970).

- <sup>28</sup> J.K adlec and K.H.G undlach, Solid State Commun.16, 621 (1975).

- <sup>29</sup> J. Scham alhorst, H. Brckl, M. Justus, A. Thom as, G. Reiss, M. Vieth, G. Giers, and J. Wecker, J. Appl. Phys. 89, 586 (2001).

- <sup>30</sup> J. Du, X. H. Xiang, G. Landry, B. You, A. Hu, H. W. Zhao, J.Q. Xiao, J. Appl. Phys. 91, 8780 (2002).

- <sup>31</sup> M ost experiments with A kO<sub>3</sub> In s fabricated by other methods (such as rf magnetron sputtering from a stoichiometric source, or atom ic layer deposition) also give hU i, within this range - for a brief literature review see V. V. A fanas'ev, M. Houssa, A. Stesmans, and M. M. Heynes, J. Appl. Phys. 91, 3079 (2002).

- <sup>32</sup> J.G. Simmons, J. Appl. Phys. 34, 1793; 2581 (1963).

- <sup>33</sup> W .F.Brinkm an, R.C.D ynes, and J.M.Rowell, J.Appl. Phys. 41, 1915 (1970).

- <sup>34</sup> R.C. Sousa, J.J. Sun, P.P. Freitas, A.K ling, M.F. da Silva, J.C. Soares, Appl. Phys. Lett. 73, 3288 (1998).

- <sup>35</sup> S.S.P.Parkin, K.-S.Moon, K.E.Pettit, D.J.Smith, R. E.Dunin-Borkowski, M.R.McCartney, Appl. Phys. Lett. 75, 543 (1999).

- <sup>36</sup> R.C. Sousa, J.J. Sun, P.P. Freitas, A.K ling, M.F. da Silva, J.C. Soares, J.Appl.Phys. 85, 5258 (1999).

- <sup>37</sup> J.Schmalhorst, H.Bruckl, G.Reiss, M.Vieth, G.Gieres, J.Wecher, J.Appl.Phys. 87, 5191 (2000).

- <sup>38</sup> S.Cardoso, P.P.Freitas, C.de Jesus, P.W ei, J.C.Soares, Appl.Phys.Lett. 76, 610 (2000).

- <sup>39</sup> K.I.Lee, J.H.Lee, W.Y.Lee, K.W. Rhie, J.G.Ha, C. S.Kim, K.H.Shin, J.Magn. & Magn. Mater. 239, 120 (2002).

- <sup>40</sup> K.I.Lee, K.H.Chae, J.H.Lee, J.G.Ha, K.Rhie, W.Y. Lee, K.H.Shin, Microelectron. Eng. 69, 305 (2003).

- <sup>41</sup> P.C. Snijders, L.P.H. Jeurgens, and W.G. Skof, Surf. Sci. 496, 97 (2002).

- <sup>42</sup> M.Gurvitch, M.A.W ashington, and H.A.Higgins, Appl. Phys.Lett. 24, 472 (1983).

- $^{43}$  W hile the run-to-run reproducibility of annealing results was very good, and we could get very similar results for annealing in both A r and N<sub>2</sub>, the gas choice has unfortunately resulted in a substantial shift: in order to get the same annealing e ect in argon, the perceived temperature should be approximately 100 C higher than for nitrogen, apparently because of a di erent gas pressure. This is why the temperatures cited below (that are the averages between the readings for A r and N<sub>2</sub>) should be considered as uncertain by approximately 50.

- <sup>44</sup> E.Y. Chen, R.W hig, J.M. Slaughter, J. Goggin, G. Steiner, and S. Tehrani, J. Appl. Phys. 87, 6061 (2000).

- <sup>45</sup> A recent study of annealing of them ally-grown alum inum oxides has shown much smaller conductance suppression within the same range of annealing temperatures – see H. Scherer, Th. Weimann, A. B. Zorin, and J. Niemeyer, J. Appl. Phys. 90, 2528 (2001). Possible reasons of the difference include the much lower oxygen exposure ( $10^5$ Pa-s vs. 3  $10^7$  Pa-s for our Crest 5) and a di erent counter-electrode material (Alvs. our Nb). An additional argum ent for the latter hypothesis is provided by the fact that annealing of junctions with various ferrom agnetic electrodes<sup>34,35,36,37,38,39,40</sup> gives broadly scattered results, in some cases<sup>34,36,38</sup> leading to an increase of the tunnel conductance.

- <sup>46</sup> J.J.A kerm an, J.M. Slaughter, R.W. Dave, I.K. Schuller, Appl. Phys. Lett. 79, 3104 (2001).

- <sup>47</sup> The code included a phenom enological description of en-

ergy relaxation of tunneling electrons in the classically allowed part of the barrier. Such relaxation, in particular, suppresses the current resonances due to the overbarrier re ection – see, e.g., M. V. Fischetti, D. J. D M aria, L. D ori, J. B atei, E. Tierney, and J. Stasiak, Phys. Rev. B 35, 4404 (1987) and references therein.W e have found that the best agreem ent with the alum inum oxide data m ay be achieved assuming the characteristic relaxation length is below 1 nm, i.e. sm aller than the barrier thickness.

- <sup>48</sup> M. Fukuda, W. M izubayashi, A. Kohno, S. M iyazaki, and M. H irose, Jpn. J. Appl. Phys. (pt. 2) 37, L1534 (1998).

- <sup>49</sup> J.S.M oodera, J.N owak, and R.J.M .van der Veerdonk, Phys. Rev. Lett. 80, 2941 (1998).

- <sup>50</sup> J. R. Kirtley, S. W ashburn, and D. J. Scalapino, Phys. Rev. B 45, 336 (1992).

- <sup>51</sup> S. Meng, C. Basceri, B. W. Busch, G. Derderian, G. Snadhu, Appl. Phys. Lett. 83, 4429 (2003).

- <sup>52</sup> J.L.Hartke, J.Appl.Phys. 39, 4861 (1968).

- <sup>53</sup> N.F.M ott and R.W. .G umey, Electronic Processes in Ionic

Crystals (Oxford U. Press, London, 1940); reproduced, e.g., by M.A. Lampert, Phys. Rev. 103, 1648 (1956).

- <sup>54</sup> R.S.Johnson, G.Lucovsky, and I.Baum vol, J.Vac.Sci. Technol.A 19, 1359 (2001).

- $^{55}$  In fact, the expression  $d_{\rm ef} = (m=m_0)^{1=2}d$  is exact only within the W KB approximation.We have checked that the m icroscopic theory gives results that m ay be approximated with the form ula  $d_{\rm ef} = (m=m_0)$  with the values of very close to 0.5 (0.506 for the parameters inferred for sample C rest 5 and 0.502 for C rest 19).

- <sup>56</sup> A.M. Bratkovsky, Phys. Rev. B 56, 2344 (1997).

- <sup>57</sup> M.Covington, J.Nowak, and D.Song, Appl. Phys. Lett. 76, 3965 (2000).

- <sup>58</sup> S.-W. Huang and J.-G. Hwu, IEEE Trans. on Electron D evices 50, 1658 (2003).

- <sup>59</sup> S.-R. Lee, C.-M. Choi, and Y. K. Kim, Appl. Phys. Lett. 83, 317 (2003).